JP6068767B2 - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- JP6068767B2 JP6068767B2 JP2016018941A JP2016018941A JP6068767B2 JP 6068767 B2 JP6068767 B2 JP 6068767B2 JP 2016018941 A JP2016018941 A JP 2016018941A JP 2016018941 A JP2016018941 A JP 2016018941A JP 6068767 B2 JP6068767 B2 JP 6068767B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- impurity element

- insulating film

- stress

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 140

- 239000012535 impurity Substances 0.000 claims description 157

- 239000000758 substrate Substances 0.000 claims description 83

- 230000015572 biosynthetic process Effects 0.000 claims description 25

- 239000004020 conductor Substances 0.000 claims description 3

- 239000010408 film Substances 0.000 description 418

- 230000035882 stress Effects 0.000 description 188

- 238000000034 method Methods 0.000 description 87

- 239000010410 layer Substances 0.000 description 73

- 238000010438 heat treatment Methods 0.000 description 62

- 239000000463 material Substances 0.000 description 38

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 32

- 229910052710 silicon Inorganic materials 0.000 description 32

- 239000010703 silicon Substances 0.000 description 32

- 239000010409 thin film Substances 0.000 description 30

- 238000004544 sputter deposition Methods 0.000 description 23

- 238000004519 manufacturing process Methods 0.000 description 22

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 21

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 20

- 239000003566 sealing material Substances 0.000 description 20

- 239000004973 liquid crystal related substance Substances 0.000 description 19

- 230000008569 process Effects 0.000 description 19

- 238000000137 annealing Methods 0.000 description 18

- 239000011229 interlayer Substances 0.000 description 18

- 230000008859 change Effects 0.000 description 17

- 238000002425 crystallisation Methods 0.000 description 17

- 239000011159 matrix material Substances 0.000 description 17

- 230000001133 acceleration Effects 0.000 description 15

- 239000000956 alloy Substances 0.000 description 15

- 150000002500 ions Chemical class 0.000 description 15

- 239000002356 single layer Substances 0.000 description 15

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 14

- 230000003287 optical effect Effects 0.000 description 13

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 12

- 230000006870 function Effects 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 229910045601 alloy Inorganic materials 0.000 description 11

- 229910052760 oxygen Inorganic materials 0.000 description 11

- 239000007789 gas Substances 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 238000000059 patterning Methods 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 8

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 8

- 230000008025 crystallization Effects 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 8

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 239000011574 phosphorus Substances 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- 229910052799 carbon Inorganic materials 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 238000005468 ion implantation Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 239000010453 quartz Substances 0.000 description 7

- 239000011347 resin Substances 0.000 description 7

- 229920005989 resin Polymers 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- 229910052804 chromium Inorganic materials 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 238000005224 laser annealing Methods 0.000 description 6

- 229910052759 nickel Inorganic materials 0.000 description 6

- 238000002161 passivation Methods 0.000 description 6

- 239000004033 plastic Substances 0.000 description 6

- 229920003023 plastic Polymers 0.000 description 6

- 238000004151 rapid thermal annealing Methods 0.000 description 6

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 6

- 239000003054 catalyst Substances 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- 238000005499 laser crystallization Methods 0.000 description 5

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 5

- 125000006850 spacer group Chemical group 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 229910052715 tantalum Inorganic materials 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 238000005984 hydrogenation reaction Methods 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 229910021419 crystalline silicon Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 238000001994 activation Methods 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000003078 antioxidant effect Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000005465 channeling Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 238000005247 gettering Methods 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 150000002894 organic compounds Chemical class 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 230000008646 thermal stress Effects 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- YLYPIBBGWLKELC-RMKNXTFCSA-N 2-[2-[(e)-2-[4-(dimethylamino)phenyl]ethenyl]-6-methylpyran-4-ylidene]propanedinitrile Chemical compound C1=CC(N(C)C)=CC=C1\C=C\C1=CC(=C(C#N)C#N)C=C(C)O1 YLYPIBBGWLKELC-RMKNXTFCSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910018575 Al—Ti Inorganic materials 0.000 description 1

- 229920002799 BoPET Polymers 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 239000005041 Mylar™ Substances 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- NRCMAYZCPIVABH-UHFFFAOYSA-N Quinacridone Chemical compound N1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3NC1=C2 NRCMAYZCPIVABH-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical group [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000007664 blowing Methods 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000010406 cathode material Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 239000007850 fluorescent dye Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 125000002080 perylenyl group Chemical group C1(=CC=C2C=CC=C3C4=CC=CC5=CC=CC(C1=C23)=C45)* 0.000 description 1

- CSHWQDPOILHKBI-UHFFFAOYSA-N peryrene Natural products C1=CC(C2=CC=CC=3C2=C2C=CC=3)=C3C2=CC=CC3=C1 CSHWQDPOILHKBI-UHFFFAOYSA-N 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000002985 plastic film Substances 0.000 description 1

- 229920006255 plastic film Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 230000026683 transduction Effects 0.000 description 1

- 238000010361 transduction Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

本発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装

置およびその作製方法に関する。特に、本発明は、液晶表示装置に代表される電気光学装

置およびその様な電気光学装置を部品として搭載した半導体装置およびその作製方法に関

する。なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しう

る装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

The present invention relates to a semiconductor device having a circuit formed of a thin film transistor (hereinafter referred to as TFT) and a manufacturing method thereof. In particular, the present invention relates to an electro-optical device typified by a liquid crystal display device, a semiconductor device in which such an electro-optical device is mounted as a component, and a manufacturing method thereof. Note that in this specification, a semiconductor device refers to all devices that can function by utilizing semiconductor characteristics, and an electro-optical device, a semiconductor circuit, and an electronic device are all semiconductor devices.

近年、絶縁表面を有する基板上に形成された薄膜(厚さ数〜数百nm程度)を用いてT

FTを構成し、このTFTで形成した大面積集積回路を有する半導体装置の開発が進んで

いる。その代表例として、アクティブマトリクス型の液晶表示装置や発光装置が知られて

いる。特に、結晶質珪素膜を活性領域にしたTFTは電界効果移動度が高いことから、い

ろいろな機能回路を形成することも可能である。

In recent years, a thin film (thickness of about several to several hundred nm) formed on a substrate having an insulating surface is used for T

Development of a semiconductor device having an FT and having a large-area integrated circuit formed of the TFT is in progress. As typical examples, an active matrix liquid crystal display device and a light emitting device are known. In particular, a TFT having a crystalline silicon film as an active region has high field effect mobility, and thus various functional circuits can be formed.

例えば、アクティブマトリクス型の液晶表示装置には、機能ブロックごとに画像表示を

行う画素回路や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バ

ッファ回路、サンプリング回路などの画素回路を制御するための駆動回路が一枚の基板上

に形成される。

For example, in an active matrix liquid crystal display device, a pixel circuit that displays an image for each functional block, or a pixel circuit such as a shift register circuit based on a CMOS circuit, a level shifter circuit, a buffer circuit, or a sampling circuit is controlled. Are formed on a single substrate.

また、前記TFTは、少なくとも半導体膜と、酸化珪素膜や酸化窒化珪素膜等からなる

絶縁膜と、各種金属材料等からなる配線とを有している。前記配線には、ソース配線やゲ

ート配線(ゲート電極を含む)などがある。これらの膜の厚さは数〜数百nm程度である

ため、薄膜と言うことができる。

The TFT includes at least a semiconductor film, an insulating film made of a silicon oxide film, a silicon oxynitride film, or the like, and wiring made of various metal materials. Examples of the wiring include a source wiring and a gate wiring (including a gate electrode). Since the thickness of these films is about several to several hundred nm, it can be said to be a thin film.

これらの薄膜は、CVD法(化学的気相成長法)やスパッタ法などの公知の成膜技術に

より形成される。しかしながら、前記薄膜には内部応力があることが知られている。なお

、内部応力には真性応力と、前記薄膜と基板との熱膨張係数の差に起因する熱応力とが含

まれている。

These thin films are formed by a known film forming technique such as CVD (chemical vapor deposition) or sputtering. However, it is known that the thin film has internal stress. The internal stress includes intrinsic stress and thermal stress resulting from the difference in thermal expansion coefficient between the thin film and the substrate.

熱応力は、基板の材質やプロセス温度、圧力等を考慮することにより、その影響を無視

することができるが、真性応力の発生メカニズムは必ずしも明確にはされておらず、むし

ろ膜の成長過程やその後の熱処理などによる相変化や組成変化が複雑に絡みあって発生し

ているものと考えられている。

The effect of thermal stress can be ignored by considering the substrate material, process temperature, pressure, etc., but the mechanism of generation of intrinsic stress is not necessarily clear, rather the film growth process and It is considered that the phase change and composition change due to subsequent heat treatment and the like are complicatedly entangled.

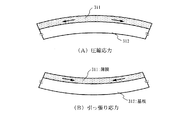

一般的に内部応力には、圧縮応力と引っ張り応力とがある。図5(A)に示すように、

薄膜311が伸張しようとするときには、基板312は押し縮められ薄膜311を外側に

して形成するので、これを圧縮応力と呼んでいる。一方、図5(B)に示すように、基板

312に対して薄膜311が収縮しようとするときには、基板312はそれを妨げる方向

に引っ張るため薄膜を内側にして変形し、これを引っ張り応力と呼んでいる。一般に、引

っ張り応力の値は+で示し、圧縮応力の値は―で示すことが多い。

Generally, the internal stress includes a compressive stress and a tensile stress. As shown in FIG.

When the

このような内部応力がトランジスタの電気的特性に与える影響について、例えば、「0

.13μmCMOSトランジスタ性能に対するエッチストップ窒化膜の応力の影響;応用

物理学会分科会シリコンテクノロジーNo.25 ULSIデバイス関連特集号(200

1)pp36―39」に記載されている。これによると、NMOSトランジスタはチャネ

ル形成領域が引っ張り応力を受けると移動度が向上し、PMOSトランジスタは圧縮応力

を受けると移動度が向上することが報告されている。

Regarding the influence of such internal stress on the electrical characteristics of the transistor, for example, “0

. Influence of stress of etch stop nitride film on 13 μm CMOS transistor performance; 25 Special Issue on ULSI Devices (200

1) pp 36-39 ". According to this, it has been reported that the mobility of the NMOS transistor is improved when the channel formation region is subjected to tensile stress, and the mobility is improved when the PMOS transistor is subjected to compressive stress.

上述のように、TFTの配線も薄膜により形成されている。そのため、前記配線も内部

応力を有し、該内部応力が強いとピーリングが発生する場合があった。

また、配線と同一材料で形成されるゲート電極は、絶縁膜を介して半導体膜上に形成され

ている。前記ゲート電極の内部応力は半導体膜にまで作用し、前記絶縁膜と前記半導体膜

との界面や、前記半導体膜に歪みを与えることによって、しきい値電圧や電界効果移動度

に代表される電気的特性に悪影響を及ぼす場合がある。

As described above, the TFT wiring is also formed of a thin film. Therefore, the wiring also has internal stress, and peeling may occur when the internal stress is strong.

Further, the gate electrode formed of the same material as the wiring is formed on the semiconductor film with an insulating film interposed therebetween. The internal stress of the gate electrode acts on the semiconductor film, and the electric field represented by the threshold voltage and the field effect mobility is applied to the interface between the insulating film and the semiconductor film and by distorting the semiconductor film. May adversely affect physical properties.

本発明はこのような問題点を解決するための技術であり、配線を有するアクティブマト

リクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、半導体

装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的としてい

る。

The present invention is a technique for solving such a problem, and in an electro-optical device and a semiconductor device typified by an active matrix liquid crystal display device having wiring, the operating characteristics and reliability of the semiconductor device are improved. The goal is to improve yield.

本発明は、TFTの配線に不純物元素を導入したり、不純物元素の導入と熱処理の両方

を行うことで、前記配線を所望の内部応力に制御することを可能とする。特に本発明を、

ゲート電極に適用することは極めて有効である。また、所望の領域のみに不純物元素を導

入したり、熱処理を行って所望の内部応力に制御することも可能とする。

The present invention makes it possible to control the wiring to a desired internal stress by introducing an impurity element into the TFT wiring or by performing both the impurity element introduction and heat treatment. In particular, the present invention

Application to the gate electrode is extremely effective. Further, an impurity element can be introduced only in a desired region, or heat treatment can be performed to control a desired internal stress.

例えば、本発明を適用して、nチャネル型TFTにおけるチャネル形成領域が受ける応

力を引っ張り応力とし、pチャネル型TFTにおけるチャネル形成領域が受ける応力を圧

縮応力とすることも可能である。また、nチャネル型TFTにおけるチャネル形成領域の

方が、pチャネル型TFTにおけるチャネル形成領域よりも相対的に引っ張り応力を強く

することも、pチャネル型TFTにおけるチャネル形成領域の方が、nチャネル型TFT

におけるチャネル形成領域よりも相対的に圧縮応力を強くすることも可能である。このよ

うにすることで、TFTの電気的特性を良好なものとし、さらに半導体装置の動作特性も

大幅に向上することが可能となる。

For example, by applying the present invention, a stress applied to a channel formation region in an n-channel TFT can be referred to as a tensile stress, and a stress applied to a channel formation region in a p-channel TFT can be referred to as a compressive stress. Further, the channel formation region in the n-channel TFT has a stronger tensile stress than the channel formation region in the p-channel TFT, and the channel formation region in the p-channel TFT has an n-channel type. TFT

It is also possible to make the compressive stress relatively stronger than the channel formation region. In this way, the electrical characteristics of the TFT can be improved, and the operating characteristics of the semiconductor device can be greatly improved.

不純物元素の導入の方法は、プラズマドーピング法、イオン注入法、イオンシャワード

ーピング法などにより行えばよい。このような不純物元素の導入の方法において、薄膜へ

打ち込まれるイオンのエネルギーは、薄膜を形成する元素の結合エネルギーと比較して非

常に大きい。そのため、前記薄膜へ打ち込まれるイオンは、前記半導体膜を形成する原子

を格子点から弾き飛ばして格子位置に存在するようになったり、打ち込まれるイオンや格

子点から弾き飛ばされた原子は格子間位置に存在するようになる。このようにして薄膜が

伸張するので、薄膜が圧縮応力を有している場合、前記圧縮応力は増大し、薄膜が引っ張

り応力を有している場合、前記引っ張り応力は緩和される。

As a method for introducing the impurity element, a plasma doping method, an ion implantation method, an ion shower doping method, or the like may be used. In such a method for introducing an impurity element, the energy of ions implanted into the thin film is very large compared to the binding energy of the elements forming the thin film. Therefore, the ions that are implanted into the thin film may be present at the lattice position by blowing off the atoms that form the semiconductor film from the lattice points, or the ions that are implanted or atoms that are ejected from the lattice points may be located at the interstitial positions. To come to exist. Since the thin film stretches in this way, the compressive stress increases when the thin film has compressive stress, and the tensile stress is relaxed when the thin film has tensile stress.

また、熱処理により、格子間位置に存在していた原子が格子位置に戻るので、原子の配

列の規則性は向上する。そのため、薄膜が収縮するので、薄膜が引っ張り応力を有してい

る場合、前記引っ張り応力は増大し、薄膜が圧縮応力を有している場合、前記圧縮応力は

緩和される。

In addition, since the atoms present at the interstitial positions return to the lattice positions by the heat treatment, the regularity of the arrangement of atoms is improved. Therefore, since the thin film contracts, the tensile stress increases when the thin film has tensile stress, and the compressive stress is relaxed when the thin film has compressive stress.

さらに、熱処理を行ってから不純物元素の導入を行うと、原子配列の規則性が向上した

膜中に加速されたイオンが打ち込まれるので、前記イオンは結晶格子の隙間に沿って衝突

を起すことなく深いところまで進入することが可能となる。(チャネリング)そのため、

内部応力を制御するための不純物元素の導入において、ドーズ量は少なくて済み、また、

低加速度の電圧で行うことが可能となる。

Further, when the impurity element is introduced after the heat treatment, accelerated ions are implanted into the film with improved regularity of atomic arrangement, so that the ions do not collide along the gap of the crystal lattice. It is possible to enter deeper. (Channeling) Therefore,

In the introduction of impurity elements to control internal stress, the dose amount is small, and

It is possible to carry out with a low acceleration voltage.

また、不純物元素を導入してから熱処理を行うと、薄膜中に薄膜を形成する原子よりも

多くの原子が導入されているので、格子間位置に存在していた原子が格子位置に戻る以上

に原子が存在することになる。そのため、不純物元素の導入を行わない場合よりも薄膜の

収縮が小さいので、引っ張り応力の増加量も小さくなる。つまり、後工程で熱処理を行う

ことが分かっている場合は、予め不純物元素を導入しておけば、内部応力の変化量を小さ

くすることが可能となる。

In addition, when the heat treatment is performed after introducing the impurity element, more atoms are introduced into the thin film than the atoms that form the thin film, so that the atoms that existed at the interstitial position return more than the lattice position. There will be atoms. Therefore, since the shrinkage of the thin film is smaller than when no impurity element is introduced, the increase in tensile stress is also small. That is, if it is known that heat treatment is performed in a later process, the amount of change in internal stress can be reduced by introducing an impurity element in advance.

このように、不純物元素の導入、もしくは不純物元素の導入および熱処理の両方を行う

ことで、所望の内部応力に制御することが可能となる。もちろん、不純物の導入や熱処理

は1回に限らず、複数回行ってもよい。本発明はこれらの特性を配線に適用し、該配線の

応力を制御することで、半導体装置の動作特性および信頼性を向上させるものである。特

に、TFTのゲート電極における内部応力が制御されることで、半導体膜が受ける応力を

制御することが可能となる。そのため、しきい値電圧や電界効果移動度に代表される電気

的特性を向上させることが可能となる。また、個々のゲート電極の応力を制御することも

可能であることから、電気的特性のばらつきを抑えることも可能となる。

As described above, it is possible to control to a desired internal stress by introducing the impurity element or both the impurity element introduction and the heat treatment. Of course, the introduction of impurities and the heat treatment are not limited to one time but may be performed a plurality of times. The present invention improves the operating characteristics and reliability of the semiconductor device by applying these characteristics to the wiring and controlling the stress of the wiring. In particular, the stress applied to the semiconductor film can be controlled by controlling the internal stress in the gate electrode of the TFT. Therefore, it is possible to improve electrical characteristics represented by threshold voltage and field effect mobility. In addition, since the stress of each gate electrode can be controlled, variation in electrical characteristics can be suppressed.

本明細書で開示する本発明の作製方法は、導電膜に不純物元素を導入して、前記導電膜

における内部応力を±1GPa以下とすることを特徴としている。

The manufacturing method of the present invention disclosed in this specification is characterized in that an impurity element is introduced into a conductive film so that an internal stress in the conductive film is ± 1 GPa or less.

また、本発明の他の作製方法は、導電膜に不純物元素を導入し、前記導電膜に熱処理を

行って、前記導電膜における内部応力を±1GPa以下とすることを特徴としている。

Another manufacturing method of the present invention is characterized in that an impurity element is introduced into a conductive film and heat treatment is performed on the conductive film so that an internal stress in the conductive film is ± 1 GPa or less.

また、本発明の他の作製方法は、導電膜に熱処理を行って、前記導電膜に不純物元素を

導入して、前記導電膜における内部応力を±1GPa以下とすることを特徴としている。

Another manufacturing method of the present invention is characterized in that a heat treatment is performed on the conductive film, an impurity element is introduced into the conductive film, and an internal stress in the conductive film is set to ± 1 GPa or less.

上記各作製方法において、前記不純物元素の導入の方法は、プラズマドーピング法、イ

オン注入法、イオンシャワードーピング法などにより行うことができる。

In each of the above manufacturing methods, the impurity element can be introduced by a plasma doping method, an ion implantation method, an ion shower doping method, or the like.

また、上記各作製方法において、前記不純物元素に特に限定はないが、n型を付与する

不純物元素、p型を付与する不純物元素、および希ガス元素から選ばれた一種または複数

種の元素であることが望ましい。n型を付与する不純物元素やp型を付与する不純物元素

はソース領域やドレイン領域を形成する上で欠かすことのできない不純物元素である。そ

のため、新たに他の不純物元素を用意する必要がなく経済的である。特に、ゲート電極に

不純物元素を導入する場合、ソース領域およびドレイン領域に前記不純物元素を導入する

工程と同時に導入することが可能であるため、工程数を増やすことなく導入できるため好

ましい。また、希ガス元素は不活性元素であるため、TFTの電気的特性に影響を及ぼさ

ないため好ましい。

In each of the above manufacturing methods, the impurity element is not particularly limited, but may be one or more elements selected from an impurity element imparting n-type, an impurity element imparting p-type, and a rare gas element. It is desirable. An impurity element imparting n-type conductivity or an impurity element imparting p-type conductivity is an impurity element indispensable for forming a source region and a drain region. Therefore, it is economical because it is not necessary to prepare another impurity element. In particular, when an impurity element is introduced into the gate electrode, the impurity element can be introduced at the same time as the step of introducing the impurity element into the source region and the drain region. Further, since the rare gas element is an inert element, it is preferable because it does not affect the electrical characteristics of the TFT.

また、不純物元素の導入量が多いほど、薄膜における内部応力が圧縮応力である場合は

、前記圧縮応力は増大し、薄膜における内部応力が引っ張り応力である場合は、前記引っ

張り応力が緩和したのち、圧縮応力を有するようになることもある。つまり、不純物元素

の導入量によって、薄膜における内部応力が圧縮応力となる場合もあれば、引っ張り応力

となる場合もある。

In addition, as the amount of the impurity element introduced is larger, the internal stress in the thin film is a compressive stress, and the compressive stress is increased.If the internal stress in the thin film is a tensile stress, the tensile stress is relaxed, It may have compressive stress. That is, depending on the amount of impurity element introduced, the internal stress in the thin film may be a compressive stress or a tensile stress.

また、上記各作製方法において、前記導電膜におけ内部応力の値は、±1GPa以下と

なることが望ましい。導電膜の内部応力が強いとピーリングを発生することが知られてお

り、一般にピーリングの発生を抑制することのできる目安は±1GPa以下となっている

。もちろん、ピーリングの発生は、導電膜が形成される条件等に大きく影響する。

In each of the above manufacturing methods, the value of internal stress in the conductive film is preferably ± 1 GPa or less. It is known that peeling is generated when the internal stress of the conductive film is strong, and generally a standard capable of suppressing the occurrence of peeling is ± 1 GPa or less. Of course, the occurrence of peeling greatly affects the conditions under which the conductive film is formed.

また、上記各作製方法において、前記導電膜は、単層に限らず、2層以上の積層構造で

あっても良い。

In each of the above manufacturing methods, the conductive film is not limited to a single layer and may have a stacked structure of two or more layers.

また、上記各作製方法において、前記熱処理は、RTA法、レーザアニール法、ファー

ネスアニール炉を用いた熱アニール法等を適用することができる。

In each of the above manufacturing methods, an RTA method, a laser annealing method, a thermal annealing method using a furnace annealing furnace, or the like can be applied as the heat treatment.

また、前記熱処理は、時間や温度によって、薄膜における内部応力の変化に大きく影響

する。熱処理の時間が長いほど、また熱処理の温度が高いほど、薄膜における内部応力が

引っ張り応力である場合は、前記引っ張り応力は増大し、薄膜における内部応力が圧縮応

力である場合は、前記圧縮応力が緩和したのち、引っ張り応力を有するようになることも

ある。つまり、熱処理の条件によって、薄膜における内部応力が圧縮応力となる場合もあ

れば、引っ張り応力となる場合もある。

The heat treatment greatly affects the change of internal stress in the thin film depending on time and temperature. The longer the heat treatment time and the higher the heat treatment temperature, the higher the tensile stress when the internal stress in the thin film is a tensile stress, and the lower the compressive stress when the internal stress in the thin film is a compressive stress. After relaxation, it may have tensile stress. That is, depending on the heat treatment conditions, the internal stress in the thin film may be a compressive stress or a tensile stress.

また、本発明の構成を以下に示す。 Moreover, the structure of this invention is shown below.

nチャネル型TFTを有する半導体装置であって、前記nチャネル型TFTは半導体膜

および導電膜を有し、前記半導体膜は引っ張り応力を受けており、前記導電膜は不純物元

素が導入されていることを特徴としている。

A semiconductor device having an n-channel TFT, wherein the n-channel TFT has a semiconductor film and a conductive film, the semiconductor film is subjected to tensile stress, and an impurity element is introduced into the conductive film It is characterized by.

pチャネル型TFTを有する半導体装置であって、前記pチャネル型TFTは半導体膜

および導電膜を有し、前記半導体膜は圧縮応力を受けており、前記導電膜は不純物元素が

導入されていることを特徴としている。

A semiconductor device having a p-channel TFT, wherein the p-channel TFT has a semiconductor film and a conductive film, the semiconductor film is subjected to compressive stress, and an impurity element is introduced into the conductive film It is characterized by.

nチャネル型TFTとpチャネル型TFTとを有する半導体装置であって、前記nチャ

ネル型TFTは、第1の半導体膜と、前記第1の半導体膜上に形成された第1の導電膜と

を有し、前記pチャネル型TFTは、第2の半導体膜と、前記第2の半導体膜上に形成さ

れた第2の導電膜とを有し、前記第1の半導体膜は引っ張り応力を受けており、前記第2

の半導体膜は圧縮応力を受けており、前記第1の導電膜および前記第2の導電膜は不純物

元素が導入されていることを特徴としている。

A semiconductor device having an n-channel TFT and a p-channel TFT, wherein the n-channel TFT includes a first semiconductor film and a first conductive film formed on the first semiconductor film. The p-channel TFT includes a second semiconductor film and a second conductive film formed on the second semiconductor film, and the first semiconductor film receives a tensile stress. The second

The semiconductor film is subjected to compressive stress, and an impurity element is introduced into the first conductive film and the second conductive film.

上記各構成において、前記不純物元素に特に限定はないが、n型を付与する不純物元素

、p型を付与する不純物元素、および希ガス元素から選ばれた一種または複数種の元素で

あることが望ましい。n型を付与する不純物元素やp型を付与する不純物元素はソース領

域やドレイン領域を形成する上で欠かすことのできない不純物元素である。そのため、新

たに他の不純物元素を用意する必要がなく経済的である。特に、ゲート電極に不純物元素

を導入する場合、ソース領域およびドレイン領域に前記不純物元素を導入する工程と同時

に導入することが可能であるため、工程数を増やすことなく導入できるため好ましい。ま

た、希ガス元素は不活性元素であるため、TFTの電気的特性に影響を及ぼさないため好

ましい。

In each of the above structures, the impurity element is not particularly limited, but is preferably one or more elements selected from an impurity element imparting n-type, an impurity element imparting p-type, and a rare gas element. . An impurity element imparting n-type conductivity or an impurity element imparting p-type conductivity is an impurity element indispensable for forming a source region and a drain region. Therefore, it is economical because it is not necessary to prepare another impurity element. In particular, when an impurity element is introduced into the gate electrode, the impurity element can be introduced at the same time as the step of introducing the impurity element into the source region and the drain region. Further, since the rare gas element is an inert element, it is preferable because it does not affect the electrical characteristics of the TFT.

また、上記各構成を備えたTFTを用いて液晶表示装置や発光装置に代表される半導体

装置を形成することを特徴としている。

In addition, a semiconductor device typified by a liquid crystal display device or a light-emitting device is formed using a TFT having the above-described structures.

本発明の構成を採用することにより、以下に示すような基本的有意性を得ることが出来

る。

(a)従来の作製プロセスに適合した、簡単な方法である。

(b)所望の内部応力を有する配線の形成を実現できる。そのため、他の膜における応力

をも低減することができる。また、配線のパターニング処理も良好に行うことができる。

(c)以上の利点を満たした上で、アクティブマトリクス型の液晶表示装置に代表される

半導体装置において、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を

実現することができる。

By adopting the configuration of the present invention, the following basic significance can be obtained.

(A) It is a simple method adapted to the conventional manufacturing process.

(B) The formation of wiring having a desired internal stress can be realized. Therefore, stress in other films can be reduced. In addition, the patterning process of the wiring can be performed well.

(C) In a semiconductor device typified by an active matrix liquid crystal display device, the operating characteristics and reliability of the semiconductor device can be improved and the yield can be improved while satisfying the above advantages.

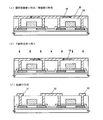

[実施の形態1]

本発明の実施形態について、図1を用いて説明する。本実施形態では、本発明をTFT

のゲート電極に適用した場合について説明する。

[Embodiment 1]

An embodiment of the present invention will be described with reference to FIG. In this embodiment, the present invention is applied to a TFT.

A case where the present invention is applied to the gate electrode will be described.

まず、基板10上に下地絶縁膜11を形成する。基板10としては、ガラス基板や石英

基板や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したも

のを用いても良い。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いて

もよい。

First, the

また、下地絶縁膜11としては、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの

絶縁膜から成る下地絶縁膜11を形成する。ここでは下地膜11として単層構造を用いた

例を示したが、前記絶縁膜を2層以上積層させた構造としても良い。なお、下地絶縁膜1

1を形成しなくてもよい。

As the

1 may not be formed.

次いで、下地絶縁膜11上に半導体膜12を形成する。半導体膜12は、非晶質構造を

有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)

により成膜した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルな

どの触媒を用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜12

の厚さは25〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料

に限定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成す

ると良い。

Next, the

Then, a known crystallization process (laser crystallization method, thermal crystallization method, or thermal crystallization method using a catalyst such as nickel) is performed to form a crystalline semiconductor film. This

Is formed with a thickness of 25 to 200 nm (preferably 30 to 100 nm). There is no limitation on the material of the semiconductor film, but it is preferably formed of silicon or a silicon germanium (SiGe) alloy.

次いで、半導体膜12上に絶縁膜13を形成する。絶縁膜13はプラズマCVD法、ス

パッタ法等を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積層構

造で形成する。なお、この絶縁膜13はゲート絶縁膜となる。

Next, an insulating

次いで、絶縁膜13上にスパッタ法、プラズマCVD法等を用い、膜厚250〜600

nmの導電膜14を形成する。ここでは、導電膜14として単層構造を用いた例を示した

が、前記導電膜を2層以上積層させた構造としても良い。

Next, a film thickness of 250 to 600 is formed on the insulating

A

しかしながら、CVD法により形成されると、前記導電膜14は引っ張り応力15が強

い場合がある。そのため、不純物元素の導入を行って、前記導電膜14における内部応力

を緩和させ、所望の内部応力にする。不純物元素の導入は、プラズマドーピング法、イオ

ン注入法、またはイオンシャワードーピング法などにより行えば良い。また、導入する不

純物元素は、n型を付与する不純物元素、p型を付与する不純物元素、および希ガス元素

から選ばれた一種または複数種の元素を用い、加速電圧30〜120keV、ドーズ量を

1×1012〜9×1016/cm2とし、ピークの濃度が1×1017〜1×1022/cm3と

なるように行う。

(図1(C))もちろん、最適な不純物元素の導入条件は、導電膜の状態や所望とする内

部応力によっても異なる。また、レジストからなるマスクを用いて、所望の領域のみに不

純物元素を導入すれば、前記所望の領域のみの内部応力を変化させることも可能である。

However, when the

(FIG. 1C) Of course, the optimum impurity element introduction conditions vary depending on the state of the conductive film and the desired internal stress. In addition, if an impurity element is introduced only into a desired region using a resist mask, the internal stress only in the desired region can be changed.

このようにして形成された導電膜が有する内部応力は所望の内部応力となり、半導体膜

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

The internal stress of the conductive film thus formed becomes a desired internal stress, and the stress exerted on the semiconductor film can be reduced. When a TFT is manufactured using such a conductive film, the electrical characteristics are improved, and the operating characteristics of the semiconductor device can be greatly improved.

[実施の形態2]

本発明の実施形態について、図1を用いて説明する。本実施形態では、不純物元素を導入

した後、熱処理を行うことにより内部応力を制御する場合について説明する。

[Embodiment 2]

An embodiment of the present invention will be described with reference to FIG. In the present embodiment, a case will be described in which the internal stress is controlled by performing a heat treatment after introducing an impurity element.

まず、実施の形態1にしたがって、不純物元素の導入まで行う。

First, the steps up to introduction of an impurity element are performed in accordance with

続いて熱処理を行って、前記導電膜14における内部応力が引っ張り応力であるなら増

大し、圧縮応力であるなら緩和する。熱処理は、ファーネスアニール炉を用いた熱アニー

ル法、レーザアニール法、RTA法等、公知の方法により行えばよい。例えば、ファーネ

スアニール炉を用いた熱アニール法を行うのであれば、温度500〜1000℃程度の窒

素雰囲気中に3分〜12時間程度曝せばよい。もちろん、最適な熱処理の条件は、導電膜

の状態や所望とする内部応力によっても異なる。また、長時間の熱処理は、TFTの作製

工程における半導体膜の結晶化や不純物元素の活性化と同時に行えば、新たに工程を増加

させることなく行うことができ、効率が良い。

Subsequently, heat treatment is performed to increase if the internal stress in the

また、レーザアニール法等により所望の領域のみに熱処理を行えば、前記所望の領域の

みの内部応力を変化させることも可能である。

Further, if heat treatment is performed only on a desired region by laser annealing or the like, it is possible to change the internal stress only on the desired region.

このようにして形成された導電膜が有する内部応力は所望の内部応力となり、半導体膜

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

The internal stress of the conductive film thus formed becomes a desired internal stress, and the stress exerted on the semiconductor film can be reduced. When a TFT is manufactured using such a conductive film, the electrical characteristics are improved, and the operating characteristics of the semiconductor device can be greatly improved.

[実施の形態3]

本発明の実施形態について、図2を用いて説明する。本実施形態では、不純物元素を導

入した後、熱処理を行うことにより内部応力を制御する場合について説明する。

[Embodiment 3]

An embodiment of the present invention will be described with reference to FIG. In the present embodiment, a case will be described in which the internal stress is controlled by performing a heat treatment after introducing an impurity element.

まず、実施の形態1にしたがって、絶縁膜13の形成まで行う。

First, according to the first embodiment, the formation up to the formation of the insulating

次いで、絶縁膜13上にスパッタ法、プラズマCVD法等を用い、膜厚250〜600

nmの導電膜17を形成する。ここでは、導電膜17として単層構造を用いた例を示した

が、前記導電膜を2層以上積層させた構造としても良い。

Next, a film thickness of 250 to 600 is formed on the insulating

A

しかしながら、スパッタ法により形成される前記導電膜17は圧縮応力15が強い場合

がある。そのため、熱処理を行って、前記導電膜17における内部応力を変化させる。熱

処理は、ファーネスアニール炉を用いる熱アニール法、RTA法、レーザアニール法等、

公知の方法を用いれば良い。(図2(B))

However, the

A known method may be used. (Fig. 2 (B))

続いて熱処理を行えば、前記導電膜14における内部応力が引っ張り応力であるなら増

大し、圧縮応力であるなら緩和する。(図2(C))熱処理は、ファーネスアニール炉を

用いた熱アニール法、レーザアニール法、RTA法等、公知の方法により行えばよい。例

えば、ファーネスアニール炉を用いた熱アニール法を行うのであれば、温度500〜10

00℃程度の窒素雰囲気中に3分〜12時間程度曝せばよい。もちろん、最適な熱処理の

条件は、導電膜の状態や所望とする内部応力によっても異なる。

If heat treatment is subsequently performed, the internal stress in the

What is necessary is just to expose for about 3 minutes-12 hours in nitrogen atmosphere at about 00 degreeC. Of course, the optimum heat treatment conditions vary depending on the state of the conductive film and the desired internal stress.

さらに、不純物元素の導入を行って、内部応力を変化させる。不純物元素の導入は、プ

ラズマドーピング法、イオン注入法、またはイオンシャワードーピング法などにより行え

ば良い。また、導入する不純物元素は、n型を付与する不純物元素、p型を付与する不純

物元素、および希ガス元素から選ばれた一種または複数種の元素を用い、加速電圧30〜

120keV、ドーズ量を1×1012〜9×1016/cm2とし、ピークの濃度が1×1

017〜1×1022/cm3となるように行う。(図2(D))また、熱処理を行った後に

不純物元素を導入することで、チャネリングにより、少ないドーズ量や低加速度の電圧で

内部応力を変化させることができる。

Further, an impurity element is introduced to change the internal stress. The introduction of the impurity element may be performed by a plasma doping method, an ion implantation method, an ion shower doping method, or the like. As the impurity element to be introduced, one or a plurality of elements selected from an impurity element imparting n-type, an impurity element imparting p-type, and a rare gas element are used, and an acceleration voltage of 30 to

120 keV, the dose is 1 × 10 12 to 9 × 10 16 / cm 2 , and the peak concentration is 1 × 1

0 17 to 1 × 10 22 / cm 3 . In addition, by introducing the impurity element after the heat treatment, the internal stress can be changed with a small dose and a low acceleration voltage by channeling.

このようにして形成された導電膜が有する内部応力は所望の内部応力となり、半導体膜

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

The internal stress of the conductive film thus formed becomes a desired internal stress, and the stress exerted on the semiconductor film can be reduced. When a TFT is manufactured using such a conductive film, the electrical characteristics are improved, and the operating characteristics of the semiconductor device can be greatly improved.

以上の構成でなる本発明について、以下に示す実施例によりさらに詳細な説明を行うこ

ととする。

The present invention configured as described above will be described in more detail with reference to the following examples.

以下に本発明の実施例を説明するが、特にこれらの実施例に限定されないことはもちろ

んである。

Examples of the present invention will be described below, but it is needless to say that the present invention is not limited to these examples.

本発明の有効性を示すために行った実験について説明する。なお、本実施例では導電膜

にW(タングステン)を、不純物元素としてArを用いたが、本発明は特にこれらに限定

されるものではない。

Experiments conducted to show the effectiveness of the present invention will be described. In this embodiment, W (tungsten) is used for the conductive film and Ar is used as the impurity element. However, the present invention is not particularly limited to these.

まず、合成石英基板10上にスパッタ法によりWを膜厚300nmで形成した。次いで

、CVD法により膜厚70nmの窒化酸化珪素膜(組成比Si=32.8%、O=63.

7%、H=3.5%)を形成した後、950℃で30分の熱処理を行った。そして、窒化

酸化珪素膜を除去した。W上に窒化酸化珪素膜を形成したのは、熱処理によってWがピー

リングを起すことを防止するためである。不純物元素の導入はイオンシャワードーピング

法により行い、その条件は表1に示す。また、不純物元素の導入は、熱処理前、熱処理後

、窒化酸化珪素膜を除去後の3つの条件において行った。その結果を図3に示す。ここで

は、内部応力の変化が引っ張り応力の増加であるときは+とし、圧縮応力の増加であると

きは―としている。

First, W was formed with a film thickness of 300 nm on the

7%, H = 3.5%), and heat treatment was performed at 950 ° C. for 30 minutes. Then, the silicon nitride oxide film was removed. The reason why the silicon nitride oxide film is formed on W is to prevent W from peeling by heat treatment. Impurity elements are introduced by ion shower doping, and the conditions are shown in Table 1. The introduction of the impurity element was performed under three conditions before the heat treatment, after the heat treatment, and after the silicon nitride oxide film was removed. The result is shown in FIG. Here, when the change in internal stress is an increase in tensile stress, it is +, and when it is an increase in compressive stress, it is-.

図3より、Arを導入すると、どの条件においても内部応力は圧縮応力の方向へ変化し

ていることが分かる。熱処理後に不純物元素を導入すると、熱処理によって結晶性が向上

するため、不純物元素が膜中深くまで導入しやすくなり、内部応力は圧縮応力の方向へ大

きく変化する。しかしながら、窒化酸化珪素膜を介してArを導入すると、Wにおける実

質的なArの導入量が少ないため、圧縮応力の方向への変化も小さい。

FIG. 3 shows that when Ar is introduced, the internal stress changes in the direction of compressive stress under any conditions. When the impurity element is introduced after the heat treatment, the crystallinity is improved by the heat treatment, so that the impurity element is easily introduced deep into the film, and the internal stress greatly changes in the direction of the compressive stress. However, when Ar is introduced through the silicon nitride oxide film, since the substantial amount of Ar introduced in W is small, the change in the direction of compressive stress is small.

続いて、図4に上記の実験における熱処理前後での内部応力の変化を示す。また、不純

物元素を導入せず、熱処理のみを行った場合についても内部応力の変化を調べた。図4よ

り、加速電圧30keVでは、不純物元素を導入しない場合よりも引っ張り応力の増加が

大きい。これは、不純物元素の導入によって圧縮応力が増大した分、熱処理による引っ張

り応力も増大したと考えられる。また、80keVでは引っ張り応力の方向への変化が小

さいことから、加速電圧が高いと、膜中に十分深くまで不純物元素が導入されるため、熱

処理による影響を受けにくいと考えられる。

Next, FIG. 4 shows changes in internal stress before and after the heat treatment in the above experiment. In addition, the change in internal stress was also examined when only the heat treatment was performed without introducing the impurity element. From FIG. 4, at the acceleration voltage of 30 keV, the increase in tensile stress is larger than when no impurity element is introduced. This is probably because the tensile stress due to the heat treatment was increased by the amount of the compressive stress increased by the introduction of the impurity element. Further, since the change in the direction of tensile stress is small at 80 keV, if the acceleration voltage is high, the impurity element is introduced deeply into the film, so that it is considered that it is hardly affected by the heat treatment.

このように、不純物元素の導入によって内部応力は圧縮応力が増加し、熱処理によって

内部応力は引っ張り応力が増加することが確認できた。つまり、不純物元素の導入、もし

くは不純物元素の導入および熱処理の両方を行うことにより、内部応力を制御することが

可能となり、所望の内部応力を有する導電膜を得ることができる。

Thus, it was confirmed that the internal stress increases the compressive stress by introducing the impurity element, and the internal stress increases the tensile stress by the heat treatment. That is, by introducing the impurity element, or both the introduction of the impurity element and the heat treatment, the internal stress can be controlled, and a conductive film having a desired internal stress can be obtained.

本実施例では、本発明をTFTのゲート電極に適用する場合について、図6を用いて説

明する。

In this embodiment, the case where the present invention is applied to a gate electrode of a TFT will be described with reference to FIG.

まず、基板10上に下地絶縁膜11を形成する。基板10としては、ガラス基板や石英

基板や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したも

のを用いてもよい。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いて

もよい。

First, the

また、下地絶縁膜11としては、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの

絶縁膜から成る下地絶縁膜11を形成する。ここでは下地絶縁膜11として単層構造を用

いる例を示しているが、前記絶縁膜の2層以上積層させた構造を用いても良い。なお、下

地絶縁膜を形成しなくてもよい。本実施例では、膜厚150nmの酸化窒化珪素膜11(

組成比Si=32%、O=27%、N=24%、H=17%)を形成する。

As the

(Composition ratio Si = 32%, O = 27%, N = 24%, H = 17%).

次いで、下地絶縁膜11上に半導体膜を形成した後エッチングを行って半導体層20、

21を得る。ここで、半導体層20はnチャネル型TFTを形成するものとし、半導体層

21はpチャネル型TFTを形成するものとする。半導体膜は、非晶質構造を有する半導

体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜

した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの触媒を

用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜12の厚さは2

5〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料に限定はな

いが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成すると良い。

本実施例では、レーザ光を照射して結晶構造を有する半導体膜を形成し、パターニングを

行って半導体層20、21を形成する。

Next, a semiconductor film is formed on the

Get 21. Here, it is assumed that the

The film is formed with a thickness of 5 to 200 nm (preferably 30 to 100 nm). There is no limitation on the material of the semiconductor film, but it is preferably formed of silicon or a silicon germanium (SiGe) alloy.

In this embodiment, a semiconductor film having a crystal structure is formed by irradiation with laser light, and patterning is performed to form the semiconductor layers 20 and 21.

そして、半導体層12を覆う絶縁膜22を形成する。絶縁膜22はプラズマCVD法ま

たはスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積

層構造で形成する。なお、この絶縁膜13はゲート絶縁膜となる。本実施例では、プラズ

マCVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%

、N=7%、H=2%)で形成する。

Then, an insulating

, N = 7%, H = 2%).

続いて、絶縁膜22上にスパッタ法、プラズマCVD法等を用い、膜厚250〜600

nmの導電膜23を形成する。ここでは、導電膜23として単層構造を用いる例を示した

が、前記導電膜23を2層以上積層させた構造としても良い。

また、導電膜としてはTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素

、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、

リン等の不純物元素を導入した多結晶珪素膜に代表される半導体膜を用いてもよい。また

、AgPdCu合金を用いてもよい。本実施例では、スパッタ法により、膜厚400nm

のTa膜を形成する。また、スパッタ法で形成される膜は圧縮応力を有することが多い。

Subsequently, a film thickness of 250 to 600 is formed on the insulating

A

The conductive film may be formed of an element selected from Ta, W, Ti, Mo, Al, Cu, Cr, and Nd, or an alloy material or a compound material containing the element as a main component. Also,

A semiconductor film typified by a polycrystalline silicon film into which an impurity element such as phosphorus is introduced may be used. Further, an AgPdCu alloy may be used. In this embodiment, the film thickness is 400 nm by sputtering.

A Ta film is formed. A film formed by sputtering often has a compressive stress.

次いで、フォトリソグラフィ法を用いたパターニング処理により、前記導電膜23にエ

ッチング処理を行って、第1の導電膜24および第2の導電膜25を形成する。(図6(

B))

Next, the

B))

そして、第1の不純物元素の導入を行って、半導体膜に不純物領域27を形成する。不

純物元素の導入は、プラズマドーピング法、イオン注入法、イオンシャワードーピング法

などにより行えばよい。本実施例ではn型を付与する不純物元素として、Asを用いる。

また、第1の不純物元素の導入では、第2の不純物元素の導入で導入される不純物元素の

量より、第1の不純物元素の導入での導入量を多くしておく。第1の不純物元素の導入を

行うことで、nチャネル型TFTとして機能するための不純物領域27が形成されるが、

第1の導電膜24および第2の導電膜25にもAsが導入され、圧縮応力15は増大する

。

Then, an impurity region 27 is formed in the semiconductor film by introducing the first impurity element. The introduction of the impurity element may be performed by a plasma doping method, an ion implantation method, an ion shower doping method, or the like. In this embodiment, As is used as the impurity element imparting n-type.

In addition, in the introduction of the first impurity element, the introduction amount in the introduction of the first impurity element is set larger than the amount of the impurity element introduced in the introduction of the second impurity element. By introducing the first impurity element, an impurity region 27 for functioning as an n-channel TFT is formed.

As is also introduced into the first

続いて、第2の不純物元素の導入を行って、半導体膜に不純物領域28を形成する。こ

のとき、nチャネル型TFTを形成する半導体層20はレジストから成るマスク26bに

よって覆われているため、不純物元素は導入されない。本実施例ではp型を付与する不純

物元素として、Bを用いる。第2の不純物元素の導入を行うことで、pチャネル型TFT

として機能するための不純物領域28が形成されるが、第2の導電膜25にもBが導入さ

れ、前記第2の導電膜25の圧縮応力15はさらに増大する。

Subsequently, a second impurity element is introduced to form an impurity region 28 in the semiconductor film. At this time, since the

Although the impurity region 28 for functioning as an impurity is formed, B is also introduced into the second

このようにして、不純物領域が形成され、また、前記第2の導電膜25には前記第1の

導電膜24よりも不純物元素が多く導入されている。

In this manner, impurity regions are formed, and more impurity elements are introduced into the second

続いて、熱処理を行うと、半導体膜の結晶性の回復および不純物元素の活性化が行われ

る。また、前記熱処理により、第1の導電膜24および第2の導電膜25における内部応

力も変化する。しかしながら、前記第1の導電膜24および前記第2の導電膜25に導入

された不純物元素の量が異なるため、熱処理後の内部応力も異なる。第1の導電膜24は

不純物元素の導入量が少ないため、熱処理によって、引っ張り応力の増加の方向16へ大

きく変化し、前記第1の導電膜24における内部応力は引っ張り応力となる。そのため、

nチャネル型TFTを形成する半導体膜が受ける応力は引っ張り応力となる。また、第2

の導電膜25は不純物元素の導入量が多いため、熱処理によって、内部応力はあまり変化

せず、前記第2の導電膜25における内部応力は圧縮応力となる。そのため、nチャネル

型TFTを形成する半導体膜が受ける応力は圧縮応力となる。

Subsequently, when heat treatment is performed, the crystallinity of the semiconductor film is restored and the impurity elements are activated. Further, the internal stress in the first

The stress received by the semiconductor film forming the n-channel TFT is tensile stress. Second

Since the

このようにして、導電膜の内部応力を制御して、nチャネル型TFTを形成する半導体

膜が受ける応力を引っ張り応力とし、pチャネル型TFTを形成する半導体膜が受ける応

力を圧縮応力とすることができる。そして、このような半導体膜を用いてTFTを作製す

ると、その電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

In this way, by controlling the internal stress of the conductive film, the stress received by the semiconductor film forming the n-channel TFT is defined as tensile stress, and the stress received by the semiconductor film forming the p-channel TFT is defined as compressive stress. Can do. When a TFT is manufactured using such a semiconductor film, the electrical characteristics are improved, and the operating characteristics of the semiconductor device can be greatly improved.

本実施例では、本発明をTFTの配線に適用した場合について、図7を用いて説明する

。

In this embodiment, the case where the present invention is applied to a wiring of a TFT will be described with reference to FIG.

基板上に下地絶縁膜を形成し、前記下地絶縁膜上に半導体層を形成し、前記半導体層を

覆って絶縁膜を形成し、前記半導体層上に前記絶縁膜を介して導電層を形成した後、該導

電層をマスクとして前記半導体膜に不純物元素を導入する。また、実施例2で示す方法に

従ってもよい。

A base insulating film is formed on a substrate, a semiconductor layer is formed on the base insulating film, an insulating film is formed to cover the semiconductor layer, and a conductive layer is formed on the semiconductor layer through the insulating film Thereafter, an impurity element is introduced into the semiconductor film using the conductive layer as a mask. Further, the method shown in Embodiment 2 may be followed.

続いて、無機絶縁膜材料または有機絶縁物材料から成る層間絶縁膜29を形成する。本

実施例では、層間絶縁膜29を単層構造としているが、2層以上の積層構造としても良い

。

Subsequently, an

そして、各不純物領域とそれぞれ電気的に接続する導電膜を形成する。導電膜は引っ張

り応力が強い場合がある。そのため、不純物元素を導入して、前記導電膜の内部応力を圧

縮応力の増加の方向へ変化させる。このような方法で内部応力を制御し、±1GPa以下

の内部応力を有する導電膜を形成することができ、パターニングを行って配線31〜33

を形成するときに、配線パターンがずれることを防ぐ。

Then, a conductive film electrically connected to each impurity region is formed. The conductive film may have a high tensile stress. Therefore, an impurity element is introduced to change the internal stress of the conductive film in the direction of increasing compressive stress. By controlling the internal stress by such a method, a conductive film having an internal stress of ± 1 GPa or less can be formed, and patterning is performed to form

The wiring pattern is prevented from shifting when forming the wiring.

また、このようにして形成された導電層が有する内部応力は±1GPa以下のものとな

り、層間絶縁膜や半導体膜に及ぼす応力を低減することが可能となる。

そして、このような導電層を用いてTFTを作製すると、その電気的特性は良好なものと

なり、半導体装置の動作特性も大幅に向上し得る。

In addition, the internal stress of the conductive layer formed in this way is ± 1 GPa or less, and the stress exerted on the interlayer insulating film and the semiconductor film can be reduced.

When a TFT is manufactured using such a conductive layer, its electrical characteristics are good, and the operating characteristics of the semiconductor device can be greatly improved.

本実施例では、実施例2とは異なる構造のTFTのゲート電極に本発明を適用した場合

について、図8を用いて説明する。

In this embodiment, the case where the present invention is applied to a gate electrode of a TFT having a structure different from that of Embodiment 2 will be described with reference to FIG.

まず、基板10上に導電膜35を形成する。基板10としては、ガラス基板や石英基板

や単結晶シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを

用いてもよい。また、処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよ

い。

First, the

また、導電膜35としては、スパッタ法、プラズマCVD法等を用い、膜厚250〜6

00nmの導電膜20を形成した後、フォトリソグラフィ法によりパターニング処理を行

って形成する。ここでは、導電膜35として単層構造を用いる例を示したが、前記導電膜

を2層以上積層させた構造としても良い。また、導電膜としてはTa、W、Ti、Mo、

Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若し

くは化合物材料で形成してもよい。

また、リン等の不純物元素を導入した多結晶珪素膜に代表される半導体膜を用いてもよい

。また、AgPdCu合金を用いてもよい。本実施例では、スパッタ法により、膜厚40

0nmのAl−Ti膜を形成する。

Further, as the

After the 00 nm

You may form with the element selected from Al, Cu, Cr, Nd, or the alloy material or compound material which has the said element as a main component.

Alternatively, a semiconductor film typified by a polycrystalline silicon film into which an impurity element such as phosphorus is introduced may be used. Further, an AgPdCu alloy may be used. In this embodiment, the film thickness is 40 by sputtering.

A 0-nm Al—Ti film is formed.

続いて、不純物元素を導入して、導電膜における内部応力を圧縮応力の増加の方向15

へ変化させる。これは後工程における熱処理によって、導電膜における内部応力が引っ張

り応力の増加の方向へ変化するので、前記内部応力を緩和させるために予め行っておく処

理である。

Subsequently, an impurity element is introduced, and the internal stress in the conductive film is reduced in the direction of increasing the

To change. Since the internal stress in the conductive film changes in the direction of increasing tensile stress due to the heat treatment in the subsequent process, this is a process performed in advance in order to relieve the internal stress.

そして、導電膜35を覆う絶縁膜36を形成する。絶縁膜36はプラズマCVD法また

はスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜の単層または積層

構造で形成する。なお、この絶縁膜36はゲート絶縁膜となる。本実施例では、プラズマ

CVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、

N=7%、H=2%)で形成する。

Then, an insulating

N = 7%, H = 2%).

次いで、絶縁膜36上に半導体膜37を形成する。半導体膜37は、非晶質構造を有す

る半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)によ

り成膜した後、公知の結晶化処理(レーザ結晶化法、熱結晶化法、またはニッケルなどの

触媒を用いた熱結晶化法等)を行って結晶質半導体膜を形成する。この半導体膜37の厚

さは25〜200nm(好ましくは30〜100nm)で形成する。半導体膜の材料に限

定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成すると

良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した後、

ニッケルを含む溶液を非晶質珪素膜上に保持させる。この非晶質珪素膜に脱水素化(50

0℃、1時間)を行った後、熱結晶化(550℃、4時間)を行う。熱処理によって半導

体膜37は結晶構造を有する半導体膜となる。また、予め不純物元素が導入してあるため

、導電膜35における内部応力の変化量は小さくてすむ。

Next, a

A solution containing nickel is held on the amorphous silicon film. This amorphous silicon film is dehydrogenated (50

After performing 0 ° C for 1 hour, thermal crystallization (550 ° C for 4 hours) is performed. By the heat treatment, the

このようにして形成された導電膜が有する内部応力は所望の内部応力となり、半導体膜

に及ぼす応力が低減できる。そして、このような導電膜を用いてTFTを作製すると、そ

の電気的特性は良好なものとなり、半導体装置の動作特性も大幅に向上し得る。

The internal stress of the conductive film thus formed becomes a desired internal stress, and the stress exerted on the semiconductor film can be reduced. When a TFT is manufactured using such a conductive film, the electrical characteristics are improved, and the operating characteristics of the semiconductor device can be greatly improved.

本実施例では、本発明を絶縁ゲート型電界効果トランジスタ(MOSFETまたはIG

FET)に適用してCMOS回路を構成した場合の例について図21〜図23を用いて説

明する。

In this embodiment, the present invention is applied to an insulated gate field effect transistor (MOSFET or IG).

An example in which a CMOS circuit is configured by application to an FET will be described with reference to FIGS.

まず、単結晶シリコン基板401を用意し、不純物元素を注入してP型ウェル402、

N型ウェル403を形成する。単結晶シリコン基板はP型であってもN型であっても良い

。この様な構成はいわゆるツインタブ構造であり、ウェル濃度は1×1018/cm3以下

(代表的には1×1016〜5×1017/cm3)で形成される。

First, a single

An N-

次に、公知のLOCOS法などにより選択酸化を行い、フィールド酸化膜404を形成

した後、熱酸化工程によってシリコン表面に30nm厚の酸化膜(後のゲート絶縁膜)4

05を形成する。(図21(A))

Next, after selective oxidation is performed by a known LOCOS method or the like to form a

05 is formed. (FIG. 21 (A))

次に、第1のゲート電極406および第2のゲート電極407を形成する。本実施例で

はゲート電極を構成する材料として導電性を有するシリコン膜を用いるが、他にもTa、

W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分と

する合金材料若しくは化合物材料を用いることができる。

Next, a

An element selected from W, Ti, Mo, Al, Cu, Cr, and Nd, or an alloy material or a compound material containing the element as a main component can be used.

前記第1のゲート電極406および前記第2のゲート電極407の形成後、pチャネル

型MOSFETとなる領域(図面向かって右側)をレジストマスク408で覆い、単結晶

シリコン基板401に対してn型を付与する不純物元素を導入する。(図21(B))不

純物元素の導入の方法は、レーザドーピング法、プラズマドーピング法、イオン注入法お

よびイオンシャワードーピング法のいずれかの方法を用い、濃度が5×1018〜 1×10

19/cm3となる様に導入する。本実施例では、n型を付与する不純物元素として、As

を用いる。こうして形成される不純物領域410、411の一部(チャネル形成領域と接

する側の端部)は後にnチャネル型MOSFETのLDD領域として機能する。

After the formation of the

It introduce | transduces so that it may become 19 / cm < 3 >. In this embodiment, As an impurity element imparting n-type conductivity is As.

Is used. Part of the

次に、nチャネル型MOSFETとなる領域をレジストマスク412で覆う。

そして、単結晶シリコン基板401に対してp型を付与する不純物元素を導入する。(図

21(C))本実施例では、n型を付与する不純物元素として、B(ボロン)を用いる。

このようにして、後にpチャネル型MOSFETのLDD領域として機能する不純物領域

414、415を形成する。

Next, a region to be an n-channel MOSFET is covered with a resist

Then, an impurity element imparting p-type conductivity is introduced into the single

In this manner,

図21(C)の状態が得られたら、次に酸化珪素膜(図示せず)を堆積してエッチバッ

クを行い、サイドウォール416、417を形成する。(図22(A)

)

When the state of FIG. 21C is obtained, a silicon oxide film (not shown) is deposited and etched back to

)

次に、再びpチャネル型MOSFETとなる領域をレジストマスク418で覆い、n型

を付与する不純物元素を 1×1020/cm3の濃度で導入する。こうしてソース領域41

9、ドレイン領域420が形成され、サイドウォール416の下にはLDD領域421が

形成される。(図22(B))

Next, a region to be a p-channel MOSFET is again covered with a resist

9, a

同様に、nチャネル型MOSFETとなる領域をレジストマスク422で覆い、p型を

付与する不純物元素を1×1020/cm3の濃度で導入する。こうしてドレイン領域42

3、ソース領域424が形成され、サイドウォール417の下にはLDD領域425が形

成される。(図22(C))さらに、レジストマスク422で覆ったまま、希ガス元素か

ら選ばれた一種または複数種の元素を導入する。このようにして、第2のゲート電極40

7に第1のゲート電極406よりも不純物元素を多量に導入する。これにより、前記第2

のゲート電極407の圧縮応力は前記第1のゲート電極406より強く、pチャネル型M

OSFETにおけるチャネル形成領域が受ける圧縮応力も、nチャネル型MOSFETに

おけるチャネル形成領域が受ける応力よりも強くなる。

Similarly, a region to be an n-channel MOSFET is covered with a resist

3. A

7, a larger amount of an impurity element is introduced than the

The compressive stress of the

The compressive stress received by the channel formation region in the OSFET is also stronger than the stress received by the channel formation region in the n-channel MOSFET.

図22(C)の状態が得られたら、第1の熱処理を行い、導入した不純物元素の活性化

を行う。

When the state of FIG. 22C is obtained, a first heat treatment is performed to activate the introduced impurity element.

続いて、チタン膜を成膜して第2の熱処理を行い、ソース領域、ドレイン領域およびゲ

ート電極の表面にチタンシリサイド層426を形成する。勿論、他の金属膜を用いた金属

シリサイドを形成することもできる。シリサイド層を形成した後、チタン膜は除去する。

Subsequently, a titanium film is formed and second heat treatment is performed to form a

前記第1の熱処理および前記第2の熱処理により、第1のゲート電極406および第2

のゲート電極407の内部応力も変化するが、第2のゲート電極407は第1のゲート電

極406より不純物元素の導入量が多いため、内部応力の変化は小さい。そのため、第2

のゲート電極407の圧縮応力は第1のゲート電極406より強く、pチャネル型MOS

FETにおけるチャネル形成領域が受ける圧縮応力も、nチャネル型MOSFETにおけ

るチャネル形成領域が受ける応力よりも強い。

By the first heat treatment and the second heat treatment, the

Although the internal stress of the

The compressive stress of the

The compressive stress received by the channel formation region in the FET is also stronger than the stress received by the channel formation region in the n-channel MOSFET.

次に、層間絶縁膜427を形成し、コンタクトホールを開けてソース電極428、42

9、ドレイン電極430を形成する。勿論、電極形成後に水素化を行うことも有効である

。

Next, an

9. A

以上の様な工程によって、図23に示す様なCMOS回路を得ることができる。ゲート

電極の内部応力が制御されたCMOS回路の電気的特性は、良好なものとなり、半導体装

置の動作特性も大幅に向上し得る。

Through the steps as described above, a CMOS circuit as shown in FIG. 23 can be obtained. The electrical characteristics of the CMOS circuit in which the internal stress of the gate electrode is controlled are good, and the operating characteristics of the semiconductor device can be greatly improved.

本実施例ではアクティブマトリクス基板の作製方法について図9〜図8を用いて説明す

る。本明細書ではCMOS回路、及び駆動回路と、画素TFT、保持容量とを有する画素

部を同一基板上に形成された基板を、便宜上アクティブマトリクス基板と呼ぶ。

In this embodiment, a method for manufacturing an active matrix substrate will be described with reference to FIGS. In this specification, a substrate in which a pixel portion having a CMOS circuit, a driver circuit, a pixel TFT, and a storage capacitor is formed over the same substrate is referred to as an active matrix substrate for convenience.

まず、本実施例ではコーニング社の#7059ガラスや#1737ガラスなどに代表さ

れるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる

基板501を用いる。なお、基板501としては、石英基板や単結晶シリコン基板、金属

基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施

例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。本実施例では

合成石英ガラス基板を用いる。

First, in this embodiment, a

次いで、石英基板501上に下部遮光膜を形成する。まず、酸化珪素膜、窒化珪素膜ま

たは酸化窒化珪素膜などの絶縁膜から成る膜厚10〜150nm(好ましくは50〜10

0nm)の下地膜を形成する。そして、本実施例の処理温度に耐え得るTa、W、Cr、

Mo等の導電性材料およびその積層構造により300nm程度の膜厚で下部遮光膜を形成す

る。前記下部遮光膜はゲート配線としての機能も有する。本実施例では膜厚75nmの結

晶質珪素膜を形成し、続いて膜厚150nmのWSix(x=2.0〜2.8)を成膜し

た後、不要な部分をエッチングして下部遮光膜503を形成する。なお、本実施例では、

下部遮光膜503として単層構造を用いるが、前記絶縁膜を2層以上積層させた構造を用

いても良い。

Next, a lower light shielding film is formed on the

0 nm) is formed. And Ta, W, Cr, which can withstand the processing temperature of this embodiment

A lower light-shielding film is formed with a film thickness of about 300 nm by a conductive material such as Mo and its laminated structure. The lower light shielding film also has a function as a gate wiring. In this embodiment, a crystalline silicon film having a thickness of 75 nm is formed, and then a WSix (x = 2.0 to 2.8) having a thickness of 150 nm is formed, and then unnecessary portions are etched to form a lower light shielding film. 503 is formed. In this example,

A single layer structure is used as the lower

そして基板501および下部遮光膜503上に酸化珪素膜、窒化珪素膜または酸化窒化

珪素膜などの絶縁膜から成る膜厚10〜650nm(好ましくは50〜600nm)の下

地膜504を形成する。本実施例では下地膜504として単層構造を用いるが、前記絶縁

膜を2層以上積層させた構造を用いても良い。本実施例では、下地膜504としては、プ

ラズマCVD法を用い、SiH4、NH3、及びN2Oを反応ガスとして成膜される膜厚5

80nmの酸化窒化珪素膜504(組成比Si=32%、O=27%、N=24%、H=

17%)を350℃にて形成する。

Then, a

80 nm silicon oxynitride film 504 (composition ratio Si = 32%, O = 27%, N = 24%, H =

17%) at 350 ° C.

次いで、下地膜504上に半導体膜505を形成する。半導体膜505は、非晶質構造

を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等

)により、25〜80nm(好ましくは30〜60nm)の厚さで形成する。半導体膜の

材料に限定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形

成すると良い。

Next, a

そして、ニッケルなどの触媒を用いた熱結晶化法を行って、半導体膜を結晶化する。ま

た、ニッケルなどの触媒を用いた熱結晶化法の他に、公知の結晶化処理(レーザ結晶化法

、熱結晶化法等)を組み合わせて行ってもよい。本実施例では、酢酸ニッケル溶液(重量

換算濃度10ppm、体積5ml)をスピンコートにより膜上全面に塗布して金属含有層

405を形成し、温度600度の窒素雰囲気中に12時間曝す。

Then, a thermal crystallization method using a catalyst such as nickel is performed to crystallize the semiconductor film. In addition to a thermal crystallization method using a catalyst such as nickel, a known crystallization treatment (laser crystallization method, thermal crystallization method, etc.) may be performed in combination. In this embodiment, a nickel acetate solution (weight-

また、レーザ結晶化法も適用する場合には、パルス発振型または連続発光型のエキシマ

レーザやYAGレーザ、YVO4レーザ等を用いることができる。これらのレーザを用い

る場合には、レーザ発振器から放射されたレーザビームを光学系で線状に集光し半導体膜

に照射する方法を用いると良い。結晶化の条件は実施者が適宣選択するものであるが、エ

キシマレーザを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度

を100〜800mJ/cm2(代表的には200〜700mJ/cm2)とする。また、YAGレーザ

を用いる場合にはその第2高調波を用いパルス発振周波数1〜300Hzとし、レーザー

エネルギー密度を300〜1000mJ/cm2(代表的には350〜800mJ/cm2)とすると良

い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザビームを

基板全面に渡って照射し、この時の線状レーザビームの重ね合わせ率(オーバーラップ率

)を50〜98%として行ってもよい。

In the case where a laser crystallization method is also applied, a pulse oscillation type or a continuous emission type excimer laser, a YAG laser, a YVO 4 laser, or the like can be used. In the case of using these lasers, it is preferable to use a method in which a laser beam emitted from a laser oscillator is linearly collected by an optical system and irradiated onto a semiconductor film. The crystallization conditions are appropriately selected by the practitioner. When an excimer laser is used, the pulse oscillation frequency is 300 Hz, and the laser energy density is 100 to 800 mJ / cm 2 (typically 200 to 700 mJ / cm 2). ). When a YAG laser is used, the second harmonic is used and the pulse oscillation frequency is 1 to 300 Hz, and the laser energy density is 300 to 1000 mJ / cm 2 (typically 350 to 800 mJ / cm 2 ). Then, a laser beam condensed linearly with a width of 100 to 1000 μm, for example 400 μm, is irradiated over the entire surface of the substrate, and the superposition ratio (overlap ratio) of the linear laser beam at this time is set to 50 to 98%. Also good.

続いて、活性領域となる半導体層から、結晶化を助長するために用いた金属元素を除去

または低減するために、ゲッタリングを行う。ゲッタリングについては特開平10−27

0363号公報に開示している方法を適用すればよい。本実施例では、マスクとして、膜

厚50nmの酸化珪素膜を形成し、パターニングを行って、所望の形状の酸化珪素膜50

6a〜506dを得る。そして、半導体膜に選択的に15族に属する元素(代表的にはP

(リン))を導入し、熱処理を行うことで、半導体層から金属元素を除去または半導体特

性に影響しない程度にまで低減することができる。このようにして作製した活性領域を有

するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、

良好な特性を達成することができる。

Subsequently, gettering is performed in order to remove or reduce the metal element used to promote crystallization from the semiconductor layer serving as the active region. Regarding gettering, JP-A-10-27.

The method disclosed in Japanese Patent No. 0363 may be applied. In this embodiment, a silicon oxide film having a thickness of 50 nm is formed as a mask and patterned to form a silicon oxide film 50 having a desired shape.

6a-506d are obtained. An element belonging to

By introducing (phosphorus)) and performing heat treatment, the metal element can be removed from the semiconductor layer or reduced to the extent that the semiconductor characteristics are not affected. A TFT having an active region manufactured in this manner has a low off-current value and good crystallinity, so that high field-effect mobility can be obtained.

Good properties can be achieved.

そして、結晶質半導体膜にエッチングを行って、半導体層507a〜510aを形成す

る。(図9(D))

Then, the crystalline semiconductor film is etched to form semiconductor layers 507a to 510a. (Figure 9 (D))

次に、マスク506a〜506dを除去し、新たに絶縁膜511を形成して半導体膜の

結晶性を向上させるために熱処理を行って、半導体層の上部を熱酸化させるのが望ましい

。本実施例では、減圧CVD装置で20nmの酸化珪素膜を成膜した後、ファーネスアニ

ール炉で熱処理を行う。この処理により、半導体層507a〜510aの上部は酸化され

る。そして、酸化珪素膜および半導体層の酸化した部分をエッチングすると、結晶性の向

上した半導体層507b〜510bが得られる。

Next, it is preferable to remove the masks 506a to 506d, form a new

半導体層507b〜510bを形成した後、TFTのしきい値を制御するために微量な

不純物元素(ボロンまたはリン)を導入してもよい。

After forming the semiconductor layers 507b to 510b, a trace amount of an impurity element (boron or phosphorus) may be introduced in order to control the threshold value of the TFT.

次いで、半導体層507b〜510bを覆う第1のゲート絶縁膜511を形成する。第

1のゲート絶縁膜511はプラズマCVD法またはスパッタ法を用い、厚さを20〜15

0nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により35

nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)

で形成した。もちろん、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪

素を含む絶縁膜を用いても良い。

Next, a first

The insulating film containing silicon is formed to have a thickness of 0 nm. In this embodiment, 35 is formed by plasma CVD.

Silicon oxynitride film with a thickness of nm (composition ratio Si = 32%, O = 59%, N = 7%, H = 2%)

Formed with. Needless to say, the gate insulating film is not limited to the silicon oxynitride film, and another insulating film containing silicon may be used.

また、酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Ortho

silicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波

(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。こ

のようにして作製される酸化珪素膜は、その後400〜500℃の熱アニールによりゲー

ト絶縁膜として良好な特性を得ることができる。

When a silicon oxide film is used, TEOS (Tetraethyl Ortho

It can be formed by mixing silicate) and O 2 , setting the reaction pressure to 40 Pa, the substrate temperature to 300 to 400 ° C., and discharging at a high frequency (13.56 MHz) power density of 0.5 to 0.8 W / cm 2 . The silicon oxide film thus manufactured can obtain good characteristics as a gate insulating film by thermal annealing at 400 to 500 ° C. thereafter.

そして、前記ゲート絶縁膜を部分的にエッチングして、保持容量の電極の一方となる半

導体層510aを露出させ、該半導体層510aに不純物元素を導入する。(図10(B

))このとき、他の領域にはレジスト513が形成されており、不純物元素は導入されな

い。本実施例では、不純物元素としてP(リン)を用い、加速電圧10keV、ドーズ量

5×1014/cm2として不純物元素を導入する。

Then, the gate insulating film is partially etched to expose the

)) At this time, a resist 513 is formed in another region, and no impurity element is introduced. In this embodiment, P (phosphorus) is used as the impurity element, and the impurity element is introduced at an acceleration voltage of 10 keV and a dose of 5 × 10 14 / cm 2 .

続いて、第2のゲート絶縁膜512を形成する。第2のゲート絶縁膜512はプラズマ

CVD法またはスパッタ法を用い、厚さを20〜150nmとして珪素を含む絶縁膜で形

成する。本実施例では、プラズマCVD法により50nmの厚さで酸化窒化珪素膜(組成

比Si=32%、O=59%、N=7%、H=2%)

で形成した。もちろん、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪

素を含む絶縁膜を用いても良い。

Subsequently, a second

Formed with. Needless to say, the gate insulating film is not limited to the silicon oxynitride film, and another insulating film containing silicon may be used.

そして、下部遮光膜と接続するコンタクトを形成した後、膜厚20〜100nmの第1

の導電膜515と、膜厚100〜400nmの第2の導電膜516aとを積層形成する。

本実施例では、膜厚30nmのTaN膜からなる第1の導電膜515と、膜厚370nm

のW膜からなる第2の導電膜516aを積層形成する。TaN膜はスパッタ法で形成し、

Taのターゲットを用い、窒素を含む雰囲気内でスパッタした。また、W膜は、Wのター

ゲットを用いたスパッタ法で形成する。その他に6フッ化タングステン(WF6)を用い

る熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するために

は低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。

Then, after forming a contact connected to the lower light shielding film, a first film having a thickness of 20 to 100 nm is formed.

The

In this embodiment, a first

A second

Sputtering was performed in a nitrogen-containing atmosphere using a Ta target. The W film is formed by sputtering using a W target. In addition, it can be formed by a thermal CVD method using tungsten hexafluoride (WF 6 ). In any case, in order to use as a gate electrode, it is necessary to reduce the resistance, and the resistivity of the W film is desirably 20 μΩcm or less.

なお、本実施例では、第1の導電膜515をTaN、第2の導電膜516aをWとして

いるが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから

選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成しても