JP5814554B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5814554B2 JP5814554B2 JP2011020848A JP2011020848A JP5814554B2 JP 5814554 B2 JP5814554 B2 JP 5814554B2 JP 2011020848 A JP2011020848 A JP 2011020848A JP 2011020848 A JP2011020848 A JP 2011020848A JP 5814554 B2 JP5814554 B2 JP 5814554B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- layer

- wiring layer

- chip

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

《1−1》第1比較例

先ず、本発明の実施の形態に係る半導体装置の製造方法の効果を説明するために用いる第1比較例の半導体装置の製造方法を説明する。図8は、第1比較例の半導体装置の製造方法によって製造されたダミーチップ部の断面構造、クォーツ板1内の圧縮応力、及び配線層41,42,43内の熱応力を示す図である。第1比較例の半導体装置の製造方法では、絶縁基板としてのクォーツ板1にSi層2を貼り合せることによって製造された貼り合せウェハであるSOQウェハ3に、半導体チップの本質的な機能を担う回路素子(又は集積回路)などを形成することによって、チップ形成領域(図7における領域125)に複数の半導体チップ部(図7における長方形の領域126及び127)を形成し、その上に多層配線構造4を形成する。

本発明の実施の形態に係る半導体装置の製造方法の効果を説明するために用いる第2比較例の半導体装置の製造方法を説明する。図9は、第2比較例の半導体装置の製造方法によって製造されたダミーチップ部の断面構造、クォーツ板1内の圧縮応力、及び配線層51,52,53内の熱応力を示す図である。第2比較例の半導体装置の製造方法では、先ず、絶縁基板としてのクォーツ板1にSi層2を貼り合せることによって製造された貼り合せウェハであるSOQウェハ3に、半導体チップの本質的な機能を担う回路素子(又は集積回路)などを形成することによって、チップ形成領域(図7における領域125)に複数の半導体チップ部(図7における長方形の領域126及び127)を形成し、その上に多層配線構造5を形成する。

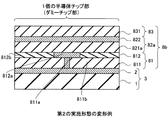

図10は、本発明の実施の形態に係る半導体装置の製造方法によって製造された半導体チップ部のうちのダミーチップ部の構造を概略的に示す図である。図10に示されるように、本発明の実施の形態に係る半導体装置の製造方法においては、絶縁基板としてのクォーツ板1にSi層2を貼り合せることによって製造された貼り合せウェハであるSOQウェハ3に、半導体チップの本質的な機能を担う回路素子(又は集積回路)などを形成することによって、チップ形成領域(図7における領域125)に複数の半導体チップ部(図7における長方形の領域126及び127)を形成し、その上に多層配線構造6を形成する。なお、複数の半導体チップ部は、個片化後に半導体チップとして使用される製品チップ部(図7における長方形の領域127)と、使用されないダミーチップ部(図7における126)とを含む。

図11は、本発明の第1の実施形態に係る半導体装置の製造方法によって製造された半導体チップ部のうちのダミーチップ部を概略的に示す縦断面図である。図11に示されるように、第1の実施形態に係る半導体装置の製造方法においては、クォーツ板1にSi層2を貼り合せることによって製造された貼り合せウェハであるSOQウェハ3に、半導体チップの本質的な機能を担う回路素子(又は集積回路)などを形成することによって、チップ形成領域(図7における領域125)に複数の半導体チップ部(図7における長方形の領域126及び127)を形成し、その上に多層配線構造7を形成する。なお、複数の半導体チップ部は、個片化後に半導体チップとして使用される製品チップ部(図7における長方形の領域127)と、使用されないダミーチップ部(図7における長方形のクロスハッチング領域126)とを含む。

図15は、第2の実施形態に係る半導体装置の製造方法によって製造された半導体チップ部のうちのダミーチップ部を概略的に示す縦断面図である。図15に示されるように、第2の実施形態に係る半導体装置の製造方法においては、クォーツ板1にSi層2を貼り合せることによって製造された貼り合せウェハであるSOQウェハ3に、半導体チップの本質的な機能を担う回路素子(又は集積回路)などを形成することによって、チップ形成領域(図7における領域125)に複数の半導体チップ部(図7における長方形の領域126及び127)を形成し、その上に多層配線構造8を形成する。なお、複数の半導体チップ部は、個片化後に半導体チップとして使用される製品チップ部(図7における長方形の領域127)と、使用されないダミーチップ部(図7における長方形のクロスハッチング領域126)とを含む。

図19は、第1及び第2の実施形態においてSOQウェハ上に形成された半導体チップである製品チップ部及びダミーチップ部の配置の他の例を概略的に示す平面図である。図19において、図7の構成と同一又は対応する構成には、同じ符号を付す。図7では、複数の半導体チップ部を含むチップ形成領域125の外周辺に接する部分を有する半導体チップ部(半導体チップ部の1辺、又は2辺、又は、角部がチップ形成領域125に接しているもの)をダミーチップ部(クロスハッチング部分)としている。しかし、図19に示されるように、チップ形成領域125の外周辺に一致する辺を有する半導体チップ部(半導体チップ部の1辺又は2辺がチップ形成領域125に接しているもの)である。このように、することによって、クラックの影響による不良品発生率が高まる可能性があるが、製品歩留りを向上させることができる。

3 SOQウェハ(半導体ウェハ)、

6,7,7a,7b,8,8a,8b 多層配線構造、

61,62,63,71,72,73,73a,74,74a,75 配線層、

125 チップ形成領域、 126 製品チップ部、 127 ダミーチップ部、

711,721,731,741,751 下部層、

712,722,732,742,752 上部層、

731a,812a,821a 貫通メタル配線(メタルプラグ)、

722a,812a メタル配線(製品チップ部と同じプロセスで製造されたもの)、

712,822,832 メタル層(ダミーチップ部の全面に形成されたもの)。

Claims (17)

- 絶縁基板にシリコン層を貼り合せることによって製造された貼り合せウェハに、複数の半導体チップ部を形成する工程と、

絶縁膜を含む下部層と該下部層上に備えられたメタル配線を含む上部層とを有する配線層を形成するプロセスを複数回行うことによって、前記複数の半導体チップ部上に、前記配線層が複数重ねられた多層配線構造を形成する工程と

を有し、

前記複数の半導体チップ部は、個片化後に半導体チップとして使用される製品チップ部と、使用されないダミーチップ部とを含み、

前記ダミーチップ部上に複数重ねられた前記配線層は、前記製品チップ部上における配線層と同じ形状を持つ第1の配線層と、該第1の配線層と異なる形状を持つ第2の配線層とを含み、

前記ダミーチップ部上に複数重ねられた前記配線層のいずれかにおける前記下部層は、貫通メタル配線を持たない絶縁膜であり、

前記絶縁基板は、クォーツ又は石英のいずれかを主成分とする基板を含む

ことを特徴とする半導体装置の製造方法。 - 絶縁基板にシリコン層を貼り合せることによって製造され、前記絶縁基板内に圧縮応力が発生している貼り合せウェハに、複数の半導体チップ部を形成する工程と、

絶縁膜を含む下部層と該下部層上に備えられたメタル配線を含む上部層とを有する配線層を形成するプロセスを複数回行うことによって、前記複数の半導体チップ部上に、前記配線層が複数重ねられた多層配線構造を形成する工程と

を有し、

前記複数の半導体チップ部は、個片化後に半導体チップとして使用される製品チップ部と、使用されないダミーチップ部とを含み、

前記ダミーチップ部上に複数重ねられた前記配線層は、前記製品チップ部上における配線層と同じ形状を持つ第1の配線層と、該第1の配線層と異なる形状を持つ第2の配線層とを含み、

前記ダミーチップ部上に複数重ねられた前記配線層のいずれかにおける前記下部層は、貫通メタル配線を持たない絶縁膜である

ことを特徴とする半導体装置の製造方法。 - 前記絶縁基板の熱膨張係数が、前記シリコン層の熱膨張係数と異なることを特徴とする請求項2に記載の半導体装置の製造方法。

- 前記ダミーチップ部上における第1の配線層は、前記貼り合せウェハに2番目に近い配線層であり、

前記ダミーチップ部上における第2の配線層は、前記貼り合せウェハに最も近い配線層である

ことを特徴とする請求項1から3までのいずれか1項に記載の半導体装置の製造方法。 - 前記ダミーチップ部上における第2の配線層の上部層は、前記ダミーチップ部上の全面を覆うように形成されたメタル層であることを特徴とする請求項1から4までのいずれか1項に記載の半導体装置の製造方法。

- 前記ダミーチップ部上における第1の配線層は、ホトリソグラフィ技術を用いる前記製品チップ部上における第1の配線層の形成プロセスと同じ形成プロセルによって形成されることを特徴とする請求項1から5までのいずれか1項に記載の半導体装置の製造方法。

- 前記貫通メタル配線を持たない前記絶縁膜である下部層は、前記貼り合せウェハに最も近い配線層の下部層を含むことを特徴とする請求項1から6までのいずれか1項に記載の半導体装置の製造方法。

- 前記貫通メタル配線を持たない前記絶縁膜である下部層は、前記貼り合せウェハに2番目に近い配線層の下部層を含むことを特徴とする請求項1から7までのいずれか1項に記載の半導体装置の製造方法。

- 前記ダミーチップ部上における第1の配線層は、前記貼り合せウェハに最も近い配線層であり、

前記ダミーチップ部上における第2の配線層は、前記貼り合せウェハに2番目に近い配線層である

ことを特徴とする請求項1から3までのいずれか1項に記載の半導体装置の製造方法。 - 前記ダミーチップ部上における第2の配線層の上部層は、前記ダミーチップ部上の全面を覆うように形成されたメタル層であることを特徴とする請求項1、2、3、及び9のいずれか1項に記載の半導体装置の製造方法。

- 前記ダミーチップ部上における第1の配線層は、ホトリソグラフィ技術を用いる前記製品チップ部上における第1の配線層の形成プロセスと同じ形成プロセルによって形成されることを特徴とする請求項1、2、3、9、及び10のいずれか1項に記載の半導体装置の製造方法。

- 前記貫通メタル配線を持たない前記絶縁膜である下部層は、前記貼り合せウェハから3番目に近い配線層の下部層を含むことを特徴とする請求項1、2、3、9、10、及び11のいずれか1項に記載の半導体装置の製造方法。

- 前記貫通メタル配線を持たない前記絶縁膜である下部層は、前記貼り合せウェハから2番目に近い配線層の下部層を含むことを特徴とする請求項1、2、3、9、10、11、及び12のいずれか1項に記載の半導体装置の製造方法。

- 前記複数重ねられた配線層は、3層以上の配線層であり、

前記貼り合せウェハ側から3番目以降の配線層の上部層は、前記ダミーチップ部上の全面を覆うように形成されたメタル層である

ことを特徴とする請求項1、2、3、9、10、11、12、及び13のいずれか1項に記載の半導体装置の製造方法。 - 前記ダミーチップ部は、前記複数の半導体チップ部を含むチップ形成領域の外周に接する部分を有する半導体チップ部であることを特徴とする請求項1から14までのいずれか1項に記載の半導体装置の製造方法。

- 前記ダミーチップ部は、前記複数の半導体チップ部を含むチップ形成領域の外周に一致する辺を有する半導体チップ部であることを特徴とする請求項1から14までのいずれか1項に記載の半導体装置の製造方法。

- 前記ダミーチップ部は、前記複数の半導体チップ部を含むチップ形成領域の外周に一致する辺を2つ有する半導体チップ部であることを特徴とする請求項1から14までのいずれか1項に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011020848A JP5814554B2 (ja) | 2011-02-02 | 2011-02-02 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011020848A JP5814554B2 (ja) | 2011-02-02 | 2011-02-02 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012160654A JP2012160654A (ja) | 2012-08-23 |

| JP5814554B2 true JP5814554B2 (ja) | 2015-11-17 |

Family

ID=46840926

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011020848A Expired - Fee Related JP5814554B2 (ja) | 2011-02-02 | 2011-02-02 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5814554B2 (ja) |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03266843A (ja) * | 1990-03-16 | 1991-11-27 | Fujitsu Ltd | アルミニゥム配線露光用マスク |

| JP3042480B2 (ja) * | 1997-12-03 | 2000-05-15 | 日本電気株式会社 | 半導体装置の製造方法及び製造装置 |

| JP4085836B2 (ja) * | 2003-02-19 | 2008-05-14 | 富士電機デバイステクノロジー株式会社 | 半導体装置の製造方法 |

| JP2006114680A (ja) * | 2004-10-14 | 2006-04-27 | Toshiba Corp | 半導体装置 |

| JP4837971B2 (ja) * | 2005-10-07 | 2011-12-14 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2007148333A (ja) * | 2005-10-24 | 2007-06-14 | Ricoh Co Ltd | 電極形成方法、アクティブマトリクス駆動回路、アクティブマトリクス駆動回路の製造方法、フラットパネルディスプレイ、フラットパネルディスプレイの製造方法、およびスクリーン版 |

| JP2009188008A (ja) * | 2008-02-04 | 2009-08-20 | Oki Semiconductor Co Ltd | 半導体装置の製造方法 |

| JP5446107B2 (ja) * | 2008-03-17 | 2014-03-19 | 三菱電機株式会社 | 素子ウェハおよび素子ウェハの製造方法 |

-

2011

- 2011-02-02 JP JP2011020848A patent/JP5814554B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012160654A (ja) | 2012-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI546910B (zh) | 晶片封裝體及其製造方法 | |

| US11450633B2 (en) | Package structure of semiconductor device with improved bonding between the substrates | |

| CN104716086B (zh) | 半导体装置的制造方法以及半导体装置 | |

| CN112885793B (zh) | 芯片封装结构及其制造方法 | |

| TWI441289B (zh) | 晶片封裝體 | |

| JP2011134893A (ja) | 半導体装置 | |

| CN106328626B (zh) | 半导体装置 | |

| US9093441B2 (en) | Semiconductor packages including semiconductor chips having protrusions and methods of fabricating the same | |

| JP6301763B2 (ja) | 半導体装置、および半導体装置の製造方法 | |

| TW201603209A (zh) | 半導體裝置及其製造方法 | |

| JP5446107B2 (ja) | 素子ウェハおよび素子ウェハの製造方法 | |

| JP5814554B2 (ja) | 半導体装置の製造方法 | |

| JP2009176833A (ja) | 半導体装置とその製造方法 | |

| CN101587873A (zh) | 降低应力的介电层结构及其制造方法 | |

| JP6470320B2 (ja) | 半導体装置 | |

| TWI549243B (zh) | 半導體結構及其製造方法 | |

| CN214428623U (zh) | 芯片封装结构 | |

| JP2005302985A (ja) | 半導体ウェーハおよび半導体チップ | |

| US11062984B2 (en) | Methods for forming semiconductor devices | |

| JP6211855B2 (ja) | 半導体装置 | |

| JP2004228479A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2006229186A (ja) | 半導体集積回路およびその製造方法 | |

| JP2013105986A (ja) | 半導体装置及びその製造方法 | |

| JP2009218503A (ja) | 半導体装置及びその製造方法 | |

| JP2014022485A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140131 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141209 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150205 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150901 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150918 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5814554 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |