JP5800264B2 - 光検出装置及び光電子増倍管にバイアスをかける方法 - Google Patents

光検出装置及び光電子増倍管にバイアスをかける方法 Download PDFInfo

- Publication number

- JP5800264B2 JP5800264B2 JP2012180265A JP2012180265A JP5800264B2 JP 5800264 B2 JP5800264 B2 JP 5800264B2 JP 2012180265 A JP2012180265 A JP 2012180265A JP 2012180265 A JP2012180265 A JP 2012180265A JP 5800264 B2 JP5800264 B2 JP 5800264B2

- Authority

- JP

- Japan

- Prior art keywords

- coupled

- voltage

- dynode

- voltage follower

- follower element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 19

- 239000003990 capacitor Substances 0.000 claims description 41

- 238000001514 detection method Methods 0.000 claims description 23

- 230000008859 change Effects 0.000 claims description 3

- 238000007689 inspection Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000001052 transient effect Effects 0.000 description 2

- 206010036618 Premenstrual syndrome Diseases 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01J—MEASUREMENT OF INTENSITY, VELOCITY, SPECTRAL CONTENT, POLARISATION, PHASE OR PULSE CHARACTERISTICS OF INFRARED, VISIBLE OR ULTRAVIOLET LIGHT; COLORIMETRY; RADIATION PYROMETRY

- G01J1/00—Photometry, e.g. photographic exposure meter

- G01J1/42—Photometry, e.g. photographic exposure meter using electric radiation detectors

- G01J1/44—Electric circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J43/00—Secondary-emission tubes; Electron-multiplier tubes

- H01J43/04—Electron multipliers

- H01J43/06—Electrode arrangements

- H01J43/18—Electrode arrangements using essentially more than one dynode

- H01J43/20—Dynodes consisting of sheet material, e.g. plane, bent

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01J—MEASUREMENT OF INTENSITY, VELOCITY, SPECTRAL CONTENT, POLARISATION, PHASE OR PULSE CHARACTERISTICS OF INFRARED, VISIBLE OR ULTRAVIOLET LIGHT; COLORIMETRY; RADIATION PYROMETRY

- G01J1/00—Photometry, e.g. photographic exposure meter

- G01J1/42—Photometry, e.g. photographic exposure meter using electric radiation detectors

- G01J1/44—Electric circuits

- G01J2001/4446—Type of detector

- G01J2001/4453—PMT

Description

・広範囲の入射光強度にわたり、又はそれに対応して広範囲のPMT電極電流にわたって電極電圧を一定に保つこと、

・速い負荷変動において一般に起きる高電圧(HV)電源の出力における電圧過渡事象を最小にすること、又はそれに対応して高電圧電源の電流変動を最小にすること、

・広いPMT利得範囲において、上記の特性を維持すること、

・PMTの寿命を長くするために、PMTを通して流れる最大電流を可能な最低レベルに制限すること、PMT電流制限値は、PMT利得、即ち印加される高電圧に依存してはならないこと、

・高電圧電源から引き出される電流を最小にすること、

のうちの少なくとも1つに適合させることができる。

PMTを低利得で動作させる場合には、各々のダイノードによって放出される電流を考慮する必要がある。フォトカソード及びフォトカソードの次のダイノードを通して流れる電流は、アノード及びその前のダイノードを通して流れる電流に対して、無視できない。

本光検出装置は、電流源によって設定される定負荷電流を高電圧電源に供給する。

光検出装置10は、フォトカソードC201、アノードA203、第1のダイノードDy1 202(1)、中間ダイノード202(2)−202(K−1)及び最終ダイノード202(K)といった複数の電極を含む、光電子増倍管200を含む。

電圧フォロワ素子228は、制御入力、出力及び付加的入力を有することができる。電圧フォロワ素子によって与えられる電圧は、電圧フォロワ素子の制御入力に与えられる電圧に従う。

光検出装置20は、バイアス回路302を有する。

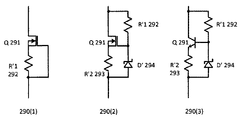

これらの電流源で、図1又は図2の電流源290を置き換えることができ、又は、これらを図5及び図6の電流源として用いることができる。

光検出装置50は、バイアス回路305を有する。

a.図1の電圧フォロワ素子VF1−VFK228は、(図5においては)MOSFETトランジスタQ1−QK211及びツェナーダイオードD1−DK226を含むように示されている。図5の各々の電圧フォロワ素子は、図3の電圧フォロワ素子228(1)の構成を有する。

b.図1の電流源290は、空乏型MOSFETトランジスタQCS210及び抵抗器Res225を含むように示されている。抵抗器Res225は、空乏型MOSFETトランジスタQCS210のゲートとソースとの間に接続される。

c.光検出装置50は、CR1−CR(K+1)で示されるK+1個のコンデンサを含む、コンデンサの第1の列を含む。第1の列は、電圧分割器に並列に結合され、ここで、j番目(jは1とK+1との間の範囲)のコンデンサCR(j)が電圧分割器のj番目の抵抗器R(j)に並列に接続される。R(K+1)及びCR(K+1)は、QKのゲート電極と負荷270との間に接続される。

d.光検出装置50は、Cdy1−CdyK222で示されるK個のコンデンサを含む、コンデンサの第2の列を含む。CdyKは、負荷と最終ダイノードDyKとの間に接続され、第2の列のうちの他の各々のコンデンサは、一対の連続するダイノード間に接続される。

光検出装置60は、バイアス回路306を有する。

a.図2の電圧フォロワ素子VF1−VFK228及びVFCは、(図6においては)MOSFETトランジスタQ1−QK及びQC211、ツェナーダイオードD1−DK及びDC226を含むように示されている。図6の各々の電圧フォロワ素子は、図3の電圧フォロワ素子228(1)の構成を有する。

b.図2の電流源290は、空乏型MOSFETトランジスタQcs291及び抵抗器Rcs292を含むように示されている。抵抗器Rcs292は、空乏型MOSFETトランジスタQcs291のゲートとソースとの間に接続される。

c.光検出装置60は、CR1−CR(K+1)で示されるK+1個のコンデンサを含む、コンデンサの第1の列を含む。第1の列は、電圧分割器に並列に結合され、ここで、j番目(jは1とK+1との間の範囲)のコンデンサCR(j)が電圧分割器のj番目の抵抗器R(j)に並列に接続される。R(K+1)及びCR(K+1)は、QKと負荷270との間に接続される。

d.光検出装置60は、Cdy1−CdyK222で示されるK個のコンデンサを含む、コンデンサの第2の列を含む。CdyKは、負荷と最終ダイノードDyKとの間に接続され、第2の列のうちの他の各々のコンデンサは、一対の連続するダイノードの間に接続される。

方法900は、互いに並列に実行することができる段階910及び920を含む。

段階910は、低い(例えば、10,000未満)、非常に低い、中間の、高い(例えば、百万を超える)又は非常に高いものとすることができる利得で光検出装置を動作させながら実施することができる。

200:光電子増倍管

201:フォトカソード

202(1):第1のダイノード

202(2)−202(K−1):中間ダイノード

202(K):最終ダイノード

203:アノード

211、291、312:MOSFETトランジスタ

222、223:コンデンサ

224、225、292、293:抵抗器

226、294、314、318:ツェナーダイオード

228:電圧フォロワ素子

230:高電圧電源

270:出力負荷(負荷素子)

272:負荷電流

290:電流源

301、302、305、306:バイアス回路

316:バイポーラトランジスタ

Claims (15)

- 光検出装置であって、

フォトカソード、アノード、第1のダイノード、中間ダイノード及び最終ダイノードを含む複数の電極を備えた光電子増倍管と、

電圧フォロワ素子列、電圧分割器及び電流源を備えたバイアス回路と

を備え、

前記電圧分割器は、高電圧電源の両端に結合され、

異なるダイノードは、前記電圧フォロワ素子列の異なる電圧フォロワ素子に結合され、

異なる電圧フォロワ素子の制御入力は、前記電圧分割器の異なる分岐点に結合され、

前記電流源は、前記電圧分割器と、前記電圧フォロワ素子列と、前記カソードと、前記高電圧電源の負極とに結合され、前記電流源は、前記電圧フォロワ素子列の電流を設定し、

前記アノードは、前記高電圧電源の正極に結合され且つ前記アノードの出力信号を受け取って前記光検出装置の出力信号に変換するように配置された、負荷素子に結合される、ことを特徴とする光検出装置。 - 前記電流源は、前記第1のダイノードと前記カソードとの間に結合されることを特徴とする、請求項1に記載の光検出装置。

- 前記電圧フォロワ素子列の1つの電圧フォロワ素子が、前記カソードと前記第1のダイノードとの間に結合され、前記電流源は、前記高電圧電源の負極と前記カソードとの間に結合されることを特徴とする、請求項1に記載の光検出装置。

- 前記電圧フォロワ素子は、トランジスタを含むことを特徴とする、請求項1に記載の光検出装置。

- 前記電圧フォロワ素子は、トランジスタ及びツェナーダイオードを含むことを特徴とする、請求項1に記載の光検出装置。

- 前記バイアス回路は、前記電圧分割器の抵抗器列の1つの抵抗器に並列に各々が結合された、コンデンサの第1の列をさらに備えることを特徴とする、請求項1に記載の光検出装置。

- コンデンサの第2の列を備え、前記コンデンサの第2の列の各々のコンデンサは一対のダイノード間に結合されることを特徴とする、請求項6に記載の光検出装置。

- 前記バイアス回路は、前記電圧分割器に並列に結合された第1のコンデンサをさらに備えることを特徴とする、請求項1に記載の光検出装置。

- コンデンサの列を備え、前記コンデンサの列の各々のコンデンサは一対のダイノード間に結合されることを特徴とする、請求項1に記載の光検出装置。

- 前記電流源は、前記電圧分割器に定電流を供給するように配置され、前記電圧フォロワ素子は、前記ダイノードによって放出される電流の変化にかかわらずに実質的に一定の電圧を出力するように配置されることを特徴とする、請求項1に記載の光検出装置。

- 10,000を超えない利得で動作するように配置されることを特徴とする、請求項1に記載の光検出装置。

- 光検出装置を動作させる方法であって、

前記光検出装置の光電子増倍管のカソードに当たった光を、前記光検出装置の出力信号に変換するステップと、

前記光検出装置のバイアス回路によって、前記光電子増倍管の複数のダイノードの各々のダイノードの電圧を前記ダイノードによって放出される電流の変化にかかわらずに実質的に一定に保つステップと

を含み、

前記複数のダイノードは、第1のダイノード、中間ダイノード及び最終ダイノードを含み、前記光電子増倍管は、アノード及びカソードをさらに備え、

前記バイアス回路は、電圧フォロワ素子列、電圧分割器及び電流源を備え、前記電圧分割器は、高電圧電源の両端に結合され、異なるダイノードは、前記電圧フォロワ素子列の異なる電圧フォロワ素子に結合され、異なる電圧フォロワ素子の制御入力は、前記電圧分割器の異なる分岐点に結合され、前記電流源は、前記電圧分割器と、前記電圧フォロワ素子列と、前記高電圧電源の負極と、前記カソードとに結合され、前記電流源は、前記電圧フォロワ素子列の電流を設定し、

前記アノードは、前記高電圧電源の正極に結合され且つ前記アノードの出力信号を受け取って前記光検出装置の出力信号に変換するように配置された、負荷素子に結合される、

ことを特徴とする方法。 - 前記電流源は、前記第1のダイノードと前記カソードとの間に結合されることを特徴とする、請求項12に記載の方法。

- 前記電圧フォロワ素子列の1つの電圧フォロワ素子が、前記カソードと前記第1のダイノードとの間に結合され、前記電流源は、前記高電圧電源の負極と前記カソードとの間に結合されることを特徴とする、請求項12に記載の方法。

- 10,000を超えない利得で前記光検出装置を動作させるステップを含むことを特徴とする、請求項12に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/440,843 | 2012-04-05 | ||

| US13/440,843 US8921756B2 (en) | 2012-04-05 | 2012-04-05 | Photo-detector device and a method for biasing a photomultiplier tube having a current source for setting a sequence of voltage follower elements |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013219001A JP2013219001A (ja) | 2013-10-24 |

| JP2013219001A5 JP2013219001A5 (ja) | 2015-08-06 |

| JP5800264B2 true JP5800264B2 (ja) | 2015-10-28 |

Family

ID=49291545

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012180265A Active JP5800264B2 (ja) | 2012-04-05 | 2012-07-30 | 光検出装置及び光電子増倍管にバイアスをかける方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8921756B2 (ja) |

| JP (1) | JP5800264B2 (ja) |

| CN (1) | CN103364082B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9941103B2 (en) * | 2013-10-19 | 2018-04-10 | Kla-Tencor Corporation | Bias-variant photomultiplier tube |

| CN104795304B (zh) * | 2014-01-16 | 2017-07-04 | 上海联影医疗科技有限公司 | 一种放大倍数可调式pmt分压电路 |

| US9671228B2 (en) * | 2014-10-21 | 2017-06-06 | Honeywell International Inc. | Floating current mirror for RLG discharge control |

| US9621972B2 (en) * | 2015-07-29 | 2017-04-11 | Rockley Photonics Limited | Burst-mode receiver |

| US9696439B2 (en) | 2015-08-10 | 2017-07-04 | Shanghai United Imaging Healthcare Co., Ltd. | Apparatus and method for PET detector |

| US10186406B2 (en) | 2016-03-29 | 2019-01-22 | KLA—Tencor Corporation | Multi-channel photomultiplier tube assembly |

| JP7176927B2 (ja) * | 2018-10-30 | 2022-11-22 | 浜松ホトニクス株式会社 | Cemアセンブリおよび電子増倍デバイス |

| JP7307849B2 (ja) | 2018-10-30 | 2023-07-12 | 浜松ホトニクス株式会社 | Cemアセンブリおよび電子増倍デバイス |

| CN110048705A (zh) * | 2019-05-23 | 2019-07-23 | 上海仁机仪器仪表有限公司 | 一种光电倍增管有源偏置电路 |

| US11361951B2 (en) | 2019-10-03 | 2022-06-14 | Kla Corporation | System and method for photomultiplier tube image correction |

| CN110828277A (zh) * | 2019-11-13 | 2020-02-21 | 上海裕达实业有限公司 | 集成式倍增检测装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4804891A (en) * | 1987-10-16 | 1989-02-14 | Gte Government Systems Corporation | Photomultiplier tube with gain control |

| US5453610A (en) * | 1994-05-20 | 1995-09-26 | Summit World Trade Corporation | Electronic gain control for photomultiplier used in gamma camera |

| US7005625B1 (en) * | 2004-12-06 | 2006-02-28 | Burle Technologies, Inc. | Low power stabilized voltage divider network |

| GB2456559B (en) * | 2008-01-18 | 2011-08-24 | Entpr Ltd | Drive and measurement circuit for a photomultiplier |

| JP5439483B2 (ja) * | 2008-07-03 | 2014-03-12 | サン−ゴバン セラミックス アンド プラスティクス,インコーポレイティド | 検出器用の能動分圧器 |

-

2012

- 2012-04-05 US US13/440,843 patent/US8921756B2/en active Active

- 2012-07-30 JP JP2012180265A patent/JP5800264B2/ja active Active

- 2012-08-14 CN CN201210289479.6A patent/CN103364082B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8921756B2 (en) | 2014-12-30 |

| CN103364082B (zh) | 2017-10-27 |

| JP2013219001A (ja) | 2013-10-24 |

| US20130264464A1 (en) | 2013-10-10 |

| CN103364082A (zh) | 2013-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5800264B2 (ja) | 光検出装置及び光電子増倍管にバイアスをかける方法 | |

| US6177665B1 (en) | High-speed logarithmic photo-detector | |

| AU758610B2 (en) | Light emission circuit | |

| US5880457A (en) | Voltage division circuit for a photomultiplier tube | |

| JP2013219001A5 (ja) | ||

| US7109463B2 (en) | Amplifier circuit with a switching device to provide a wide dynamic output range | |

| CN113189466B (zh) | 光电二极管的击穿电压测试 | |

| CN102595056A (zh) | 光电转换设备 | |

| TWI475679B (zh) | 半導體光電倍增元件 | |

| US8664580B2 (en) | Optical sensor and electronic equipment | |

| US7005625B1 (en) | Low power stabilized voltage divider network | |

| Barile et al. | A new VCII based low-power low-voltage front-end for silicon photomultipliers | |

| JP2016046945A (ja) | 電源安定化回路とそれを用いた光検出器 | |

| JP4183849B2 (ja) | 光計測装置 | |

| Heifets et al. | Fully active voltage divider for PMT photo-detector | |

| US20040164232A1 (en) | Photocurrent-to-binary signal conversion apparatus capable of suppressing waveform distortion | |

| US5440115A (en) | Zener diode biased electron multiplier with stable gain characteristic | |

| JP6417139B2 (ja) | 電子増倍管用の出力回路 | |

| KR101409882B1 (ko) | 실리콘 광전자 증배관 소자의 출력 이득제어 장치 및 방법 | |

| Petersen | CERN Summer Students Programme 2019-Final Report-Anode current simulations for the new Multi-Anode Photomultipliers in the LHCb RICH upgrade | |

| JP7440475B2 (ja) | 高電圧増幅回路、及び分析装置 | |

| JP4589041B2 (ja) | 光検出用回路及び光検出器 | |

| JP5164038B2 (ja) | 微弱光検出器 | |

| JP2005207955A (ja) | 光検出用回路及び光検出器 | |

| SU1595182A1 (ru) | Устройство дл регистрации световых импульсов |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150623 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150623 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20150623 |

|

| TRDD | Decision of grant or rejection written | ||

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20150729 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150803 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150814 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5800264 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |