JP5693450B2 - 複数のオプトエレクトロニクス素子の製造方法 - Google Patents

複数のオプトエレクトロニクス素子の製造方法 Download PDFInfo

- Publication number

- JP5693450B2 JP5693450B2 JP2011515089A JP2011515089A JP5693450B2 JP 5693450 B2 JP5693450 B2 JP 5693450B2 JP 2011515089 A JP2011515089 A JP 2011515089A JP 2011515089 A JP2011515089 A JP 2011515089A JP 5693450 B2 JP5693450 B2 JP 5693450B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor body

- semiconductor

- body support

- optoelectronic

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000005693 optoelectronics Effects 0.000 title claims description 58

- 238000004519 manufacturing process Methods 0.000 title claims description 32

- 238000000034 method Methods 0.000 title claims description 27

- 239000004065 semiconductor Substances 0.000 claims description 150

- 239000000463 material Substances 0.000 claims description 34

- 230000015572 biosynthetic process Effects 0.000 claims description 8

- 230000008569 process Effects 0.000 claims description 7

- 230000001681 protective effect Effects 0.000 claims description 7

- 230000005670 electromagnetic radiation Effects 0.000 claims description 5

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 claims description 2

- 230000000712 assembly Effects 0.000 claims 2

- 238000000429 assembly Methods 0.000 claims 2

- 238000012856 packing Methods 0.000 claims 1

- 230000005855 radiation Effects 0.000 description 14

- 235000012431 wafers Nutrition 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 13

- 239000000758 substrate Substances 0.000 description 10

- 238000000151 deposition Methods 0.000 description 9

- 230000008021 deposition Effects 0.000 description 7

- 238000004020 luminiscence type Methods 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 239000010408 film Substances 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- -1 nitride compound Chemical class 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 230000004888 barrier function Effects 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 238000002161 passivation Methods 0.000 description 3

- 230000000704 physical effect Effects 0.000 description 3

- 229910052594 sapphire Inorganic materials 0.000 description 3

- 239000010980 sapphire Substances 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission in a repetitive configuration, e.g. LED bars

- H01L27/156—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission in a repetitive configuration, e.g. LED bars two-dimensional arrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Led Devices (AREA)

- Led Device Packages (AREA)

Description

それぞれに1つのコンタクト構造が設けられており、且つ、電磁放射の形成に適した活性層を半導体層列内に備えている半導体ボディを第1の主面上に有している半導体ボディ支持体を準備するステップ、

半導体ボディを覆うことなく、コンタクト構造および半導体ボディ支持体の上の領域を少なくとも部分的に覆う平坦な充填構造を第1の主面上に形成するステップ。

Claims (11)

- 複数のオプトエレクトロニクス素子の製造方法において、

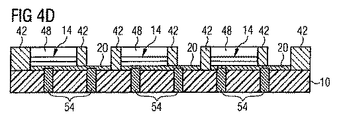

それぞれに1つのコンタクト構造(20)が設けられており、且つ、電磁放射の形成に適した活性層(16)を半導体層列(15)内に備えている複数の半導体ボディ(14)を第1の主面(12)上に有している半導体ボディ支持体(10)を準備するステップと、

前記半導体ボディ(14)を覆うことなく、前記コンタクト構造(20)および前記半導体ボディ支持体(10)の上の領域を少なくとも部分的に覆う平坦な充填構造(42,44)を前記第1の主面(12)上に形成するステップとを有し、

前記半導体ボディ支持体(10)を準備するステップは、複数の半導体ボディ(14)を、少なくとも1つのウェハ結合体から個別にまたは一緒に前記半導体ボディ支持体(10)に運ぶステップを含み、

前記平坦な充填構造を前記半導体ボディの少なくとも1つの側縁に対して距離を空けて配置し、前記半導体ボディの側方にミラー層を形成し、

少なくとも前記半導体ボディ(14)を覆う構造化されたレジスト層を形成し、構造化された前記レジスト層の外側に平坦な充填構造を形成し、構造化された前記レジスト層を除去することにより、平坦な充填構造を形成するステップを実施し、さらに、

前記平坦な充填構造は、前記半導体ボディ(14)の上面と同じ高さで平坦に形成されることを特徴とする、複数のオプトエレクトロニクス素子の製造方法。 - 複数の半導体ボディ(14)を複数のウェハ結合体から個別に前記半導体ボディ支持体(10)に運び、前記複数のウェハ結合体から運ばれた前記半導体ボディ(14)は、異なる波長の電磁放射の形成に適した活性層(16)を有する、請求項1記載の方法。

- 前記複数の半導体ボディ(14)を自由に選択可能なパターンで前記半導体ボディ支持体上に配置する、請求項1または2記載の方法。

- 前記複数の半導体ボディ(14)をウェハ結合体から補助支持体を用いて一緒に前記半導体ボディ支持体(10)に運ぶ、請求項1または2記載の方法。

- 前記半導体ボディ支持体(10)は半導体材料を含有し、該半導体材料内に保護ダイオードを形成し、該保護ダイオードを前記コンタクト構造の接続面に接続させる、請求項1から4までのいずれか1項記載の方法。

- 前記半導体ボディ支持体の上に保護ダイオードを配置し、該保護ダイオードを前記コンタクト構造の接続面に接続させる、請求項1から5までのいずれか1項記載の方法。

- 前記半導体ボディ支持体は接続面を有し、該接続面をスルーコンタクトを介して前記半導体ボディ支持体の前記第1の主面側とは反対側の面と接続し、オプトエレクトロニクス素子の表面実装を実施する、請求項1から6までのいずれか1項記載の方法。

- 前記平坦な充填構造はプラスチックを含む、請求項1から7までのいずれか1項記載の方法。

- 前記プラスチックはベンゾシクロブテンを含む、請求項8記載の方法。

- 1つまたは複数のオプトエレクトロニクス素子を前記半導体ボディ支持体の分割により個別化する、請求項1から9までのいずれか1項記載の方法。

- 複数のオプトエレクトロニクス素子を前記半導体ボディ支持体の分割により個別化し、複数のオプトエレクトロニクス素子から成る結合体を形成し、前記結合体の端部に位置するオプトエレクトロニクス素子をブリッジコンタクトを介して前記結合体の内側に位置するオプトエレクトロニクス素子と接触接続させる、請求項1から10までのいずれか1項記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008030815A DE102008030815A1 (de) | 2008-06-30 | 2008-06-30 | Verfahren zur Herstellung einer Vielzahl von optoelektronischen Bauelementen |

| DE102008030815.3 | 2008-06-30 | ||

| PCT/DE2009/000857 WO2010000224A2 (de) | 2008-06-30 | 2009-06-18 | Verfahren zur herstellung einer vielzahl von optoelektronischen bauelementen |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011526418A JP2011526418A (ja) | 2011-10-06 |

| JP2011526418A5 JP2011526418A5 (ja) | 2012-08-02 |

| JP5693450B2 true JP5693450B2 (ja) | 2015-04-01 |

Family

ID=41228784

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011515089A Expired - Fee Related JP5693450B2 (ja) | 2008-06-30 | 2009-06-18 | 複数のオプトエレクトロニクス素子の製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8431422B2 (ja) |

| EP (1) | EP2294614B1 (ja) |

| JP (1) | JP5693450B2 (ja) |

| KR (1) | KR101587299B1 (ja) |

| CN (1) | CN101983428B (ja) |

| DE (1) | DE102008030815A1 (ja) |

| WO (1) | WO2010000224A2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8816383B2 (en) * | 2012-07-06 | 2014-08-26 | Invensas Corporation | High performance light emitting diode with vias |

| DE102012217776A1 (de) | 2012-09-28 | 2014-06-12 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Bauelements |

| DE102013107862A1 (de) * | 2013-07-23 | 2015-01-29 | Osram Opto Semiconductors Gmbh | Oberflächenmontierbares optoelektronisches Halbleiterbauteil und Verfahren zur Herstellung zumindest eines oberflächenmontierbaren optoelektronischen Halbleiterbauteils |

| DE102014114188B4 (de) * | 2014-09-30 | 2022-01-20 | Osram Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils |

| DE102015103835A1 (de) * | 2015-03-16 | 2016-09-22 | Osram Opto Semiconductors Gmbh | Lichtemittierendes Bauelement und Verfahren zur Herstellung eines lichtemittierenden Bauelements |

| JP6217711B2 (ja) | 2015-08-21 | 2017-10-25 | 日亜化学工業株式会社 | 発光装置の製造方法 |

| TWI688121B (zh) | 2018-08-24 | 2020-03-11 | 隆達電子股份有限公司 | 發光二極體結構 |

| US11038088B2 (en) | 2019-10-14 | 2021-06-15 | Lextar Electronics Corporation | Light emitting diode package |

| CN111883552B (zh) * | 2020-08-04 | 2023-09-05 | 厦门乾照光电股份有限公司 | 一种集成式led芯片模组及其制作、测试、切割方法 |

| CN118472152B (zh) * | 2024-07-12 | 2024-09-17 | 诺视科技(浙江)有限公司 | 集成反射穹顶的微显示器件及其制备方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5104824A (en) * | 1990-11-06 | 1992-04-14 | Bell Communications Research, Inc. | Selective area regrowth for surface-emitting lasers and other sharp features |

| JPH11177138A (ja) * | 1997-12-11 | 1999-07-02 | Stanley Electric Co Ltd | 面実装型装置およびこれを用いた発光装置または受光装置 |

| JP3829594B2 (ja) * | 2000-06-30 | 2006-10-04 | セイコーエプソン株式会社 | 素子実装方法と光伝送装置 |

| US6432752B1 (en) * | 2000-08-17 | 2002-08-13 | Micron Technology, Inc. | Stereolithographic methods for fabricating hermetic semiconductor device packages and semiconductor devices including stereolithographically fabricated hermetic packages |

| TW473951B (en) * | 2001-01-17 | 2002-01-21 | Siliconware Precision Industries Co Ltd | Non-leaded quad flat image sensor package |

| DE10128271C1 (de) * | 2001-06-12 | 2002-11-28 | Liz Electronics Corp | Verfahren zur Herstellung von Dioden |

| DE10222609B4 (de) * | 2002-04-15 | 2008-07-10 | Schott Ag | Verfahren zur Herstellung strukturierter Schichten auf Substraten und verfahrensgemäß beschichtetes Substrat |

| DE10235332A1 (de) * | 2002-08-01 | 2004-02-19 | Infineon Technologies Ag | Mehrlagiger Schaltungsträger und Herstellung desselben |

| DE10245930A1 (de) * | 2002-09-30 | 2004-04-08 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Bauelement-Modul |

| KR101025234B1 (ko) * | 2003-02-28 | 2011-04-01 | 오스람 옵토 세미컨덕터스 게엠베하 | 구조화 방식으로 금속화된 하우징 바디를 갖는 광전자소자,상기 광전자소자의 제조 방법 및 플라스틱을 포함하는하우징 바디를 구조화 방식으로 금속화하기 위한 방법 |

| JP2004304161A (ja) * | 2003-03-14 | 2004-10-28 | Sony Corp | 発光素子、発光装置、画像表示装置、発光素子の製造方法及び画像表示装置の製造方法 |

| US20070126016A1 (en) * | 2005-05-12 | 2007-06-07 | Epistar Corporation | Light emitting device and manufacture method thereof |

| US7084496B2 (en) * | 2004-01-14 | 2006-08-01 | International Business Machines Corporation | Method and apparatus for providing optoelectronic communication with an electronic device |

| KR100880812B1 (ko) * | 2004-03-29 | 2009-01-30 | 아티큘레이티드 테크놀러지스 엘엘씨 | 롤-투-롤 제조된 광 시트 및 캡슐화된 반도체 회로디바이스들 |

| DE102004021233A1 (de) | 2004-04-30 | 2005-12-01 | Osram Opto Semiconductors Gmbh | Leuchtdiodenanordnung |

| JP2006108204A (ja) * | 2004-10-01 | 2006-04-20 | Renesas Technology Corp | 半導体モジュール及び電子装置 |

| DE102006032047A1 (de) * | 2006-07-10 | 2008-01-24 | Schott Ag | Verfahren zur Herstellung optoelektronischer Bauelemente und damit hergestellte Erzeugnisse |

| JP2008027999A (ja) * | 2006-07-19 | 2008-02-07 | Matsushita Electric Ind Co Ltd | 発光装置の製造方法および発光装置 |

| DE102007004303A1 (de) | 2006-08-04 | 2008-02-07 | Osram Opto Semiconductors Gmbh | Dünnfilm-Halbleiterbauelement und Bauelement-Verbund |

| DE102006051746A1 (de) * | 2006-09-29 | 2008-04-03 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement mit einer Lumineszenzkonversionsschicht |

| WO2008086090A1 (en) * | 2007-01-05 | 2008-07-17 | University Of Washington | Self-assembled heterogeneous integrated optical analysis system |

| DE102007008524A1 (de) * | 2007-02-21 | 2008-08-28 | Osram Opto Semiconductors Gmbh | Strahlung emittierender Chip mit mindestens einem Halbleiterkörper |

| DE102007030129A1 (de) * | 2007-06-29 | 2009-01-02 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung einer Mehrzahl optoelektronischer Bauelemente und optoelektronisches Bauelement |

| DE102007043877A1 (de) * | 2007-06-29 | 2009-01-08 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung von optoelektronischen Bauelementen und optoelektronisches Bauelement |

| DE102008013030A1 (de) | 2007-12-14 | 2009-06-25 | Osram Opto Semiconductors Gmbh | Strahlungsemittierende Vorrichtung |

| DE102008014094A1 (de) | 2008-03-13 | 2009-09-17 | Osram Opto Semiconductors Gmbh | Strahlungsemittierende Vorrichtung und Verfahren zur Herstellung einer strahlungsemittierenden Vorrichtung |

-

2008

- 2008-06-30 DE DE102008030815A patent/DE102008030815A1/de not_active Withdrawn

-

2009

- 2009-06-18 WO PCT/DE2009/000857 patent/WO2010000224A2/de active Application Filing

- 2009-06-18 JP JP2011515089A patent/JP5693450B2/ja not_active Expired - Fee Related

- 2009-06-18 EP EP09771994.2A patent/EP2294614B1/de not_active Not-in-force

- 2009-06-18 US US12/922,397 patent/US8431422B2/en active Active

- 2009-06-18 KR KR1020107020383A patent/KR101587299B1/ko active IP Right Grant

- 2009-06-18 CN CN2009801119833A patent/CN101983428B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011526418A (ja) | 2011-10-06 |

| KR20110025164A (ko) | 2011-03-09 |

| EP2294614B1 (de) | 2017-11-22 |

| WO2010000224A2 (de) | 2010-01-07 |

| US20110086447A1 (en) | 2011-04-14 |

| CN101983428B (zh) | 2013-06-12 |

| EP2294614A2 (de) | 2011-03-16 |

| CN101983428A (zh) | 2011-03-02 |

| WO2010000224A3 (de) | 2010-03-04 |

| US8431422B2 (en) | 2013-04-30 |

| DE102008030815A1 (de) | 2009-12-31 |

| KR101587299B1 (ko) | 2016-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5693450B2 (ja) | 複数のオプトエレクトロニクス素子の製造方法 | |

| JP7136834B2 (ja) | 小型光源を有する波長変換発光デバイス | |

| US10043955B2 (en) | Light emitting diode chip having wavelength converting layer and method of fabricating the same, and package having the light emitting diode chip and method of fabricating the same | |

| KR101460392B1 (ko) | 복수 개의 광전 소자들의 제조 방법 및 광전 소자 | |

| US7456035B2 (en) | Flip chip light emitting diode devices having thinned or removed substrates | |

| TWI612693B (zh) | 發光裝置及其製造方法 | |

| CN101681964B (zh) | 用于制造光电子器件的方法以及光电子器件 | |

| US7842547B2 (en) | Laser lift-off of sapphire from a nitride flip-chip | |

| US9324926B2 (en) | Wavelength converted light emitting device | |

| US9666771B2 (en) | Method of forming a wavelength converted light emitting device | |

| JP2016518033A (ja) | 光学エレメントとリフレクタを用いた発光デバイス | |

| KR100823089B1 (ko) | 파장변환 물질층을 갖는 발광 다이오드 제조방법 | |

| KR20160010206A (ko) | 웨이퍼 레벨 패키지 공정을 이용한 발광 소자 제조 방법 및 그것에 의해 제조된 발광 소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120618 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120618 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130918 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130924 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20131203 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20131210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140407 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140626 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140703 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150203 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5693450 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |