JP5556199B2 - 固体撮像素子及び撮像機器 - Google Patents

固体撮像素子及び撮像機器 Download PDFInfo

- Publication number

- JP5556199B2 JP5556199B2 JP2010019056A JP2010019056A JP5556199B2 JP 5556199 B2 JP5556199 B2 JP 5556199B2 JP 2010019056 A JP2010019056 A JP 2010019056A JP 2010019056 A JP2010019056 A JP 2010019056A JP 5556199 B2 JP5556199 B2 JP 5556199B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- pixel region

- signal

- row

- pixels

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000003384 imaging method Methods 0.000 title claims description 48

- 230000003287 optical effect Effects 0.000 claims description 56

- 238000006243 chemical reaction Methods 0.000 claims description 40

- 238000009792 diffusion process Methods 0.000 claims description 12

- 239000011159 matrix material Substances 0.000 claims description 6

- 238000012546 transfer Methods 0.000 description 22

- 238000012545 processing Methods 0.000 description 21

- 230000003321 amplification Effects 0.000 description 13

- 238000003199 nucleic acid amplification method Methods 0.000 description 13

- 238000010586 diagram Methods 0.000 description 7

- 238000000034 method Methods 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/63—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current

- H04N25/633—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current by using optical black pixels

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

Description

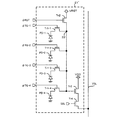

また、請求項4に記載の発明は、請求項1又は請求項2に記載の固体撮像素子において、前記ダミー画素領域の画素群は、前記列信号線への信号の出力経路が遮断されるとともに共通接続される前記フローティングディフージョン部単位で電位が固定されており、前記ダミー画素領域の画素群に対応する前記行走査部は、一括して非動作状態に固定されているようにした。

1.撮像機器の構成

2.固体撮像素子の構成

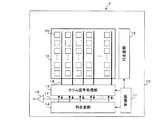

まず、本実施形態おける撮像機器の構成について図面を用いて説明する。

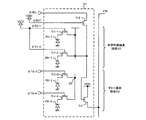

次に、本実施形態に係るCMOS型の固体撮像素子2の構成について図面を用いて説明する。

2 固体撮像素子

12 行走査部

14 列走査部

16 画素アレイ部

17 水平信号線

20,20’ 画素

21,21’ 画素群

22 FD

30 有効画素領域

31 遮光画素領域

32 光学的黒画素領域

33 ダミー画素領域

SW1〜SW6 スイッチ

VSL 列信号線

Claims (4)

- 光電変換素子と当該光電変換素子で光電変換して得られた電荷をフローティングディフージョン部に読み出すトランジスタとを含む画素が行列状に配置され、光が照射される複数の画素からなる有効画素領域と、光の照射が遮られている複数の画素からなる遮光画素領域を有する画素アレイ部と、

前記画素アレイ部を画素行毎に選択制御し、画素列毎に設けられた列信号線に前記選択した画素行の各画素からそれぞれ信号を出力させる行走査部と、

各前記列信号線から出力される信号をデジタル変換するAD変換部と、を備え、

前記遮光画素領域は、黒レベルの基準となる信号を生成する画素を有する画素からなる光学的黒画素領域と、前記列信号線への信号の出力経路が遮断され、前記光電変換素子に発生した電荷を電源に排出する画素から形成されて前記光学的黒画素領域と前記有効画素領域との間に設けられたダミー画素領域とを有しており、

前記有効画素領域、前記光学的黒画素領域及び前記ダミー画素領域は、それぞれ列方向の複数の画素が前記フローティングディフージョン部を共有する画素群から構成され、

前記行走査部は、前記遮光画素領域のうち前記ダミー画素領域の選択を行わない固体撮像素子。 - 前記行走査部は、行方向が共通する前記画素群を一括して選択制御する制御信号を出力する複数の制御回路を有しており、前記光学的黒画素領域から前記有効画素領域にいたる一連の選択制御では、前記ダミー画素領域は読み出さず、前記光学的黒画素領域から前記有効画素領域のみを連続して読み出すように選択制御するようにした請求項1に記載の固体撮像素子。

- 固体撮像素子を有し、

前記固体撮像素子は、

光電変換素子と当該光電変換素子で光電変換して得られた電荷をフローティングディフージョン部に読み出すトランジスタとを含む画素が行列状に配置され、光が照射される複数の画素からなる有効画素領域と、光の照射が遮られている複数の画素からなる遮光画素領域を有する画素アレイ部と、

前記画素アレイ部を画素行毎に選択制御し、画素列毎に設けられた列信号線に前記選択した画素行の各画素からそれぞれ信号を出力させる行走査部と、

各前記列信号線から出力される信号をデジタル変換するAD変換部と、を備え、

前記遮光画素領域は、黒レベルの基準となる信号を生成する画素を有する画素からなる光学的黒画素領域と、前記列信号線への信号の出力経路が遮断され、前記光電変換素子に発生した電荷を電源に排出する画素から形成されて前記光学的黒画素領域と前記有効画素領域との間に設けられたダミー画素領域とを有しており、

前記有効画素領域、前記光学的黒画素領域及び前記ダミー画素領域は、それぞれ列方向の複数の画素が前記フローティングディフージョン部を共有する画素群から構成され、

前記行走査部は、前記遮光画素領域のうち前記ダミー画素領域の選択を行わない撮像機器。 - 前記ダミー画素領域の画素群は、前記列信号線への信号の出力経路が遮断されるとともに共通接続される前記フローティングディフージョン部単位で電位が固定されており、

前記ダミー画素領域の画素群に対応する前記行走査部は、一括して非動作状態に固定されている請求項1又は請求項2に記載の固体撮像素子。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010019056A JP5556199B2 (ja) | 2010-01-29 | 2010-01-29 | 固体撮像素子及び撮像機器 |

| US12/929,248 US8284277B2 (en) | 2010-01-29 | 2011-01-11 | Solid-state imaging device and imaging apparatus |

| CN2011100236557A CN102143333A (zh) | 2010-01-29 | 2011-01-21 | 固态成像器件和成像装置 |

| US13/614,729 US8922679B2 (en) | 2010-01-29 | 2012-09-13 | Solid-state imaging device and imaging apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010019056A JP5556199B2 (ja) | 2010-01-29 | 2010-01-29 | 固体撮像素子及び撮像機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011160116A JP2011160116A (ja) | 2011-08-18 |

| JP2011160116A5 JP2011160116A5 (ja) | 2013-03-14 |

| JP5556199B2 true JP5556199B2 (ja) | 2014-07-23 |

Family

ID=44341336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010019056A Expired - Fee Related JP5556199B2 (ja) | 2010-01-29 | 2010-01-29 | 固体撮像素子及び撮像機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US8284277B2 (ja) |

| JP (1) | JP5556199B2 (ja) |

| CN (1) | CN102143333A (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW201216138A (en) * | 2010-10-13 | 2012-04-16 | Chunghwa Picture Tubes Ltd | Method for driving photosensor array panel |

| JP2013211603A (ja) * | 2012-03-30 | 2013-10-10 | Sony Corp | 撮像装置、撮像方法およびプログラム |

| JP2015012373A (ja) * | 2013-06-27 | 2015-01-19 | 株式会社東芝 | 固体撮像装置 |

| JP6383143B2 (ja) | 2013-10-08 | 2018-08-29 | 株式会社リコー | 撮像素子、画像読取装置、画像形成装置及び撮像方法 |

| JP6545013B2 (ja) * | 2015-06-17 | 2019-07-17 | キヤノン株式会社 | 画像形成方法、画像形成装置、および画像形成プログラム |

| US10103187B2 (en) * | 2015-12-17 | 2018-10-16 | Omnivision Technologies, Inc. | Image sensor color correction |

| KR102559953B1 (ko) * | 2016-06-13 | 2023-07-28 | 에스케이하이닉스 주식회사 | 플로팅 확산 영역의 전압 변동 리드아웃 장치 및 그 방법과 그를 이용한 씨모스 이미지 센서 |

| EP3598739B1 (en) * | 2018-04-13 | 2021-08-04 | Shenzhen Goodix Technology Co., Ltd. | Image sensing circuit and control method thereof |

| US10708528B2 (en) * | 2018-05-30 | 2020-07-07 | Semiconductor Components Industries, Llc | Image sensors having dummy pixel rows |

| KR20200075962A (ko) * | 2018-12-18 | 2020-06-29 | 삼성전자주식회사 | 피드백 루프를 통해 픽셀들의 각각의 변환 이득들을 결정하는 이미지 센서 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000196055A (ja) * | 1998-12-24 | 2000-07-14 | Toshiba Corp | 固体撮像装置 |

| JP2002165136A (ja) * | 2000-11-29 | 2002-06-07 | Canon Inc | 撮像装置及び撮像システム |

| JP2003222751A (ja) | 2001-11-21 | 2003-08-08 | Central Glass Co Ltd | 平面光部品の製造方法及び平面光部品 |

| JP4947908B2 (ja) * | 2005-02-21 | 2012-06-06 | ソニー株式会社 | 固体撮像素子、固体撮像素子の駆動方法および撮像装置 |

| US7760258B2 (en) * | 2007-03-07 | 2010-07-20 | Altasens, Inc. | Apparatus and method for stabilizing image sensor black level |

| US20110032391A1 (en) * | 2009-08-04 | 2011-02-10 | Himax Imaging, Inc. | Image Sensor with Peripheral Dummy Pixels |

| JP2011040976A (ja) * | 2009-08-11 | 2011-02-24 | Sony Corp | 固体撮像装置、固体撮像装置の駆動方法および電子機器 |

| US8872953B2 (en) * | 2009-10-30 | 2014-10-28 | Sony Corporation | Solid-state imaging device, manufacturing method thereof, camera, and electronic device |

| JP5655355B2 (ja) * | 2009-11-02 | 2015-01-21 | ソニー株式会社 | 画素欠陥補正装置、撮像装置、画素欠陥補正方法、およびプログラム |

| JP2011097542A (ja) * | 2009-11-02 | 2011-05-12 | Sony Corp | 画素欠陥検出補正装置、撮像装置、画像欠陥検出補正方法、およびプログラム |

-

2010

- 2010-01-29 JP JP2010019056A patent/JP5556199B2/ja not_active Expired - Fee Related

-

2011

- 2011-01-11 US US12/929,248 patent/US8284277B2/en active Active

- 2011-01-21 CN CN2011100236557A patent/CN102143333A/zh active Pending

-

2012

- 2012-09-13 US US13/614,729 patent/US8922679B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20130010164A1 (en) | 2013-01-10 |

| US8284277B2 (en) | 2012-10-09 |

| US8922679B2 (en) | 2014-12-30 |

| US20110187910A1 (en) | 2011-08-04 |

| JP2011160116A (ja) | 2011-08-18 |

| CN102143333A (zh) | 2011-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5556199B2 (ja) | 固体撮像素子及び撮像機器 | |

| US7787037B2 (en) | Imaging method that continuously outputs a signal based on electric charges generated by a selected pixel unit without performing an operation of deselecting the selected pixel unit | |

| JP5038188B2 (ja) | 撮像装置及びそれを用いた撮像システム | |

| JP5282543B2 (ja) | 固体撮像装置、固体撮像装置の駆動方法および撮像装置 | |

| KR101424033B1 (ko) | 고체 촬상 장치, 고체 촬상 장치의 구동 방법 및 촬상 장치 | |

| JP5821315B2 (ja) | 電子機器、電子機器の駆動方法 | |

| JP4979195B2 (ja) | 固体撮像素子、固体撮像素子の駆動方法および撮像装置 | |

| US20080284876A1 (en) | Image sensor, electronic apparatus, and driving method of electronic apparatus | |

| JP4354854B2 (ja) | 固体撮像装置の駆動方法及び固体撮像装置 | |

| JP2013005396A (ja) | 固体撮像装置、固体撮像装置の駆動方法、及び電子機器 | |

| JP2008017388A (ja) | 固体撮像装置 | |

| US8610809B2 (en) | Solid-state imaging device and camera system that controls a unit of plural rows | |

| JP2010093363A (ja) | 固体撮像素子およびその駆動方法、並びにカメラシステム | |

| US9025056B2 (en) | Solid state imaging element and camera system that determine in which horizontal read period a dummy pixel section is to be shuttered | |

| US7948546B2 (en) | Solid-state imaging apparatus having a global shutter function, adapted to be capable of suppressing a reduction in resolution | |

| JP2008218648A (ja) | 撮像装置およびカメラ | |

| JP2010028434A (ja) | 固体撮像装置 | |

| JP2008067241A (ja) | 固体撮像装置及び撮像システム | |

| JP2007166486A (ja) | 固体撮像装置 | |

| JP2007129473A (ja) | 固体撮像装置及び撮像システム | |

| JP5672363B2 (ja) | 固体撮像素子およびカメラシステム | |

| JP2013197697A (ja) | 固体撮像装置及び電子機器 | |

| JP2011091474A (ja) | 固体撮像装置及び撮像機器 | |

| WO2023002643A1 (ja) | 撮像素子及び撮像装置 | |

| JP5142694B2 (ja) | 撮像装置、撮像装置の駆動方法、及び撮像システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130125 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130918 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130924 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140225 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140409 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140520 |

|

| LAPS | Cancellation because of no payment of annual fees |