JP5502139B2 - 配線基板 - Google Patents

配線基板 Download PDFInfo

- Publication number

- JP5502139B2 JP5502139B2 JP2012112016A JP2012112016A JP5502139B2 JP 5502139 B2 JP5502139 B2 JP 5502139B2 JP 2012112016 A JP2012112016 A JP 2012112016A JP 2012112016 A JP2012112016 A JP 2012112016A JP 5502139 B2 JP5502139 B2 JP 5502139B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- connection terminal

- solder resist

- wiring board

- resist layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/01—Manufacture or treatment

- H10W74/012—Manufacture or treatment of encapsulations on active surfaces of flip-chip devices, e.g. forming underfills

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/15—Encapsulations, e.g. protective coatings characterised by their shape or disposition on active surfaces of flip-chip devices, e.g. underfills

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09881—Coating only between conductors, i.e. flush with the conductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10977—Encapsulated connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/02—Details related to mechanical or acoustic processing, e.g. drilling, punching, cutting, using ultrasound

- H05K2203/025—Abrading, e.g. grinding or sand blasting

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/07—Treatments involving liquids, e.g. plating, rinsing

- H05K2203/0779—Treatments involving liquids, e.g. plating, rinsing characterised by the specific liquids involved

- H05K2203/0783—Using solvent, e.g. for cleaning; Regulating solvent content of pastes or coatings for adjusting the viscosity

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistors

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistors

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistors electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3452—Solder masks

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

Description

絶縁層及び導体層がそれぞれ1層以上積層された積層体を有する配線基板であって、前記積層体上に互いに離間して形成された複数の接続端子と、前記複数の接続端子間に充填され、前記複数の接続端子の各側面の少なくとも一部と当接する充填部材と、前記積層体上に積層され、前記複数の接続端子を露出する開口を有するソルダーレジスト層と、を備え、前記充填部材の表面粗さは、前記ソルダーレジスト層の上面の表面粗さよりも粗いことを特徴とする。

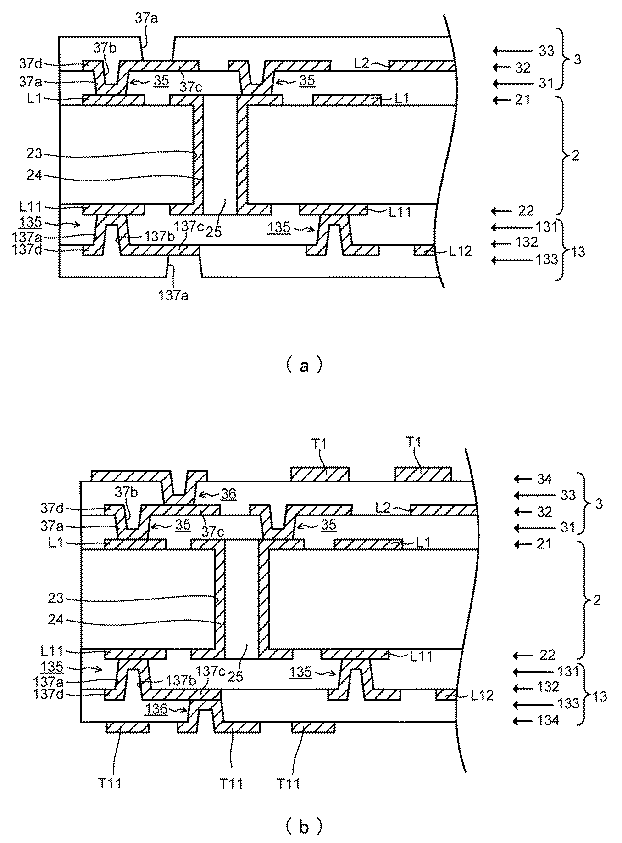

図1は、第1の実施形態における配線基板100の平面図(表面側)である。図2は、図1の線分I−Iにおける配線基板100の一部断面図である。図3は、配線基板100の表面側に形成された接続端子T1の構成図である。図3(a)は、接続端子T1の上面図である。図3(b)は、図3(a)の線分II−IIにおける断面図である。なお、以下の説明では、半導体チップが接続される側を表面側とし、マザーボードやソケット等(以下、マザーボード等と称する)が接続される側を裏面側とする。

図1〜3に示す配線基板100は、コア基板2と、半導体チップ(不図示)との接続端子T1が複数形成され、コア基板2の表面側に積層されるビルドアップ層3(表面側)と、ビルドアップ層3に積層され、複数の接続端子T1間を充填する充填部材4と、充填部材4に積層され、接続端子T1の少なくとも一部を露出する開口5aが形成されたソルダーレジスト層5と、マザーボード等(不図示)との接続端子T11が複数形成され、コア基板2の裏面側に積層されるビルドアップ層13(裏面側)と、ビルドアップ層13に積層され、接続端子T11の少なくとも一部を露出する開口14aが形成されたソルダーレジスト層14と、を備える。

ビルドアップ層3は、コア基板2の表面側に積層された樹脂絶縁層31,33及び導体層32,34からなる。樹脂絶縁層31は、熱硬化性樹脂組成物からなり、表面に金属配線L2をなす導体層32が形成されている。また、樹脂絶縁層31には、コア導体層21と導体層32とを電気的に接続するビア35が形成されている。樹脂絶縁層33は、熱硬化性樹脂組成物からなり、表層に複数の接続端子T1を有する導体層34が形成されている。また、樹脂絶縁層33には、導体層32と導体層34とを電気的に接続するビア36が形成されている。ここで、樹脂絶縁層31,33及び導体層32は積層体を構成する。

ビルドアップ層13は、コア基板2の裏面側に積層された樹脂絶縁層131,133及び導体層132,134からなる。樹脂絶縁層131は、熱硬化性樹脂組成物からなり、裏面に金属配線L12をなす導体層132が形成されている。また、樹脂絶縁層131には、コア導体層22と導体層132とを電気的に接続するビア135が形成されている。樹脂絶縁層133は、熱硬化性樹脂組成物からなり、表層に1以上の接続端子T11を有する導体層134が形成されている。また、樹脂絶縁層133には、導体層132と導体層134とを電気的に接続するビア136が形成されている。

図4〜図11は、第1の実施形態に係る配線基板100の製造工程を示す図である。以下、図4〜図11を参照して、配線基板100の製造方法について説明する。

板状の樹脂製基板の表面及び裏面に銅箔が貼付された銅張積層板を準備する。また、銅張積層板に対してドリルを用いて孔あけ加工を行い、スルーホール23となる貫通孔を所定位置にあらかじめ形成しておく。そして、従来公知の手法に従って無電解銅めっき及び電解銅めっきを行うことでスルーホール23内壁にスルーホール導体24を形成し、銅張積層板の両面に銅めっき層を形成する(図4(a)参照)。

コア基板2の表面及び裏面に、樹脂絶縁層31,131となるエポキシ樹脂を主成分とするフィルム状絶縁樹脂材料をそれぞれ重ね合わせて配置する。そして、この積層物を真空圧着熱プレス機で加圧加熱し、フィルム状絶縁樹脂材料を熱硬化させながら圧着する。次に、従来周知のレーザー加工装置を用いてレーザー照射を行い、樹脂絶縁層31,131にビアホール37a,137aをそれぞれ形成する(図5(a)参照)。

次に、ビルドアップ層3の表層をなす複数の接続端子T1間を、接続端子T1よりも低い位置まで充填部材4で充填する。なお、接続端子T1間を充填部材4で充填するために、接続端子T1の表面(特に、側面)を粗化しておくことが好ましい。接続端子T1の表面は、例えば、メックエッチボンド(メック社製)等のエッチング液で処理することで粗化することができる。また、各接続端子T1の表面を粗化する代わりに、Sn(錫)、Ti(チタン)、Cr(クロム)、Ni(ニッケル)のいずれか1つの金属元素を各接続端子T1の表面にコーティングして金属層を形成した後、この金属層の上にカップリング剤処理を施し、充填部材4との接着性を向上させてもよい。

この第1の充填方法では、表層に接続端子T1が形成されたビルドアップ層3の表面に熱硬化性の絶縁性樹脂を薄くコートして熱硬化させた後、硬化した絶縁性樹脂を接続端子T1よりも低くなるまで研磨することで、充填部材4を接続端子T1間に充填する。この研磨により、充填部材4の表面H1を粗くすることができる。

この第2の充填方法では、表層に接続端子T1が形成されたビルドアップ層3の表面に熱硬化性の絶縁性樹脂を薄くコートした後、絶縁性樹脂を溶融する溶剤で、接続端子T1上面を覆う余分な絶縁性樹脂を除去した後、熱硬化させることで充填部材4を接続端子T1間に充填する。この除去により、充填部材4の表面H1を粗くすることができる。

この第3の充填方法では、表層に接続端子T1が形成されたビルドアップ層3の表面に熱硬化性の絶縁性樹脂を厚くコートして熱硬化させた後、半導体素子の実装領域以外の領域をマスクし、接続端子T1よりも低くなるまで絶縁性樹脂をRIE(Reactive Ion Etching)等によりドライエッチングすることで充填部材4を接続端子T1間に充填する。なお、この第3の充填方法で、充填部材4を接続端子T1間に充填する場合、充填部材4とソルダーレジスト層5とが一体的に形成される。また、このドライエッチングにより、充填部材4の表面H1及び開口5aの内周面H3を粗くすることができる。

図8は、第4の充填方法の説明図である。以下、図8を参照して、第4の充填方法について説明する。第4の充填方法では、表層に配線導体T1が形成されたビルドアップ層3の表面に光硬化性の絶縁性樹脂を厚くコートした後(図8(a)参照)、後にソルダーレジスト層の開口5aとなるべき領域の内側領域をマスクして絶縁性樹脂を露光・現像して、開口5aの外側領域となるべき絶縁性樹脂を光硬化させる(図8(b)参照)。次に、炭酸ナトリウム水溶液(濃度1重量%)に、この製造途中の配線基板100を短時間(未感光部の絶縁性樹脂表面が若干膨潤する程度の時間)浸漬する(図8(c)参照)。その後、水洗して膨潤した絶縁性樹脂を乳化させる(図8(d)参照)。次に、膨潤・乳化した絶縁性樹脂を製造途中の配線基板100から除去する(図8(e)参照)。光硬化していない絶縁性樹脂の上端の位置が、各配線導体T1の上端より低い位置となるまで上記浸漬及び水洗を、それぞれ1回、又はそれぞれ数回繰り返す。その後、熱または紫外線により絶縁性樹脂を硬化させる。なお、この第4の充填方法で、充填部材4を接続端子T1間に充填する場合、充填部材4とソルダーレジスト層5とが一体的に形成される。また、浸漬及び水洗により、充填部材4の表面H1及び開口5aの内周面H3を粗くすることができる。

充填部材4及びビルドアップ層13の表面に、それぞれフィルム状のソルダーレジストをプレスして積層する。積層したフィルム状のソルダーレジストを露光・現像して、各接続端子T1の表面及び側面を露出させるNSMD形状の開口5aが形成されたソルダーレジスト層5と、各接続端子T11の表面の一部を露出させるSMD形状の開口14aが形成されたソルダーレジスト層14とを得る。なお、充填工程において上述した第1,第2の充填方法を採用した場合、ソルダーレジスト層5の開口5aの内周面H3を粗くする処理(例えば、研磨やエッチング)を行う。また、充填工程において上述した第3,第4の充填方法を採用した場合、充填部材4及びソルダーレジスト層5が一体的に形成されるため、この工程において、ソルダーレジスト層5を積層する必要はない。

次に、接続端子T1の露出面を過硫酸ナトリウム等によりエッチングして、接続端子T1表面の酸化膜等の不純物を除去するとともに、接続端子T1の主面Fの周囲に段差Lを形成する。その後、還元剤を用いた無電解還元めっきにより、接続端子T1,T11の露出面に金属めっき層Mを形成する。無電解置換めっきにより接続端子T1の露出面に金属めっき層Mを形成する場合は、接続端子T1の露出面の金属が置換されて金属めっき層Mが形成される。このため、接続端子T1の露出面を過硫酸ナトリウム等によりエッチングしなくとも、接続端子T1の主面Fの周囲に段差Lが形成される。

厚みが5〜30μmの半田層を接続端子T1の露出面にコートする場合、接続端子T1の露出面を少しだけエッチング(ソフトエッチング)し、接続端子T1の露出面に形成された酸化膜を除去する。この際、接続端子T1の主面Fの周囲に段差Lが形成される。次にSn(錫)粉末、Ag(銀)、Cu(銅)などの金属を含むイオン性化合物及びフラックスを混合したペースト(例えば、ハリマ化成株式会社:スーパーソルダー(製品名))を、接続端子T1の露出面全面を覆うように、SMD形状の開口14a内全体に薄く塗布する。その後、リフローを行い、接続端子T1の露出面にSnとAg、もしくは、Sn、Ag及びCuの合金からなる半田層を形成する。

厚みが10μm以下の半田層を接続端子T1の露出面にコートする場合、接続端子T1の露出面を少しだけエッチング(ソフトエッチング)し、接続端子T1の露出面に形成された酸化膜を除去する。この際、接続端子T1の主面Fの周囲に段差Lが形成される。次に、接続端子T1の露出面に無電解Sn(錫)めっきを行うことによりSnめっき層を形成し、このSnめっき層の全面を覆うようにしてフラックスを塗布する。その後、リフローを行い、接続端子T1にめっきされたSnめっき層を溶融させて接続端子T1の主面Fに半田層を形成する。この際、溶融したSnは、表面張力により、接続端子T1の主面Fに凝集する。

半田印刷により、接続端子T11上に形成された金属めっき層M上に半田ペーストを塗布した後、所定の温度と時間でリフローを行い、接続端子T11上に半田ボールBを形成する。

図12は、第2の実施形態における配線基板200の平面図(表面側)である。図13は、図12の線分I−Iにおける配線基板200の一部断面図である。図14は、配線基板200の表面側に形成された接続端子T2の構成図である。図14(a)は、接続端子T2の上面図である。図14(b)は、図14(a)のII−IIにおける断面図である。以下、図12〜図14を参照して配線基板200の構成について説明するが、図1〜図3を参照して説明した配線基板100と同一の構成については同一の符号を付して重複した説明を省略する。

配線基板200の表面側では、コア導体層21と電気的に接続する蓋めっき層41が形成され、この蓋めっき層41と導体層32及び導体層32と導体層34とが、それぞれフィルドビア42及びフィルドビア43により電気的に接続されている。フィルドビア42,43は、ビアホール44aとビアホール44a内側にめっきにより充填されたビア導体44bとを有する。また、ビルドアップ層3の最表層には、後述する接続端子T2だけが形成され、接続端子T2と同一層において接続される配線パターンや配線パターンを覆うソルダーレジスト層は形成されていない。ここで、樹脂絶縁層31,33及び導体層32は積層体を構成する。

配線基板200の裏面側では、コア導体層22と電気的に接続する蓋めっき層141が形成され、この蓋めっき141と導体層132及び導体層132と導体層134とが、それぞれフィルドビア142及びフィルドビア143により電気的に接続されている。フィルドビア142,143は、ビアホール144aとビアホール144a内側にめっきにより充填されたビア導体144bとを有する。

図1〜図3を参照して説明した配線基板100及び図12〜図14を参照して説明した配線基板200では、接続端子T1、T2間にそれぞれ充填する充填部材4の上面は、平坦(フラット)となっていたが、充填部材4の上面は、必ずしも平坦(フラット)である必要はなく、例えば、図15に示すように、充填部材4の上面が丸みを帯びた、いわゆるフィレット形状となっていても、同様の効果を得ることができる。

Claims (6)

- 絶縁層及び導体層がそれぞれ1層以上積層された積層体を有する配線基板であって、

前記積層体上に互いに離間して形成された複数の接続端子と、

前記複数の接続端子間に充填され、前記複数の接続端子の各側面の少なくとも一部と当接する充填部材と、

前記積層体上に積層され、前記複数の接続端子を露出する開口を有するソルダーレジスト層と、

を備え、

前記充填部材の表面粗さは、前記ソルダーレジスト層の上面の表面粗さよりも粗く、

前記ソルダーレジスト層が有する前記開口の内周面の表面粗さは、前記ソルダーレジスト層の上面の表面粗さよりも粗く、

前記充填部材と前記ソルダーレジスト層とが一体的に形成されることを特徴とする配線基板。 - 前記充填部材の表面粗さ(Ra)は、0.06μm〜0.8μmであることを特徴とする請求項1に記載の配線基板。

- 前記ソルダーレジスト層の表面粗さ(Ra)は、0.02μm〜0.25μmであることを特徴とする請求項1又は請求項2に記載の配線基板。

- 前記充填部材は、ソルダーレジストとして機能することを特徴とする請求項1乃至請求項3のいずれか1項に記載の配線基板。

- 前記接続端子は、少なくとも一部が前記充填部材の表面から突出していることを特徴とする請求項1乃至請求項4のいずれか1項に記載の配線基板。

- 前記ソルダーレジスト層の上面の高さは、前記接続端子の上面の高さよりも高いことを特徴とする請求項1乃至請求項5のいずれか1項に記載の配線基板。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012112016A JP5502139B2 (ja) | 2012-05-16 | 2012-05-16 | 配線基板 |

| KR1020147001606A KR101523478B1 (ko) | 2012-05-16 | 2013-04-10 | 배선기판 |

| EP13791078.2A EP2747529B1 (en) | 2012-05-16 | 2013-04-10 | Wiring board |

| US14/235,729 US9179552B2 (en) | 2012-05-16 | 2013-04-10 | Wiring board |

| PCT/JP2013/002424 WO2013171965A1 (ja) | 2012-05-16 | 2013-04-10 | 配線基板 |

| CN201380002506.XA CN103733739B (zh) | 2012-05-16 | 2013-04-10 | 布线基板 |

| TW102117152A TWI601466B (zh) | 2012-05-16 | 2013-05-15 | 配線基板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012112016A JP5502139B2 (ja) | 2012-05-16 | 2012-05-16 | 配線基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013239604A JP2013239604A (ja) | 2013-11-28 |

| JP5502139B2 true JP5502139B2 (ja) | 2014-05-28 |

Family

ID=49583398

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012112016A Expired - Fee Related JP5502139B2 (ja) | 2012-05-16 | 2012-05-16 | 配線基板 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9179552B2 (ja) |

| EP (1) | EP2747529B1 (ja) |

| JP (1) | JP5502139B2 (ja) |

| KR (1) | KR101523478B1 (ja) |

| CN (1) | CN103733739B (ja) |

| TW (1) | TWI601466B (ja) |

| WO (1) | WO2013171965A1 (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6037514B2 (ja) * | 2014-05-22 | 2016-12-07 | 日本特殊陶業株式会社 | 配線基板、配線基板の製造方法 |

| JP2015231003A (ja) * | 2014-06-06 | 2015-12-21 | イビデン株式会社 | 回路基板および回路基板の製造方法 |

| JP6230971B2 (ja) * | 2014-08-05 | 2017-11-15 | 日本特殊陶業株式会社 | 配線基板の製造方法 |

| KR20160099381A (ko) * | 2015-02-12 | 2016-08-22 | 삼성전기주식회사 | 인쇄회로기판 및 인쇄회로기판의 제조 방법 |

| JP2016207893A (ja) * | 2015-04-24 | 2016-12-08 | イビデン株式会社 | プリント配線板およびその製造方法 |

| CN105376944A (zh) * | 2015-11-11 | 2016-03-02 | 广德宝达精密电路有限公司 | 一种提高印制板密度的加工工艺 |

| JP2017152536A (ja) * | 2016-02-24 | 2017-08-31 | イビデン株式会社 | プリント配線板及びその製造方法 |

| TWI595812B (zh) * | 2016-11-30 | 2017-08-11 | 欣興電子股份有限公司 | 線路板結構及其製作方法 |

| TWI614862B (zh) * | 2017-01-13 | 2018-02-11 | 矽品精密工業股份有限公司 | 基板結構及其製法 |

| KR20190012485A (ko) * | 2017-07-27 | 2019-02-11 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조 방법 |

| TWI771400B (zh) * | 2018-03-30 | 2022-07-21 | 南韓商Lg新能源股份有限公司 | 組裝孔結構 |

| KR102872348B1 (ko) * | 2020-03-10 | 2025-10-17 | 엘지이노텍 주식회사 | 인쇄회로기판 및 이의 제조 방법 |

| KR102901381B1 (ko) * | 2020-04-20 | 2025-12-18 | 엘지이노텍 주식회사 | 회로 기판 |

| KR102898765B1 (ko) * | 2020-04-23 | 2025-12-12 | 엘지이노텍 주식회사 | 회로 기판 |

| KR102909754B1 (ko) * | 2020-06-12 | 2026-01-09 | 엘지이노텍 주식회사 | 인쇄회로기판 및 이의 제조 방법 |

| CN112867243A (zh) * | 2021-01-06 | 2021-05-28 | 英韧科技(上海)有限公司 | 多层电路板 |

| US12550269B2 (en) | 2021-04-26 | 2026-02-10 | Lg Innotek Co., Ltd. | Circuit board |

| CN115988730A (zh) * | 2021-10-15 | 2023-04-18 | 奥特斯奥地利科技与系统技术有限公司 | 部件承载件、以及部件承载件的制造方法和使用方法 |

| JPWO2024071069A1 (ja) * | 2022-09-28 | 2024-04-04 |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3400877B2 (ja) * | 1994-12-14 | 2003-04-28 | 三菱電機株式会社 | 半導体装置及びその製造方法 |

| JP3050807B2 (ja) * | 1996-06-19 | 2000-06-12 | イビデン株式会社 | 多層プリント配線板 |

| JP3050812B2 (ja) * | 1996-08-05 | 2000-06-12 | イビデン株式会社 | 多層プリント配線板 |

| US5729896A (en) * | 1996-10-31 | 1998-03-24 | International Business Machines Corporation | Method for attaching a flip chip on flexible circuit carrier using chip with metallic cap on solder |

| MY139405A (en) * | 1998-09-28 | 2009-09-30 | Ibiden Co Ltd | Printed circuit board and method for its production |

| CN101925260A (zh) * | 1999-08-12 | 2010-12-22 | Ibiden股份有限公司 | 多层印刷电路板 |

| JP2001274537A (ja) * | 2000-03-28 | 2001-10-05 | Ngk Spark Plug Co Ltd | 配線基板及び配線基板の製造方法 |

| JP2002033567A (ja) * | 2000-07-14 | 2002-01-31 | Ngk Spark Plug Co Ltd | 基板の製造方法及び保持治具 |

| JP2004179578A (ja) * | 2002-11-29 | 2004-06-24 | Ngk Spark Plug Co Ltd | 配線基板及びその製造方法 |

| JP2006216842A (ja) * | 2005-02-04 | 2006-08-17 | Matsushita Electric Ind Co Ltd | メモリカードおよびプリント配線板 |

| JP4538373B2 (ja) * | 2005-05-23 | 2010-09-08 | 日本特殊陶業株式会社 | コアレス配線基板の製造方法、及びそのコアレス配線基板を有する電子装置の製造方法 |

| WO2006126621A1 (ja) * | 2005-05-23 | 2006-11-30 | Ibiden Co., Ltd. | プリント配線板 |

| CN101854771A (zh) * | 2005-06-30 | 2010-10-06 | 揖斐电株式会社 | 印刷线路板 |

| CN101171894B (zh) * | 2005-06-30 | 2010-05-19 | 揖斐电株式会社 | 印刷线路板 |

| US7969005B2 (en) * | 2007-04-27 | 2011-06-28 | Sanyo Electric Co., Ltd. | Packaging board, rewiring, roughened conductor for semiconductor module of a portable device, and manufacturing method therefor |

| JP5138277B2 (ja) * | 2007-05-31 | 2013-02-06 | 京セラSlcテクノロジー株式会社 | 配線基板およびその製造方法 |

| KR101551898B1 (ko) * | 2007-10-05 | 2015-09-09 | 신꼬오덴기 고교 가부시키가이샤 | 배선 기판, 반도체 장치 및 이들의 제조 방법 |

| JP2009152317A (ja) * | 2007-12-19 | 2009-07-09 | Panasonic Corp | 半導体装置およびその製造方法 |

| JP5020123B2 (ja) | 2008-03-03 | 2012-09-05 | 新光電気工業株式会社 | 配線基板の製造方法 |

| US7985622B2 (en) * | 2008-08-20 | 2011-07-26 | Intel Corporation | Method of forming collapse chip connection bumps on a semiconductor substrate |

| US8129828B2 (en) | 2008-09-29 | 2012-03-06 | Ngk Spark Plug Co., Ltd. | Wiring substrate with reinforcement |

| US8686300B2 (en) * | 2008-12-24 | 2014-04-01 | Ibiden Co., Ltd. | Printed wiring board and method for manufacturing the same |

| US8426959B2 (en) * | 2009-08-19 | 2013-04-23 | Samsung Electronics Co., Ltd. | Semiconductor package and method of manufacturing the same |

| JP2011138868A (ja) * | 2009-12-28 | 2011-07-14 | Ngk Spark Plug Co Ltd | 多層配線基板 |

| JP2011138869A (ja) * | 2009-12-28 | 2011-07-14 | Ngk Spark Plug Co Ltd | 多層配線基板の製造方法及び多層配線基板 |

| JP5566200B2 (ja) * | 2010-06-18 | 2014-08-06 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP2012009586A (ja) * | 2010-06-24 | 2012-01-12 | Shinko Electric Ind Co Ltd | 配線基板、半導体装置及び配線基板の製造方法 |

| JP2012069629A (ja) * | 2010-09-22 | 2012-04-05 | Nec Casio Mobile Communications Ltd | プリント配線板の製造方法 |

| JP5547594B2 (ja) * | 2010-09-28 | 2014-07-16 | 新光電気工業株式会社 | 配線基板、半導体装置及び配線基板の製造方法 |

| JP5855905B2 (ja) * | 2010-12-16 | 2016-02-09 | 日本特殊陶業株式会社 | 多層配線基板及びその製造方法 |

| JP5861262B2 (ja) * | 2011-03-26 | 2016-02-16 | 富士通株式会社 | 回路基板の製造方法及び電子装置の製造方法 |

| KR101177664B1 (ko) * | 2011-05-11 | 2012-08-27 | 삼성전기주식회사 | 인쇄회로기판의 제조방법 |

-

2012

- 2012-05-16 JP JP2012112016A patent/JP5502139B2/ja not_active Expired - Fee Related

-

2013

- 2013-04-10 WO PCT/JP2013/002424 patent/WO2013171965A1/ja not_active Ceased

- 2013-04-10 CN CN201380002506.XA patent/CN103733739B/zh not_active Expired - Fee Related

- 2013-04-10 US US14/235,729 patent/US9179552B2/en not_active Expired - Fee Related

- 2013-04-10 KR KR1020147001606A patent/KR101523478B1/ko not_active Expired - Fee Related

- 2013-04-10 EP EP13791078.2A patent/EP2747529B1/en not_active Not-in-force

- 2013-05-15 TW TW102117152A patent/TWI601466B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013239604A (ja) | 2013-11-28 |

| TW201406243A (zh) | 2014-02-01 |

| WO2013171965A1 (ja) | 2013-11-21 |

| TWI601466B (zh) | 2017-10-01 |

| US9179552B2 (en) | 2015-11-03 |

| KR101523478B1 (ko) | 2015-05-27 |

| KR20140036005A (ko) | 2014-03-24 |

| EP2747529A1 (en) | 2014-06-25 |

| CN103733739A (zh) | 2014-04-16 |

| US20140196939A1 (en) | 2014-07-17 |

| CN103733739B (zh) | 2017-06-09 |

| EP2747529A4 (en) | 2015-05-06 |

| EP2747529B1 (en) | 2019-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5502139B2 (ja) | 配線基板 | |

| JP5415632B2 (ja) | 配線基板 | |

| JP5341227B1 (ja) | 配線基板 | |

| JP5410580B1 (ja) | 配線基板 | |

| JP5913063B2 (ja) | 配線基板 | |

| JP2014078551A (ja) | 配線基板、配線基板の製造方法 | |

| JP2013105908A (ja) | 配線基板 | |

| JP5913055B2 (ja) | 配線基板 | |

| JP2014089996A (ja) | 配線基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140312 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5502139 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |