JP5479218B2 - 昇圧回路 - Google Patents

昇圧回路 Download PDFInfo

- Publication number

- JP5479218B2 JP5479218B2 JP2010116465A JP2010116465A JP5479218B2 JP 5479218 B2 JP5479218 B2 JP 5479218B2 JP 2010116465 A JP2010116465 A JP 2010116465A JP 2010116465 A JP2010116465 A JP 2010116465A JP 5479218 B2 JP5479218 B2 JP 5479218B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- charge pump

- reference voltage

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

=VCPL−((VCPL×nR−Vr×R)/(R+nR)) 式(5)

=VCPL×R+Vr×R 式(6)

=(VCPL+Vr)/(1+n) 式(7)

負荷が軽い場合でも出力電圧のリップルの周期が短くリップル電圧が小さいチャージポンプ回路1が記載されている。

=(1/(R1+R2))×(R1×Vr2+R2×VCPL) 式(12)

=((R3+R4)/R3)×Vr1−(R4/R3)×Vn3 式(16)

=((R3+R4)/R3)×Vr1+(R4/R3)×Vn1−(2R4/R3)×Vr1

=((R3−R4)/R3)×Vr1+(R4/R3)×Vn1 式(17)

よって、図1の回路構成を採ることにより、VCPLの安定化とリップル電圧を抑える効果が得られる。

106:電圧比較用アンプ

107、207、307:電圧出力端子

205:電圧電流変換回路(OTA)

212:バッファ

300、300A、300B:昇圧回路

301:電源

302:発振回路

303、303A:チャージポンプ回路

304、304A:基準電圧生成回路

305、305A:第1基準電圧出力端子

306:ユニティゲインアンプ

308、310:第1基準電圧入力端子(非反転入力端子)

309、309A、311:差動増幅回路

313:クロックバッファ

315、315A:第2基準電圧出力端子

321、322:インバータ

C1〜C6、C11、Cin:容量

Di1〜Di3、Di1A〜Di3A:ダイオード

R、R1〜R6、R1A、R2A、R5A、R6A、R11〜R16、R21、R22、nR:抵抗

Tr1〜Tr15、Tr21〜Tr36、Tr41〜Tr45:トランジスタ

VCPL、VCPLA:(昇圧回路の)出力電圧

Vn1、Vn1A:第1のノード

Vr1、Vr1A:第1の基準電圧

Vr2、Vr2A:第2の基準電圧

Claims (9)

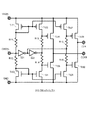

- クロック信号に基づいて昇圧を行うチャージポンプ回路と、

前記チャージポンプ回路の出力電圧に比例する電圧と基準電圧とが初段の非反転入力信号と反転入力信号として入力され、前段の差動出力信号と基準電圧とが後段の非反転入力信号と反転入力信号として入力され、最終段の差動出力信号が前記チャージポンプ回路の動作制御電圧信号として前記チャージポンプ回路の動作を制御する縦続接続された複数の差動増幅回路と、

を備え、

前記縦続接続された複数の差動増幅回路は、各段の差動出力信号が当該段の反転入力信号として帰還されるようにそれぞれ負帰還接続されていることを特徴とする昇圧回路。 - 発振回路を更に備え、

前記チャージポンプ回路は、前記発振回路の発振周波数に基づいて振幅が前記最終段の差動出力信号により制御される前記クロック信号を生成するクロックバッファを備え、前記クロックバッファが出力するクロック信号の電圧振幅に基づいて前記チャージポンプ回路の昇圧能力が制御されることを特徴とする請求項1記載の昇圧回路。 - 前記基準電圧を第1の基準電圧としたときに、前記第1の基準電圧と第2の基準電圧とを出力する基準電圧生成回路を更に備え、

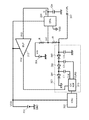

前記第2の基準電圧と前記チャージポンプ回路の出力電圧とを抵抗分圧した電圧が前記チャージポンプ回路の出力電圧に比例する電圧として前記初段に入力されることを特徴とする請求項1または2記載の昇圧回路。 - 前記初段の前段にさらにユニティゲインアンプを備え、前記チャージポンプ回路の出力電圧に比例する電圧が前記ユニティゲインアンプを介してインピーダンス変換されて前記初段に入力されることを特徴とする請求項1乃至3いずれか1項記載の昇圧回路。

- 前記チャージポンプ回路が負電圧の絶対値が大きくなるように昇圧して出力するチャージポンプ回路であって、

前記縦続接続された複数の差動増幅回路は全体として、前記チャージポンプ回路の出力電圧に比例する電圧が、下降すれば前記チャージポンプ回路の昇圧能力を減少させ、上昇すれば前記チャージポンプ回路の昇圧能力を増加させるように接続されていることを特徴とする請求項1乃至4いずれか1項記載の昇圧回路。 - 前記チャージポンプ回路が正電圧を昇圧して出力するチャージポンプ回路であって、

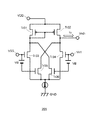

前記縦続接続された複数の差動増幅回路は全体として、前記チャージポンプ回路の出力電圧に比例する電圧が、上昇すれば前記チャージポンプ回路の昇圧能力を減少させ、下降すれば前記チャージポンプ回路の昇圧能力を増加させるように接続されていることを特徴とする請求項1乃至4いずれか1項記載の昇圧回路。 - 前記チャージポンプ回路の電圧出力端子と、第1のノードと、の間に接続された第1の抵抗と、

前記基準電圧生成回路の前記第2の基準電圧を出力する第2基準電圧出力端子と、前記第1のノードと、の間に接続された第2の抵抗と、

をさらに備え、

前記複数縦続接続された差動増幅回路は、

第1の差動増幅回路と、

前記第1の差動増幅回路の差動出力端子が第3の抵抗を介して反転入力端子に接続され、差動出力端子と前記反転入力端子が第4の抵抗を介して接続され、前記第1の基準電圧を出力する前記基準電圧生成回路の第1基準電圧出力端子が非反転入力端子に接続され、前記差動出力端子が前記クロックバッファの電源端子に接続された第2の差動増幅回路と、

を備え、

前記第1の差動増幅回路は、

反転入力端子が第5の抵抗を介して前記第1のノードに接続されるとともに、第6の抵抗を介して当該差動増幅回路の差動出力端子に接続され、

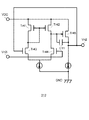

非反転入力端子が前記第1基準電圧出力端子に接続されていることを特徴とする請求項3記載の昇圧回路。 - 前記チャージポンプ回路の電圧出力端子と、第1のノードと、の間に接続された第1の抵抗と、

前記第2の基準電圧を出力する前記基準電圧生成回路の第2基準電圧出力端子と、前記第1のノードと、の間に接続された第2の抵抗と、

非反転入力端子が前記第1のノードに接続され、反転入力端子が差動出力端子に接続されたユニティゲインアンプと、

をさらに備え、

前記複数縦続接続された差動増幅回路は、

第1の差動増幅回路と、

前記第1の差動増幅回路の差動出力端子が第3の抵抗を介して反転入力端子に接続され、差動出力端子と前記反転入力端子が第4の抵抗を介して接続され、前記第1の基準電圧を出力する前記基準電圧生成回路の第1基準電圧出力端子が非反転入力端子に接続され、前記差動出力端子が前記クロックバッファの電源端子に接続された第2の差動増幅回路と、

を備え、

前記第1の差動増幅回路は、

反転入力端子が第5の抵抗を介して前記ユニティゲインアンプの差動出力端子に接続されるとともに、第6の抵抗を介して当該差動増幅回路の差動出力端子に接続され、

非反転入力端子が前記第1基準電圧出力端子に接続されていることを特徴とする請求項3記載の昇圧回路。 - 前記請求項1乃至8いずれか1項記載の昇圧回路が単一の半導体基板の上に形成されていることを特徴とする半導体集積回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010116465A JP5479218B2 (ja) | 2010-05-20 | 2010-05-20 | 昇圧回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010116465A JP5479218B2 (ja) | 2010-05-20 | 2010-05-20 | 昇圧回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011244651A JP2011244651A (ja) | 2011-12-01 |

| JP5479218B2 true JP5479218B2 (ja) | 2014-04-23 |

Family

ID=45410707

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010116465A Expired - Fee Related JP5479218B2 (ja) | 2010-05-20 | 2010-05-20 | 昇圧回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5479218B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11024373B2 (en) | 2019-09-12 | 2021-06-01 | Hefei Reliance Memory Limited | Voltage-mode bit line precharge for random-access memory cells |

| CN113765369B (zh) * | 2021-09-01 | 2024-01-23 | 深圳市爱协生科技股份有限公司 | 在复杂电源域中的新型正电压转负电压的电压转换电路 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0779561A (ja) * | 1993-09-10 | 1995-03-20 | Sony Corp | 昇圧電源回路および昇圧回路 |

| JPH11219596A (ja) * | 1998-02-03 | 1999-08-10 | Nec Corp | 半導体装置の電源回路 |

| JP2001177357A (ja) * | 1999-12-17 | 2001-06-29 | Matsushita Electric Works Ltd | 差動アンプ |

| JP3666805B2 (ja) * | 2000-09-19 | 2005-06-29 | ローム株式会社 | Dc/dcコンバータ |

| US6704180B2 (en) * | 2002-04-25 | 2004-03-09 | Medtronic, Inc. | Low input capacitance electrostatic discharge protection circuit utilizing feedback |

| JP2005071067A (ja) * | 2003-08-25 | 2005-03-17 | Renesas Technology Corp | 電圧発生回路 |

| KR100752643B1 (ko) * | 2005-03-14 | 2007-08-29 | 삼성전자주식회사 | 입력 전압에 적응적으로 제어되는 전압 승압 장치 |

-

2010

- 2010-05-20 JP JP2010116465A patent/JP5479218B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011244651A (ja) | 2011-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4613986B2 (ja) | スイッチング電源装置 | |

| US11444537B2 (en) | Power converters and compensation circuits thereof | |

| TWI661669B (zh) | 多級放大器 | |

| US7375992B2 (en) | Switched-capacitor regulators | |

| US8823343B2 (en) | Power amplifying circuit, DC-DC converter, peak holding circuit, and output voltage control circuit including the peak holding circuit | |

| JP5131321B2 (ja) | スイッチング電源装置 | |

| US7385444B2 (en) | Class D amplifier | |

| JP6098057B2 (ja) | 電源の制御回路、電源装置及び電源の制御方法 | |

| US9148052B2 (en) | Switching regulator with reduced EMI | |

| CN101548456A (zh) | 开关稳压器以及用于控制其工作的方法 | |

| US9595866B2 (en) | Hysteretic switching regulator including a power converting unit and a switch driving unit | |

| JP2009303317A (ja) | 基準電圧発生回路及びその基準電圧発生回路を備えたdc−dcコンバータ | |

| US20100156491A1 (en) | Voltage converters and voltage generating methods | |

| JP2013046496A (ja) | 制御回路、電源装置及び電源の制御方法 | |

| JP5605177B2 (ja) | 制御回路、電子機器及び電源の制御方法 | |

| JP5479218B2 (ja) | 昇圧回路 | |

| JP5966503B2 (ja) | 昇降圧型dc−dcコンバータおよび携帯機器 | |

| US10340929B2 (en) | Voltage controlled oscillator and phase locked loop comprising the same | |

| CN113824318A (zh) | 电源转换器的控制电路及其控制方法 | |

| JP2010063290A (ja) | 電源制御回路 | |

| US8937569B2 (en) | Analog-to-digital conversion device | |

| JP5499431B2 (ja) | 三角波発生回路 | |

| JP2006155100A (ja) | 電源回路 | |

| WO2012053133A1 (ja) | チョッパ増幅器、アクティブフィルタ、基準周波数生成回路 | |

| Tsai et al. | An integrated 12-V electret earphone driver with symmetric Cockcroft-Walton pumping topology for in-ear hearing aids |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140122 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140212 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5479218 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |