JP5458692B2 - 電子装置 - Google Patents

電子装置 Download PDFInfo

- Publication number

- JP5458692B2 JP5458692B2 JP2009152037A JP2009152037A JP5458692B2 JP 5458692 B2 JP5458692 B2 JP 5458692B2 JP 2009152037 A JP2009152037 A JP 2009152037A JP 2009152037 A JP2009152037 A JP 2009152037A JP 5458692 B2 JP5458692 B2 JP 5458692B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- power storage

- storage means

- comparator

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B10/00—Integration of renewable energy sources in buildings

- Y02B10/70—Hybrid systems, e.g. uninterruptible or back-up power supplies integrating renewable energies

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E60/00—Enabling technologies; Technologies with a potential or indirect contribution to GHG emissions mitigation

- Y02E60/10—Energy storage using batteries

Landscapes

- Electric Clocks (AREA)

- Electromechanical Clocks (AREA)

- Stand-By Power Supply Arrangements (AREA)

- Charge And Discharge Circuits For Batteries Or The Like (AREA)

- Secondary Cells (AREA)

Description

発電手段と、

該発電手段に対してそれぞれ並列に接続された第1蓄電手段、該第1蓄電手段より容量の小さな第2蓄電手段、および、装置の機能を実現する機能回路と、

閉成状態から開成状態に切り替わることで、前記機能回路および前記第2蓄電手段を前記発電手段および前記第1蓄電手段から切り離すことが可能な第1スイッチ手段と、

閉成状態から開成状態に切り替わることで、前記第1蓄電手段を前記発電手段、前記第2蓄電手段および前記機能回路から切り離すことが可能な第2スイッチ手段と、

前記第1蓄電手段の端子電圧と前記第2蓄電手段の端子電圧とを比較する第1比較器と、

前記機能回路を駆動可能な電源電圧である第1閾値電圧と前記第2蓄電手段の端子電圧とを比較する第2比較器と、

前記第1比較器の出力に基づき前記第1スイッチ手段と前記第2スイッチ手段との切り替えを制御する論理手段と、

を備え、

前記論理手段は、

前記第1蓄電手段の端子電圧が前記第2蓄電手段の端子電圧より大きい場合に前記第1スイッチ手段を閉成状態に、前記第2スイッチ手段を開成状態に切り替えるとともに、

前記第1蓄電手段の端子電圧が前記第2蓄電手段の端子電圧より小さい場合に前記第1スイッチ手段を開成状態に、前記第2スイッチ手段を閉成状態に切り替え、

前記第2比較器の出力に基づき前記第2蓄電手段の端子電圧が前記第1閾値電圧より低い場合に、前記第1比較器の出力に基づく前記第1スイッチ手段の切り替え制御を解除して、前記第2スイッチ手段を閉成状態とすることを特徴とする電子装置である。

先ず、上記のステップS3,S5の処理により第2ラッチ48がハイレベルにされることで移行されるクイックスタート状態について説明する。

次に、上記のステップS2,S6の処理により第2ラッチ48がローレベルにされることで移行される通常動作状態について説明する。

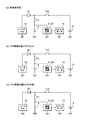

この通常動作状態において、ソーラセル12への入射光が高照度状態になって多くの発電がなされると、図4(a)の切替状態と、図4(b)の切替状態とが、繰り返されて、ソーラセル12の発電電流がコンデンサ3と二次電池2に交互に送られていく。

通常動作状態において、ソーラセル12への入射光が低照度状態になって、ソーラセル12の発電量が低下すると、コンデンサ3に蓄えられた電力が機能回路(21,24)により消費されることで、二次電池2の電圧よりもコンデンサ3の電圧が早く低下する。その結果、コンデンサ3の電圧と二次電池2の電圧を比較するコンパレータCP1の出力はローレベルで一定となり、図5(a)に示すように、第1スイッチTr1はオン、第2スイッチTr2はオフにされる。

通常動作状態において、ソーラセル12への入射高がゼロ照度等になって、ソーラセル12の発電がほとんど行われなくなると、図3の“照度0”の期間に示すように、機能回路(21,24)の電力消費によりコンデンサ3の放電が進んで、コンデンサ3の電圧が低駆動電圧Vd1を下回ることになる。

続いて、図2のステップS9の処理により第1ラッチ42がローレベルにされることで移行される高負荷モードの動作について説明する。

2 二次電池

3 コンデンサ

11 指針

12 ソーラセル

14 ステップモータ

15 発振回路

21 CPU

22 RAM

23 ROM

24 駆動回路

25 計時回路

32 電池電圧検出器

CP1 コンパレータ

40 スイッチ切替回路

41 電圧リファレンス回路

42 第1ラッチ

43,44 アンドゲート

45 インバータ

46 切替回路

47 切替制限回路

48 第2ラッチ

CP2 コンパレータ

55 基準電圧生成回路

56 オアゲート

Tr1 第1スイッチ(第1スイッチ手段)

Tr2 第2スイッチ(第2スイッチ手段)

Vd1 低駆動電圧

Claims (5)

- 発電手段と、

該発電手段に対してそれぞれ並列に接続された第1蓄電手段、該第1蓄電手段より容量の小さな第2蓄電手段、および、装置の機能を実現する機能回路と、

閉成状態から開成状態に切り替わることで、前記機能回路および前記第2蓄電手段を前記発電手段および前記第1蓄電手段から切り離すことが可能な第1スイッチ手段と、

閉成状態から開成状態に切り替わることで、前記第1蓄電手段を前記発電手段、前記第2蓄電手段および前記機能回路から切り離すことが可能な第2スイッチ手段と、

前記第1蓄電手段の端子電圧と前記第2蓄電手段の端子電圧とを比較する第1比較器と、

前記機能回路を駆動可能な電源電圧である第1閾値電圧と前記第2蓄電手段の端子電圧とを比較する第2比較器と、

前記第1比較器の出力に基づき前記第1スイッチ手段と前記第2スイッチ手段との切り替えを制御する論理手段と、

を備え、

前記論理手段は、

前記第1蓄電手段の端子電圧が前記第2蓄電手段の端子電圧より大きい場合に前記第1スイッチ手段を閉成状態に、前記第2スイッチ手段を開成状態に切り替えるとともに、

前記第1蓄電手段の端子電圧が前記第2蓄電手段の端子電圧より小さい場合に前記第1スイッチ手段を開成状態に、前記第2スイッチ手段を閉成状態に切り替え、

前記第2比較器の出力に基づき前記第2蓄電手段の端子電圧が前記第1閾値電圧より低い場合に、前記第1比較器の出力に基づく前記第1スイッチ手段の切り替え制御を解除して、前記第2スイッチ手段を閉成状態とすることを特徴とする電子装置。 - 前記第1蓄電手段の充電レベルを検出する検出手段と、

前記第1比較器の比較する電圧の切り替え及び前記第2比較器の作用の切り替えを行う第1制御手段と、を備え、

前記第1制御手段は、

前記検出手段の検出に基づき前記第1蓄電手段の充電レベルが通常使用レベルにある場合には前記第1比較器に前記第1蓄電手段の端子電圧と前記第2蓄電手段の端子電圧とを比較させ、前記第2比較器の出力信号を出力させる一方、前記第1蓄電手段の充電レベルが当該第1蓄電手段の放電を制限するチャージレベルにある場合に前記第1比較器に前記第2蓄電手段の端子電圧と電圧リファレンス回路から供給される電圧とを比較させ、前記第2比較器の出力信号に係わらず所定の信号を出力させることを特徴とする請求項1記載の電子装置。 - 前記第1スイッチ手段と前記第2スイッチ手段とを強制的に閉成状態に切り替えることが可能な第2制御手段を備え、

前記第2制御手段は、

前記機能回路の負荷が大きくなる所定の動作モードのときに前記第1スイッチ手段と前記第2スイッチ手段とを強制的に閉成状態にすることを特徴とする請求項1〜2の何れか一項に記載の電子装置。 - 前記第1蓄電手段は二次電池であり、

前記第2蓄電手段はコンデンサであることを特徴とする請求項1〜3の何れか一項に記載の電子装置。 - 前記機能回路は、時計機能に関わる動作を行うことを特徴とする請求項1〜4の何れか一項に記載の電子装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009152037A JP5458692B2 (ja) | 2009-06-26 | 2009-06-26 | 電子装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009152037A JP5458692B2 (ja) | 2009-06-26 | 2009-06-26 | 電子装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011010478A JP2011010478A (ja) | 2011-01-13 |

| JP2011010478A5 JP2011010478A5 (ja) | 2012-07-26 |

| JP5458692B2 true JP5458692B2 (ja) | 2014-04-02 |

Family

ID=43566460

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009152037A Active JP5458692B2 (ja) | 2009-06-26 | 2009-06-26 | 電子装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5458692B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6314002B2 (ja) * | 2014-03-07 | 2018-04-18 | 旭化成エレクトロニクス株式会社 | 切り替え回路およびモニタ回路 |

| WO2016031395A1 (ja) * | 2014-08-28 | 2016-03-03 | シャープ株式会社 | 電子機器およびその制御方法 |

| CN107248771A (zh) * | 2017-08-10 | 2017-10-13 | 温州大学 | 新能源供电的蓄电池保护系统及其方法 |

| JP7081349B2 (ja) * | 2018-07-04 | 2022-06-07 | 株式会社リコー | 制御システム、制御システムによる制御方法、及びプログラム |

| JP7124661B2 (ja) * | 2018-11-15 | 2022-08-24 | 富士通株式会社 | 電源装置及び通信装置 |

| JP7082562B2 (ja) * | 2018-11-21 | 2022-06-08 | ルネサスエレクトロニクス株式会社 | 制御システム、半導体装置及び半導体装置の製造方法 |

| WO2023190966A1 (ja) * | 2022-03-31 | 2023-10-05 | シチズン時計株式会社 | 電子時計 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63161390U (ja) * | 1987-04-10 | 1988-10-21 | ||

| JPH1175322A (ja) * | 1997-08-29 | 1999-03-16 | S I I R D Center:Kk | 充電制御回路 |

-

2009

- 2009-06-26 JP JP2009152037A patent/JP5458692B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011010478A (ja) | 2011-01-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5458692B2 (ja) | 電子装置 | |

| US8873344B2 (en) | Power consumption control device, timepiece device, electronic device, power consumption control method, power consumption control program | |

| JP5260706B2 (ja) | 計時回路を備える携帯式電子機器の電力システム | |

| US6510400B1 (en) | Temperature control circuit for central processing unit | |

| US7876144B2 (en) | Start-up circuit and start-up method | |

| US9841805B2 (en) | Power management circuit and electronic device employing the same | |

| US8963625B2 (en) | Semiconductor device driven by a main power supply voltage and an auxiliary power supply voltage | |

| US20100182880A1 (en) | Electronic timepiece | |

| JP4678056B2 (ja) | 電子時計 | |

| JP2012145558A (ja) | 制御装置、電子機器、時計装置、及び制御方法 | |

| EP1542099B1 (en) | Electronic clock | |

| CN106998081B (zh) | 电子装置及其充放电管理方法 | |

| JP6610048B2 (ja) | 半導体装置および電子時計 | |

| JP4353081B2 (ja) | 電子機器及びその制御方法 | |

| JP5465022B2 (ja) | 電子回路 | |

| JP2013233008A (ja) | 電源装置 | |

| JP2002034148A (ja) | 電子機器およびその制御方法 | |

| JP2001099964A (ja) | 電子時計および電子時計の制御方法 | |

| US11223221B2 (en) | Power management | |

| JP2008241540A (ja) | 電子時計 | |

| JP2010230508A (ja) | 時計用電子回路 | |

| JP2012095448A (ja) | 二次電池の充電回路および充電方式 | |

| JP2000332585A (ja) | 発振検出回路、半導体装置、電子機器および発振検出方法 | |

| JP2000266872A (ja) | 計時装置および計時装置の制御方法 | |

| JP2003172788A (ja) | 電子時計 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120608 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120608 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120608 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131002 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131008 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131217 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131230 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5458692 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |