JP5448496B2 - 情報処理装置及びその制御方法 - Google Patents

情報処理装置及びその制御方法 Download PDFInfo

- Publication number

- JP5448496B2 JP5448496B2 JP2009037056A JP2009037056A JP5448496B2 JP 5448496 B2 JP5448496 B2 JP 5448496B2 JP 2009037056 A JP2009037056 A JP 2009037056A JP 2009037056 A JP2009037056 A JP 2009037056A JP 5448496 B2 JP5448496 B2 JP 5448496B2

- Authority

- JP

- Japan

- Prior art keywords

- cpu

- memory

- control means

- storage

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0284—Multiple user address space allocation, e.g. using different base addresses

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/28—Using a specific disk cache architecture

- G06F2212/283—Plural cache memories

- G06F2212/284—Plural cache memories being distributed

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/31—Providing disk cache in a specific location of a storage system

- G06F2212/311—In host system

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Facsimiles In General (AREA)

Description

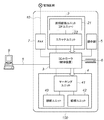

第1ボードと、第2ボードとを有する情報処理装置であって、

前記第1ボードは、

第1制御手段と、

前記第1制御手段のワークメモリとして使用される第1記憶手段とを有し、

前記第2ボードは、

第2制御手段と、

不揮発性の第2記憶手段とを有し、

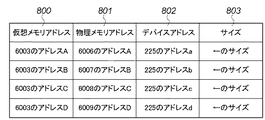

前記第1制御手段は、オペレーティングシステムが管理する仮想メモリ空間を介して前記第2記憶手段に記憶されたデータにアクセスし、

前記第1制御手段は、前記仮想メモリ空間のアドレスと、前記第1記憶手段の物理アドレスと、前記第2記憶手段の物理アドレスとの対応関係を示す情報を作成して当該情報を前記第2制御手段へ転送し、

前記第2制御手段は、前記情報に基づいて、前記第2記憶手段に記憶されたデータを前記第1記憶手段へ転送することを特徴とする。

以上、本発明の実施形態について詳述したが、本発明は、複数の機器から構成されるシステムに適用しても良いし、また一つの機器からなる装置に適用しても良い。

Claims (4)

- 第1ボードと、第2ボードとを有する情報処理装置であって、

前記第1ボードは、

第1制御手段と、

前記第1制御手段のワークメモリとして使用される第1記憶手段とを有し、

前記第2ボードは、

第2制御手段と、

不揮発性の第2記憶手段とを有し、

前記第1制御手段は、オペレーティングシステムが管理する仮想メモリ空間を介して前記第2記憶手段に記憶されたデータにアクセスし、

前記第1制御手段は、前記仮想メモリ空間のアドレスと、前記第1記憶手段の物理アドレスと、前記第2記憶手段の物理アドレスとの対応関係を示す情報を作成して当該情報を前記第2制御手段へ転送し、

前記第2制御手段は、前記情報に基づいて、前記第2記憶手段に記憶されたデータを前記第1記憶手段へ転送することを特徴とする情報処理装置。 - 前記第1制御手段は、前記オペレーティングシステムの起動が完了し、前記第2制御手段による前記第1記憶手段へのデータの転送が完了した場合に、アプリケーションの実行を開始することを特徴とする請求項1に記載の情報処理装置。

- 前記第2制御手段は、前記第1記憶手段に記憶されるキャッシュデータと前記第2記憶手段に記憶されるデータを同期させる同期イベントの発行に伴って前記第1記憶手段へのデータの転送を実行することを特徴とする請求項1に記載の情報処理装置。

- 第1制御手段と、前記第1制御手段のワークメモリとして使用される第1記憶手段とを有する第1ボードと、第2制御手段と、不揮発性の第2記憶手段とを有する第2ボードとを有する情報処理装置を制御する制御方法であって、

前記第1制御手段が、オペレーティングシステムが管理する仮想メモリ空間を介して前記第2記憶手段に記憶されたデータにアクセスするアクセス工程と、

前記第1制御手段が、前記仮想メモリ空間のアドレスと、前記第1記憶手段の物理アドレスと、前記第2記憶手段の物理アドレスとの対応関係を示す情報を作成して当該情報を前記第2制御手段へ転送する第1転送工程と、

前記第2制御手段が、前記情報に基づいて、前記第2記憶手段に記憶されたデータを前記第1記憶手段へ転送する第2転送工程とを有することを特徴とする情報処理装置の制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009037056A JP5448496B2 (ja) | 2009-02-19 | 2009-02-19 | 情報処理装置及びその制御方法 |

| US12/698,750 US8281073B2 (en) | 2009-02-19 | 2010-02-02 | Information processing apparatus and method of controlling same |

| US13/611,263 US20130007367A1 (en) | 2009-02-19 | 2012-09-12 | Information processing apparatus and method of controlling same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009037056A JP5448496B2 (ja) | 2009-02-19 | 2009-02-19 | 情報処理装置及びその制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010191818A JP2010191818A (ja) | 2010-09-02 |

| JP2010191818A5 JP2010191818A5 (ja) | 2012-04-05 |

| JP5448496B2 true JP5448496B2 (ja) | 2014-03-19 |

Family

ID=42560877

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009037056A Expired - Fee Related JP5448496B2 (ja) | 2009-02-19 | 2009-02-19 | 情報処理装置及びその制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8281073B2 (ja) |

| JP (1) | JP5448496B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5340058B2 (ja) * | 2009-06-30 | 2013-11-13 | キヤノン株式会社 | 画像処理装置、その制御方法及びプログラム |

| DE102011088416A1 (de) | 2010-12-16 | 2012-06-21 | Canon K. K. | Informationsverarbeitungsvorrichtung zur geeigneten ausführung einer herunterfahrverarbeitung, verfahren zur steuerung der informationsverarbeitungsvorrichtung und speichermedium |

| US9958926B2 (en) * | 2011-12-13 | 2018-05-01 | Intel Corporation | Method and system for providing instant responses to sleep state transitions with non-volatile random access memory |

| JP6041522B2 (ja) * | 2012-04-18 | 2016-12-07 | キヤノン株式会社 | 情報処理装置、情報処理装置の制御方法、プログラム及び記憶媒体 |

| US9009392B2 (en) * | 2012-04-25 | 2015-04-14 | International Business Machines Corporation | Leveraging a hybrid infrastructure for dynamic memory allocation and persistent file storage |

| JP2016208453A (ja) * | 2015-04-28 | 2016-12-08 | キヤノン株式会社 | 画像形成装置、画像形成装置の制御方法、及びプログラム |

| JP2019142095A (ja) * | 2018-02-20 | 2019-08-29 | 京セラドキュメントソリューションズ株式会社 | 画像形成装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5338937A (en) * | 1976-09-22 | 1978-04-10 | Hitachi Ltd | Address conversion mechanism of electronic computer system |

| JPS57162164A (en) * | 1981-03-30 | 1982-10-05 | Nec Corp | Data transfer device |

| JP3369580B2 (ja) * | 1990-03-12 | 2003-01-20 | ヒューレット・パッカード・カンパニー | 直接メモリアクセスを行うためのインターフェース装置及び方法 |

| JPH07244614A (ja) | 1994-03-02 | 1995-09-19 | Fanuc Ltd | メモリアクセス方式 |

| US5878198A (en) | 1994-12-21 | 1999-03-02 | Canon Kabushiki Kaisha | Information processing apparatus and method and memory medium storing information processing program |

| US6092170A (en) * | 1996-11-29 | 2000-07-18 | Mitsubishi Denki Kabushiki Kaisha | Data transfer apparatus between devices |

| JP3578265B2 (ja) | 1999-11-19 | 2004-10-20 | 日本電気株式会社 | 不揮発性メモリへのデータ書き込み方法および情報処理装置ならびに記録媒体 |

| JP2001166993A (ja) * | 1999-12-13 | 2001-06-22 | Hitachi Ltd | 記憶制御装置およびキャッシュメモリの制御方法 |

| JP4054503B2 (ja) | 2000-01-06 | 2008-02-27 | キヤノン株式会社 | 画像処理装置 |

| US6829692B2 (en) * | 2001-09-14 | 2004-12-07 | Intel Corporation | System and method for providing data to multi-function memory |

| US6804741B2 (en) * | 2002-01-16 | 2004-10-12 | Hewlett-Packard Development Company, L.P. | Coherent memory mapping tables for host I/O bridge |

| JP2004152004A (ja) | 2002-10-30 | 2004-05-27 | Canon Inc | 画像処理装置 |

| JP4376040B2 (ja) * | 2003-11-27 | 2009-12-02 | 株式会社日立製作所 | 複数のプロセッサを用いて情報処理を行う装置及び方法 |

| JP4516322B2 (ja) * | 2004-01-28 | 2010-08-04 | 株式会社日立製作所 | 複数の上位装置で共有される記憶装置システムを持つサイト間での共有排他制御方式を備えたコンピュータシステム |

| JP2008102850A (ja) * | 2006-10-20 | 2008-05-01 | Toshiba Corp | 情報処理装置及び情報処理方法 |

-

2009

- 2009-02-19 JP JP2009037056A patent/JP5448496B2/ja not_active Expired - Fee Related

-

2010

- 2010-02-02 US US12/698,750 patent/US8281073B2/en not_active Expired - Fee Related

-

2012

- 2012-09-12 US US13/611,263 patent/US20130007367A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010191818A (ja) | 2010-09-02 |

| US8281073B2 (en) | 2012-10-02 |

| US20100211743A1 (en) | 2010-08-19 |

| US20130007367A1 (en) | 2013-01-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5448496B2 (ja) | 情報処理装置及びその制御方法 | |

| KR101562973B1 (ko) | 메모리 장치 및 메모리 장치의 동작 방법 | |

| CN100555257C (zh) | 处理页面复制期间的dma操作的存储控制器和方法 | |

| JP4361073B2 (ja) | 画像処理装置とその制御方法 | |

| US20080235477A1 (en) | Coherent data mover | |

| JP5783809B2 (ja) | 情報処理装置、起動方法およびプログラム | |

| JP5959958B2 (ja) | 記憶装置及び記憶装置におけるデータ消去方法 | |

| JP2007183961A (ja) | ハードディスクドライブキャッシュメモリ及び再生デバイス | |

| JP2008077144A (ja) | 仮想化システム、メモリ管理方法及び制御プログラム | |

| JP6875808B2 (ja) | 情報処理装置 | |

| JP2006202252A (ja) | 電子機器、データ処理方法、及びコンピュータプログラム | |

| JP5078671B2 (ja) | 情報処理装置、情報処理システム及び情報処理方法 | |

| JP7267692B2 (ja) | ファームウェアを更新する画像形成装置 | |

| JP5578811B2 (ja) | 情報処理装置、情報処理装置の制御方法及びプログラム | |

| JP5060241B2 (ja) | 情報処理装置及びその制御方法 | |

| JP4567966B2 (ja) | エミュレーションシステムおよびエミュレーション方法 | |

| JP2018063676A (ja) | 情報処理装置及びその制御方法、並びにプログラム | |

| JP2001134486A (ja) | マイクロプロセッサおよび記憶装置 | |

| JP2015215684A (ja) | 情報処理装置及び情報処理プログラム | |

| JP5334048B2 (ja) | メモリ装置および計算機 | |

| JP2004220575A (ja) | カード型メモリのインターフェース回路、その回路を搭載したasic、及びそのasicを搭載した画像形成装置 | |

| JP2011138401A (ja) | プロセッサシステム、プロセッサシステムの制御方法、及び制御回路 | |

| JPH11194973A (ja) | 画像情報処理装置、その制御方法および記録媒体 | |

| JP4965974B2 (ja) | 半導体集積回路装置 | |

| JP2000259362A (ja) | プリンタ及びプリンタのデータ処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120220 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130613 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130621 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130909 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131224 |

|

| LAPS | Cancellation because of no payment of annual fees |