JP5264640B2 - 積層型半導体装置及びその製造方法 - Google Patents

積層型半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP5264640B2 JP5264640B2 JP2009173037A JP2009173037A JP5264640B2 JP 5264640 B2 JP5264640 B2 JP 5264640B2 JP 2009173037 A JP2009173037 A JP 2009173037A JP 2009173037 A JP2009173037 A JP 2009173037A JP 5264640 B2 JP5264640 B2 JP 5264640B2

- Authority

- JP

- Japan

- Prior art keywords

- jig

- opening

- common electrode

- semiconductor device

- chip structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/45124—Aluminium (Al) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Description

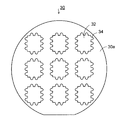

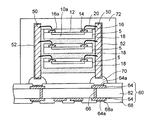

本発明の実施形態を説明する前に、本発明に関連する関連技術の問題点について説明する。図1は関連技術の積層型半導体装置を示す断面図である。

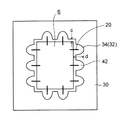

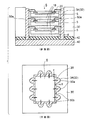

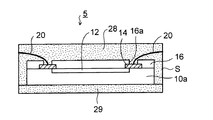

図2〜図12は本発明の第1実施形態の積層型半導体装置の製造方法を示す断面図(一部平面図)、図13は同じく積層型半導体装置を示す断面図及び平面図である。

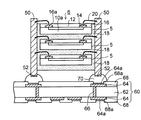

図18〜図25は本発明の第2実施形態の積層型半導体装置の製造方法を示す断面図、図26は同じく積層型半導体装置を示す断面図及び平面図である。

Claims (10)

- 複数の接続パッドと該接続パッドにそれぞれ接続されて外側に延在する複数のワイヤ端子とを備えた半導体チップが積層されて、前記積層された半導体チップの間及び側面に絶縁層が形成された積層チップ構造体と、

垂直方向に並んで配置された前記ワイヤ端子に対応する部分の前記積層チップ構造体の側面に、前記絶縁層から外側に突出して形成された複数の共通電極と

を有し、

前記複数の共通電極は相互に分離されており、前記共通電極は電解金属めっき層から形成され、前記ワイヤ端子が前記電解金属めっき層に直接接続されており、かつ、

前記共通電極は、前記積層チップ構造体の下面から外部に延在していることを特徴とする積層型半導体装置。 - 前記ワイヤ端子は前記半導体チップの側方の前記絶縁層から外側に延在しており、

前記ワイヤ端子の先端部が前記共通電極の中に配置されていることを特徴とする請求項1に記載の積層型半導体装置。 - 最上の前記半導体チップの上面に前記絶縁層がさらに形成されており、全ての前記ワイヤ端子が前記絶縁層にそれぞれ埋め込まれており、かつ

前記ワイヤ端子の先端面は前記半導体チップの側方の前記絶縁層の外面と同一位置に配置され、

前記ワイヤ端子の先端面が前記共通電極に接続されていることを特徴とする請求項1に記載の積層型半導体装置。 - 前記共通電極は、銅からなることを特徴とする請求項1乃至3のいずれか一項に記載の積層型半導体装置。

- めっき給電部材の上に開口部が設けられた治具を配置し、前記治具の開口部に、接続パッドと該接続パッドに接続されて外側に延在するワイヤ端子とを備えた半導体チップが積層されて、前記積層された半導体チップの間及び側面に絶縁層が形成された積層チップ構造体を形成する工程であって、前記治具の開口部は前記ワイヤ端子に対応する部分に外側に突出する突出開口部を備え、

前記めっき給電部材をめっき給電経路に利用する電解めっきにより、前記積層チップ構造体と前記治具の突出開口部の側面との間隔に外側に突出する突出金属部を充填することに基づいて、垂直方向に並んで配置された複数の前記ワイヤ端子に接続される共通電極を得る工程と、

前記めっき給電部材及び前記治具を前記積層チップ構造体から除去する工程とを有することを特徴とする積層型半導体装置の製造方法。 - 前記治具の開口部に前記積層チップ構造体を形成する工程において、

前記積層チップ構造体と前記治具の突出開口部以外の開口部の側面との間にクリアランスが存在し、

前記共通電極を得る工程において、

前記クリアランス上の前記積層チップ構造体の側面に前記突出金属部に繋がる繋り部が同時に形成され、

前記めっき給電部材及び前記治具を除去する工程の後に、

前記突出金属部及び前記繋り部を、外面から前記繋り部が消失するまでエッチングすることにより、前記共通電極を得る工程をさらに有することを特徴とする請求項5に記載の積層型半導体装置の製造方法。 - 前記治具の開口部に前記積層チップ構造体を形成する工程において、

前記積層チップ構造体と前記治具の突出開口部以外の開口部の側面との間にクリアランスが存在し、

前記共通電極を得る工程の前に、

前記積層チップ構造体と前記治具の開口部の側面との隙間に前記積層チップ構造体の上部まで樹脂体を充填する工程と、

前記積層チップ構造体と前記治具の突出開口部の側面との間隔に充填された前記樹脂体を除去して前記めっき給電部材を露出させ、前記クリアランスに充填された前記樹脂体を残す工程とをさらに有することを特徴とする請求項5に記載の積層型半導体装置の製造方法。 - 前記治具の開口部に前記積層チップ構造体を形成する工程において、

前記ワイヤ端子は前記半導体チップの側方の前記絶縁層から外側に延在しており、

前記共通電極を形成する工程において、

前記ワイヤ端子の先端部が前記突出開口部の中に配置されることを特徴とする請求項5又は6に記載の積層型半導体装置の製造方法。 - 前記治具の開口部に前記積層チップ構造体を形成する工程において、

最上の前記半導体チップの上面に前記絶縁層がさらに形成されおり、全ての前記ワイヤ端子は前記絶縁層にそれぞれ埋め込まれており、かつ

前記ワイヤ端子の先端面は前記半導体チップの側方の前記絶縁層の外面と同一位置に配置され、

前記共通電極を形成する工程において、

前記ワイヤ端子の先端面が前記共通電極に接続されることを特徴とする請求項5又は6に記載の積層型半導体装置の製造方法。 - 前記共通電極は、銅から形成されることを特徴とする請求項5又は6に記載の積層型半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009173037A JP5264640B2 (ja) | 2009-07-24 | 2009-07-24 | 積層型半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009173037A JP5264640B2 (ja) | 2009-07-24 | 2009-07-24 | 積層型半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011029370A JP2011029370A (ja) | 2011-02-10 |

| JP2011029370A5 JP2011029370A5 (ja) | 2012-07-12 |

| JP5264640B2 true JP5264640B2 (ja) | 2013-08-14 |

Family

ID=43637784

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009173037A Active JP5264640B2 (ja) | 2009-07-24 | 2009-07-24 | 積層型半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5264640B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6727111B2 (ja) * | 2016-12-20 | 2020-07-22 | 新光電気工業株式会社 | 半導体装置及びその製造方法 |

| CN111081687B (zh) * | 2019-12-16 | 2022-02-01 | 东莞记忆存储科技有限公司 | 一种堆叠式芯片封装结构及其封装方法 |

| US20230156997A1 (en) * | 2020-04-03 | 2023-05-18 | Ultramemory Inc. | Memory unit, semiconductor module, dimm module, and manufacturing method for same |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2670323B1 (fr) * | 1990-12-11 | 1997-12-12 | Thomson Csf | Procede et dispositif d'interconnexion de circuits integres en trois dimensions. |

| US5466634A (en) * | 1994-12-20 | 1995-11-14 | International Business Machines Corporation | Electronic modules with interconnected surface metallization layers and fabrication methods therefore |

| KR100379835B1 (ko) * | 1998-12-31 | 2003-06-19 | 앰코 테크놀로지 코리아 주식회사 | 반도체패키지및그제조방법 |

| JP3476383B2 (ja) * | 1999-05-27 | 2003-12-10 | シャープ株式会社 | 半導体積層パッケージ |

| JP2009071095A (ja) * | 2007-09-14 | 2009-04-02 | Spansion Llc | 半導体装置の製造方法 |

-

2009

- 2009-07-24 JP JP2009173037A patent/JP5264640B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011029370A (ja) | 2011-02-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9953914B2 (en) | Substrate-less stackable package with wire-bond interconnect | |

| US8659151B2 (en) | Semiconductor device and manufacturing method thereof | |

| KR101734882B1 (ko) | 영역 어레이 유닛 컨넥터를 갖는 적층 가능한 몰딩된 마이크로전자 패키지 | |

| JP3960479B1 (ja) | 両面電極構造の半導体装置の製造方法 | |

| JP5942823B2 (ja) | 電子部品装置の製造方法、電子部品装置及び電子装置 | |

| US10229892B2 (en) | Semiconductor package and method for manufacturing a semiconductor package | |

| KR20100087329A (ko) | 칩 스케일 적층형 다이 패키지 | |

| US9029199B2 (en) | Method for manufacturing semiconductor device | |

| JP6770853B2 (ja) | リードフレーム及び電子部品装置とそれらの製造方法 | |

| KR20040092435A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2009099697A (ja) | 半導体装置及びその製造方法 | |

| KR101538541B1 (ko) | 반도체 디바이스 | |

| JP2006128455A (ja) | 半導体装置およびその製造方法 | |

| JP2010263080A (ja) | 半導体装置 | |

| US7964493B2 (en) | Method of manufacturing semiconductor device | |

| JP5264640B2 (ja) | 積層型半導体装置及びその製造方法 | |

| JP2005286057A (ja) | 回路装置およびその製造方法 | |

| JP4334397B2 (ja) | 半導体装置及びその製造方法 | |

| JP4577316B2 (ja) | 半導体装置の製造方法 | |

| JP2006100666A (ja) | 半導体装置及びその製造方法 | |

| JP4979661B2 (ja) | 半導体装置の製造方法 | |

| TW200935572A (en) | Semiconductor chip packaging body and its packaging method | |

| JP2016046509A (ja) | プリント配線板および半導体パッケージ | |

| JP4168494B2 (ja) | 半導体装置の製造方法 | |

| JP4751585B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120523 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120523 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130405 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130423 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130430 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5264640 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |