JP5238564B2 - プリディストータ - Google Patents

プリディストータ Download PDFInfo

- Publication number

- JP5238564B2 JP5238564B2 JP2009065890A JP2009065890A JP5238564B2 JP 5238564 B2 JP5238564 B2 JP 5238564B2 JP 2009065890 A JP2009065890 A JP 2009065890A JP 2009065890 A JP2009065890 A JP 2009065890A JP 5238564 B2 JP5238564 B2 JP 5238564B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- lookup table

- distortion compensation

- distortion

- predistorter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Transmitters (AREA)

- Amplifiers (AREA)

Description

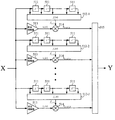

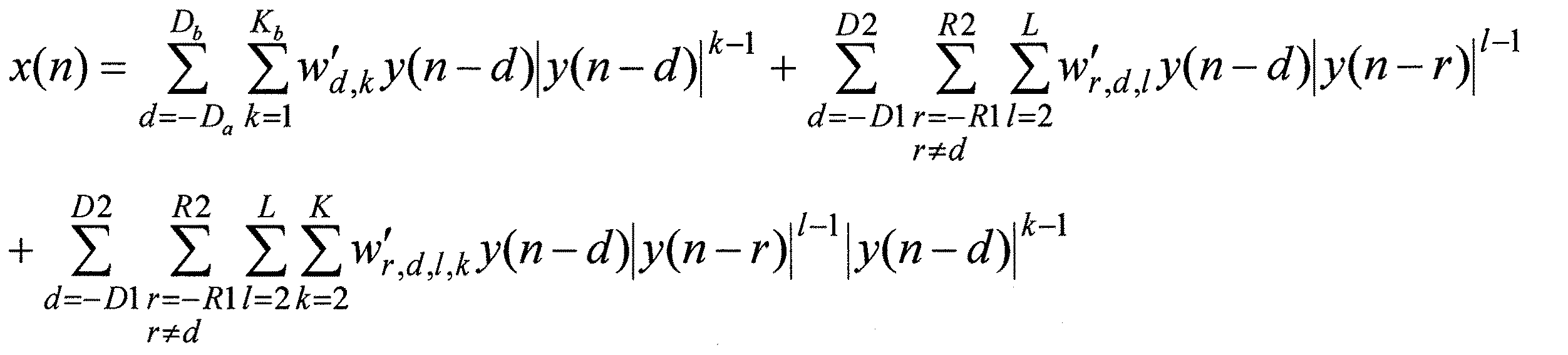

次に、プリディストータ301のルックアップテーブル23の詳細について説明する。図4は複数の増幅器で構成された増幅回路をモデル化した図であり、入力信号Xが入力され出力信号Yを出力する。ここで、入力信号X、および出力信号Yをともに周期Tsでサンプリングした離散時間信号をそれぞれx(nTs)、およびy(nTs)とし、表記を簡単にするためにそれぞれx(n)、およびy(n)で表すこととする。また、x(n)およびy(n)はともに実数成分と虚数成分を持つ複素数信号であり、x(n)およびy(n)に対する乗算、および加算は、それぞれ複素乗算、および複素加算を示すものとする。すなわち、先に説明した図1、及び図2においては、歪補償回路11には複素数信号が入力され、歪補償回路11と被補償回路401の間には図示しない直交変調器、D/A変換器、およびアップコンバータがあり、被補償回路401と制御部13の間には図示しないダウンコンバータ、A/D変換器、および直交復調器がある。図4のようにモデル化された増幅器の歪補償値を得るのに、複数のルックアップテーブルを用いる。すなわち、増幅器を構成する要素増幅器の歪特性を表す歪特性多項式を

j:要素増幅器の番号

J:要素増幅器の総数

r:正規化先行時間、または正規化遅延時間

R1j:j番目要素増幅器に対応する合成多項式の最大の正規化先行時間

R2j:j番目要素増幅器に対応する合成多項式の最大の正規化遅延時間

d:入力信号の正規化先行時間、または正規化遅延時間

D1j:j番目要素増幅器の最大の正規化先行時間

D2j:j番目要素増幅器の最大の正規化遅延時間

l:要素増幅器の合成多項式の次数

Lj:j番目要素増幅器の合成多項式の最大次数

k:要素増幅器の歪特性多項式の次数

Kj:j番目要素増幅器の歪多項式の最大次数

y(n)=Gx(n)

となり、線形であるのが理想的である。但し、Gは増幅装置の利得を表す実数定数である。ここでは、以降の議論を簡単にする目的で、G=1とおくこととする。

しかし、増幅回路の歪補償が十分でなければ、y(n)=x(n)とはならず、

例えば、0≦|x|≦8191を満たす全ての整数値である。

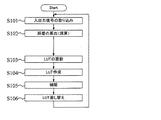

まず、従来のルックアップテーブルの更新方法について説明する。図7は、従来のプリディストータのルックアップテーブルの更新方法を説明するフローチャートである。ステップS101で、入力信号及び出力信号をサンプリングする。ステップS102で、入力信号と出力信号との差分を計算して誤差を算出する。ステップS103で、ステップS102で算出した誤差を小さくするようにルックアップテーブルを更新し、ステップS104で新たなルックアップテーブルを作成する。ステップS105で、歪補償値が存在しないアドレスの歪補償値を隣接するアドレスの歪補償値で直線補間し、当該アドレスの歪補償値を直線補間した値から取得する。更に、ステップS105では入力信号の振幅値(または電力値)の量子化ステップをさらに細かく設定したアドレスに対する歪補償値を直線補間した値から取得する。ステップS106で、当該アドレスを補間した歪補償値を用いたルックアップテーブルに差し替える。

Δw(i)=(Δw0(i),Δw1(i),・・・,ΔwK(i))T

である。

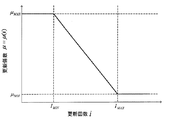

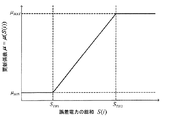

本発明では更新回数、または誤差信号e(i(N+M)+n)の電力に応じて更新係数μを適応的に変化させる。例えば、本発明の例として更新係数μを更新回数に応じて変化させる場合には、更新係数を

11:歪補償回路

13:制御部

21:遅延素子

22:強度算出部

23、23−0、23−5、23−11、23−13:ルックアップテーブル

23−1D:一変数ルックアップテーブル

23−2D:二変数ルックアップテーブル

23−MD:多変数ルックアップテーブル

24:複素乗算器

27:遅延部

31:遅延部

32、32−0、32−5、32−11、32−13:歪信号生成部

33:歪補償値生成部

401:被補償回路

511:遅延素子

512−j:振幅値関数(jは自然数)

513:要素増幅器

514:複素乗算器

515:積算器

X:入力信号

Y:出力信号

A:予歪補償信号

S、S−0、S−5、S−9、S−11、S−13:サンプリング信号

H、H−0、0,H−9,5、H−11,17:歪信号

Claims (4)

- ルックアップテーブルが入力信号に基づいて生成した予歪補償信号を被補償回路へ出力する歪補償回路と、

前記入力信号及び前記被補償回路の出力信号が入力され、前記ルックアップテーブルが前記入力信号に基づいて生成した歪補償値と前記入力信号とから計算した入力計算信号と、前記ルックアップテーブルが前記出力信号に基づいて生成した歪補償値と前記出力信号とから計算した出力計算信号との差分から誤差ルックアップテーブル内の全ての値を計算し、前記誤差ルックアップテーブルを前記ルックアップテーブルに加算して前記ルックアップテーブル内の全ての値を更新する制御部と、

を備えるプリディストータ。 - ルックアップテーブルが入力信号に基づいて生成した予歪補償信号を被補償回路へ出力する歪補償回路と、

前記予歪補償信号及び前記被補償回路の出力信号が入力され、前記予歪補償信号と前記ルックアップテーブルが前記出力信号に基づいて生成した出力計算信号との差分から誤差ルックアップテーブル内の全ての値を計算し、前記誤差ルックアップテーブルを前記ルックアップテーブルに加算して前記ルックアップテーブル内の全ての値を更新する制御部と、

を備えるプリディストータ。 - 前記制御部は、前記ルックアップテーブルを更新する際に前記誤差ルックアップテーブルに乗じる更新係数を、前記ルックアップテーブルを更新した回数に基づいて決定することを特徴とする請求項1又は2に記載のプリディストータ。

- 前記制御部は、前記ルックアップテーブルを更新する際に前記誤差ルックアップテーブルに乗じる更新係数を、前記予歪補償信号と前記計算信号との差分に基づいて決定することを特徴とする請求項1又は2に記載のプリディストータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009065890A JP5238564B2 (ja) | 2009-03-18 | 2009-03-18 | プリディストータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009065890A JP5238564B2 (ja) | 2009-03-18 | 2009-03-18 | プリディストータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010220004A JP2010220004A (ja) | 2010-09-30 |

| JP5238564B2 true JP5238564B2 (ja) | 2013-07-17 |

Family

ID=42978332

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009065890A Active JP5238564B2 (ja) | 2009-03-18 | 2009-03-18 | プリディストータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5238564B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5706129B2 (ja) * | 2010-10-25 | 2015-04-22 | 日本無線株式会社 | プリディストータ |

| JP7809427B2 (ja) * | 2022-02-24 | 2026-02-02 | 日本無線株式会社 | 歪補償装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3876408B2 (ja) * | 2001-10-31 | 2007-01-31 | 富士通株式会社 | 歪補償装置及び歪補償方法 |

| JP2004172676A (ja) * | 2002-11-15 | 2004-06-17 | Japan Radio Co Ltd | 歪補償方法 |

| KR100518456B1 (ko) * | 2003-10-10 | 2005-09-30 | 학교법인 포항공과대학교 | 전력 증폭기의 선형화를 위한 디지털 피드백 선형화 장치및 방법 |

| JP4308163B2 (ja) * | 2005-03-22 | 2009-08-05 | 富士通株式会社 | 歪補償装置 |

-

2009

- 2009-03-18 JP JP2009065890A patent/JP5238564B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010220004A (ja) | 2010-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5120178B2 (ja) | 非線形システム逆特性同定装置及びその方法、電力増幅装置及び電力増幅器のプリディストータ | |

| JP5753272B2 (ja) | タップ出力の正規化を伴う非線形モデル | |

| US20140314176A1 (en) | Non-Linear Modeling of a Physical System Using Two-Dimensional Look-Up Table with Bilinear Interpolation | |

| US8933752B2 (en) | Power amplifier apparatus, distortion compensation coefficient updating method, and transmission apparatus | |

| JP5751056B2 (ja) | 歪補償装置、送信機および歪補償方法 | |

| US8451055B2 (en) | Distortion compensating apparatus, transmitting apparatus, and distortion compensating method | |

| JP4909261B2 (ja) | 電力増幅器におけるモデルに基づく歪み低減 | |

| US20120128098A1 (en) | Apparatus and method for digital predistortion of non-linear amplifiers | |

| JP6054739B2 (ja) | 歪み補償装置及び歪み補償方法 | |

| JP5336134B2 (ja) | プリディストータ | |

| CN102404263B (zh) | 数字预失真处理方法及装置 | |

| JP5299958B2 (ja) | プリディストータ | |

| JP5238564B2 (ja) | プリディストータ | |

| JP5226468B2 (ja) | プリディストータ | |

| JP5706129B2 (ja) | プリディストータ | |

| US9548703B2 (en) | Distortion compensation apparatus, transmission apparatus, and distortion compensation method | |

| JP5160344B2 (ja) | プリディストータ | |

| KR20140073421A (ko) | 고주파 증폭 장치 및 왜곡보상 방법 | |

| JP5663261B2 (ja) | プリディストータ | |

| JP2010124190A (ja) | プリディストータ | |

| JP5221260B2 (ja) | プリディストータ | |

| JP5260335B2 (ja) | プリディストータ | |

| WO2018109862A1 (ja) | 電力増幅回路 | |

| JP2005079935A (ja) | 適応プリディストーション型歪補償電力増幅器 | |

| JP5115979B2 (ja) | プリディストータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130326 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130401 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5238564 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160405 Year of fee payment: 3 |