JP5114569B2 - 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ - Google Patents

回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ Download PDFInfo

- Publication number

- JP5114569B2 JP5114569B2 JP2010526814A JP2010526814A JP5114569B2 JP 5114569 B2 JP5114569 B2 JP 5114569B2 JP 2010526814 A JP2010526814 A JP 2010526814A JP 2010526814 A JP2010526814 A JP 2010526814A JP 5114569 B2 JP5114569 B2 JP 5114569B2

- Authority

- JP

- Japan

- Prior art keywords

- light emitting

- conductor

- emitting element

- circuit board

- wire

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/315—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material

- B41J2/32—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material using thermal heads

- B41J2/335—Structure of thermal heads

- B41J2/33505—Constructional details

- B41J2/3351—Electrode layers

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/315—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material

- B41J2/32—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material using thermal heads

- B41J2/335—Structure of thermal heads

- B41J2/33505—Constructional details

- B41J2/3352—Integrated circuits

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/315—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material

- B41J2/32—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material using thermal heads

- B41J2/335—Structure of thermal heads

- B41J2/33575—Processes for assembling process heads

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/315—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material

- B41J2/32—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of heat to a heat sensitive printing or impression-transfer material using thermal heads

- B41J2/335—Structure of thermal heads

- B41J2/3359—Manufacturing processes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/435—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material

- B41J2/475—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material for heating selectively by radiation or ultrasonic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/4501—Shape

- H01L2224/45012—Cross-sectional shape

- H01L2224/45015—Cross-sectional shape being circular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/485—Material

- H01L2224/48505—Material at the bonding interface

- H01L2224/48599—Principal constituent of the connecting portion of the wire connector being Gold (Au)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

- H01L2224/7825—Means for applying energy, e.g. heating means

- H01L2224/783—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/78301—Capillary

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/852—Applying energy for connecting

- H01L2224/85201—Compression bonding

- H01L2224/85205—Ultrasonic bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/78—Apparatus for connecting with wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/16—Assemblies consisting of a plurality of semiconductor or other solid state devices the devices being of types provided for in two or more different subclasses of H10B, H10D, H10F, H10H, H10K or H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of semiconductor or other solid state devices the devices being of types provided for in two or more different subclasses of H10B, H10D, H10F, H10H, H10K or H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01023—Vanadium [V]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0103—Zinc [Zn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01031—Gallium [Ga]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01032—Germanium [Ge]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01049—Indium [In]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01083—Bismuth [Bi]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/10329—Gallium arsenide [GaAs]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/10336—Aluminium gallium arsenide [AlGaAs]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1301—Thyristor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H29/00—Integrated devices, or assemblies of multiple devices, comprising at least one light-emitting semiconductor element covered by group H10H20/00

- H10H29/10—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00

- H10H29/14—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00 comprising multiple light-emitting semiconductor components

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Health & Medical Sciences (AREA)

- General Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Led Device Packages (AREA)

- Printers Or Recording Devices Using Electromagnetic And Radiation Means (AREA)

Description

本発明は、回路基板、並びに、それを用いた、画像形成装置、サーマルヘッド及びイメージセンサに関する。

近年、回路基板、並びに、それを用いた、画像形成装置、サーマルヘッド及びイメージセンサなどの各種装置の小型化が進んでいる。

これらの小型化を図るためには、回路基板を構成する基板に形成される素子自体も小型にする必要があり、これに伴って導体も小さくなる傾向にある。このとき、ワイヤの径やボンディングツール(キャピラリなど)のサイズも小さいものとなることから、導体とワイヤとの付着力を向上させる事が求められていた。

したがって本発明の目的は、装置を小型化しても、電気的接続の信頼性の高い回路基板、およびそれを用いた、画像形成装置、サーマルヘッド並びにイメージセンサを提供することにある。

本発明の一実施形態に係る回路基板は、基板と、導体と、ワイヤとを具備する。前記導体は、前記基板上に位置し、表面に溝部を有する。前記ワイヤは、前記導体に接続される。前記溝部は、前記ワイヤと前記導体との接続部を、一部の開口を除いて取り囲む。

本発明の他の実施形態に係る画像形成装置は、上記回路基板と、第1の駆動回路と、を含む。

本発明のさらに他の実施形態に係るサーマルヘッドは、上記回路基板と、第2の駆動回路と、を含む。

本発明のさらに他の実施形態に係るイメージセンサは、上記回路基板と、演算回路と、を含む。

本実施形態に係る構成によれば、ワイヤを剥離しにくくすることができるため、接続信頼性が向上し、装置を長寿命化することができる。

本発明の目的、特色、および利点は、下記の詳細な説明と図面とからより明確になるであろう。

以下、図面を参照しつつ本発明の好適な実施形態について詳細に説明する。なお、以下の図面に記載される構成は本発明の実施形態の一例であり、この構成のみに限定されるものではない。

≪回路基板の基本構成について≫

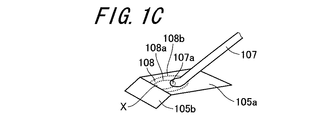

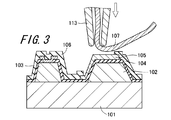

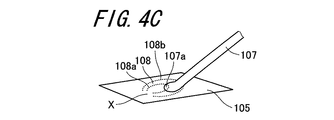

本発明の一実施形態の回路基板は、図4Cに示すように、基板上に位置する導体105と、この導体105に接続(bonding)されるワイヤ107とを具備している。そして、導体105は、その表面に、溝部108を有する。この溝部108は、例えば、図3に示すように、ワイヤ107を導体105に接続する際、キャピラリを導体105に押し付けることで形成される。溝部108は、ワイヤ107と導体105との接続部107a(斜線で示した部分)を、一部の開口Xを除いて取り囲む。ここでいう「溝部が取り囲む」とは、図4Cに示すように、溝部108の外周側の縁部108bおよび開口Xによって囲むことを意味している。この開口Xにおいて溝部108の内側領域と外側領域とが連続している。なお、内側領域とは、前述したような、溝部108によって取り囲まれた領域をいう。

本発明の一実施形態の回路基板は、図4Cに示すように、基板上に位置する導体105と、この導体105に接続(bonding)されるワイヤ107とを具備している。そして、導体105は、その表面に、溝部108を有する。この溝部108は、例えば、図3に示すように、ワイヤ107を導体105に接続する際、キャピラリを導体105に押し付けることで形成される。溝部108は、ワイヤ107と導体105との接続部107a(斜線で示した部分)を、一部の開口Xを除いて取り囲む。ここでいう「溝部が取り囲む」とは、図4Cに示すように、溝部108の外周側の縁部108bおよび開口Xによって囲むことを意味している。この開口Xにおいて溝部108の内側領域と外側領域とが連続している。なお、内側領域とは、前述したような、溝部108によって取り囲まれた領域をいう。

また、図4Bは、図4Aに示した前記接続構造とは異なる導体105とワイヤ107との接続構造を示す。図4Bにおいて導体105は、上面と側面とを有する台座部に設けられている。この実施形態において、導体105は、台座部の上面上に位置するパッド部105aと、台座部の側面上に位置し、パッド部105aと電気的に接続される側面配線部105bとを有している。そして、開口Xが、パッド部105aと側面配線部105bとの境界部に位置している。

本実施形態の構成によれば、下記の理由により、良好な付着力が得られる。以下、本実施形態の作用効果について、図4A〜図4Cを用いて説明する。図4A〜図4Cは、導体とワイヤとの接続構造を示す模式的な斜視図であり、図4Aは、本発明の実施形態には含まない構成、図4Bおよび図4Cは、本発明の実施形態に含まれる構成を示す。なお、溝部108を示す図面において、接続部107aをわかりやすくするために溝部108の幅を大きく示しており、実際の寸法にもとづいて記載されたものではない。

図4Aの構成では、導体205とワイヤ107とが接続部107aを形成しており、ステッチボンディング等のワイヤボンディングの際に生じた溝部208がパッド部205a上に残っている。接続部107aは溝部208によって囲われた領域に存在している。しかしながら、後述する理由により、回路基板を小型化すると溝部208によって囲われた領域は導体205から分断される場合がある。もし分断されてしまった場合、接続部107aは、この溝部208によって囲われた狭い領域の有する付着力によって辛うじてつながっている状態となり、接続部107aが基板から剥離してしまう恐れがある。

これに対して、図4Bに示された実施形態の構成では、パッド部105aとワイヤ107とが接続部107aを形成しており、ワイヤボンディングの際に生じた溝部108がパッド部105a上に存在している点は図4Aの構成と同様である。しかしながら、図4Bに示す実施形態の構成では、パッド部105aと台座部に設けた側面配線部105bとは繋がっており、溝部108の一部が、パッド部105a側の側面配線部105bとの境界で欠けた形状となっている(溝部108が途切れ、開口Xを形成している)。この構成によれば、接続部107aが設けられているパッド部105aの領域は、溝部108に囲われた領域だけではなく、この領域につながって設けられている側面配線部105bともつながっている。したがって、溝部108がパッド部105aの上では分断されてしまっていたとしても、完全には周囲と分離されず、側面配線部105bとつながっているため、図4Aに示された構成に比べて良好な付着力を得ることができる。

また、図4Cに示すような、平面状の導体105を有する構成においても、図4Bの場合と同様に、ワイヤ107と導体105との良好な付着力を得ることができる。すなわち、図4Cでは、導体105の表面に溝部108が形成されており、この溝部108の一部が欠けた形状となっている(溝部108が途切れ、開口Xを形成している)。この構成によれば、接続部107aが設けられている溝部108に囲われた内側領域は、開口Xを介して、溝部108の外側の領域とつながっている。

以下、回路基板の小型化が溝部108に与える影響について、発明者が知見した内容を説明する。

通常、ステッチボンド等で接続されたたワイヤ107と導体105との接続強度は、(i)ワイヤ107と被接合物である導体105との境界の強度と、(ii)導体105と基板との密着強度で決まる。回路基板を小型化するために、導体105の面積を小さくすると、このサイズに合わせてワイヤ107の径を小さくする、またはワイヤ107と導体105との接続に使用されるキャピラリの先端径を小さくする必要があるため、上記(i)の強度が下がる傾向にある。

上記(i)の強度の強度低下を抑制するために、導体105上にワイヤ107を強く押しつぶすことによりワイヤ107と導体105の金属間結合を向上させて対策が一般的に用いられている。しかしながら、回路基板の導体105のサイズの小型化に合わせて小径化したキャピラリの先端にさらに大きな力を印加することとなるため、先端にかかる応力が大きくなり、導体105の厚みが、溝部108の部位で薄くなる傾向にある。このように導体105が薄くなると、溝部108により周囲を囲まれた内側の領域と、その周囲の領域とが分断されやすくなる。そして、溝部108の内側領域の導体105は、その内側領域の小さい面積でしか基板に密着することができなくなり、溝部108の内側の領域が基板から剥離する可能性が増大する。

図4Bおよび図4Cに示す構成によれば、上述したように、導体105上の溝部108の内側の領域が、開口Xを介して溝部108の外側の領域とつながっているので、接続部107aが形成された溝部108の内側の導体105が補強され、良好な付着力を得ることができる。

図4Cのような、内側領域と外側領域とが開口Xでつながるように、溝部108を導体105上に形成する方法としては、例えば、ワイヤ107を導体105に接続する際、基板またはキャピラリを傾けることにより形成できる。あるいは、キャピラリの先端の一部の形状を変形させることによって、先端の一部が導体105に接触しないようにすればよい。

好ましくは、図4Bのように、基板の表面に上面と側面とを有する台座部を設け、この台座部の上面にはパッド部105aを形成し、台座部の側面には側面配線部105bを形成することによって、導体105をパッド部105aと側面配線部105bとから成る折れ曲がった平板状にするのがよい。このような構成にすると、基板またはキャピラリを傾けなくとも、キャピラリの先端の一部がパッド部105aからはみ出すように接続するだけで、一部の領域で開口Xを形成するように、溝部108を容易に形成することができる。

また、図4Bのような台座部上に導体105を設けた場合、ワイヤ107の導体105に対する付着力をより高めることができる。すなわち、従来は、溝部がパッド部の中に安定して留まるように、十分に小さい先端径を有するキャピラリを選択する必要があった。しかし、図4Bに示される構成は、

従来に比べて大きい先端径を有するキャピラリを用いて作製が可能なことから、ワイヤ107がキャピラリによりつぶされる箇所とワイヤとの境界のサイズを大きくすることができ、付着力をさらに高めることができる。

従来に比べて大きい先端径を有するキャピラリを用いて作製が可能なことから、ワイヤ107がキャピラリによりつぶされる箇所とワイヤとの境界のサイズを大きくすることができ、付着力をさらに高めることができる。

以上のように、本発明の一実施形態の回路基板における導体とワイヤとの接続構造を示す図4Bおよび図4Cによれば、ワイヤ107を導体105から剥離しにくくすることができるため、接続信頼性が向上し、装置を長寿命化することができる。

≪駆動部を有する回路基板について≫

<第1の実施形態に係る回路基板>

次に本発明の第1の実施形態に係る回路基板について、発光素子等の駆動部を具備した実施形態をもとに説明する。

<第1の実施形態に係る回路基板>

次に本発明の第1の実施形態に係る回路基板について、発光素子等の駆動部を具備した実施形態をもとに説明する。

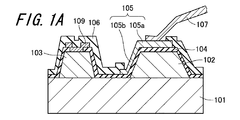

図1Aに示す発光装置は、基板101上に、駆動部としての発光素子103と台座部102とを備える。基板101は、発光素子103と同じ種類の半導体を用いて形成されることが多い。

発光素子103としては、具体的に発光ダイオード、発光サイリスタなどの半導体発光素子が挙げられる。発光素子103には、発光信号を印加するための電極109が設けられている。発光素子はn型およびp型の半導体層を積層して形成されるが、詳細な構成については後述する。

台座部102は、基板101の表面上で、発光素子103とは異なる位置に形成されている。そして、台座部の形状が上面と側面とを有する角錐台であり、導体105が上面から側面までつながっている。導体105のうち、台座部102の上面に位置する部位をパッド部105a、台座部102の側面に位置する部位を側面配線部105bと称する。パッド部105aには、Auなどから構成されるワイヤ107が接続されている。ワイヤ107の他端(ワイヤ107の両端のうち、パッド105aと接続しない側の端部)は、外部の駆動回路に接続される。この駆動回路は、発光素子103を発光駆動させる。

なお、台座部102は、発光素子103と同じ半導体の層構成で形成するのが簡便なため望ましい。しかしこの場合、台座部102が導電性を有し、導体105と導通してしまうため、台座部102上に第1の絶縁層104を設け、その上に導体105を設ける。なお、図では詳細な構成は省略しているが、導体105は発光素子103に発光のための信号を印加する電極109と電気的に接続され、外部の駆動回路からワイヤ107に対して発光の信号が印加されたときに、発光素子103に伝える働きを有する。

第2の絶縁層106は、導体105および発光素子103の電極109の少なくとも外周部を覆うように設けられている。この第2の絶縁層106が設けられていることにより、電極の外周部の界面から水分が侵入して剥離することを防止するので、信頼性を向上させることができる。

第1の絶縁層104,第2の絶縁層106は、SiN、SiO2などの誘電体膜またはポリイミドなどの樹脂材料により形成される。

図1Bおよび図1Cに示すように、パッド部105aとワイヤ107とは接続部107aを形成している。そして、接続の際に生じた溝部108の一部が、パッド部105a側の側面配線部105bとの境界で欠け、開口Xを形成している。この構成によれば、接続部107aが設けられているパッド部105aの領域は、溝部108に囲われた領域だけではなく、この領域に連続して設けられている側面配線部105bともつながっている。

なお、角錐台の台座部102を平面視したときに、パッド部105aを構成する辺が側面配線部105bとの境界部に該当する。このとき、側面配線部105bは、パッド部105aを構成する辺のいずれに設けても構わないが、好ましくは、他の辺よりも発光素子103に最も近接している辺に設けるのが良い。これにより、溝部108は、パッド部105aの表面上であって発光素子103寄りの境界部と接する態様となる。言い換えれば、発光素子103の方にずらせて設けられることになる。その結果、台座部102同士(パッド部105a同士)の間隔を近づけて配置することができるから、台座部(パッド部)の数を増やすことが可能となり、発光装置のサイズを主走査方向に小型化し、解像度の高い発光装置を作製することができる。

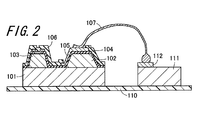

図2は、図1A〜図1Cに示した発光装置をプリント基板110に実装した実装体を示す模式的な断面図であり、図3は、ワイヤ107を導体105(パッド部105a)にステッチボンドする工程を示す断面図である。

図2に示すように、プリント基板110上には、図1A〜図1Bで説明した本発明の第1の実施形態に係る発光装置と、IC111などの駆動回路とが設けられており、電極112とワイヤ107とが接続している。なお、ここでは、駆動回路として電極112に接続する例を示したが、プリント基板上に設けられた銅などの配線パッドに直接ワイヤ107を設けてもよい。また、駆動回路は、本発明の一実施形態の回路基板に構成されていてもよい。

ワイヤ107は、始めの工程でプリント基板110のIC111の電極112に対して接続され(first bond)、次の工程で発光素子側の導体105(パッド部105a)に対して接続される(second bond)。具体的には以下のような工程を経る。

(1)ワイヤ107の先端にボール状の部位を有する状態から、ワイヤクランプが開いてキャピラリ113が降下し、前記部位がターゲットである電極112と接触するとともに、熱・荷重・超音波をボールに伝えて接続を形成する。

(2)キャピラリ113を一定の高さ(ループ高さ)まで上昇した後、導体105までキャピラリ113を移動させる。この際に安定した形のループを形成するため、キャピラリ113を特殊な軌跡で移動させることでワイヤ107にくせをつけてもよい。

(3)再びキャピラリ113が降下して、ワイヤ107をパッド部105a上に押し付ける。この際に熱と荷重と超音波とを加えてワイヤ107を変形させ、ワイヤ107をターゲット上に接合させるためのステッチボンドと、次のステップでテイルを確保するためのテイルボンドを形成する。なお、テイルとは、キャピラリ113の先端であって、前記ボール状の部位の逆側に位置する先端部分をいう。

図3ではこの工程においてキャピラリ113が降下するときの状態を示す。本実施形態では、この工程において、キャピラリ113をパッド部105aに押し付ける際に、側面配線部105bの側にずらして設定することにより、キャピラリ113の先端部がパッド部105a上に押し付けられてできるキャピラリの痕は、側面配線部105bとの境界部で欠けた形状となる。

(4)次に、キャピラリ113はワイヤ107を残したまま上昇し、キャピラリ113の先端に一定の長さのテイルを確保した後、ワイヤクランプを閉じてワイヤ107をつかみ、テイルボンドの部分からワイヤ107をひきちぎる。このときテイルボンドがワイヤを仮止めした状態となっているので、ワイヤ107はキャピラリ113と一緒には上昇しない。

(5)キャピラリ113の先端であって、テイルに高電圧をかけて火花を飛ばし、その熱でテイル中の接続部を溶かすことにより、溶けた接続部は表面張力により球形に近いボール状になって固化される。以下、(1)に戻り、継続して接続をおこなうことができる。

≪回路基板の各構成要素の詳細について≫

以下、本発明の実施形態に係る回路基板の各構成要素についてさらに詳しく説明する。

以下、本発明の実施形態に係る回路基板の各構成要素についてさらに詳しく説明する。

<第2の実施形態に係る回路基板>

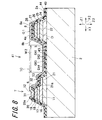

図5は、本発明の第2の実施形態に係る回路基板(発光装置1)を示す断面図である。図6は、発光装置1を示す断面図である。基本的には図1A〜図1Cで説明した構成と同じであるが、素子自体の構成を細かく説明するため、図1A〜図1Cのワイヤと第2絶縁層とを省略して記載した。なお、図5は、発光装置1のうち、後述するゲート用台座部34と発光素子本体11を切断する面における断面図である。また、図6は、後述するカソード用台座部22を切断する面における断面図である。

図5は、本発明の第2の実施形態に係る回路基板(発光装置1)を示す断面図である。図6は、発光装置1を示す断面図である。基本的には図1A〜図1Cで説明した構成と同じであるが、素子自体の構成を細かく説明するため、図1A〜図1Cのワイヤと第2絶縁層とを省略して記載した。なお、図5は、発光装置1のうち、後述するゲート用台座部34と発光素子本体11を切断する面における断面図である。また、図6は、後述するカソード用台座部22を切断する面における断面図である。

図5および図6に示す構成において、発光装置1は、基板2と、発光素子3と、台座部4と、ゲート用配線5と、アノード用配線6と、カソード用配線7と、導体8とを含む。図1A〜図1Cの説明では、導体と発光素子の電極とを結ぶ詳細な構成を省略したが、図5および図6において、ゲート用配線5、アノード用配線6、およびカソード用配線7などが導体8と発光素子3の電極とを仲介して電気的に接続する。

基板2は、板状であって、n型半導体から成る。発光素子3は、基板2の厚み方向Z(以下、厚み方向Zという)の一表面2a上の、基板2の幅方向X(以下、幅方向Xという)の一方X1の端部寄りに形成される。発光素子3は、本実施形態ではpnpn構造を有する発光サイリスタから成る。そして、発光素子3は、発光素子本体11と、第1電極12と、第2電極13と、発光素子本体11に重なって形成される絶縁層15の一部とを含んで構成される。発光素子3は、しきい電圧を超える電位差をアノードとカソードとの間に与えることによって発光する。しきい電圧は、ゲートに印加する電圧に応じて変化する。

発光素子本体11は、第1のn型半導体層16と、第1のp型半導体層17と、第2のn型半導体層18と、第2のp型半導体層19と、オーミックコンタクト層20とがそれぞれこの順に積層されて、基板2の厚み方向Zの一表面2a上に形成される。発光素子本体11は、基板2から厚み方向Zの一方Z1に向かって側面が集まるように形成される。

基板2としては、III−V族化合物半導体およびIV族半導体などの結晶成長が可能な半導体基板が挙げられ、たとえば、ガリウム砒素(GaAs)、インジウムリン(InP)、ガリウムリン(GaP)、シリコン(Si)またはゲルマニウム(Ge)などの半導体材料が挙げられる。

第1のn型半導体層16は、ガリウム砒素(GaAs)、アルミニウムガリウム砒素(AlGaAs)またはインジウムガリウムリン(InGaP)などの半導体材料によって形成される。第1のn型半導体層16のキャリア密度は、1×1018cm−3程度が望ましい。

第1のp型半導体層17は、アルミニウムガリウム砒素(AlGaAs)またはガリウム砒素(GaAs)などの半導体材料によって形成される。第1のp型半導体層17を形成する半導体材料としては、第1のn型半導体層16を形成する半導体材料のエネルギーギャップと同じエネルギーギャップを有するもの、もしくは、第1のn型半導体層16を形成する半導体材料のエネルギーギャップよりも小さいエネルギーギャップを有するものが選ばれる。第1のp型半導体層17のキャリア密度は1×1017cm−3程度が望ましい。

第2のn型半導体層18は、アルミニウムガリウム砒素(AlGaAs)またはガリウム砒素(GaAs)などの半導体材料によって形成される。第2のn型半導体層18を形成する半導体材料には、第1のp型半導体層17を形成する半導体材料のエネルギーギャップと同じエネルギーギャップを有するもの、もしくは、第1のp型半導体層17を形成する半導体材料のエネルギーギャップよりも小さいエネルギーギャップを有するものが選ばれる。第2のn型半導体層18のキャリア密度は、第1のn型半導体層16、第1のp型半導体層17、第2のn型半導体層18および第2のp型半導体層19の全層の中で最も小さく、具体的には1×1016cm−3〜1×1017cm−3程度が望ましい。第2のn型半導体層18は、アルミニウムガリウム砒素(AlGaAs)、ガリウム砒素(GaAs)などの半導体材料から形成されることによって、得られた発光素子は高い内部量子効率を得ることができる。

第2のp型半導体層19は、アルミニウムガリウム砒素(AlGaAs)またはガリウム砒素(GaAs)などの半導体材料によって形成される。第2のp型半導体層19を形成する半導体材料には、第1のp型半導体層17および第2のn型半導体層18を形成する半導体材料のエネルギーギャップと同じエネルギーギャップを有するもの、もしくは、第1のp型半導体層17および第2のn型半導体層18を形成する半導体材料のエネルギーギャップよりも大きいエネルギーギャップを有するものが選ばれる。第2のp型半導体層19のキャリア密度は、1×1018cm−3程度が望ましい。

オーミックコンタクト層20は、ガリウム砒素(GaAs)またはインジウムガリウムリン(InGaP)などの半導体材料によって形成されるp型半導体層であり、第1電極12とのオーミック接合を行うためのものである。オーミックコンタクト層20のキャリア密度は1×1019cm−3以上が望ましい。

発光素子本体11は、第2電極13と接続される第2電極接続部21を有する。第2電極接続部21は、第1のn型半導体層16と、第1のp型半導体層17の厚み方向Zの基板2寄りの一部とが、第1のn型半導体層16と、第1のp型半導体層17と、第2のn型半導体層18と、第2のp型半導体層19と、オーミックコンタクト層20とが積層された部位から、幅方向Xの他方X2に突出して形成される。

台座部4は、基板2の厚み方向Zの一表面2a上の発光素子3とは異なる領域に設けられる。台座部4は、基板2の幅方向Xの他方X2の端部寄りに形成される。台座部4は、図5では、では厚み方向Zおよび幅方向Xに垂直な配列方向Yに所定の間隔をあけて配置されるアノード用台座部と、ゲート用台座部34と、カソード用台座部35と、第3電極14とを含む。アノード用台座部と、ゲート用台座部34と、カソード用台座部35とを総称する場合、または不特定のものを指定する場合には、単に台座部4という。台座部4は、台座部本体22と、絶縁層15の台座部本体22に重なって形成される部分とを含んで構成される。

台座部本体22は、例えば、図5では発光素子本体11の各半導体層とそれぞれ同じ厚みを有する半導体層を積層して形成される。台座部本体22は、発光素子本体11と同じ材料を用いた層構成を成すので、対応する層については発光素子本体11の各半導体層と同一の名称を付す。

台座部本体22は、第1のn型半導体層24と、第1のp型半導体層25と、第2のn型半導体層26と、第2のp型半導体層27と、オーミックコンタクト層28とがそれぞれこの順に積層されて、基板2の厚み方向Zの一表面2a上に形成される。台座部本体22は、四角錘台状に形成される。

絶縁層15は、先の図1において第1の絶縁層として説明した構成要素である。この絶縁層15は、発光素子本体11の表面と、台座部本体22の表面と、基板2の表面とを厚み方向Zの一方Z1から覆って形成される。絶縁層15は、電気絶縁性、透光性および平坦性を有する樹脂材料によって形成される。絶縁層15は、ポリイミドおよびベンゾシクロブテン(BCB)などによって形成される。

発光素子3と台座部4とは、発光装置1の小型化を実現するために可能な限り近接して配置される。発光素子3と台座部4との間隔W1は、たとえば10μm〜200μmである。

発光素子本体11のオーミックコンタクト層20の厚み方向Zの一表面20a上に積層された絶縁層15の一部には、厚み方向Zに貫通する第1貫通孔31が形成される。また第2電極接続部21の厚み方向Zの一表面21a上に積層された絶縁層15の一部には、厚み方向Zに貫通する第2貫通孔32が形成される。また図6に示すようにカソード用台座部35と基板2の幅方向Xの他方X2の端部との間に形成される絶縁層15の一部には、厚み方向Zに貫通する第3貫通孔33が形成される。

第1電極12は、第1貫通孔31を厚み方向Zの一方Z1から覆うように形成される。第1電極12は、発光素子3のアノードに相当する。第2電極13は、第2貫通孔32を厚み方向Zの一方Z1から覆うように形成される。第2電極13は、発光素子3のゲートに相当する。図6に示す第3電極14は、第3貫通孔33を厚み方向Zの一方Z1から覆うように形成される。第3電極14は、基板2を介して第1のn型半導体層16に電気的に接続されるので、発光素子3のカソードに相当する。第1〜第3電極12,13,14は、金属材料および合金材料などの導電性を有する材料によって形成される。

台座部4にはワイヤの一端が接続される導体8が形成される。この導体8はパッド部8aと側面配線部8bとを含む。そして、台座部4の厚み方向Zの一表面4a上、すなわち台座部4の上面上には、パッド部8aが配置され、台座部4の側面上には側面配線部8bが配置される。発光装置1は、ワイヤを介して、他の装置と電気的に接続される。導体8は、アノード用台座部の厚み方向Zの一表面上の全面にわたって形成されるアノード用導体と、ゲート用台座部34の厚み方向Zの一表面4a上の全面にわたって形成されるゲート用導体Gと、カソード用台座部35の厚み方向Zの一表面4a上に形成されるカソード用導体Cとを含む。以後ゲート用導体Gと、カソード用台座部35の厚み方向Zの一表面4a上に形成されるカソード用導体Cとを総称する場合、不特定のものを示す場合、およびパッド部8aまたは側面配線部8bの構成要素を区別せず総称する場合には、単に導体8という。

ゲート用配線5は、絶縁層15の表面に沿って第2電極13とゲート用導体Gとの間に設けられる。ゲート用導体Gは、ゲート用配線5を介して第2電極13と電気的に接続される。

アノード用配線6は、絶縁層15の表面に沿って第1電極12とアノード用導体との間に設けられる。アノード用導体は、アノード用配線6を介して第1電極12と電気的に接続される。このアノード用配線6は、ゲート用配線5と短絡しないように、ゲート用配線5と所定の間隔をあけて配置される。

カソード用配線7は、絶縁層15の表面に沿って第3電極14とカソード用導体Cとの間に設けられる。カソード用導体Cは、カソード用配線7を介して第3電極14と電気的に接続される。発光素子3のカソードをグランドに接続する場合には、このカソード用導体Cとグランドとの間をワイヤによって接続すればよい。

第1電極12、第2電極13、第3電極14、アノード用配線6、ゲート用配線5、カソード用配線7、アノード用導体、ゲート用導体G、およびカソード用導体Cは、それぞれ金(Au)、金とゲルマニウムとの合金(AuGe)、または金と亜鉛との合金(AuZn)などによって形成される。

発光素子本体11および台座部本体22は、第1のn型半導体層16,24、第1のp型半導体層17,25、第2のn型半導体層18,26、第2のp型半導体層19,27、オーミックコンタクト層20,28をそれぞれ形成するための半導体材料を、エピタキシャル成長および化学気相成長(CVD)法などによって基板2の一表面2a上に順次積層した後、フォトリソグラフィによってパターニングおよびエッチングを行うことにより形成される。したがって、一連の製造プロセスにおいて、発光素子本体11および台座部本体22を同時に形成することができる。よって、製造工程を増加させないで台座部本体22を形成することができ、製造コストを低減することができる。

絶縁層15は、前述したポリイミドなどの樹脂材料をスピンコーティングした後、塗付した樹脂材料を硬化させ、第1〜第3貫通孔31,32,33をフォトリソグラフィによってパターニングおよびエッチングすることにより形成される。

第1〜第3電極12,13,14、アノード用配線6、ゲート用配線5、カソード用配線7、アノード用導体、ゲート用導体G、およびカソード用導体Cは、絶縁層15を形成した後、蒸着法などによって導電性材料を絶縁層15の表面に積層され、その後、フォトリソグラフィによってパターニングおよびエッチングして、同時に形成される。したがって、第1〜第3電極12,13,14と、アノード用配線6、ゲート用配線5、カソード用配線7、アノード用導体、ゲート用導体G、およびカソード用導体Cの厚みは、ほぼ等しい。

アノード用導体とカソード用導体Cとゲート用導体Gとは、発光装置1において基板2の一表面2aから最も離間した位置に形成される。またアノード用配線6、ゲート用配線5およびカソード用配線7は、仮想一平面10よりも基板2に近接して形成される。発光素子3の厚み方向Zの一表面3aと導体8の厚み方向Zの一表面との基板2の一表面2aからの高さHは、たとえば2μm〜10μmに選ばれる。

このように、アノード用導体とカソード用導体Cとゲート用導体Gが、アノード用配線6、ゲート用配線5およびカソード用配線7と離間することにより、それらの導体と発光素子3とが十分に離間することになり、キャピラリと発光素子3との衝突を低減させ、また、ワイヤを接続時の発光素子3への衝撃を緩和することができる。

本実施形態では、発光素子本体11は、n型半導体層とp型半導体層との順が反対であってもよい。

また本実施形態では、導体8の厚み方向Zの一表面の基板2からの間隔は、発光素子3の厚みと等しくなるが、導体8の厚み方向Zの一表面の基板2からの間隔を、発光素子3の厚みよりも大きくなるように台座部4または導体8を形成してもよい。

ワイヤを接続するときに発光素子3に加わる衝撃を緩和するために、発光素子3と台座部4とを離間して配置するようにしてもよい。ただし発光素子3と台座部4との間隔W1が大きすぎると、電気信号が劣化する、あるいは装置が大形になるので、発光素子3と台座部4との間隔W1は、たとえば10μm〜200μmに選ばれる。

<第3の実施形態に係る回路基板>

発光装置41は、発光素子アレイ42と、複数の台座部Dと、複数の制御信号伝送配線GHと、アノード用配線6と、ゲート用配線5と、カソード用配線7と、第1絶縁層43と、第3絶縁層44と、複数の導体8とを含む。図7〜9に示す発光装置41の構成において、前述の第1の実施形態に係る発光装置1の構成と対応する構成については、同一の符号を付す。なお、第3絶縁層44は、図1における第2の絶縁層とは別の構成要素である。

発光装置41は、発光素子アレイ42と、複数の台座部Dと、複数の制御信号伝送配線GHと、アノード用配線6と、ゲート用配線5と、カソード用配線7と、第1絶縁層43と、第3絶縁層44と、複数の導体8とを含む。図7〜9に示す発光装置41の構成において、前述の第1の実施形態に係る発光装置1の構成と対応する構成については、同一の符号を付す。なお、第3絶縁層44は、図1における第2の絶縁層とは別の構成要素である。

発光素子アレイ42は、n(記号nは、2以上の整数)個の発光素子ブロックBを含む。各発光素子ブロックBは、それぞれm(記号mは、2以上の整数)個の発光素子Tを含んで構成される。すなわち発光素子アレイ42は、n×m個の発光素子Tを含んで構成される。図7の発光装置の場合、m=4である。各発光素子Tは、基板2の厚み方向Zの一表面2a上の幅方向Xの他方X1の端部寄りに、相互に間隔をあけて配列方向Yに沿って直線状に配列される。各発光素子ブロックBは、配列方向Yの一方Y1から順にm個ずつの発光素子Tによってそれぞれ構成される。n個の発光素子ブロックBのうちの、配列方向Yの一方Y1から順にi(記号iは、1以上かつn以下の整数)番目に配置される発光素子ブロックBを、発光素子ブロックBiとする。また発光素子ブロックBiを構成する発光素子Tのうちの、配列方向Yの一方Y1から順にj(記号jは、1以上かつm以下の整数)番目に配置される発光素子Tを発光素子Tjとする。複数の発光素子Tを総称する場合、および不特定の発光素子Tを示す場合には、単に発光素子Tとする。また複数の発光素子ブロックBを総称する場合、および不特定の発光素子ブロックBを示す場合には、単に発光素子ブロックBとする。発光素子Tは、600〜800nmの波長の光を発光できるように形成される。

発光素子Tは、前述した第1の実施形態に係る発光装置1における発光素子3と同様の構成であるので、対応する構成については同様の符号を付す。発光素子Tは、発光素子本体11と、第1絶縁層43の一部と、第3絶縁層44の一部と、第1電極12と、第2電極13とを含んで構成される。特に発光素子本体11は、前述した第1の実施形態に係る発光装置1における発光素子本体11と同じ構造を有している。

各発光素子ブロックBを構成する発光素子Tは、発光素子ブロックB毎に第1電極12が互いにアノード用配線6を介して電気的に接続される。

発光装置41は、本実施形態では3×n個の台座部Dを含む。台座部Dは、基板2の厚み方向Zの一表面2a上であって幅方向Xの一方X2の端部寄りに、相互に間隔をあけて配列方向Yに直線状に配列される。台座部Dは、前述した第1の実施形態に係る発光装置1における台座部4と同様の構成であるので、対応する構成については同じ符号を付す。台座部Dは、台座部本体22と、第1絶縁層43の一部と、第3絶縁層44の一部と、第3電極14とを含んで構成される。特に台座部本体22は、前述した第1の実施形態に係る発光装置1における台座部本体22と同じ構造を有している。

発光素子Tと台座部Dとは、発光装置41の小型化を実現するために、後述する制御信号伝送配線GHを形成することが可能な間隔をあけて近接して配置される。発光素子Tと台座部Dとの間隔W2は、たとえば10μm〜200μmに選ばれる。

導体8は、図1Aの導体105と同様の構成を示す。パッド部8aの幅方向Xの寸法W3は、たとえば30μm〜120μmに選ばれる。またパッド部8aの配列方向Yの寸法W4は、たとえば30μm〜120μmに選ばれる。

この発光装置41の構成によれば、発光素子Tが、一列状に複数個配列され、台座部Dも一列状に複数個配列されている。台座部D上のパッド部8aを発光素子Tに近づけて配列できるため、発光装置41の幅方向Xのサイズを縮小化することができる。

複数の導体8のうち、配列方向Yの一方Y1から順に3×i−1番目に配置される導体8を、アノード用導体Aiとする。以後複数のアノード用導体Aを総称する場合、および不特定のアノード用導体Aを示す場合には、単にアノード用導体Aとする。

発光装置41は、図7に示すように発光素子ブロックBを構成する発光素子Tの数(m個)と同数のm本の制御信号伝送配線GHを含む。図7に示す発光装置41ではm=4なので、発光装置41は、4本の第1〜第4制御信号伝送配線GH1,GH2,GH3,GH4を含む。

制御信号伝送配線GHは、発光素子アレイ42と台座部Dとの間に形成される。そして、制御信号伝送配線GHは、前述した第1の実施形態に係る発光装置1の絶縁層15に相当する第1絶縁層43の厚み方向Zの一表面上に配列方向Yに沿って形成される。第1〜第4制御信号伝送配線GH1,GH2,GH3,GH4は、各発光素子Tの第2電極13にそれぞれ順次1つずつゲート用配線5を介して接続される。そして、第1〜第4制御信号伝送配線GH1,GH2,GH3,GH4は、配列される発光素子Tに沿って、それぞれが4つおきに発光素子Tの第2電極13に接続される。すなわち第1制御信号伝送配線GH1は、発光素子T1の第2電極13に電気的に接続され、第2制御信号伝送配線GH2は、発光素子T2の第2電極13に電気的に接続され、第3制御信号伝送配線GH3は、発光素子T3の第2電極13に電気的に接続され、第4制御信号伝送配線GH4は、発光素子T4の第2電極13に電気的に接続される。

第1〜第4制御信号伝送配線GH1,GH2,GH3,GH4はそれぞれ、複数の導体8のうちのいずれか1つにゲート用配線5を介して電気的に接続される。以後第1制御信号伝送配線GH1、GH2GH3、およびGH4に電気的に接続される導体8をそれぞれ、第1ゲート用導体G1、第2ゲート用導体G2、第3ゲート用導体G3および第4ゲート用導体G4とする。

また複数の台座部Dのうちの1つは、前述の第1の実施形態に係る発光装置1のカソード用台座部35に相当する。以後カソード用配線7を介して第3電極14に電気的に接続される導体8を、カソード用導体Cとする。

第1絶縁層43は、前述した第1の実施形態に係る発光装置1における絶縁層15に相当する。

第3絶縁層44は、第1絶縁層43および制御信号伝送配線GHの表面を、厚み方向Zの一方Z1から覆う。前述したゲート用配線5は、第3絶縁層44の表面に沿って幅方向Xに延び、所定の制御信号伝送配線GHに接続される。第3絶縁層44のうち、制御信号伝送配線GHのゲート用配線5が接続されるべき表面上に位置する部分には、貫通孔45が形成される。そして、この貫通孔45にゲート用配線5の一部が形成される。

アノード用配線6は、第3絶縁層44の表面に沿って形成される。そして、アノード用配線6は、第1電極12から第2電極接続部21の厚み方向Zの一方Z1方向に設けられた第1延在部6aと、配列方向Yに延び、第1延在部6aの第1電極12とは反対側の端部をそれぞれ接続する第2延在部6bと、第2延在部6bの配列方向Yの中央から幅方向Xに延び、アノード用導体Aに接続される第3延在部6cとを含む。

第1絶縁層43および第3絶縁層44の一部には、厚み方向Zに貫通する第1貫通孔31が形成される。また、第1絶縁層43および第3絶縁層44の一部には、厚み方向Zに貫通する第2貫通孔32が形成される。さらに、第1絶縁層43および第3絶縁層44の一部には、厚み方向Zに貫通する第3貫通孔33が形成される。

第1電極12は、アノードに相当する。第2電極13は、ゲートに相当する。第3電極14は、カソードに相当する。

発光素子本体11および台座部本体22は、前述の第1の実施形態と同様の工程を経ることによって形成される。

第1絶縁層43および第3絶縁層44の形成方法は次のとおりである。まず、前述したポリイミドなどの樹脂材料をスピンコーティングした後、塗付した樹脂材料を硬化させる。そして、第1〜第3貫通孔31,32,33をフォトリソグラフィによってパターニングおよびエッチングすることにより第1絶縁層43および第3絶縁層44形成される。

図10は、図7に示される発光装置41の等価回路を示す回路図である。発光装置41は、駆動部をさらに含む。駆動部は、各アノード用導体Aおよび各ゲート用導体Gにそれぞれワイヤを介して電気的に接続される。図10に示す発光装置41では、各発光素子Tのカソードに相当するカソード用導体Cを接地電位とする。

駆動部は、アノード用導体Aiにセレクト信号φiを、ゲート用導体Gjに制御信号ψjをそれぞれ与える。セレクト信号φiは、アノード用配線6を介して発光素子ブロックBjに含まれる各発光素子T1,T2,T3,T4のアノードに与えられる。制御信号ψjは、制御信号伝送配線GHjを介して各発光素子Tjのゲートに与えられる。駆動部は、駆動用ドライバーIC(Integrated Circuit)によって実現される。

発光素子Tは、カソードが接地しているときには、アノードにハイレベルの高電圧が印加される。そして発光素子Tは、ゲートにローレベルが印加されているときに発光し、アノードおよびゲートが共にハイレベル、または、アノードおよびゲートが共にローレベルのときには、消灯している。ハイレベルは、たとえば3ボルト〜10ボルトであり、ローレベルは、たとえば0(零)ボルトである。したがってたとえば発光素子ブロックBiの発光素子T2を発光させる場合には、駆動部は、ハイレベルのセレクト信号φiを与えるとともに、ローレベルの制御信号ψ2、ハイレベルの制御信号ψ1、ψ3、ψ4を与える。このようにセレクト信号φiおよび制御信号ψjを制御することによって選択的に発光素子Tを発光させることができる。たとえば各発光素子Tのゲートおよびアノード毎にボンディング用のパッド部8aを形成する場合には、発光素子Tの数の2倍のボンディング用のパッド部が必要になるが、m個の発光素子Tをまとめて発光素子ブロックBとすることによって、駆動部に接続される端子の数をn+m個にすることができる。これによって駆動部の端子数を抑制することができる。

駆動部は、外部から基準となるクロックパルス信号が入力されて、このクロックパルス信号に基づいて、制御信号ψ1〜ψ4を同期して出力する。前記クロックパルス信号は、後述する画像形成装置87の制御部96から与えられる。クロックパルス信号のクロック周期は、後述する画像形成装置87の制御部96における制御周期よりも長く選ばれる。また駆動部は、クロックパルス信号とともに与えられる画像情報に基づいて、セレクト信号φiを出力する。

<第4の実施形態に係る回路基板>

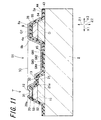

図11は、本発明の第4の実施形態に係る回路基板である発光装置51を示す断面図である。発光装置51は、第2の実施形態の発光装置41の構成から、カソード用配線7、第3電極14が除かれ、発光素子Tを発光サイリスタから発光ダイオードに置換されている。このように発光素子Tを発光ダイオードによって構成したとしても、駆動部は、制御信号ψおよびセレクト信号φを与えることによって選択的に発光素子Tを発光させることができる。

図11は、本発明の第4の実施形態に係る回路基板である発光装置51を示す断面図である。発光装置51は、第2の実施形態の発光装置41の構成から、カソード用配線7、第3電極14が除かれ、発光素子Tを発光サイリスタから発光ダイオードに置換されている。このように発光素子Tを発光ダイオードによって構成したとしても、駆動部は、制御信号ψおよびセレクト信号φを与えることによって選択的に発光素子Tを発光させることができる。

以上説明した本発明の第4の実施形態に係る発光装置41によれば、前述の第1の実施形態に係る発光装置1と同様に、ワイヤを剥離しにくくすることができるため、信頼性が向上し、装置の長寿命化を図ることができる。

また発光装置41は、溝部108を発光素子T寄りにずらすことにより、パッド部8a同士を近づけて配置することができる。そして、その結果、各発光素子Tを配列方向Yに密に配置することができる。これによって解像度の高い画像形成装置87を実現することができる。

≪画像形成装置について≫

次に本発明の他の実施形態に係る画像形成装置について説明する。図12は、発光装置41を有する画像形成装置87の基本的構成を示す側面図である。なお、本発明の一実施形態に係る回路基板である画像形成装置87は、電子写真方式の画像形成装置であり、感光体ドラム90への露光装置に使用される発光装置41を有する。発光装置41は、図2に示したように、例えば、駆動用ICである駆動回路が搭載されたプリント基板に実装される。

次に本発明の他の実施形態に係る画像形成装置について説明する。図12は、発光装置41を有する画像形成装置87の基本的構成を示す側面図である。なお、本発明の一実施形態に係る回路基板である画像形成装置87は、電子写真方式の画像形成装置であり、感光体ドラム90への露光装置に使用される発光装置41を有する。発光装置41は、図2に示したように、例えば、駆動用ICである駆動回路が搭載されたプリント基板に実装される。

画像形成装置87は、Y(イエロ)、M(マゼンタ)、C(シアン)、K(ブラック)の4色のカラー画像を形成するタンデム方式を採用した装置である。図12に示す画像形成装置87は、4つの発光装置41Y,41M,41C,41K、集光部であるレンズアレイ88Y,88M,88C,88Kが実装された回路基板およびレンズアレイ88を保持する第1ホルダ89Y,89M,89C,89K、4つの感光体ドラム90Y,90M,90C,90K、4つの現像剤供給部91Y,91M,91C,91K、転写部である転写ベルト92、4つのクリーナ93Y,93M,93C,93K、4つの帯電器94Y,94M,94C,94K、定着部95および制御部96を含む。

各発光装置41は、駆動部によって各色のカラー画像情報に基づいて駆動される。

各発光装置からの光は、レンズアレイ88を介して各感光体ドラム90Y,90M,90C,90Kに集光して照射される。レンズアレイ88は、たとえば発光装置の光軸上にそれぞれ配置される複数のレンズを含み、これらのレンズを一体的に形成して構成される。

発光装置41およびレンズアレイ88は、第1ホルダ89によって保持される。第1ホルダ89は、発光素子41の光照射方向と、レンズアレイ88のレンズの光軸方向と、をほぼ一致させるようにして位置合わせさせる。

各感光体ドラム90Y,90M,90C,90Kは、たとえば円筒状の基体表面に感光体層が被着されている。そして、その感光体層には各発光装置41Y,41M,41C,41Kからの光を受けて静電潜像が形成される。

各感光体ドラム90Y,90M,90C,90Kの周辺部には、各静電潜像の形成位置を基準として回転方向下流側に向かって順番に、露光された感光体ドラム90Y,90M,90C,90Kに現像剤を供給する現像剤供給部91Y,91M,91C,91K、転写ベルト92、クリーナ93Y,93M,93C,93K、および帯電器94Y,94M,94C,94Kがそれぞれ配置される。感光体ドラム90に現像剤によって形成された画像を記録シートに転写する転写ベルト92は、4つの感光体ドラム90Y,90M,90C,90Kに対して共通に設けられる。

前記感光体ドラム90Y,90M,90C,90Kは、第2ホルダによって保持され、この第2ホルダと第1ホルダ89とは、相対的に固定される。各感光体ドラム90Y,90M,90C,90Kの回転軸方向は、発光装置の厚み方向Zおよび幅方向Xに垂直な配列方向Yとほぼ一致するようにして位置合わせされる。

転写ベルト92によって、記録シートを搬送し、現像剤によって画像が形成された記録シートは、定着部95に搬送される。定着部95は、記録シートに転写された現像剤を定着させる。感光体ドラム90Y,90M,90C,90Kは、回転駆動部によって回転される。

制御部96は、前述した駆動部にクロック信号および画像情報を与えるとともに、感光体ドラム90Y,90M,90C,90Kを回転駆動させる回転駆動部、現像剤供給部91Y,91M,91C,91K、転写部92、帯電器94Y,94M,94C,94Kおよび定着部95を制御する。

≪サーマルヘッドについて≫

また、図13に示すように、本実施形態の回路基板は、駆動部として発熱抵抗体121を設けることによって、サーマルプリンタまたはインクジェットプリンタ等に用いられるサーマルヘッドに用いることができる。本発明の一実施形態に係るサーマルヘッドは、このサーマルヘッド用の回路基板と、第2の駆動回路122と、を備える。駆動回路122は、ワイヤ107に接続され、第2の画像情報に基づいて発熱抵抗体121を駆動する。

また、図13に示すように、本実施形態の回路基板は、駆動部として発熱抵抗体121を設けることによって、サーマルプリンタまたはインクジェットプリンタ等に用いられるサーマルヘッドに用いることができる。本発明の一実施形態に係るサーマルヘッドは、このサーマルヘッド用の回路基板と、第2の駆動回路122と、を備える。駆動回路122は、ワイヤ107に接続され、第2の画像情報に基づいて発熱抵抗体121を駆動する。

≪イメージセンサについて≫

また、図14に示すように、本実施形態の回路基板は、駆動部として受光素子131を設けることによって、イメージセンサに用いることができる。本発明の一実施形態に係るイメージセンサは、このイメージセンサ用の回路基板と、演算回路132と、を含む。演算回路132は、受光素子131で発生した電気信号を演算処理する。この電気信号は、光パターン(第3の画像情報)に対応して受光素子131で発生する。

また、図14に示すように、本実施形態の回路基板は、駆動部として受光素子131を設けることによって、イメージセンサに用いることができる。本発明の一実施形態に係るイメージセンサは、このイメージセンサ用の回路基板と、演算回路132と、を含む。演算回路132は、受光素子131で発生した電気信号を演算処理する。この電気信号は、光パターン(第3の画像情報)に対応して受光素子131で発生する。

上記の発光素子または発熱抵抗体を搭載した本実施形態の画像形成装置、および受光素子を搭載した本実施形態のイメージセンサは、小型化しても良好なワイヤの付着力を得られる本実施形態の回路基板を備えているので、小型で長寿命かつ歩留りの高い画像形成装置およびイメージセンサとなる。

本発明は、その精神または主要な特徴から逸脱することなく、他のいろいろな形態で実施できる。したがって、前述の実施形態はあらゆる点で単なる例示に過ぎず、本発明の範囲は特許請求の範囲に示すものであって、明細書本文には何ら拘束されない。さらに、特許請求の範囲に属する変形や変更は全て本発明の範囲内のものである。

本発明は、その精神または主要な特徴から逸脱することなく、他のいろいろな形態で実施できる。したがって、前述の実施形態はあらゆる点で単なる例示に過ぎず、本発明の範囲は特許請求の範囲に示すものであって、明細書本文には何ら拘束されない。さらに、特許請求の範囲に属する変形や変更は全て本発明の範囲内のものである。

1,41,51 発光装置

2 基板

3 発光素子

4 台座部

5 ゲート用配線

6 アノード用配線

7 カソード用配線

8 導体

8a パッド部

8b 側面配線部

12 第1電極

13 第2電極

14 第3電極

34 ゲート用台座部

35 カソード用台座部

42 発光素子アレイ

87 画像形成装置

88 レンズアレイ

89 ホルダ

90 感光体ドラム

91 現像剤供給部

92 転写ベルト

93 クリーナ

94 帯電器

95 定着部

96 制御部

101 基板

102 台座部

103 発光素子

104 第1の絶縁層

105 導体

105a パッド部

105b 側面配線部

106 第2の絶縁層

107 ワイヤ

107a 接続部

108 溝部

109 電極

110 プリント基板

111 駆動用IC

112 電極

113 キャピラリ

120 サーマルヘッド

121 発熱抵抗体

122 駆動回路

130 イメージセンサ

131 受光素子

132 演算回路

A アノード用導体

C カソード用導体

D 台座部

G ゲート用導体

GH 制御信号伝送配線

2 基板

3 発光素子

4 台座部

5 ゲート用配線

6 アノード用配線

7 カソード用配線

8 導体

8a パッド部

8b 側面配線部

12 第1電極

13 第2電極

14 第3電極

34 ゲート用台座部

35 カソード用台座部

42 発光素子アレイ

87 画像形成装置

88 レンズアレイ

89 ホルダ

90 感光体ドラム

91 現像剤供給部

92 転写ベルト

93 クリーナ

94 帯電器

95 定着部

96 制御部

101 基板

102 台座部

103 発光素子

104 第1の絶縁層

105 導体

105a パッド部

105b 側面配線部

106 第2の絶縁層

107 ワイヤ

107a 接続部

108 溝部

109 電極

110 プリント基板

111 駆動用IC

112 電極

113 キャピラリ

120 サーマルヘッド

121 発熱抵抗体

122 駆動回路

130 イメージセンサ

131 受光素子

132 演算回路

A アノード用導体

C カソード用導体

D 台座部

G ゲート用導体

GH 制御信号伝送配線

Claims (4)

- 基板と、

前記基板上に位置し、表面に溝部を有する導体と、

前記導体に接続されたワイヤと、を備え、

前記溝部は、前記ワイヤと前記導体との接続部を、一部の開口を除いて取り囲む、回路基板。 - 前記基板上に位置し上面と側面とを有する台座部、をさらに備え、

前記導体は、前記上面上に位置するパッド部と、前記パッド部と電気的に接続されるとともに前記側面上に位置する側面配線部と、を有し、

前記開口が、前記パッド部と前記側面配線部との境界部に位置する、請求項1に記載の回路基板。 - 前記基板上であって前記台座部とは異なる領域に位置し、前記導体と電気的に接続された駆動部、をさらに備える請求項2に記載の回路基板。

- 前記台座部の形状が角錐台であり、

前記角錐台における前記上面と前記側面との境界のうち前記境界部は、平面視で前記駆動部に最も近接している、請求項3に記載の回路基板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010526814A JP5114569B2 (ja) | 2008-08-29 | 2009-08-31 | 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ |

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222506 | 2008-08-29 | ||

| JP2008222506 | 2008-08-29 | ||

| JP2009076241 | 2009-03-26 | ||

| JP2009076241 | 2009-03-26 | ||

| JP2010526814A JP5114569B2 (ja) | 2008-08-29 | 2009-08-31 | 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ |

| PCT/JP2009/065225 WO2010024442A1 (ja) | 2008-08-29 | 2009-08-31 | 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2010024442A1 JPWO2010024442A1 (ja) | 2012-01-26 |

| JP5114569B2 true JP5114569B2 (ja) | 2013-01-09 |

Family

ID=41721601

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010526814A Expired - Fee Related JP5114569B2 (ja) | 2008-08-29 | 2009-08-31 | 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8525040B2 (ja) |

| JP (1) | JP5114569B2 (ja) |

| WO (1) | WO2010024442A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2021261757A1 (ko) * | 2020-06-22 | 2021-12-30 | 삼성전자주식회사 | 발광 다이오드 모듈 및 발광 다이오드 모듈 제조 방법 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103681725A (zh) * | 2012-09-11 | 2014-03-26 | 旭明光电股份有限公司 | 发光二极管 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002171020A (ja) * | 2000-12-01 | 2002-06-14 | Sharp Corp | 半導体レーザ装置およびそのワイヤボンディング法 |

| JP2008112883A (ja) * | 2006-10-31 | 2008-05-15 | Hitachi Cable Ltd | 発光ダイオードアレイ及び発光ダイオードアレイの製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5842628A (en) * | 1995-04-10 | 1998-12-01 | Fujitsu Limited | Wire bonding method, semiconductor device, capillary for wire bonding and ball bump forming method |

| JPH09289276A (ja) | 1996-04-23 | 1997-11-04 | Hitachi Ltd | リードフレームおよびそれを用いた半導体装置 |

| JP3895570B2 (ja) * | 2000-12-28 | 2007-03-22 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP2005150294A (ja) | 2003-11-13 | 2005-06-09 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2005236234A (ja) | 2004-02-23 | 2005-09-02 | Sharp Corp | ワイヤボンド装置、ワイヤボンド検査方法およびワイヤボンド補正方法 |

| JP4484039B2 (ja) * | 2004-06-04 | 2010-06-16 | 日立電線株式会社 | 発光ダイオードアレイ |

| JP4558539B2 (ja) * | 2005-03-09 | 2010-10-06 | 日立協和エンジニアリング株式会社 | 電子回路用基板、電子回路、電子回路用基板の製造方法および電子回路の製造方法 |

| WO2007145074A1 (ja) * | 2006-06-15 | 2007-12-21 | Sanyo Electric Co., Ltd. | 電子部品 |

-

2009

- 2009-08-31 JP JP2010526814A patent/JP5114569B2/ja not_active Expired - Fee Related

- 2009-08-31 US US13/061,097 patent/US8525040B2/en not_active Expired - Fee Related

- 2009-08-31 WO PCT/JP2009/065225 patent/WO2010024442A1/ja not_active Ceased

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002171020A (ja) * | 2000-12-01 | 2002-06-14 | Sharp Corp | 半導体レーザ装置およびそのワイヤボンディング法 |

| JP2008112883A (ja) * | 2006-10-31 | 2008-05-15 | Hitachi Cable Ltd | 発光ダイオードアレイ及び発光ダイオードアレイの製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2021261757A1 (ko) * | 2020-06-22 | 2021-12-30 | 삼성전자주식회사 | 발광 다이오드 모듈 및 발광 다이오드 모듈 제조 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110155423A1 (en) | 2011-06-30 |

| JPWO2010024442A1 (ja) | 2012-01-26 |

| US8525040B2 (en) | 2013-09-03 |

| WO2010024442A1 (ja) | 2010-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1418624B1 (en) | Light emitting diode array and print head | |

| CN1835256B (zh) | 半导体复合装置、led、led打印头和成像装置 | |

| US8664668B2 (en) | Combined semiconductor apparatus with semiconductor thin film | |

| TW201705532A (zh) | 可印刷之無機半導體結構 | |

| EP1850389A2 (en) | Composite semiconductor light emitting device, LED head that employs the composite semiconcuctor device, and image forming apparatus that employs the LED head | |

| JP2009296003A (ja) | 半導体複合装置、光プリントヘッド、及び画像形成装置 | |

| US7893455B2 (en) | Semiconductor light emitting device with stress absorber, LED printhead, and image forming apparatus | |

| JP5114569B2 (ja) | 回路基板、画像形成装置、サーマルヘッドおよびイメージセンサ | |

| JP4326884B2 (ja) | 半導体装置、ledヘッド、及び画像形成装置 | |

| JP4302720B2 (ja) | 半導体装置、ledヘッド及び画像形成装置 | |

| JP5546315B2 (ja) | 電子装置、光プリントヘッド、および画像形成装置 | |

| JP2007299955A (ja) | 電子装置、発光装置および画像形成装置 | |

| JP3485788B2 (ja) | 発光ダイオードアレイ及び光プリントヘッド | |

| JP4244672B2 (ja) | 発光素子アレイチップ | |

| JP5404709B2 (ja) | 半導体装置、led装置、ledヘッド、及び画像形成装置 | |

| JP2004195946A (ja) | 光プリンタヘッド | |

| JP2008300448A (ja) | 発光素子アレイおよび画像形成装置 | |

| JP2007157761A (ja) | 信号伝送路の接続構造および発光装置ならびに画像形成装置 | |

| JP2006303331A (ja) | 発光装置および画像形成装置 | |

| JP2011155536A (ja) | 発光素子アレイ、光プリントヘッドおよび画像形成装置 | |

| JP2002292924A (ja) | 光プリンタヘッド | |

| JP2006286981A (ja) | 発光装置および画像形成装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120918 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121015 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |