JP5114216B2 - センサ素子の再構成可能なアレイのための最適化スイッチング構成 - Google Patents

センサ素子の再構成可能なアレイのための最適化スイッチング構成 Download PDFInfo

- Publication number

- JP5114216B2 JP5114216B2 JP2007556129A JP2007556129A JP5114216B2 JP 5114216 B2 JP5114216 B2 JP 5114216B2 JP 2007556129 A JP2007556129 A JP 2007556129A JP 2007556129 A JP2007556129 A JP 2007556129A JP 5114216 B2 JP5114216 B2 JP 5114216B2

- Authority

- JP

- Japan

- Prior art keywords

- switch

- array

- subelements

- configuration

- cost function

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004422 calculation algorithm Methods 0.000 claims description 50

- 238000000034 method Methods 0.000 claims description 48

- 238000002604 ultrasonography Methods 0.000 claims description 24

- 238000012285 ultrasound imaging Methods 0.000 claims description 16

- 230000005540 biological transmission Effects 0.000 claims description 10

- 230000008859 change Effects 0.000 claims description 7

- 238000002922 simulated annealing Methods 0.000 claims description 7

- 238000010276 construction Methods 0.000 claims 1

- 239000011159 matrix material Substances 0.000 description 64

- 230000006870 function Effects 0.000 description 42

- 238000010586 diagram Methods 0.000 description 18

- 230000008569 process Effects 0.000 description 17

- 239000000758 substrate Substances 0.000 description 16

- 238000005457 optimization Methods 0.000 description 15

- 239000000523 sample Substances 0.000 description 12

- 230000004044 response Effects 0.000 description 11

- 238000003384 imaging method Methods 0.000 description 10

- 238000013507 mapping Methods 0.000 description 10

- 238000003491 array Methods 0.000 description 9

- 238000013461 design Methods 0.000 description 9

- 230000006872 improvement Effects 0.000 description 9

- 238000004088 simulation Methods 0.000 description 9

- 230000002829 reductive effect Effects 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 230000007423 decrease Effects 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 230000001934 delay Effects 0.000 description 6

- 239000004020 conductor Substances 0.000 description 5

- 241000132023 Bellis perennis Species 0.000 description 4

- 235000005633 Chrysanthemum balsamita Nutrition 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 238000004364 calculation method Methods 0.000 description 4

- 239000010408 film Substances 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 238000000137 annealing Methods 0.000 description 3

- 238000001816 cooling Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 238000011156 evaluation Methods 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 230000036961 partial effect Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 230000005855 radiation Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 238000013519 translation Methods 0.000 description 3

- 235000012431 wafers Nutrition 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000012856 packing Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 230000036755 cellular response Effects 0.000 description 1

- 230000001010 compromised effect Effects 0.000 description 1

- 238000000205 computational method Methods 0.000 description 1

- 238000005094 computer simulation Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001066 destructive effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000005242 forging Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 238000005459 micromachining Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 230000008672 reprogramming Effects 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G10—MUSICAL INSTRUMENTS; ACOUSTICS

- G10K—SOUND-PRODUCING DEVICES; METHODS OR DEVICES FOR PROTECTING AGAINST, OR FOR DAMPING, NOISE OR OTHER ACOUSTIC WAVES IN GENERAL; ACOUSTICS NOT OTHERWISE PROVIDED FOR

- G10K11/00—Methods or devices for transmitting, conducting or directing sound in general; Methods or devices for protecting against, or for damping, noise or other acoustic waves in general

- G10K11/18—Methods or devices for transmitting, conducting or directing sound

- G10K11/26—Sound-focusing or directing, e.g. scanning

- G10K11/34—Sound-focusing or directing, e.g. scanning using electrical steering of transducer arrays, e.g. beam steering

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B06—GENERATING OR TRANSMITTING MECHANICAL VIBRATIONS IN GENERAL

- B06B—METHODS OR APPARATUS FOR GENERATING OR TRANSMITTING MECHANICAL VIBRATIONS OF INFRASONIC, SONIC, OR ULTRASONIC FREQUENCY, e.g. FOR PERFORMING MECHANICAL WORK IN GENERAL

- B06B1/00—Methods or apparatus for generating mechanical vibrations of infrasonic, sonic, or ultrasonic frequency

- B06B1/02—Methods or apparatus for generating mechanical vibrations of infrasonic, sonic, or ultrasonic frequency making use of electrical energy

- B06B1/06—Methods or apparatus for generating mechanical vibrations of infrasonic, sonic, or ultrasonic frequency making use of electrical energy operating with piezoelectric effect or with electrostriction

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B06—GENERATING OR TRANSMITTING MECHANICAL VIBRATIONS IN GENERAL

- B06B—METHODS OR APPARATUS FOR GENERATING OR TRANSMITTING MECHANICAL VIBRATIONS OF INFRASONIC, SONIC, OR ULTRASONIC FREQUENCY, e.g. FOR PERFORMING MECHANICAL WORK IN GENERAL

- B06B1/00—Methods or apparatus for generating mechanical vibrations of infrasonic, sonic, or ultrasonic frequency

- B06B1/02—Methods or apparatus for generating mechanical vibrations of infrasonic, sonic, or ultrasonic frequency making use of electrical energy

- B06B1/0292—Electrostatic transducers, e.g. electret-type

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S15/00—Systems using the reflection or reradiation of acoustic waves, e.g. sonar systems

- G01S15/88—Sonar systems specially adapted for specific applications

- G01S15/89—Sonar systems specially adapted for specific applications for mapping or imaging

- G01S15/8906—Short-range imaging systems; Acoustic microscope systems using pulse-echo techniques

- G01S15/8909—Short-range imaging systems; Acoustic microscope systems using pulse-echo techniques using a static transducer configuration

- G01S15/8915—Short-range imaging systems; Acoustic microscope systems using pulse-echo techniques using a static transducer configuration using a transducer array

- G01S15/8925—Short-range imaging systems; Acoustic microscope systems using pulse-echo techniques using a static transducer configuration using a transducer array the array being a two-dimensional transducer configuration, i.e. matrix or orthogonal linear arrays

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T7/00—Image analysis

-

- A—HUMAN NECESSITIES

- A61—MEDICAL OR VETERINARY SCIENCE; HYGIENE

- A61B—DIAGNOSIS; SURGERY; IDENTIFICATION

- A61B2562/00—Details of sensors; Constructional details of sensor housings or probes; Accessories for sensors

- A61B2562/02—Details of sensors specially adapted for in-vivo measurements

- A61B2562/028—Microscale sensors, e.g. electromechanical sensors [MEMS]

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01S—RADIO DIRECTION-FINDING; RADIO NAVIGATION; DETERMINING DISTANCE OR VELOCITY BY USE OF RADIO WAVES; LOCATING OR PRESENCE-DETECTING BY USE OF THE REFLECTION OR RERADIATION OF RADIO WAVES; ANALOGOUS ARRANGEMENTS USING OTHER WAVES

- G01S7/00—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00

- G01S7/52—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00 of systems according to group G01S15/00

- G01S7/52017—Details of systems according to groups G01S13/00, G01S15/00, G01S17/00 of systems according to group G01S15/00 particularly adapted to short-range imaging

- G01S7/52046—Techniques for image enhancement involving transmitter or receiver

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Remote Sensing (AREA)

- Acoustics & Sound (AREA)

- Radar, Positioning & Navigation (AREA)

- General Physics & Mathematics (AREA)

- Mechanical Engineering (AREA)

- Multimedia (AREA)

- Computer Networks & Wireless Communication (AREA)

- Theoretical Computer Science (AREA)

- Computer Vision & Pattern Recognition (AREA)

- Ultra Sonic Daignosis Equipment (AREA)

- Transducers For Ultrasonic Waves (AREA)

- Investigating Or Analyzing Materials By The Use Of Ultrasonic Waves (AREA)

Description

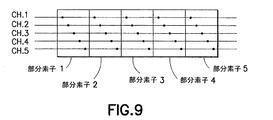

[1]どのリング(すなわち、どのシステム・チャンネル)が所与の列バス・ラインについて可能であるが決定する。例えば、アレイの頂部近くでは、外側の素子のみが存在することができる。その場合、単一のリングが可能である。中心へ向かうにつれて、全てのリングが存在するが、所与の列バス・ラインについては幾分かのリングのみ可能である。

[a]同じリングを1つの列内の2本以上のバス・ラインに割り当てることはできないこと、及び

[b]同じリングが既に前の4つの列において割り当てられていた場合、その同じリングを列バス・ラインに割り当てることはできないことである。

4 基板

6 絶縁支持体

8 膜

10 電極

12 電極

14 空洞

16 トランスデューサ部分素子

18A、18B、18C、18D 環状の素子

30 アクセス・スイッチ

30’ アクセス・スイッチ

32 cMUT部分素子

34 バス

34a〜34d 列バス・ライン

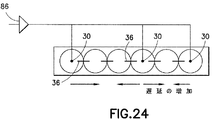

36 マトリクス・スイッチ

38 システム・チャンネル

40 接続点

42 共通接続点

46 接続線

50 CMOSセル

56 バイア

60 アレイ

62 音響裏当て層

64 ハンダ・バンプ

65 信号電極

66 導電パッド

70 マルチプレクサ

72 バス・ライン

74 バス・ライン

76 バス・ライン

80 バス・ライン

82 バス・ライン

84 バス・ライン

86 駆動装置

Claims (10)

- 再構成可能なセンサ素子アレイの制御中にスイッチ回路網によって導入されるエラーを最小にするスイッチ構成を具現化するための方法であって、

(a)初期スイッチ構成を生成する段階と、

(b)(i)複数のスイッチ構成を生成する段階、

(ii)前記複数のスイッチ構成の性能を決定する段階、

(iii)前記複数のスイッチ構成の前記性能に少なくとも部分的に基づいてコスト関数についての値を算出する段階、

(iv)算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階、及び

(v)算出した値が前記コスト関数についての最小値でない場合、前記値算出の結果の関数として現在のスイッチ構成を修正して、修正スイッチ構成に修正する段階を含み、

これらの段階(i)乃至(v)を各スイッチ構成について繰り返す反復アルゴリズムを遂行する段階と、

(c)算出した値が前記コスト関数についての最小値である場合、コスト関数の値を最小にした修正スイッチ構成により前記スイッチ回路網を構成する段階と、

を有し、

使用される前記コスト関数は、所定の閾値よりも大きいスイッチ距離を持つセンサ素子の数である、方法。 - 前記の構成する段階は、前記スイッチの状態を制御するための制御回路をプログラムする段階を含んでいる、請求項1記載の方法。

- 前記の算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階は、模擬アニーリング型のアルゴリズムを使用して遂行される、請求項1記載の方法。

- 各センサ素子はそれぞれの超音波トランスデューサ素子であり、前記段階(b)(ii)は、スイッチのオン時抵抗を測定する段階、及び超音波トランスデューサ素子の容量を測定する段階を含んでいる、請求項1記載の方法。

- 使用される前記コスト関数は用途により変わる、請求項1記載の方法。

- 前記センサ素子アレイが超音波トランスデューサ素子のアレイであり、第1のコスト関数が、前記センサ素子アレイが送信モードで動作しているときに使用するための第1のスイッチ構成を最適化するために使用され、また第2のコスト関数が、前記センサ素子アレイが受信モードで動作しているときに使用するための第2のスイッチ構成を最適化するために使用される、請求項5記載の方法。

- 前記センサ素子アレイが超音波トランスデューサ素子のアレイであり、第1のコスト関数が、前記センサ素子アレイが第1組のシステム・パラメータに従って動作しているときに使用するための第1のスイッチ構成を最適化するために使用され、また第2のコスト関数が、前記センサ素子アレイが第2組のシステム・パラメータに従って動作しているときに使用するための第2のスイッチ構成を最適化するために使用される、請求項5記載の方法。

- 前記方法は、前記センサ素子アレイの構成が変わったとき及び、前記センサ素子アレイの動作環境内の所定の温度変化が検出されたときに常に遂行される、請求項1記載の方法。

- 超音波撮像システムを動作させる方法であって、該超音波撮像システムがスイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランスデューサ素子のアレイを持ち、前記超音波撮像システムを動作させる方法が、

(a)超音波撮像システムの第1の動作状態で使用するための第1のスイッチ構成を最適化する段階と、

(b)超音波撮像システムの第2の動作状態で使用するための第2のスイッチ構成を最適化する段階とを有し、

これら最適化する段階が、反復アルゴリズムを使用してコスト関数を最小にすることを含んでおり、使用される前記コスト関数は、所定の閾値よりも大きいスイッチ距離を持つセンサ素子の数である、方法。 - 前記超音波トランスデューサ素子のアレイは、前記第1の動作状態で第1の開口構成を持ち且つ前記第2の動作状態で前記第1の開口構成とは異なる第2の開口構成を持ち、

前記超音波トランスデューサ素子のアレイは、前記第1の動作状態では送信モードで動作し且つ前記第2の動作状態では受信モードで動作する、

請求項9記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/978,175 US7353056B2 (en) | 2003-03-06 | 2004-10-29 | Optimized switching configurations for reconfigurable arrays of sensor elements |

| US10/978,175 | 2004-10-29 | ||

| PCT/US2005/030237 WO2007086817A1 (en) | 2004-10-29 | 2005-08-25 | Optimized switching configurations for reconfigurable arrays of sensor elements |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008517736A JP2008517736A (ja) | 2008-05-29 |

| JP2008517736A5 JP2008517736A5 (ja) | 2008-10-09 |

| JP5114216B2 true JP5114216B2 (ja) | 2013-01-09 |

Family

ID=37492006

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007556129A Expired - Fee Related JP5114216B2 (ja) | 2004-10-29 | 2005-08-25 | センサ素子の再構成可能なアレイのための最適化スイッチング構成 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7353056B2 (ja) |

| JP (1) | JP5114216B2 (ja) |

| KR (1) | KR101222401B1 (ja) |

| CN (1) | CN100536790C (ja) |

| DE (1) | DE112005003446T5 (ja) |

| WO (1) | WO2007086817A1 (ja) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050096545A1 (en) * | 2003-10-30 | 2005-05-05 | Haider Bruno H. | Methods and apparatus for transducer probe |

| US8008835B2 (en) * | 2004-02-27 | 2011-08-30 | Georgia Tech Research Corporation | Multiple element electrode cMUT devices and fabrication methods |

| US7545075B2 (en) * | 2004-06-04 | 2009-06-09 | The Board Of Trustees Of The Leland Stanford Junior University | Capacitive micromachined ultrasonic transducer array with through-substrate electrical connection and method of fabricating same |

| US7589456B2 (en) * | 2005-06-14 | 2009-09-15 | Siemens Medical Solutions Usa, Inc. | Digital capacitive membrane transducer |

| US7880565B2 (en) * | 2005-08-03 | 2011-02-01 | Kolo Technologies, Inc. | Micro-electro-mechanical transducer having a surface plate |

| RU2441298C2 (ru) * | 2006-06-26 | 2012-01-27 | Конинклейке Филипс Электроникс, Н.В. | Межсоединение методом перевернутого кристалла на основе сформированных соединений |

| JP4795878B2 (ja) * | 2006-07-13 | 2011-10-19 | 株式会社東芝 | 超音波診断装置及び超音波プローブを用いた超音波診断装置並びに超音波診断システム |

| US8615284B2 (en) * | 2006-09-06 | 2013-12-24 | Innurvation, Inc. | Method for acoustic information exchange involving an ingestible low power capsule |

| JP4885779B2 (ja) * | 2007-03-29 | 2012-02-29 | オリンパスメディカルシステムズ株式会社 | 静電容量型トランスデューサ装置及び体腔内超音波診断システム |

| US20080242979A1 (en) * | 2007-03-30 | 2008-10-02 | Rayette Ann Fisher | Combined X-ray detector and ultrasound imager |

| US7892176B2 (en) * | 2007-05-02 | 2011-02-22 | General Electric Company | Monitoring or imaging system with interconnect structure for large area sensor array |

| US20080296708A1 (en) * | 2007-05-31 | 2008-12-04 | General Electric Company | Integrated sensor arrays and method for making and using such arrays |

| US20080315331A1 (en) * | 2007-06-25 | 2008-12-25 | Robert Gideon Wodnicki | Ultrasound system with through via interconnect structure |

| JP5329408B2 (ja) * | 2007-07-11 | 2013-10-30 | 株式会社日立メディコ | 超音波探触子及び超音波診断装置 |

| ITTO20070779A1 (it) * | 2007-11-05 | 2009-05-06 | Fond Istituto Italiano Di T Ec | Disposizione di sensori tattili e sistema sensoriale corrispondente |

| US7781238B2 (en) * | 2007-12-06 | 2010-08-24 | Robert Gideon Wodnicki | Methods of making and using integrated and testable sensor array |

| US20090182233A1 (en) * | 2008-01-10 | 2009-07-16 | Robert Gideon Wodnicki | Ultrasound System With Integrated Control Switches |

| US8087153B2 (en) * | 2008-06-24 | 2012-01-03 | Canon Kabushiki Kaisha | Manufacturing method of an electromechanical transducer |

| US8176787B2 (en) * | 2008-12-17 | 2012-05-15 | General Electric Company | Systems and methods for operating a two-dimensional transducer array |

| US8316714B2 (en) * | 2009-07-22 | 2012-11-27 | Siemens Medical Solutions Usa, Inc. | Scan patterns for electronically positioned apertures on an array |

| US8345508B2 (en) * | 2009-09-20 | 2013-01-01 | General Electric Company | Large area modular sensor array assembly and method for making the same |

| JP5473579B2 (ja) | 2009-12-11 | 2014-04-16 | キヤノン株式会社 | 静電容量型電気機械変換装置の制御装置、及び静電容量型電気機械変換装置の制御方法 |

| US20110160591A1 (en) * | 2009-12-30 | 2011-06-30 | General Electric Company | Fetal heart rate monitor with wide search area |

| JP5659564B2 (ja) * | 2010-06-10 | 2015-01-28 | コニカミノルタ株式会社 | 超音波探触子および超音波診断装置 |

| FR2962926B1 (fr) * | 2010-07-23 | 2015-01-02 | Univ Tours Francois Rabelais | Procede et dispositif de generation d'ultrasons mettant en oeuvre des cmuts, et procede et systeme d'imagerie medicale. |

| CN102573654B (zh) | 2010-08-06 | 2014-12-10 | 奥林巴斯医疗株式会社 | 超声波诊断装置 |

| US8409102B2 (en) | 2010-08-31 | 2013-04-02 | General Electric Company | Multi-focus ultrasound system and method |

| KR101630759B1 (ko) * | 2010-12-14 | 2016-06-16 | 삼성전자주식회사 | 초음파 변환기의 셀, 채널 및 이를 포함하는 초음파 변환기 |

| JP5252016B2 (ja) * | 2011-03-18 | 2013-07-31 | 横河電機株式会社 | 振動式トランスデューサ |

| US8622752B2 (en) * | 2011-04-13 | 2014-01-07 | Teradyne, Inc. | Probe-card interposer constructed using hexagonal modules |

| DE102011108730B4 (de) | 2011-07-28 | 2015-11-12 | Ndt Global Gmbh & Co. Kg | Verfahren und Vorrichtung zur Ultraschallprüfung mit einem Matrix Phased Array Prüfkopf |

| KR101761819B1 (ko) * | 2011-08-24 | 2017-07-26 | 삼성전자주식회사 | 초음파 변환기 및 그 제조 방법 |

| JP6024154B2 (ja) * | 2012-03-30 | 2016-11-09 | セイコーエプソン株式会社 | 超音波装置、プローブ、電子機器及び診断装置 |

| EP2912789B1 (en) * | 2012-10-26 | 2017-08-02 | Rensselaer Polytechnic Institute | Acoustic-electric channel construction and operation using adaptive transducer arrays |

| US9660170B2 (en) * | 2012-10-26 | 2017-05-23 | Fujifilm Dimatix, Inc. | Micromachined ultrasonic transducer arrays with multiple harmonic modes |

| US20140155751A1 (en) * | 2012-12-05 | 2014-06-05 | Kabushiki Kaisha Toshiba | Method and system for element-by-element flexible subarray beamforming |

| US9457379B2 (en) * | 2012-12-10 | 2016-10-04 | Apple Inc. | Ultrasonic MEMS transmitter |

| US9096422B2 (en) * | 2013-02-15 | 2015-08-04 | Fujifilm Dimatix, Inc. | Piezoelectric array employing integrated MEMS switches |

| KR20220097541A (ko) | 2013-03-15 | 2022-07-07 | 버터플라이 네트워크, 인크. | 모놀리식 초음파 이미징 디바이스, 시스템 및 방법 |

| US9667889B2 (en) | 2013-04-03 | 2017-05-30 | Butterfly Network, Inc. | Portable electronic devices with integrated imaging capabilities |

| WO2014207654A2 (en) * | 2013-06-26 | 2014-12-31 | Koninklijke Philips N.V. | Integrated circuit arrangement for an ultrasound transducer array |

| CA2919183A1 (en) | 2013-07-23 | 2015-01-29 | Butterfly Network, Inc. | Interconnectable ultrasound transducer probes and related methods and apparatus |

| AU2015247501B2 (en) | 2014-04-18 | 2018-11-29 | Butterfly Network, Inc. | Ultrasonic imaging compression methods and apparatus |

| EP3132441B1 (en) * | 2014-04-18 | 2020-11-25 | Butterfly Network, Inc. | Architecture of single substrate ultrasonic imaging devices, related apparatuses |

| JP6555869B2 (ja) | 2014-10-17 | 2019-08-07 | キヤノン株式会社 | 静電容量型トランスデューサ |

| EP3229979B1 (en) * | 2014-12-11 | 2018-04-04 | Koninklijke Philips N.V. | Catheter transducer with staggered columns of micromachined ultrasonic transducers |

| US9506790B2 (en) * | 2015-03-24 | 2016-11-29 | Daniel Measurement And Control, Inc. | Transducer mini-horn array for ultrasonic flow meter |

| CN104965105B (zh) * | 2015-07-06 | 2018-03-23 | 中国科学院半导体研究所 | 集成超声换能器的afm探针阵列 |

| US10616690B2 (en) * | 2016-08-22 | 2020-04-07 | Goertek Inc. | Capacitive MEMS microphone and electronic apparatus |

| WO2018178772A2 (en) * | 2017-03-28 | 2018-10-04 | Nanofone Ltd. | High performance sealed-gap capacitive microphone |

| CN107196792B (zh) * | 2017-05-17 | 2020-08-04 | 南京大学 | 可扩展的支持动态部分重构的可重构计算配置网络系统 |

| US11619527B2 (en) | 2018-10-01 | 2023-04-04 | Micro Motion, Inc. | Ultrasonic transducer with a sealed 3D-printed mini-horn array |

| CN109350112B (zh) * | 2018-11-13 | 2020-06-12 | 飞依诺科技(苏州)有限公司 | 超声图像的成像方法、装置及医疗设备 |

| TWI706641B (zh) * | 2019-03-06 | 2020-10-01 | 奔騰智慧生醫股份有限公司 | 具備多線波束與微波束成形的系統架構與處理方法 |

| CN111855819B (zh) * | 2020-07-28 | 2023-03-24 | 广东汕头超声电子股份有限公司 | 一种无损探伤检测阵列超声探头及其焊接方法 |

| CN112371469B (zh) * | 2020-09-21 | 2021-05-07 | 南京大学 | 一种随机分布阵元间距的超声换能器线形阵列及其设计优化方法 |

| US12085646B2 (en) * | 2020-11-11 | 2024-09-10 | Siemens Medical Solutions Usa, Inc. | Matrix transducer configurable as a one-dimensional transducer in ultrasound imaging |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US48219A (en) * | 1865-06-13 | Improvement in submerged pumps | ||

| DE2628492B1 (de) * | 1976-06-25 | 1977-05-26 | Siemens Ag | Geraet zur untersuchung von koerpern durch abtastung mittels ultraschall |

| JPS5332987A (en) * | 1976-09-08 | 1978-03-28 | Hitachi Medical Corp | Method of controlling ultrasonic vibrator |

| US4307613A (en) | 1979-06-14 | 1981-12-29 | University Of Connecticut | Electronically focused ultrasonic transmitter |

| DE3019409A1 (de) | 1980-05-21 | 1982-01-21 | Siemens AG, 1000 Berlin und 8000 München | Ultraschallwandleranordnung |

| FR2553521B1 (fr) | 1983-10-18 | 1986-04-11 | Cgr Ultrasonic | Sonde d'echographie, procede de fabrication de cette sonde et appareil d'echographie incorporant une telle sonde |

| EP0215972B1 (de) | 1985-09-24 | 1990-12-05 | Hewlett-Packard GmbH | Schaltmatrix |

| US5146435A (en) | 1989-12-04 | 1992-09-08 | The Charles Stark Draper Laboratory, Inc. | Acoustic transducer |

| GB2260872B (en) * | 1991-09-20 | 1995-10-25 | Sharp Kk | An optical transmission system |

| JPH05160263A (ja) * | 1991-12-05 | 1993-06-25 | Fujitsu Ltd | Lsiの外部端子の信号配置決定方法 |

| US5568384A (en) * | 1992-10-13 | 1996-10-22 | Mayo Foundation For Medical Education And Research | Biomedical imaging and analysis |

| WO1994030030A1 (en) | 1993-06-04 | 1994-12-22 | The Regents Of The University Of California | Microfabricated acoustic source and receiver |

| US5452268A (en) | 1994-08-12 | 1995-09-19 | The Charles Stark Draper Laboratory, Inc. | Acoustic transducer with improved low frequency response |

| US5596222A (en) | 1994-08-12 | 1997-01-21 | The Charles Stark Draper Laboratory, Inc. | Wafer of transducer chips |

| US5619476A (en) | 1994-10-21 | 1997-04-08 | The Board Of Trustees Of The Leland Stanford Jr. Univ. | Electrostatic ultrasonic transducer |

| US5894452A (en) | 1994-10-21 | 1999-04-13 | The Board Of Trustees Of The Leland Stanford Junior University | Microfabricated ultrasonic immersion transducer |

| US5558623A (en) | 1995-03-29 | 1996-09-24 | Rich-Mar Corporation | Therapeutic ultrasonic device |

| US5774690A (en) * | 1995-09-14 | 1998-06-30 | The United States Of America As Represented By The Secetary Of The Navy | Method for optimization of element placement in a thinned array |

| JPH0981615A (ja) * | 1995-09-14 | 1997-03-28 | Sony Corp | 回路設計装置および方法 |

| JPH09179894A (ja) * | 1995-12-22 | 1997-07-11 | Sony Corp | 回路設計装置および方法 |

| US5737233A (en) * | 1996-01-05 | 1998-04-07 | Nec Research Institute, Inc. | VLSI circuit layout method based on spreading functions and simulated annealing heuristics to minimize area |

| US5732706A (en) | 1996-03-22 | 1998-03-31 | Lockheed Martin Ir Imaging Systems, Inc. | Ultrasonic array with attenuating electrical interconnects |

| US6159149A (en) | 1996-03-22 | 2000-12-12 | Lockheed Martin Corporation | Ultrasonic camera |

| DE19643893A1 (de) | 1996-10-30 | 1998-05-07 | Siemens Ag | Ultraschallwandler in Oberflächen-Mikromechanik |

| US5902241A (en) | 1997-11-24 | 1999-05-11 | General Electric Company | Large-aperture imaging using transducer array with adaptive element pitch control |

| US5982709A (en) | 1998-03-31 | 1999-11-09 | The Board Of Trustees Of The Leland Stanford Junior University | Acoustic transducers and method of microfabrication |

| GB9815992D0 (en) | 1998-07-23 | 1998-09-23 | Secr Defence | Improvements in and relating to microchemical devices |

| US6120449A (en) | 1998-11-25 | 2000-09-19 | General Electric Company | Method and apparatus for compensating for inoperative elements in ultrasonic transducer array |

| US6754241B1 (en) * | 1999-01-06 | 2004-06-22 | Sarnoff Corporation | Computer system for statistical multiplexing of bitstreams |

| US6183419B1 (en) | 1999-02-01 | 2001-02-06 | General Electric Company | Multiplexed array transducers with improved far-field performance |

| US6434539B1 (en) * | 1999-04-20 | 2002-08-13 | Sonetech Corporation | Method and apparatus for determining and forming delayed waveforms for forming transmitting or receiving beams for an acoustic system array of transmitting or receiving elements for imaging in non-homogenous/non-uniform mediums |

| US6381197B1 (en) | 1999-05-11 | 2002-04-30 | Bernard J Savord | Aperture control and apodization in a micro-machined ultrasonic transducer |

| US6292435B1 (en) | 1999-05-11 | 2001-09-18 | Agilent Technologies, Inc. | Circuit and method for exciting a micro-machined transducer to have low second order harmonic transmit energy |

| US6271620B1 (en) | 1999-05-20 | 2001-08-07 | Sen Corporation | Acoustic transducer and method of making the same |

| FR2798542B1 (fr) * | 1999-09-13 | 2002-01-18 | France Telecom | Recepteur a multiplexage par repartition en frequences orthogonales avec estimation iterative de canal et procede correspondant |

| EP1214909A4 (en) | 1999-09-17 | 2011-11-23 | Hitachi Medical Corp | ULTRASONIC PROBE AND ULTRASONIC DIAGNOSTIC DEVICE CONTAINING SAME |

| US6282963B1 (en) * | 1999-10-12 | 2001-09-04 | General Electric Company | Numerical optimization of ultrasound beam path |

| US6359367B1 (en) | 1999-12-06 | 2002-03-19 | Acuson Corporation | Micromachined ultrasonic spiral arrays for medical diagnostic imaging |

| US6461299B1 (en) | 1999-12-22 | 2002-10-08 | Acuson Corporation | Medical diagnostic ultrasound system and method for harmonic imaging with an electrostatic transducer |

| US6384516B1 (en) | 2000-01-21 | 2002-05-07 | Atl Ultrasound, Inc. | Hex packed two dimensional ultrasonic transducer arrays |

| US6503204B1 (en) | 2000-03-31 | 2003-01-07 | Acuson Corporation | Two-dimensional ultrasonic transducer array having transducer elements in a non-rectangular or hexagonal grid for medical diagnostic ultrasonic imaging and ultrasound imaging system using same |

| US6443901B1 (en) | 2000-06-15 | 2002-09-03 | Koninklijke Philips Electronics N.V. | Capacitive micromachined ultrasonic transducers |

| US6589180B2 (en) | 2001-06-20 | 2003-07-08 | Bae Systems Information And Electronic Systems Integration, Inc | Acoustical array with multilayer substrate integrated circuits |

| US6551248B2 (en) | 2001-07-31 | 2003-04-22 | Koninklijke Philips Electronics N.V. | System for attaching an acoustic element to an integrated circuit |

| US6585653B2 (en) | 2001-07-31 | 2003-07-01 | Koninklijke Philips Electronics N.V. | Micro-machined ultrasonic transducer (MUT) array |

| US7006955B2 (en) * | 2001-10-15 | 2006-02-28 | General Electric Company | System and method for statistical design of ultrasound probe and imaging system |

| AU2003296928A1 (en) * | 2002-11-05 | 2004-06-07 | Diagnostic Ultrasound Corporation | 3d ultrasound-based instrument for non-invasive measurement of amniotic fluid volume |

| US8094893B2 (en) * | 2002-12-02 | 2012-01-10 | Koninklijke Philips Electronics N.V. | Segmentation tool for identifying flow regions in an image system |

| US6733454B1 (en) * | 2003-02-26 | 2004-05-11 | Siemens Medical Solutions Usa, Inc. | Automatic optimization methods and systems for doppler ultrasound imaging |

| US6865140B2 (en) * | 2003-03-06 | 2005-03-08 | General Electric Company | Mosaic arrays using micromachined ultrasound transducers |

| GB0305315D0 (en) * | 2003-03-07 | 2003-04-09 | Weber Martin | Image processing system |

-

2004

- 2004-10-29 US US10/978,175 patent/US7353056B2/en not_active Expired - Fee Related

-

2005

- 2005-08-25 WO PCT/US2005/030237 patent/WO2007086817A1/en active Application Filing

- 2005-08-25 DE DE112005003446T patent/DE112005003446T5/de not_active Withdrawn

- 2005-08-25 KR KR1020077012161A patent/KR101222401B1/ko active IP Right Grant

- 2005-08-25 JP JP2007556129A patent/JP5114216B2/ja not_active Expired - Fee Related

- 2005-08-25 CN CNB2005800455716A patent/CN100536790C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE112005003446T5 (de) | 2007-12-13 |

| US7353056B2 (en) | 2008-04-01 |

| KR20070106687A (ko) | 2007-11-05 |

| WO2007086817A1 (en) | 2007-08-02 |

| JP2008517736A (ja) | 2008-05-29 |

| CN101094612A (zh) | 2007-12-26 |

| US20050096546A1 (en) | 2005-05-05 |

| CN100536790C (zh) | 2009-09-09 |

| KR101222401B1 (ko) | 2013-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5114216B2 (ja) | センサ素子の再構成可能なアレイのための最適化スイッチング構成 | |

| JP5155662B2 (ja) | センサ素子の再構成可能なアレイのためのスイッチング回路 | |

| US7257051B2 (en) | Integrated interface electronics for reconfigurable sensor array | |

| JP5525674B2 (ja) | チャネル数を低減するための再構成可能なリニアセンサアレイ | |

| JP5400477B2 (ja) | 超音波トランスデューサアレイの要素を動的に再構成する方法、スイッチネットワーク及び、超音波システム | |

| JP4751671B2 (ja) | モザイクセンサ配列走査の制御方法及びデバイス | |

| CN100452469C (zh) | 使用显微机械加工的超声换能器的镶嵌式阵列 | |

| JP3977826B2 (ja) | 超音波診断装置 | |

| US20090182233A1 (en) | Ultrasound System With Integrated Control Switches | |

| US20090182229A1 (en) | UltraSound System With Highly Integrated ASIC Architecture | |

| US20070016026A1 (en) | Transmit and receive interface array for highly integrated ultrasound scanner | |

| JP4520381B2 (ja) | 超音波診断装置 | |

| JP2007507311A (ja) | 3dイメージングのためのマイクロ加工超音波トランスデューサ・アレイ及びその操作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080821 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080821 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110105 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110218 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110322 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110329 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110615 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110830 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111011 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120925 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121015 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |