以下、図面を参照しつつ、本発明の実施の形態について説明する。なお、図面は簡略的なものであるから、この図面の記載を根拠として本発明の技術的範囲を狭く解釈してはならない。また、同一の要素には、同一の符号を付し、重複する説明は省略するものとする。また、図面は、もっぱら技術的事項の説明のためのものであり、図面に示された要素の正確な大きさ等は反映していない。

〔第1の実施の形態〕

図1に、第1の実施の形態にかかるキャッシュ機構を説明するためのブロック図を示す。図1に示された演算処理機構100は、メモリ1、キャッシュコントローラ2、CPU3、キャッシュ4、プロファイラ5、プロファイルデータキュー6、ディスクリプタコントローラ7、バススコアテーブル8、リンクリストキャッシュテーブル9、キャッシュコントロールディスクリプタテーブル10、を備える。

メモリ1には、実行されるプログラム、その他のデータが格納される。CPU3は、メモリ1に格納されたプログラムを実行する。また、メモリ1に格納されたデータにアクセスする。キャッシュコントローラ2は、メモリ1のデータをキャッシュ4にフェッチする。また、キャッシュコントローラ2は、CPU3−メモリ1間のアクセス、CPU3−キャッシュ4間のアクセスを監視したりする。本実施形態におけるキャッシュコントローラ2は、キャッシュコントロールディスクリプタテーブル10を参照して、適切なタイミングでプリフェッチする。従って、キャッシュ4には、プリフェッチにより必要なデータが格納される。

本実施形態においては、上述の、キャッシュコントローラ2、キュッシュ4、プロファイラ5、プロファイルデータキュー6、ディスクリプタコントローラ7、バススコアテーブル8、リンクリストキャッシュテーブル9、キャッシュコントロールディスクリプタテーブル10からキャッシュ機構が構成される。

以下、キャッシュ機構に含まれる構成要素について説明する。

プロファイラ5は、メモリ1へのアクセスを監視し、メモリ1へのアクセスがないタイミングを検出する。そして、そのタイミングにおけるプログラムカウンタのカウント値(以下、単にPCとする)をCPU3から取得し、このPCをプリフェッチ可能PCとしてプロファイルデータキュー6に連絡する。

プロファイラ5は、時間計測タイマを持ち、メモリ1からキャッシュ4へのデータの読み込みにどれだけの時間がかかるのかを計測する。そして、この計測結果に基づいて、プリフェッチを行うタイミングを検出する。プロファイラ5は、メモリ1へのアクセスが終了したとき、時間計測タイマを動作させる。また、メモリ1へのアクセスが開始したとき、時間計測タイマを停止する。時間計測タイマが動作中であれば、時間計測タイマのカウント値をダウンカウントする。時間計測タイマのカウント値が0であれば、記憶済みのバス開放時のPCをプリフェッチ可能PCとして、プロファイルデータキュー6に連絡する。

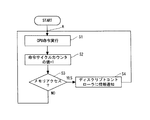

プロファイラ5により行われる処理を図2のフローチャートに示す。プロファイラ5は、メモリ1へのアクセスを監視する。プロファイラ5は、メモリ1へのアクセスの開始を検出する(S1)。アクセスの開始を検出したとき、プロファイラ5は、時間計測タイマを停止させる(S2)。そして、プロファイラ5は、そのアクセスが、キャッシュコントローラ2によるプリフェッチ時のアクセスかどうかを判断する(S3)。つまり、キャッシュコントロールディスクリプタテーブル10を参照して、キャッシュコントローラ2がメモリ1のデータをキャッシュ4にプリフェッチするときのアクセスであるか判断する。そして、プリフェッチ時のアクセスであれば、その時のPCをCPU3から取得し、そのPCをプリフェッチ可能PCとしてプロファイルデータキュー6に登録する(S4)。そして、再び、開始点Aに戻る。また、S3において、プリフェッチ時のアクセスではない場合にも、再び、開始点Aに戻る。

S1において、メモリ1へのアクセスの開始を検出しないとき、プロファイラ5は、メモリ1へのアクセスの終了を検出する(S5)。そして、メモリ1へのアクセスの終了を検出したとき、その時点でのPCをCPU3から取得し、そのPCを記憶する(S6)。また、時間計測タイマを動作させる(S7)。

S5において、メモリ1へのアクセスの終了を検出しないとき、プロファイラ5は、時間計測タイマが停止中かを確認する(S8)。時間計測タイマが停止中であれば、開始点Aに戻る。時間計測タイマが動作中であれば、ダウンカウントさせる(S9)。そして、時間計測タイマのカウント値が0であるかを確認する(S10)。時間計測タイマのカウント値が0であれば、記憶済みのPCをプロファイルデータキューにプリフェッチ可能PCとして登録する(S11)。そして、その時のPCをバス開放時のPCとする(S12)。そして、上述のS6、S7のステップを実行後、開始点Aに戻る。S10において、時間計測タイマのカウント値が0ではない場合には、開始点Aに戻る。

また、プロファイラ5は、ディスクリプタコントローラ7にCPU3からメモリ1にアクセスがあったときの情報を与える。

プロファイラ5は、命令サイクルカウンタを持ち、CPU3が命令を実行することを検出する度に、そのカウント値を1ずつ増加させる。また、プロファイラ5は、CPU3のレジスタから、CPU3によるメモリ1へのアクセス時(以下、メモリアクセス時と呼ぶこともある)のPC、メモリ1のアドレス(以下、メモリアドレスと呼ぶ)を取得する。そして、この取得した情報(PC、メモリアドレス)と上述の命令サイクルカウンタのカウント値(以下、単にカウント値と呼ぶこともある)とを、ディスクリプタコントローラ7に連絡する。

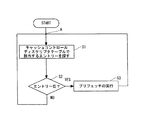

プロファイラ5により行われる処理を図3のフローチャートに示す。プロファイラ5は、CPU3が命令を1つ実行したことを検出する(S1)。そして、命令サイクルカウンタのカウント値を1増加させる(S2)。そして、そのCPU3において処理される命令が、CPU3からメモリ1へのアクセスであるのか確認する(S3)。CPU3からメモリ1へのアクセスである場合には、プロファイラ5は、ディスクリプタコントローラ7に情報を通知する(S4)。なお、通知される情報は、CPU3によるメモリアクセス時のPC、メモリアドレス、カウント値である。そして、開始点Aに戻る。S3においてメモリアクセスではない場合には、開始点Aに戻る。

上述のように、CPUからメモリへのアクセス時における所定の情報(PC、メモリアドレス、カウント値)が、プロファイラ5からディスクリプタコントローラ7に与えられる。換言すると、プロファイラ5は、CPUからメモリへのアクセスがあるたびに、所定の情報をディスクリプタコントローラ7に連絡する。そして、ディスクリプタコントローラ7は、プロファイラ5から与えられた情報に基づいて、リンクリストキャッシュテーブル9、バススコアテーブル8に後述の動作を行う。これによって、リンクリスト式のプログラム(リンクリスト構造を含むプログラム)であっても、キュッシュヒットを得る確率を高めることができる。

ディスクリプタコントローラ7は、プロファイルデータキュー6に格納されたプリフェッチ可能PCをキャッシュコントロールディスクリプタテーブル10に連絡する。また、リンクリストキャッシュテーブル9を参照した結果に基づいて、プリフェッチされるべきメモリアドレスをキャッシュコントロールディスクリプタテーブル10に連絡する。

ここで、ディスクリプタコントローラ7の動作について詳述する前に、バススコアテーブル8、リンクリストキャッシュテーブル9について説明する。

図4に、バススコアテーブル8とリンクリストキャッシュテーブル9を説明する模式図を示す。図4に示すように、バススコアテーブル8は、エントリー8eを有する。エントリー8eは、インデックスとしてのPC、メモリアドレスを格納するフィールドを有する。なお、格納されるPCとメモリアドレスとは、プロファイラ5から同時に与えられたときのものである。なお、バススコアテーブル8のエントリーには、データの在/無、メモリアドレスの有効/無効、最終PC到達サイクル、再PC到達サイクル、といったフィールドもある。最終PC到達サイクルは、プロファイラ5から与えられた最後のカウント値である。再PC到達サイクルは、今回のプロファイラ5から与えられたカウント値から、前回の最終PC到達サイクルを減算した値である。

図4に示すように、リンクリストキャッシュテーブル9は、エントリー9e1、9e2を有する。各エントリーは、インデックスとしてのメモリアドレス、リンクインデックスを有する。エントリー9e1のリンクインデックスに他のエントリー9e2のインデックスが設定されることにより、エントリー9e1とエントリー9e2とは互いに関連づけ(リンク)られる。なお、リンクインデックスには、他のエントリーのインデックスのほか、自身のエントリーのインデックスも設定される。また、各エントリーには、エントリーにおけるデータの有無、といった情報も格納される。

上述のように、CPU3によるメモリ1へのアクセスがあったとき、PC、メモリアドレス、カウント値が、プロファイラ5からディスクリプタコントローラ7に連絡される。そして、ディスクリプタコントローラ7は、リンクリストキャッシュテーブル9に次のように動作をする。

ディスクリプタコントローラ7は、プロファイラ5から与えられたメモリアドレスに基づいて、そのメモリアドレスをインデックスとするリンクリストキャッシュテーブル9のエントリーを検索する。そして、取得したエントリーの状態に応じて、そのエントリーを次のように設定する。

1−2−A:取得したエントリーにデータが無い場合。

ディスクリプタコントローラ7は、取得したエントリーのリンクインデックスに、取得したエントリー自身のインデックスを設定する。また、ディスクリプタコントローラ7は、プロファイラ5から与えられた情報に含まれるメモリアドレスを、キャッシュコントロールディスクリプタテーブル10にプリフェッチされるべきメモリアドレス(プリフェッチ用メモリアドレス)として連絡する。

1−2−B:取得したエントリーにデータが在るが、プロファイラ5から与えられたメモリアドレスとは異なるアドレスである場合。

ディスクリプタコントローラ7は、取得したエントリーのリンクインデックスに、取得したエントリー自身のインデックスを設定する。また、ディスクリプタコントローラ7は、プロファイラ5から与えられたメモリアドレスを、キャッシュコントロールディスクリプタテーブル10にプリフェッチ用メモリアドレスとして連絡する。

1−2−C:取得したエントリーにデータが在り、プロファイラ5から与えられたメモリアドレスと同じアドレスがある場合。

ディスクリプタコントローラ7は、取得したエントリーのリンクインデックスにより特定されるエントリーのメモリアドレスを、キャッシュコントロールディスクリプタテーブル10にプリフェッチ用メモリアドレスとして連絡する。換言すると、ディスクリプタコントローラ7は、プロファイラ5から与えられたメモリアドレスをキャッシュコントロールディスクリプタテーブル10に連絡しない。なお、取得したエントリーのリンクインデックスには、あらかじめ、後述の2−2−C−bの手順によって、他のエントリーとリンクされている。

また、1−2−A、1−2−Bの場合、ディスクリプタコントローラ7は、バススコアテーブル8に次のように動作をする。ディスクリプタコントローラ7は、プロファイラ5から与えられたPCに基づいて、そのPCをインデックスとするバススコアテーブル8のエントリーを取得する。そして、取得したエントリーを次のように設定する。

2−2−A:バススコアテーブル8のエントリーにデータが無い場合。

プロファイラ5から与えられたメモリアドレスを、そのエントリーのメモリアドレスに設定する。また、プロファイラ5から与えられたカウント値を、そのエントリーの最終PC到達サイクルに設定する。また、そのエントリーの再PC到達サイクルを0とする。

2−2−B:バススコアテーブル8のエントリーにデータが在り、再PC到達サイクル0の場合。

プロファイラ5から与えられたメモリアドレスを、そのエントリーのメモリアドレスに設定する。また、プロファイラ5から与えられたカウント値から、そのエントリーにある最終PC到達サイクルの値を減算する。そして、この減算値を、そのエントリーの再PC到達サイクルに設定する。また、そのエントリーの最終PC到達サイクルに、プロファイラ5から与えられたカウント値を設定する。

2−2−C:バススコアテーブル8のエントリーにデータが在り、再PC到達サイクル0でない場合。

ディスクリプタコントローラ7は、プロファイラ5から与えられたカウント値から、そのエントリーにある最終PC到達サイクルを減算する。そして、減算して得た値(以下、カウントサイクル値と呼ぶ)と、そのエントリーの再PC到達サイクルを比較する。ディスクリプタコントローラ7は、比較した結果に基づいて、そのエントリーを次のように設定する。

2−2−C−a:カウントサイクル値と再PC到達サイクルの値が異なる場合。

ディスクリプタコントローラ7は、2−2−Bの場合と同じように動作する。すなわち、ディスクリプタコントローラ7は、プロファイラ5から与えられた命令サイクルカウントのカウント値から最終PC到達サイクルを減算する。そして、減算して得たカウントサイクル値を、そのエントリーの再PC到達サイクルに設定する。また、エントリーの最終PC到達サイクルに、プロファイラ5から与えられた命令サイクルカウンタのカウントを設定する。また、プロファイラ5から与えられたメモリアドレスを、そのエントリーのメモリアドレスとして設定する。

2−2−C−b:カウントサイクル値と再PC到達サイクルの値が同じ場合。

ディスクリプタコントローラ7は、次のようにバススコアテーブル8のエントリーに動作する。そのエントリーにあるメモリアドレスに基づいて、そのメモリアドレスをインデックスとするリンクリストキャッシュテーブル9のエントリーを検索する。そして、取得したリンクリストキャッシュテーブル9のエントリーのリンクインデックスに、プロファイラ5から与えられたメモリアドレスをインデックスとするリンクリストキャッシュテーブル9のエントリーのインデックスを設定する。これによって、各エントリーはリンクされる。そして、リンクリストキャッシュテーブル9には、プログラムの実行に従ってアクセスされるメモリアドレスの順番が記憶される。この点は、以降の説明からも明らかとなる。この後、プロファイラ5から与えられたメモリアドレスを、そのエントリーのメモリアドレスとして設定する。

さらに、ディスクリプタコントローラ7の動作を、図5のフローチャートを用いて説明する。図5に示すように、まず、ディスクリプタコントローラ7は、後述するキャッシュコントロールディスクリプタテーブル10に対する処理を行う(S1)。次に、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを取得する(S2)。次に、取得したエントリーにデータが無いか確認する(S3)。エントリーにデータが無い場合、そのエントリーを2−2−Aの設定をする(S4)。そして、開始点Bに戻る。

取得したエントリーにデータがある場合には、そのエントリーにある再PC到達サイクル0か確認する(S5)。その値が0である場合には、2−2−Bの設定する(S6)。

再PC到達サイクル0ではない場合(S5)、上述のカウントサイクル値(プロファイラ5から与えられたカウント値から、そのエントリーにある最終PC到達サイクルを減算して得た値)が、取得したエントリーの再PC到達サイクルと違うか確認する(S7)。値が異なる場合、2−2−Bの設定する(S6)。そして、開始点Bに戻る。

カウントサイクル値と取得したエントリーの再PC到達サイクルが同じ場合には、2−2−C−bのように処理を実行する(S8)。そして、開始点Bに戻る。

尚、S7において、カウントサイクル値と再PC到達サイクルの値が同じであれば、一定の間隔でメモリアクセスが行われていることを確認できる。よって、2−2−C−bの処理に基づいて記憶されるメモリアドレスの順番の信頼性を高めることができる。

次に、図5のS1(ディスクリプタコントローラ7によるキャッシュコントロールディスクリプタテーブル10への動作)について説明する。図6のフローチャートに示すように、ディスクリプタコントローラ7は、プロファイラ5から与えられた情報に基づいて、CPU3からメモリ1にリードアクセスがあったか判断する(S1)。リードアクセスがあった場合、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチ動作の開始点となるプリフェッチ開始PCを得る(S2)。次に、プロファイラ5から与えられたPCに基づいて、バススコアテーブル8からエントリーを取得する(S3)。次に、取得したエントリーのメモリアドレスと、プロファイラ5から与えられたメモリアドレスとが同じか判断する(S4)。そして、アドレスが同じでない場合、プロファイラ5から与えられたメモリアドレスをプリフェッチ用のメモリアドレスとする(S5)。

取得したアドレスが同じ場合、次のようにプレフェッチ用メモリアドレスを設定する(S6)。上述の1−2−Bの場合、プロファイラ5から与えられたメモリアドレスを、プリフェッチ用のメモリアドレスとして設定する。上述の1−2−Cの場合、取得したバススコアテーブル8のエントリーのメモリアドレスをインデックスとするリンクリストキャッシュテーブル9のエントリーのリンクインデックスにリンクされたリンクリストキャッシュテーブル9のエントリーのメモリアドレスを、プリフェッチ用のメモリアドレスとして設定する。

そして、ディスクリプタコントローラ7は、上述のS5又はS6で設定したプリフェッチアドレスと、上述のS2で取得したプリフェッチ開始PCとをキャッシュコントロールディスクリプタテーブル10に連絡する(S7)。そして、上述の1−2−A、1−2−Bの場合、取得したリンクリストキャッシュテーブル9のエントリーを上述したように設定する(S8)。なお、リードアクセスが無い場合(S1)には、上述のS8の処理が実行される。

次に、キャッシュコントロールディスクリプタテーブル10について説明する。キャッシュコントロールディスクリプタテーブル10は、PCをインデックスとするエントリーがある。エントリーは、エントリーの有効/無効、プリフェッチ開始PC、プリフェッチ用メモリアドレス、のフィールドを有する。

上述のように、ディスクリプタコントローラ7は、キャッシュコントロールディスクリプタテーブル10にプリフェッチ可能PCを連絡する。また、リンクリストキャッシュテーブル9を参照した結果に基づいて、プリフェッチすべきメモリアドレスをキャッシュコントロールディスクリプタテーブル10に連絡する。そして、キャッシュコントロールディスクリプタテーブル10のエントリーには、プリフェッチ開始PCとプリフェッチ用メモリアドレスが設定される。

なお、キャッシュコントロールディスクリプタテーブル10は、ディスクリプタコントローラ7からの指令に基づいて、エントリーの登録、エントリーの削除が行われる。

次に、キャッシュコントローラ2について説明する。キャッシュコントローラ2は、CPU3から与えられる実行中のPCをインデックスとして、上述のように設定されたキャッシュコントロールディスクリプタテーブル10から該当するエントリーを探す。CPU3から与えられるPCをインデックスとするエントリーがある場合、そのタイミングで、そのエントリーにあるメモリアドレスにアクセスし、そのアドレスにあるデータをメモリ1からキャッシュ3にフェッチする。

キャッシュコントローラ2の動作を図7のフローチャートに示す。図7に示すように、キャッシュコントローラ2は、CPU3から与えられる実行中のPCに基づいて、キャッシュコントロールディスクリプタテーブル10に該当するエントリーを探す(S1)。そして、該当するエントリーがあるかどうか判断する(S2)。該当するエントリーがある場合には、そのエントリーにあるメモリアドレスにアクセスし、そのアドレスにあるデータをメモリ1からキャッシュ3にフェッチする(S3)。フェッチした後は、開始点Aに戻る。該当するエントリーがない場合には、開始点Aに戻る。

本実施形態においては、ディスクリプタコントローラ7は、上述の2−2−C−bのように動作する。これによって、リンクリストキャッシュテーブル9には、実行されるリンクリスト式のプログラムの命令の実行に伴ってアクセスされるメモリアドレスの順番が記憶される。従って、次回又はそれ以降、同じプログラムが実行された場合には、リンクリストキャッシュテーブル9に保存されたメモリアドレスの順番を活用してプリフェッチする。これによって、リンクリスト式のプログラムにおいても、キャッシュヒットする確率を高めることができる。すなわち、リンクリスト式のプログラムのように、リストセルの順番に従ってアクセスされるメモリアドレスの値が一定数で増加していないものであっても、リンクリストキャッシュテーブル9に保存された情報を活用することにより、適切にプリフェッチできる。

本実施形態のキャッシュ機構の動作について補足する。上述の2−2−C−b:カウントサイクル値と再PC到達サイクルの値が同じ場合では、ディスクリプタコントローラ7はバススコアテーブル8のエントリーにあるメモリアドレスに基づいて、そのメモリアドレスをインデックスとするリンクリストキャッシュテーブル9のエントリーを検索する。そして、取得したエントリーのリンクインデックスに、プロファイラ5から与えられたメモリアドレスをインデックスとするエントリーのインデックスを設定する。これによって、各エントリーはリンクされる。

プログラムが次回又はそれ以降に実行されるとき、ディスクリプタコントローラ7は、リンクリストキャッシュテーブル9にアクセスする。そして、1−2−C:取得したエントリーにデータが格納されており、メモリアクセス時のメモリアドレスと同じメモリアドレスがある場合が発生する。そして、ディスクリプタコントローラ7は、キャッシュコントロールディスクリプタテーブル10に取得したエントリーのリンクインデックスにより特定されるエントリーにあるメモリアドレスをプリフェッチ用メモリアドレスとして連絡する。

本実施形態では、リンクリストキャッシュテーブル9に、プログラムの実行に従ってアクセスされるメモリアドレスの順番が記憶される。従って、ディスクリプタコントローラ7は、リンクリストキャッシュテーブル9を参照することで、アクセスされる順番どおりに、プリフェッチ用メモリアドレスを取得できる。ディスクリプタコントローラ7は、プリフェッチ開始PCとともにプリフェッチ用メモリアドレスをキャッシュコントロールディスクリプタテーブル10に連絡する。キャッシュコントローラ2は、キャッシュコントロールディスクリプタテーブル10を参照することで、適切にプリフェッチを行うことができる。すなわち、本実施形態におけるキャッシュ機構は、リンクリスト式のプログラムにおいても、キャッシュヒットを得ることができる。

ここで、以下、図8に示されたプリフェッチの実行トレース表を用いて、本実施形態におけるプリフェッチ方法について説明する。なお、実行されるプログラムは、図16に示された配置サンプルであることを前提とする。また、プロファイラ5は、ループごとに5行目のPCをプロファイルデータキュー6にプリフェッチ可能PCとして連絡するものとする。

まず、リンクリスト式のプログラムの1回目の実行(プログラムの第1実行時)について説明する。なお、ループごとの実行結果については、図9を参照するものとする。

P=10のループ(サイクル2〜8間のループ)では、リストセル1の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス10である。

ディスクリプタコントローラ7は、メモリアドレス10をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル7のとき、ディスクリプタコントローラ7は、メモリアドレス10をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスを、メモリアドレス10とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8に格納されたエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル7のとき、ディスクリプタコントローラ7は、バススコアテーブル8にインデックスPC7とするエントリーを登録する。また、そのエントリーに、データが在るとする。また、そのエントリーのメモリアドレスに、メモリアドレス10を設定する。また、再PC到達サイクルに0を設定する。また、最終PC到達サイクルに7を設定する。

P=30のループ(サイクル9〜15間のループ)では、リストセル2の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス30である。

ディスクリプタコントローラ7は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル14のとき、ディスクリプタコントローラ7は、メモリアドレス30をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス30とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のサイクル7で登録したエントリーがある。そして、ディスクリプタコントローラ7は、そのエントリーにおける再PC到達サイクル0であることを確認する。そして、サイクル14のとき、そのエントリーのPCを14に変更する。また、そのエントリーのメモリアドレスに、メモリアドレス30を設定する。また、そのエントリーの再PC到達サイクルに7を設定する。また、最終PC到達サイクルに14を設定する。

P=20のループ(サイクル16〜22間のループ)では、リストセル3の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス20である。

ディスクリプタコントローラ7は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル21のとき、ディスクリプタコントローラ7は、メモリアドレス20をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス20とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のようにサイクル14で設定したエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル21からそのエントリーの最終PC到達サイクルの14を減算する。そして、減算して得たカウントサイクル値7と、そのエントリーにおける再PC到達サイクル7は等しいことを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス30(前回のループにおいてアクセスされたメモリアドレス)に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。そして、取得したメモリアドレス30をインデックスとするエントリー(前回のループにおいてアクセスされたメモリアドレスをインデックスとするエントリー)と、現在のメモリアドレス20をインデックスとするリンクリストキャッシュテーブル9のエントリー(今回のループにおいてアクセスされたメモリアドレスをインデックスとするエントリー)とをリンクさせる。具体的には、メモリアドレス30をインデックスとするエントリーのリンクインデックスに、メモリアドレス20をインデックスとするエントリーのインデックスを設定する。

図9に示すように、メモリアドレス30をインデックスとするエントリーにおけるリンクインデックスに設定された値が30から20に変更される。つまり、メモリアドレス30をインデックスとするエントリーは、自身のエントリーにリンクされていた状態から、メモリアドレス20をインデックスとするエントリーにリンクされた状態となる。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを20に設定する。また、バススコアテーブル8の最終PC到達サイクルに21を設定する。

P=40のループ(サイクル23〜29間のループ)では、リストセル4の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス40である。

ディスクリプタコントローラ7は、メモリアドレス40をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル28のとき、ディスクリプタコントローラ7は、メモリアドレス40をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス40とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のようにサイクル21で設定したエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル28からそのエントリーの最終PC到達サイクルの21を減算する。減算して得たカウントサイクル値7と、そのエントリーにおける再PC到達サイクルの値7は等しいことを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス20(前回のループにおいてアクセスされたメモリアドレス)に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス20をインデックスとするエントリー(前回のループにおいてアクセスされたメモリアドレスをインデックスとするエントリー)と、現在のメモリアドレス40をインデックスとするエントリー(今回のループにおいてアクセスされたメモリアドレスをインデックスとするエントリー)とをリンクさせる。具体的には、メモリアドレス20をインデックスとするエントリーのリンクインデックスに、メモリアドレス40をインデックスとするエントリーのインデックスを設定する。

図9に示すように、メモリアドレス20をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が20から40に変更される。つまり、メモリアドレス20をインデックスとするエントリーは、自身のエントリーにリンクされていた状態から、メモリアドレス40をインデックスとするエントリーにリンクされた状態となる。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを40に設定する。また、バススコアテーブル8の最終PC到達サイクルに28を設定する。

このようにして、リンクリスト式のプログラムが1回実行されることにより、メモリアドレス30をインデックスとするエントリーのリンクインデックスには、メモリアドレス20をインデックスとするエントリーがリンクされる。また、メモリアドレス20をインデックスとするエントリーのリンクインデックスには、メモリアドレス40をインデックスとするエントリーがリンクされる。すなわち、プログラムの命令の実行順に伴ってアクセスされるメモリアドレスの順番がリンクリストキャッシュテーブル9に記憶される。

したがって、次回以降、このプログラムが実行されるとき、メモリアドレス20をメモリアドレス30へのアクセス時にプリフェッチする。これによって、次段階で必要となるメモリアドレス20のデータをキャッシュ4に用意することができる。よって、メモリ1にCPU3はアクセスする必要はなく、キャッシュ4にアクセスすればよく、CPU3は、必要なデータを高速に取得できる。また、メモリアドレス20へのアクセス時に、メモリアドレス40をプリフェッチする。これによって、次の段階で必要となるメモリアドレス40のデータをキャッシュ4に用意することができる。よって、メモリ1にCPU3はアクセスする必要はなく、キャッシュ4にアクセスすればよい。そして、CPU3は、必要となるデータを高速に取得できる。

次に、リンクリスト式のプログラムの2回目の実行(プログラムの第2実行時)について説明する。なお、ループごとの実行結果については、図10を参照するものとする。また、2回目のループ実行時の状況は、初回のループサイクルからCサイクル隔てているものとする。

P=10のループ(サイクル2〜8間のループ)では、リストセル1の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス10である。

ディスクリプタコントローラ7は、メモリアドレス10をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス10とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス10をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス10とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、PC7をインデックスとするエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル7+Cから、そのエントリーの最終PC到達サイクル28を減算する。減算して得たカウントサイクル−21+Cと、そのエントリーにおける再PC到達サイクル0とは異なることを確率的に認識する。なお、上述のようにCサイクル隔てているため、現在のサイクルは7+Cに設定されている。

そこで、ディスクリプタコントローラ7は、そのエントリーに次のように動作する。メモリアドレスを10に設定する。また、再PC到達サイクルに、−21+Cを設定する。また、バススコアテーブル8の最終PC到達サイクルに7+Cを設定する。

P=30のループ(サイクル9〜15間のループ)では、リストセル2の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス30である。

ディスクリプタコントローラ7は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス20をインデックスとするエントリーを取得する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス20とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス30をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス30とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、PC7をインデックスとするエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル14+Cからそのエントリーの最終PC到達サイクルの7+Cを減算する。減算して得た値(カウントサイクル値)7と、そのエントリーにおける再PC到達サイクル−21+Cは異なることを確率的に認識する。

そこで、ディスクリプタコントローラ7は、そのエントリーに次のように動作する。メモリアドレスを30に設定する。また、再PC到達サイクルに7(14+Cから7+Cを減算した値)を設定する。また、バススコアテーブル8の最終PC到達サイクルに14+Cを設定する。

P=20のループ(サイクル16〜22間のループ)では、リストセル3の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス20である。

ディスクリプタコントローラ7は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス40をインデックスとするエントリーを取得する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス40とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス20をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス20とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、PC7をインデックスとするエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル21+Cからそのエントリーの最終PC到達サイクルの14+Cを減算する。減算して得た値(カウントサイクル値)7と、そのエントリーにおける再PC到達サイクル7とが同じ値であることを認識する。

そこで、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス30に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス30をインデックスとするエントリーと、現在のメモリアドレス20をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス30をインデックスとするエントリーのリンクインデックスに、メモリアドレス20をインデックスとするエントリーのインデックスを設定する。このようにして、メモリアドレス30をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が30から20に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを20に設定する。また、バススコアテーブル8の最終PC到達サイクルに21+Cを設定する。

P=40のループ(サイクル23〜29間のループ)では、リストセル4の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス40である。

ディスクリプタコントローラ7は、メモリアドレス40をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス40をインデックスとするエントリーを取得する(つまり、自身のエントリーを取得する)。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス40とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス40をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス40とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、PC7をインデックスとするエントリーがある。そして、ディスクリプタコントローラ7は、現在のサイクル28+Cからそのエントリーの最終PC到達サイクルの21+Cを減算する。減算して得た値(カウントサイクル値)7と、そのエントリーにおける再PC到達サイクルの値が7と同じ値であることを認識する。

そこで、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス20に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス20をインデックスとするエントリーと、現在のメモリアドレス40をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス20をインデックスとするエントリーのリンクインデックスに、メモリアドレス40をインデックスとするエントリーのインデックスを設定する。このようにして、メモリアドレス20をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が20から40に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを40に設定する。また、バススコアテーブル8の最終PC到達サイクルに28+Cを設定する。

このようにして、図10に示すように、キャッシュコントロールディスクリプタテーブル10には、適切なタイミングでプリフェッチを行う指示が設定される。そして、キャッシュコントローラ2は、キャッシュコントロールディスクリプタテーブル10を参照して、適切なタイミングでプリフェッチする。

〔第2の実施の形態〕

第1の実施の形態とは、ディスクリプタコントローラ7からバススコアテーブル8に対する動作が主に異なる。また、バススコアテーブル8のエントリーの内容も異なる。また、メモリ1の各メモリアドレスには、次にアクセスされるメモリアドレスを示すデータも格納されている。なお、本実施形態では、プロファイラ5は、第1の実施の形態のように、命令サイクルカウンタを有する必要はない。つまり、上記した図3におけるS2のステップは、本実施形態においては省略可能である。

バススコアテーブル8は、第1の実施の形態と同様に、PCをインデックスとするエントリーを有する。本実施形態におけるエントリーは、ステータス情報を有する。ステータス情報は、(3a)エントリーにデータが無い状態、(3b)エントリーにデータが在って、後述のロードアドレスオフセットが無しの状態、(3c)エントリーにデータが在って、後述のロードアドレスオフセットが在りの状態、の3つのステータスを示す。また、プリフェッチ開始PC、ロードアドレスオフセット、最終ロード値、を含む。

なお、本実施形態では、メモリ1の各メモリアドレスには、次にアクセスされるメモリアドレスを示すデータが格納されている。そして、次にアクセスされるメモリアドレスを示すデータは、メモリアドレスから一定のロードアドレスオフセットを加算した位置からロードされる。よって、上述の最終ロード値は、次にアクセスされるメモリアドレスに相当する。ロードアドレスオフセットは、今回のメモリアクセス時のメモリアドレスから前回のメモリアクセス時に設定された最終ロード値を減算して得た値である。したがって、ループにおいて分岐処理が行われていたとしても、第1の実施の形態と同様に、好適にプリフェッチすることができる。

ディスクリプタコントローラ7は、プロファイラ5から与えられたPCをインデックスとして、バススコアテーブル8からエントリーを得る。ディスクリプタコントローラ7は、エントリーの状態により、次のような動作をする。

3a:エントリーにデータが無い場合。

ディスクリプタコントローラ7は、エントリーにメモリアドレスを設定する。また、最終ロード値に、最後にロードした値を設定する。エントリーのステータスを、エントリーにデータ在りでロードレスアドレスオフセット無しに設定する。

3b:エントリーにデータが在って、ロードアドレスオフセットがなしの場合。

ディスクリプタコントローラ7は、プロファイラ5から与えられたメモリアドレスからエントリーの最終ロード値を減算する。そして、この減算値を、そのエントリーのロードアドレスオフセットに設定する。最終ロード値に、最後にロードした値を設定する。メモリアドレスに、プロファイラ5から与えられたメモリアドレスを設定する。エントリーのステータスをエントリーにデータ在りで、ロードアドレスオフセット在りに設定する。

3c:エントリーにデータが在って、ロードアドレスオフセットがありの場合。

ディスクリプタコントローラ7は、プロファイラ5から与えられたメモリアドレスからエントリーの最終ロード値を減算する。そして、減算して得た値とロードアドレスオフセットを比較する。ディスクリプタコントローラ7は、比較した結果に基づいて、次のように動作する。

3c−1:減算値とロードアドレスオフセットの値が異なる場合。

ディスクリプタコントローラ7は、3b:エントリーにデータが在って、かつロードアドレスオフセットがなしの場合と同じ動作をする。

3c−2:減算値とロードアドレスオフセットの値とが同じ場合。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーにあるメモリもアドレスに基づいて、そのメモリアドレスをインデックスとして、リンクリストキャッシュテーブル9からエントリーを検索する。そして、取得したリンクリストキャッシュテーブル9のエントリーが持つリンクインデックスに、プロファイラ5から与えられたメモリアドレスをインデックスとするエントリーを指定するように設定する。これによって、リンクリストキャッシュテーブル9には、プログラムの実行に伴ってアクセスされるメモリアドレスの順番が記憶される。その後に、最終ロード値に、最後にロードした値を設定する。

本実施形態におけるディスクリプタコントローラ7の動作を、図11のフローチャートを用いて説明する。

図11に示すように、まず、ディスクリプタコントローラ7は、第1の実施の形態と同様に、キャッシュコントロールディスクリプタテーブル10に対する処理を行う(S1)。次に、ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを取得する(S2)。次に、取得したエントリーにデータが無いか確認する(S3)。エントリーにデータが無い場合、そのエントリーを上述の3aのように設定する(S4)。そして、開始点Cに戻る。取得したエントリーにデータがある場合には、上述の3bの場合であるか確認する(S5)。そして、上述の3bの場合であれば、上述の3bに記載したようにエントリーの設定を行う(S6)。上述の3bの場合でなければ、上述の3c−1の場合であるのか判断する(S7)。上述の3c−1の場合であれば、上述のS6を実行する。上述の3c−1の場合でなければ、上述の3C−2のように処理を実行する(S8)。そして、開始点Cに戻る。S7において、減算値とロードアドレスオフセットの値とが同じであれば、実行されるループに分岐があったとしても問題は生じない。したがって、2−2−C−bの処理に基づいて、アクセスされるメモリアドレスの順番の記憶は問題なく行える。

ここで、以下、再び図8に示されたプリフェッチの実行トレース表を用いて、本実施形態におけるプリフェッチ方法について説明する。なお、実行されるプログラムとしては、図16に示された配置サンプルであることを前提とする。また、プロファイラ5は、ループごとに5行目のPCをプロファイルデータキュー6にプリフェッチ可能PCとして連絡するものとする。

まず、リンクリスト式のプログラムの1回目の実行(プログラムの第1実行時)について説明する。なお、ループごとの実行結果については、図12を参照するものとする。

P=10のループ(サイクル2〜8間のループ)では、リストセル1の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス10である。

ディスクリプタコントローラ7は、メモリアドレス10をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル7のとき、ディスクリプタコントローラ7は、メモリアドレス10をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス10とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

また、ディスクリプタコントローラ7は、バススコアテーブル8に格納されたエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル7のとき、ディスクリプタコントローラ7は、バススコアテーブル8にエントリーを登録する。そのエントリーに、インデックスとして、PC7を設定する。また、そのエントリーに、データが在るとする。また、そのエントリーのメモリアドレスに、メモリアドレス10を設定する。また、ステータス情報を、エントリーにデータありでロードアドレスオフセット無しとする。また、最終ロード値に、最後にロードした値30を記録させる。

P=30のループ(サイクル9〜15間のループ)では、リストセル2の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス30である。

ディスクリプタコントローラ7は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル14のとき、ディスクリプタコントローラ7は、メモリアドレス30をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス30とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、サイクル7で登録したエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット無しであることを認識する。そして、エントリーに次のように設定する。メモリアドレスに、プロファイラ5から与えられたメモリアドレス30を設定する。エントリーのステータス情報に、エントリーにデータありでロードアドレスオフセットありを設定する。ロードアドレスオフセットに、現在のプロファイラ5から与えられたメモリアドレス30から、エントリーに在る最終ロード値を減算した値0を設定する。また、最終ロード値に、最後にロードした値20を設定する。

P=20のループ(サイクル16〜22間のループ)では、リストセル3の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス20である。

ディスクリプタコントローラ7は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル21のとき、ディスクリプタコントローラ7は、メモリアドレス20をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス20とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、サイクル14で設定したエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス20から、そのエントリーにある最終ロード値20を減算する。減算して得た値0と、そのエントリーに在るロードアドレスオフセット0が同じ値であることを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス30に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス30をインデックスとするエントリーと、現在のメモリアドレス20をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス30をインデックスとするエントリーのリンクインデックスに、メモリアドレス20をインデックスとするエントリーのインデックスを設定する。そして、図12に示すように、メモリアドレス30をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が30から20に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを20に設定する。また、エントリーのステータス情報に、エントリーにデータありでロードアドレスオフセットありを設定する。また、最終ロード値に、最後にロードした値40を設定する。

P=40のループ(サイクル23〜29間のループ)では、リストセル4の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス40である。

ディスクリプタコントローラ7は、メモリアドレス40をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。しかし、該当するエントリーは存在しない。そこで、サイクル28のとき、ディスクリプタコントローラ7は、メモリアドレス40をインデックスとするエントリーを登録する。また、そのエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス40とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、サイクル21で設定したエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス40から、そのエントリーにある最終ロード値40を減算する。減算して得た値0と、そのエントリーに在るロードアドレスオフセット0が同じ値であることを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス20に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス20をインデックスとするエントリーと、現在のメモリアドレス40をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス20をインデックスとするエントリーのリンクインデックスに、メモリアドレス40をインデックスとするエントリーのインデックスを設定する。そして、図12に示すように、メモリアドレス20をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が20から40に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを40に設定する。また、エントリーのステータス情報に、エントリーにデータありでロードアドレスオフセットありを設定する。また、最終ロード値に、最後にロードした値0を設定する。

このようにして、本実施形態の場合も、リンクリスト式のプログラムが1回実行されることにより、メモリアドレス30をインデックスとするエントリーのリンクインデックスには、メモリアドレス20をインデックスとするエントリーがリンクされる。実行されるプログラムにおいては、メモリアドレス30にアクセスされた後に、メモリアドレス20にアクセスされる。したがって、次回以降、このプログラムが実行され、メモリアドレス30にアクセスされたとき、メモリアドレス20にあるデータはキャッシュ4にフェッチされる。これによって、次の段階で必要となるメモリアドレス20のデータをキャッシュ4に用意することができる。よって、CPU3は、メモリ1にアクセスする必要はなく、キャッシュ4にアクセスして必要なデータを取得できる。すなわち、プリフェッチによりキャッシュヒットを得ることができる。

また、メモリアドレス20をインデックスとするエントリーのリンクインデックスには、メモリアドレス40をインデックスとするエントリーがリンクされる。したがって、次回以降、このプログラムが実行され、メモリアドレス20にメモリアクセスされたとき、メモリアドレス40にあるデータはキャッシュ4にフェッチされる。これによって、次の段階で必要となるメモリアドレス40のデータをキャッシュ4に用意することができる。すなわち、プリフェッチによりキャッシュヒットを得ることができる。よって、CPU3は、メモリ1にアクセスする必要はなく、キャッシュ4にアクセスして、必要となるデータを取得することができる。

次に、このリンクリスト式のプログラムの2回目の実行(プログラムの第2実行時)について説明する。なお、ループごとの実行結果については、図13を参照するものとする。

P=10のループ(サイクル2〜8間のループ)では、リストセル1の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス10である。

ディスクリプタコントローラ7は、メモリアドレス10をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのメモリアドレス10をキャッシュコントロールディスクリプタテーブル10に連絡する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス10とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス10をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス10とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、PC7をインデックスとするエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス10から、そのエントリーにある最終ロード値0を減算する。減算して得た値10と、そのエントリーに在るロードアドレスオフセット0が異なる値であることを確認する。

そして、ディスクリプタコントローラ7は、そのエントリーに次のことを設定する。メモリアドレスに10を設定する。エントリーのステータス情報を、エントリーにデータ在りでロードアドレスオフセット在りを設定する。ロードアドレスオフセットに、プロファイラ5から与えられたアドレス10から、そのエントリーの最終ロード値を減算した値10を設定する。最終ロード値に、最後にロードした値30を設定する。

P=30のループ(サイクル9〜15間のループ)では、リストセル2の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス30である。

ディスクリプタコントローラ7は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス20をインデックスとするエントリーを取得する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス20とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス30をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス30とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、PC7をインデックスとするエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス30から、そのエントリーにある最終ロード値30を減算する。減算して得た値0と、そのエントリーに在るロードアドレスオフセット10が異なる値であることを確認する。

そして、ディスクリプタコントローラ7は、そのエントリーに次のことを設定する。メモリアドレスに30を設定する。エントリーのステータス情報を、エントリーにデータ在りでロードアドレスオフセット在りを設定する。ロードアドレスオフセットに、プロファイラ5から与えられたメモリアドレス30から、そのエントリーの最終ロード値30を減算した値0を設定する。最終ロード値に、最後にロードした値20を設定する。

P=20のループ(サイクル16〜22間のループ)では、リストセル3の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス20である。

ディスクリプタコントローラ7は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス40をインデックスとするエントリーを取得する。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス40とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス20をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス20とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、PC7をインデックスとするエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス20から、そのエントリーにある最終ロード値20を減算する。減算して得た値0と、そのエントリーに在るロードアドレスオフセット0が同じ値であることを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス30に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス30をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス30をインデックスとするエントリーと、現在のメモリアドレス20をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス30をインデックスとするエントリーのリンクインデックスに、メモリアドレス20をインデックスとするエントリーのインデックスを設定する。このようにして、図12に示すように、メモリアドレス30をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が30から20に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを20に設定する。また、エントリーのステータス情報に、エントリーにデータありでロードアドレスオフセットありを設定する。また、最終ロード値に、最後にロードした値40を設定する。

P=40のループ(サイクル23〜29間のループ)では、リストセル4の実行が行われる。このとき、CPU3からアクセスされるメモリ1のアドレスは、メモリアドレス40である。

ディスクリプタコントローラ7は、メモリアドレス40をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、該当するエントリーを取得する。そして、ディスクリプタコントローラ7は、このエントリーのリンクインデックスにリンクされたメモリアドレス40をインデックスとするエントリーを取得する(つまり、自身のエントリーを取得する)。

また、このとき、ディスクリプタコントローラ7は、プロファイルデータキュー6からプリフェッチの開始点となるPC5を取得する。そして、ディスクリプタコントローラ7は、PC5とメモリアドレス40とをキャッシュコントロールディスクリプタテーブル10に連絡する。

そして、ディスクリプタコントローラ7は、メモリアドレス40をインデックスとするエントリーにデータが在るとする。また、そのエントリーのメモリアドレスは、メモリアドレス40とする。また、そのエントリーのリンクインデックスには、自身のエントリーのインデックスを設定する。

ディスクリプタコントローラ7は、バススコアテーブル8のエントリーを探す。バススコアテーブル8には、上述のように、PC7をインデックスとするエントリーがある。ディスクリプタコントローラ7は、そのエントリーのステータス情報を確認する。そして、ステータス情報が、エントリーにデータがありでロードアドレスオフセット在りであることを認識する。そして、プロファイラ5から与えられたメモリアドレス40から、そのエントリーにある最終ロード値40を減算する。減算して得た値0と、そのエントリーに在るロードアドレスオフセット0が同じ値であることを確認する。

そして、ディスクリプタコントローラ7は、次のように動作する。バススコアテーブル8のエントリーに在るメモリアドレス20に基づいて、ディスクリプタコントローラ7はリンクリストキャッシュテーブル9のエントリーを探す。すなわち、バススコアテーブル8は、メモリアドレス20をインデックスとして、リンクリストキャッシュテーブル9のエントリーを探す。そして、その探したメモリアドレス20をインデックスとするエントリーと、現在のメモリアドレス40をインデックスとするエントリーとをリンクさせる。具体的には、メモリアドレス20をインデックスとするエントリーのリンクインデックスに、メモリアドレス40をインデックスとするエントリーのインデックスを設定する。このようにして、図12に示すように、メモリアドレス20をインデックスとするエントリーにおけるリンクインデックスに設定されたインデックス値が40に変更される。

また、ディスクリプタコントローラ7は、バススコアテーブル8のメモリアドレスを20に設定する。また、エントリーのステータス情報に、エントリーにデータありでロードアドレスオフセットありを設定する。また、最終ロード値に、最後にロードした値0を設定する。

図13に示すように、キャッシュコントロールディスクリプタテーブル10には、適切なタイミングでプリフェッチを行う指示が設定されることが分かる。そして、キャッシュコントローラ2は、キャッシュコントロールディスクリプタテーブル10を参照して、適切なタイミングでプリフェッチする。

本発明の技術的範囲は、上述の実施の形態に限られない。リンクリストキャッシュテーブルのエントリー同士をリンクさせる具体的な方法は任意である。エントリーのリンクリストインデックスではなく、エントリーのメモリアドレスを利用して、各エントリーをリンクさせることもできる。

プロファイラは、CPU3からメモリ1へのストア命令、リード命令のいずれかを検出しても良いし、双方を検出しても良い。プリフェッチ可能PCとされるプロファイルキューに登録されたPCは、直近に登録されたPCである必要はない。プロファイルキュー自体は、プログラムの分岐命令等により適宜リフレッシュされる。