JP5010938B2 - 待ち時間の短い基線ワンダー補償システムおよび方法 - Google Patents

待ち時間の短い基線ワンダー補償システムおよび方法 Download PDFInfo

- Publication number

- JP5010938B2 JP5010938B2 JP2007037771A JP2007037771A JP5010938B2 JP 5010938 B2 JP5010938 B2 JP 5010938B2 JP 2007037771 A JP2007037771 A JP 2007037771A JP 2007037771 A JP2007037771 A JP 2007037771A JP 5010938 B2 JP5010938 B2 JP 5010938B2

- Authority

- JP

- Japan

- Prior art keywords

- baseline wander

- candidate data

- estimate

- signal

- estimates

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/10009—Improvement or modification of read or write signals

- G11B20/10268—Improvement or modification of read or write signals bit detection or demodulation methods

- G11B20/10287—Improvement or modification of read or write signals bit detection or demodulation methods using probabilistic methods, e.g. maximum likelihood detectors

- G11B20/10296—Improvement or modification of read or write signals bit detection or demodulation methods using probabilistic methods, e.g. maximum likelihood detectors using the Viterbi algorithm

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/10009—Improvement or modification of read or write signals

- G11B20/10046—Improvement or modification of read or write signals filtering or equalising, e.g. setting the tap weights of an FIR filter

- G11B20/10203—Improvement or modification of read or write signals filtering or equalising, e.g. setting the tap weights of an FIR filter baseline correction

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/39—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes

- H03M13/41—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes using the Viterbi algorithm or Viterbi processors

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

- Error Detection And Correction (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Dc Digital Transmission (AREA)

Description

(inter−symbol interference)(ISI)で特徴付けられる任意のチャネル110とともに利用することができる。

(数1)y(k) = x(k) + n(k)

(数2)y(3) = x(3) + n(3)

(数3)u00,2 + (y(3)-a(3))2 < u01,2 + (y(3)-a'(3))2 の場合、166を生存パスとして選択する。

(数4)u00,2 + (y(3)-a(3))2 > u01,2 + (y(3)-a'(3))2の場合、168を生存パスとして選択する。

(数5)u00,2 + (y(3)-a(3))2 = u01,2 + (y(3)-a'(3))2の場合、166あるいは168をランダムに(あるいは所定の規則に則って)生存パスとして選択する。

(数6)u00,3 = min{u00,2 + (y(3)-a(3))2, u01,2 + (y(3)-a'(3))2}に設定する。

(数7)u00,2 + (y3+B(3)-a3)2 < u01,2 + (y3+B'(3)-a3')2の場合、166を生存パスとして選択する。

(数8)u00,2 + (y3+B(3)-a3)2 > u01,2 + (y3+B'(3)-a3')2の場合、168を生存パスとして選択する。

(数9)u00,2 + (y3+B(3)-a3)2 = u01,2 + (y3+B'(3)-a3')2の場合、166あるいは168をランダムに(あるいは所定の規則に則って)生存パスとして選択する。

(数10)u00,3 = min{u00,2 + (y(3)+B(3)-a(3))2, u01,2 + (y3+B'(3)-a'(3))2}に設定する。

(数11)B(k) = (1- β)B(k-1) + βa(k-1)

さらに、s領域からz領域への様々なマッピングを使用することができる。双一次変換が上述されたが、例えば本発明の範囲を逸脱せずに、インパルス不変変換(impulse invariant transforms)あるいは整合z変換(matched z−transforms)などの他の変換を利用することもできる。

(数29)B(k) = B1(k) + B2(k) - B3(k)

(数30)BT(k) = B(k) + BA(k)

(数31)y(k) = a(k) - B(k) + n(k)

従い、パスメモリ166が真の入力データ列106に対応するという仮定に基づくと、ノイズ概算n(k)は、受信された信号y(k)のノイズ成分の概算である。

(数32)BA(k) = dBA(k-1) + cn(k)

ここでcは小さな定数である。幾らかの実装例においては、d=1−cであり、BA(k)はBA(k−1)とn(k)の加重平均である。

(数33)u00,2 + (y(3)+BT(3)-a(3))2 < u01,2 + (y(3)+B'T(3)-a'(3))2の場合、166を生存パスとして選択する。

(数34)u00,2 + (y(3)+BT(3)-a(3))2 > u01,2 + (y(3)+B'T(3)-a'(3))2の場合、168を生存パスとして選択する。

(数35)u00,2 + (y(3)+BT(3)-a(3))2 = u01,2 + (y(3)+B'T(3)-a'(3))2の場合、166あるいは168をランダムに(あるいは所定の規則に則って)生存パスとして選択する。

(数36)u00,3 = min{u00,2 + (y(3)+BT(3)-a(3))2, u01,2 + (y(3)+B'T(3)-a'(3))2}に設定する。

(数38)u00,2 + (y(3)+BT(1)-a(3))2 < u01,2 + (y(3)+B'T(1)-a'(3))2の場合、166を生存パスとして選択する。

(数39)u00,2 + (y(3)+BT(1)-a(3))2 > u01,2 + (y(3)+B'T(1)-a'(3))2の場合、168を生存パスとして選択する。

(数40)u00,2 + (y(3)+BT(1)-a(3))2 = u01,2 + (y(3)+B'T(1)-a'(3))2の場合、166あるいは168をランダムに(あるいは所定の規則に則って)生存パスとして選択する。

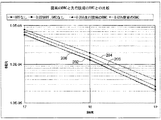

図9−13は性能結果の例を示す。より詳しくは、図9はチャネル密度が1である垂直記録チャネルの一例の性能結果を示す。HPF段階を持たず基線ワンダー概算あるいは補償を行わないチャネル例のBER202が、縦軸の対数目盛に示され、チャネル入力信号104のSNRに対してプロットされており、このプロットには菱形の印が付されている。コーナ周波数がα=0.05%であるHPF段階を持ち基線ワンダー概算あるいは補償を行わないこのチャネル例はBER204を持ち、プロットに正方形の印が付されている。図4のシステム130を使用するHPF段階を持つチャネル例は(つまり基線ワンダー概算器132を持つ)、BER206を持ち、そのプロットは三角形の印を付されている。示したように、システム130は、基線ワンダー補償を行わないシステムと比べるとBERが改善されている。最後に、図6の変更検知器150を使用するHPF段階を持つチャネルの例はBER208を持ち、そのプロットを十字の印で示す。示されているように、変更検知器150はHPF段階の歪曲低周波成分が全く無い場合と略同等なBERとなっている。

Claims (32)

- 信号を検知して検知データ列を提供する方法であって、

複数の候補データ列を提供する工程と、

前記候補データ列個々と関連付けて第一の複数の基線ワンダー概算を算出する工程と、

前記第一の複数の基線ワンダー概算と前記候補データ列個々との差異をフィルタリングする工程と、

少なくともフィルタリングされた前記差異の一部に基づき、前記候補データ列個々と関連付けて第二の複数の基線ワンダー概算を算出する工程と、

少なくとも前記第一および第二の複数の基線ワンダー概算の一部に基づき、前記候補データ列個々と関連付けて第三の複数の基線ワンダー概算を算出する工程と、

前記信号に基づくメトリックを、前記候補データ列個々に基づくメトリック個々と比較する工程であって、比較結果を前記第三の複数の基線ワンダー概算の対応するものにより補償する工程と、

前記比較結果に基づき、前記複数の候補データ列のうちの一つを前記検知データ列として選択する工程とを含む、方法。 - 前記第三の複数の基線ワンダー概算のうち対応するものにより、前記候補データ列個々に基づくメトリック個々をオフセットすることで、前記比較結果を補償する、請求項1に記載の方法。

- 前記信号に基づくメトリックを比較し、前記複数の候補データ列のうちの一つを選択する工程は、

第一段階で、前記信号に基づく第一のメトリックを、前記候補データ列個々の各々における箇所に基づくメトリックと比較することであって、比較結果を前記第一の複数の基線ワンダー概算のうち対応するものにより補償することと、

前記第一段階で、一以上の候補データ列を前記比較結果に基づき前記検知データ列の候補として切り捨てることとを含む、請求項1に記載の方法。 - 第二段階で、前記信号に基づく第二のメトリックを、前記候補データ列個々の各々における追加的箇所に基づく追加的なメトリックと比較する工程であって、前記比較結果を、前記第二の複数の基線ワンダー概算の対応するものにより補償する工程と、

前記第二段階で、追加的な候補データ列を前記比較結果に基づき前記検知データ列の候補として切り捨てる工程とをさらに含む、請求項3に記載の方法。 - 前記候補データ列はヴィテルビ・トレリスのパスメモリに対応する、請求項1から4のいずれか一項に記載の方法。

- 前記候補データ列個々に関連付けられている前記第一の複数の基線ワンダー概算は、前の段階のパスメモリに関連付けられた基線ワンダー概算に基づき現在の段階で算出された単一基線ワンダー概算を含み、前記前の段階は、前記現在の段階の前の複数の段階である、請求項5に記載の方法。

- 前記信号に基づく前記メトリックを前記候補データ列個々に基づくメトリック個々と比較する工程は、前記信号に基づく前記メトリックと、前記候補データ列個々に基づくメトリック個々の各々との間の距離尺度を算出することを含む、請求項1から6のいずれか一項に記載の方法。

- 前記距離尺度は、ユークリッド距離尺度に基づく、請求項7に記載の方法。

- 前記複数の候補データ列のうちの一つを選択する工程は、前記信号に基づくメトリックに最も近い対応するメトリックを持つ前記候補データ列を選択することを含む、請求項7に記載の方法。

- 前記第二の複数の基線ワンダー概算を算出する工程は、

受信した信号サンプルに少なくとも基づき、前記第二の複数の基線ワンダー概算を算出することを含む、請求項1に記載の方法。 - 前記第一の複数の基線ワンダー概算を算出する工程は、

基線ワンダーの源のモデルに基づき前記第一の複数の基線ワンダー概算を算出することを含む、請求項1に記載の方法。 - 前記基線ワンダーの源のモデルは、ハイパスフィルタモデルを含む、請求項11に記載の方法。

- 信号を検知して検知データ列を提供する方法であって、

複数の候補データ列を提供する工程と、

前記候補データ列個々と関連付けて基線ワンダー概算を算出する工程と、

前記基線ワンダー概算と前記候補データ列個々との差異をフィルタリングする工程と、

少なくともフィルタリングされた前記差異の一部に基づき、前記候補データ列個々と関連付けてノイズ概算を算出する工程と、

少なくとも算出された前記ノイズ概算の一部に基づき、算出された前記基線ワンダー概算を調整する工程と、

前記信号に基づくメトリックを、前記候補データ列個々に基づくメトリック個々と比較する工程であって、比較結果を前記ノイズ概算で調整した前記基線ワンダー概算の対応するものにより補償する工程と、

前記比較結果に基づき、前記複数の候補データ列のうちの一つを前記検知データ列として選択する工程とを含む、方法。 - 前記基線ワンダー概算を算出する工程は、

適応的基線ワンダー概算器を用いて前記基線ワンダー概算を算出することを含む、請求項13に記載の方法。 - 前記ノイズ概算を算出する工程は、前記ノイズ概算のうち少なくとも一つを、対応する、前に算出された適応的基線ワンダー概算と、対応する候補データ列の要素と、前に受信された前記信号の要素とに基づき算出する工程をさらに含む、請求項13に記載の方法。

- 前記基線ワンダー概算を算出する工程は、

基線ワンダー源の予め選択されたモデルに基づき、少なくとも一つの、モデルに基づく基線ワンダー概算を算出することと、

前記少なくとも一つのモデルに基づく基線ワンダー概算を、少なくとも一つの適応的基線ワンダー概算に加えることとをさらに含む、請求項13に記載の方法。 - 信号を検知して検知データ列を提供するシステムであって、

複数の候補データ列を処理する検知器と、

前記候補データ列個々と関連付けて第一の複数の基線ワンダー概算を算出し、

前記第一の複数の基線ワンダー概算と前記候補データ列個々との差異をフィルタリングし、

少なくともフィルタリングされた前記差異の一部に基づき、前記候補データ列個々と関連付けて第二の複数の基線ワンダー概算を算出し、

少なくとも前記第一および第二の複数の基線ワンダー概算の一部に基づき、前記候補データ列個々と関連付けて第三の複数の基線ワンダー概算を算出する、

基線ワンダー概算器と、

を含み、

前記検知器は、

前記信号に基づくメトリックを、前記候補データ列個々に基づくメトリック個々と比較し、比較結果を前記第三の複数の基線ワンダー概算の対応するものにより補償し、

前記比較結果に基づき、前記複数の候補データ列のうちの一つを前記検知データ列として選択するようさらに構成された、システム。 - 前記検知器は、前記第三の複数の基線ワンダー概算のうち対応するものにより、前記候補データ列個々に基づくメトリック個々をオフセットすることで、前記比較結果を補償するようさらに構成されている、請求項17に記載のシステム。

- 前記検知器は、第一段階で、前記信号に基づく第一のメトリックを、前記候補データ列個々の各々における箇所に基づくメトリックと比較し、比較結果を前記第一の複数の基線ワンダー概算のうち対応するものにより補償し、

前記第一段階で、一以上の候補データ列を前記比較結果に基づき前記検知データ列の候補として切り捨てるよう構成されている、請求項17に記載のシステム。 - 前記検知器は、

第二段階で、前記信号に基づく第二のメトリックを、前記候補データ列個々の各々における追加的箇所に基づく追加的なメトリックと比較し、比較結果を、前記第二の複数の基線ワンダー概算の対応するものにより補償し、

前記第二段階で、追加的な候補データ列を前記第二段階の前記比較結果に基づき前記検知データ列の候補として切り捨てるようさらに構成されている、請求項19に記載のシステム。 - 前記候補データ列はヴィテルビ・トレリスのパスメモリに対応する、請求項17から20のいずれか一項に記載のシステム。

- 前記候補データ列個々に関連付けられている前記第一の複数の基線ワンダー概算は、前の段階のパスメモリに関連付けられた基線ワンダー概算に基づき現在の段階で算出された単一基線ワンダー概算を含み、前記前の段階は、前記現在の段階の前の複数の段階である、請求項21に記載のシステム。

- 前記検知器は、前記信号に基づく前記メトリックと、前記候補データ列個々に基づくメトリック個々の各々との間の距離尺度を算出することにより、前記信号を前記候補データ列個々の各々と比較するようさらに構成された、請求項17から22のいずれか一項に記載のシステム。

- 前記距離尺度は、ユークリッド距離尺度に基づく、請求項23に記載のシステム。

- 前記検知器は、前記信号に基づくメトリックに最も近い対応するメトリックを持つ前記候補データ列を選択することにより、前記複数の候補データ列のうちの一つを選択するよう構成された、請求項23に記載のシステム。

- 前記基線ワンダー概算器は、

受信した信号サンプルに少なくとも基づき、前記第二の複数の基線ワンダー概算を算出することにより、

前記第二の複数の基線ワンダー概算を算出するよう構成された、請求項17に記載のシステム。 - 前記基線ワンダー概算器は、

基線ワンダーの源のモデルに基づき前記第一の複数の基線ワンダー概算を算出するよう構成された、請求項17に記載のシステム。 - 前記基線ワンダーの源のモデルは、ハイパスフィルタモデルを含む、請求項27に記載のシステム。

- 信号を検知して検知データ列を提供するシステムであって、

複数の候補データ列を処理する検知器と、

前記候補データ列個々と関連付けて基線ワンダー概算を算出し、

前記基線ワンダー概算と前記候補データ列個々との差異をフィルタリングし、

少なくともフィルタリングされた前記差異の一部に基づき、前記候補データ列個々と関連付けてノイズ概算を算出し、

少なくとも算出された前記ノイズ概算の一部に基づき、算出された前記基線ワンダー概算を調整する、

基線ワンダー概算器と、

を含み、

前記検知器は、

前記信号に基づくメトリックを、前記候補データ列個々に基づくメトリック個々と比較し、比較結果を前記ノイズ概算で調整した前記基線ワンダー概算の対応するものにより補償し、

前記比較結果に基づき、前記複数の候補データ列のうちの一つを前記検知データ列として選択するようさらに構成された、システム。 - 前記基線ワンダー概算器は、適応的基線ワンダー概算を算出するよう構成された、請求項29に記載のシステム。

- 前記基線ワンダー概算器は、前記ノイズ概算を、対応する前に算出された適応的基線ワンダー概算と、対応する候補データ列の要素と、前に受信された前記信号の要素とに基づき算出するようさらに構成された、請求項29に記載のシステム。

- 前記基線ワンダー概算器は、

基線ワンダー源の予め選択されたモデルに基づき、少なくとも一つの、モデルに基づく基線ワンダー概算を算出し、

前記少なくとも一つのモデルに基づく基線ワンダー概算を、少なくとも一つの適応的基線ワンダー概算に加えることにより、

基線ワンダー概算を算出するよう構成された、請求項29に記載のシステム。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US77516006P | 2006-02-21 | 2006-02-21 | |

| US60/775,160 | 2006-02-21 | ||

| US79038806P | 2006-04-07 | 2006-04-07 | |

| US60/790,388 | 2006-04-07 | ||

| US11/520,531 US7974366B2 (en) | 2006-02-21 | 2006-09-12 | Low-latency baseline-wander compensation systems and methods |

| US11/520,531 | 2006-09-12 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007299509A JP2007299509A (ja) | 2007-11-15 |

| JP2007299509A5 JP2007299509A5 (ja) | 2012-02-16 |

| JP5010938B2 true JP5010938B2 (ja) | 2012-08-29 |

Family

ID=38181145

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007037771A Expired - Fee Related JP5010938B2 (ja) | 2006-02-21 | 2007-02-19 | 待ち時間の短い基線ワンダー補償システムおよび方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7974366B2 (ja) |

| EP (1) | EP1833052B1 (ja) |

| JP (1) | JP5010938B2 (ja) |

| CN (1) | CN101047676B (ja) |

| SG (1) | SG135118A1 (ja) |

| TW (1) | TWI441488B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101350030B1 (ko) * | 2008-09-19 | 2014-01-13 | 에이저 시스템즈 엘엘시 | 데이터 처리 회로, 저주파 손실을 감소시키는 방법 및 저장 디바이스 |

| CN102480292A (zh) * | 2010-11-25 | 2012-05-30 | 承景科技股份有限公司 | 基线漂移校正系统及方法 |

| CN102386889B (zh) * | 2011-09-29 | 2015-08-19 | 深圳Tcl新技术有限公司 | 基线漂移去除方法、装置及中值滤波器 |

| US8902530B1 (en) * | 2012-03-30 | 2014-12-02 | Sk Hynix Memory Solutions Inc. | Decision directed and non-decision directed low frequency noise cancelation in turbo detection |

| CN105705086B (zh) * | 2013-11-08 | 2019-05-07 | 皇家飞利浦有限公司 | Ecg高通滤波器 |

| CN104776869B (zh) * | 2014-01-10 | 2019-01-22 | 深圳迈瑞生物医疗电子股份有限公司 | 一种光信号的解调方法、装置 |

| CN108259067A (zh) * | 2016-12-29 | 2018-07-06 | 深圳市中兴微电子技术有限公司 | 一种自适应判决反馈均衡的方法和装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2877109B2 (ja) * | 1996-12-12 | 1999-03-31 | 日本電気株式会社 | 情報検出装置および情報検出方法 |

| US6563892B1 (en) * | 1999-06-15 | 2003-05-13 | Telefonaktiebolaget Lm Ericsson | Method and system for detection of binary information in the presence of slowly varying disturbances |

| US6449320B1 (en) * | 1999-07-02 | 2002-09-10 | Telefonaktiebolaget Lm Ericsson (Publ) | Equalization with DC-offset compensation |

| JP3647761B2 (ja) * | 2001-03-07 | 2005-05-18 | 富士通株式会社 | データ再生方法及びデータ再生装置並びに光磁気ディスク装置 |

| WO2003050810A2 (en) * | 2001-12-07 | 2003-06-19 | Seagate Technology Llc | Method and apparatus for preprocessing low frequencies in perpendicular recording |

| US7167327B2 (en) * | 2003-01-06 | 2007-01-23 | Agere Systems Inc. | Integrated circuit and method for remodulating bits and hard disk drive incorporating the same |

| US7165211B2 (en) * | 2004-09-20 | 2007-01-16 | Guzik Technical Enterprises | Viterbi decoder with direct current restoration |

| KR20060031077A (ko) * | 2004-10-07 | 2006-04-12 | 삼성전자주식회사 | 연선을 이용하는 이더넷 수신기의 디지털 신호 처리 장치 |

-

2006

- 2006-09-12 US US11/520,531 patent/US7974366B2/en active Active

-

2007

- 2007-02-16 SG SG200701060-6A patent/SG135118A1/en unknown

- 2007-02-16 TW TW096106322A patent/TWI441488B/zh not_active IP Right Cessation

- 2007-02-19 JP JP2007037771A patent/JP5010938B2/ja not_active Expired - Fee Related

- 2007-02-21 EP EP07003582.9A patent/EP1833052B1/en not_active Not-in-force

- 2007-02-25 CN CN200710100616.6A patent/CN101047676B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007299509A (ja) | 2007-11-15 |

| EP1833052A1 (en) | 2007-09-12 |

| CN101047676A (zh) | 2007-10-03 |

| CN101047676B (zh) | 2015-02-11 |

| TW200742361A (en) | 2007-11-01 |

| US20070195912A1 (en) | 2007-08-23 |

| EP1833052B1 (en) | 2013-04-10 |

| US7974366B2 (en) | 2011-07-05 |

| SG135118A1 (en) | 2007-09-28 |

| TWI441488B (zh) | 2014-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5010938B2 (ja) | 待ち時間の短い基線ワンダー補償システムおよび方法 | |

| KR100968336B1 (ko) | 판독 채널, 정보 판독 방법 및 컴퓨터 판독가능 저장 매체 | |

| US7961797B1 (en) | Nonlinear viterbi complexity reduction | |

| EP0751519B1 (en) | A reduced complexity EPR4 post-processor for sampled data detection | |

| US20040071206A1 (en) | Digital filter adaptively learning filter coefficient | |

| JP2007299509A5 (ja) | ||

| JP4945955B2 (ja) | タップ係数設計方法及びタップ係数設計装置 | |

| US7948703B1 (en) | Adaptive target optimization methods and systems for noise whitening based viterbi detectors | |

| JP2012517654A (ja) | 適応的ベースライン補償のためのシステム及び方法 | |

| US5931966A (en) | Viterbi detector with a pipelined look-up table of squared errors | |

| US20100322353A1 (en) | Nonlinear post-processors for channels with signal-dependent noise | |

| US10692527B1 (en) | Target parameter adaptation | |

| JP3033238B2 (ja) | 適応的最尤復号装置および復号方法 | |

| US6377635B1 (en) | Method and apparatus for viterbi detection of generalized partial response signals using partial matched filter and matched filter metrics | |

| KR100474819B1 (ko) | 데이터기록/재생장치의신호검출방법및그장치 | |

| JP4916728B2 (ja) | 符号化装置、信号処理装置、および記憶システム | |

| JP2001344903A (ja) | デジタル情報再生装置 | |

| KR100297827B1 (ko) | 고밀도저장기기에있어서디코딩방법및장치 | |

| US20140334028A1 (en) | Systems and Methods for Processing Data With Linear Phase Noise Predictive Filter | |

| JP5099035B2 (ja) | デジタルフィルタ | |

| US7535955B1 (en) | Methods, algorithms, software, architectures, systems and circuitry for adaptive filtering and/or minimizing a sequence detector error rate | |

| JP2007273016A (ja) | 再生信号処理装置 | |

| JPH11238320A (ja) | 信号処理方法およびそれを用いた記録再生装置 | |

| JP2007087461A (ja) | 信号処理方法及び信号処理装置 | |

| JPH10255214A (ja) | デジタル信号復号装置、磁気情報再生装置および磁気情報の再生信号の波形歪補正方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110920 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110927 |

|

| A524 | Written submission of copy of amendment under section 19 (pct) |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20111227 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120529 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120604 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5010938 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150608 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees | ||

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |