JP4939735B2 - Semiconductor integrated circuit device - Google Patents

Semiconductor integrated circuit device Download PDFInfo

- Publication number

- JP4939735B2 JP4939735B2 JP2004179692A JP2004179692A JP4939735B2 JP 4939735 B2 JP4939735 B2 JP 4939735B2 JP 2004179692 A JP2004179692 A JP 2004179692A JP 2004179692 A JP2004179692 A JP 2004179692A JP 4939735 B2 JP4939735 B2 JP 4939735B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- element formation

- formation region

- integrated circuit

- circuit device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Element Separation (AREA)

Description

本発明は、半導体集積回路装置およびその製造方法に関し、特に、細長い素子形成領域が並行に形成された半導体集積回路装置に適用して有効な技術に関するものである。 The present invention relates to a semiconductor integrated circuit device and a method for manufacturing the same, and more particularly to a technique effective when applied to a semiconductor integrated circuit device in which elongated element formation regions are formed in parallel.

半導体集積回路装置は、絶縁膜で区画された素子形成領域(アクティブ)の主表面に形成された素子や配線からなる。この素子形成領域は、例えば、素子分離領域により他の素子形成領域と分離され、この素子分離領域は、例えば、素子分離絶縁膜で形成される。素子分離絶縁膜は、例えば、STI(Shallow Trench Isolation)技術を用いて形成される。このSTIとは、半導体基板に形成した溝の上部に酸化シリコン膜などの絶縁膜を堆積し、溝外部の酸化シリコン膜を化学的機械研磨(CMP;Chemical Mechanical Polishing)法等により除去することにより溝の内部に酸化シリコン膜を埋め込み、これを素子間の分離に用いるというものである。 A semiconductor integrated circuit device includes elements and wirings formed on the main surface of an element formation region (active) partitioned by an insulating film. This element formation region is separated from other element formation regions by an element isolation region, for example, and this element isolation region is formed by, for example, an element isolation insulating film. The element isolation insulating film is formed using, for example, an STI (Shallow Trench Isolation) technique. In this STI, an insulating film such as a silicon oxide film is deposited on the upper part of the groove formed in the semiconductor substrate, and the silicon oxide film outside the groove is removed by a chemical mechanical polishing (CMP) method or the like. A silicon oxide film is embedded in the groove and used for isolation between elements.

例えば、電気的書き込みおよび消去が可能な不揮発性メモリ(EEPROM:Electrically Erasable Programmable Read Only Memory)等のメモリLSI(Large Scale Integrated Circuit)は、一定の間隔(ピッチ)で並行に配置された、細長い素子形成領域上に形成される。 For example, a memory LSI (Large Scale Integrated Circuit) such as an electrically erasable programmable read only memory (EEPROM) is an elongated element arranged in parallel at a constant interval (pitch). It is formed on the formation region.

このような素子形成領域は、メモリセルの微細化および高集積化に伴い、その幅がより小さくなり、また、狭ピッチで配置される傾向にある。 Such element formation regions tend to be smaller in width and arranged at a narrower pitch with the miniaturization and higher integration of memory cells.

なお、メモリセルの微細化に対応するため、いわゆるSAC(Self-Aligned Contact)技術を用いてドレインコンタクトを形成したNOR型のフラッシュメモリについては、例えば、IEDM(International Electron Devices Meeting),1998,pp979−982,“A Novel 4.6F2NOR Cell Technology With Lightly Doped Source(LDS) Junction For High Density Flash Memories”(非特許文献1)に、記載されている。

本発明者らは、半導体記憶装置、特に、前述のような不揮発性メモリについて検討した結果、下記の公知でない課題を見いだした。 As a result of studying semiconductor memory devices, particularly nonvolatile memories as described above, the present inventors have found the following unknown problems.

即ち、素子の微細化が進むにつれ、メモリセルの不良が増加する。この原因について検討した結果、素子形成領域の端部に生じる結晶欠陥が原因ではないかと考えている。 That is, as the device becomes finer, the number of memory cell defects increases. As a result of examining this cause, it is thought that the crystal defect which arises in the edge part of an element formation area may be the cause.

即ち、半導体集積回路装置内のメモリセル形成領域の外周部には、メモリセルを駆動するために必要な論理回路等(以下、周辺回路という)が形成される周辺回路形成領域が存在する。従って、メモリセルが形成される細長い素子形成領域が、狭いピッチで配置されたその周辺には、周辺回路が形成される他の素子形成領域が配置され、これらの素子形成領域間は、幅の広い絶縁膜で分離される。 That is, there is a peripheral circuit formation region in which a logic circuit or the like (hereinafter referred to as a peripheral circuit) necessary for driving the memory cell is formed at the outer periphery of the memory cell formation region in the semiconductor integrated circuit device. Accordingly, in the periphery of the elongated element formation region in which the memory cells are formed, arranged at a narrow pitch, another element formation region in which a peripheral circuit is formed is disposed, and the width between these element formation regions is Separated by a wide insulating film.

従って、後述する実施の形態で詳細に説明するように、メモリセルが形成される細長い素子形成領域の端部に、応力が集中し結晶欠陥が生じやすい。 Therefore, as will be described in detail in the embodiments described later, stress is concentrated at the end of the elongated element formation region where the memory cell is formed, and crystal defects are likely to occur.

このような欠陥が生じると、メモリセルのドレイン領域と半導体基板との間や、ソース領域とドレイン領域との間の、リーク電流が増加してしまう。さらに、このリーク電流が、センスアンプの動作電流以上になった場合には、不良となってしまう。 When such a defect occurs, a leakage current increases between the drain region of the memory cell and the semiconductor substrate, or between the source region and the drain region. Furthermore, if this leakage current is greater than or equal to the operating current of the sense amplifier, it becomes defective.

また、前述したように、細長い素子形成領域上には、複数のメモリセルが形成されているため、一つのメモリセル内に欠陥が生じたとしても、かかるメモリセルと同一のデータ線に接続されているメモリセルが、すべて不良となってしまう。 As described above, since a plurality of memory cells are formed on the elongated element formation region, even if a defect occurs in one memory cell, it is connected to the same data line as that memory cell. All the memory cells that are present become defective.

本発明の目的は、素子形成領域内の半導体基板の欠陥を低減させることにある。 An object of the present invention is to reduce defects in a semiconductor substrate in an element formation region.

また、本発明の他の目的は、素子形成領域内の半導体基板の欠陥を低減させることによりリーク電流の低減を図ることにある。 Another object of the present invention is to reduce leakage current by reducing defects in the semiconductor substrate in the element formation region.

また、本発明の他の目的は、リーク電流の低減を図ることにより、製品の歩留まり向上や信頼性の向上を図ることにある。 Another object of the present invention is to improve product yield and reliability by reducing leakage current.

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。 The above and other objects and novel features of the present invention will be apparent from the description of this specification and the accompanying drawings.

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。 Of the inventions disclosed in the present application, the outline of typical ones will be briefly described as follows.

(1)本発明の半導体集積回路装置は、メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、第1の方向と垂直な第2の方向に2以上配置された素子形成領域の端部を、メモリセルを囲むように形成された導電性膜の下まで伸長したものである。 (1) A semiconductor integrated circuit device according to the present invention is an element formation region in which a memory cell is formed, and is partitioned by an insulating film, and the element formation region extending in the first direction is perpendicular to the first direction. One or more end portions of the element formation regions arranged in the second direction are extended to below the conductive film formed so as to surround the memory cell.

(2)本発明の半導体集積回路装置は、絶縁膜によって区画され、第1方向に延在する素子形成部を、第1の方向と垂直な第2の方向に2以上配置し、この素子形成部の端部を第2方向に延在する接続部で接続したものである。 (2) In the semiconductor integrated circuit device of the present invention, two or more element forming portions that are partitioned by an insulating film and extend in the first direction are arranged in a second direction perpendicular to the first direction. The end of each part is connected by a connecting part extending in the second direction.

(3)本発明の半導体集積回路装置は、メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、第1の方向と垂直な第2の方向に複数配置された素子形成領域のうち、最外の素子形成領域の第2方向の幅を、他の素子形成領域の幅より広くするものである。 (3) The semiconductor integrated circuit device of the present invention is an element formation region in which a memory cell is formed, and is partitioned by an insulating film, and the element formation region extending in the first direction is perpendicular to the first direction. Of the element formation regions arranged in the second direction, the width of the outermost element formation region in the second direction is made wider than the width of other element formation regions.

(4)本発明の半導体集積回路装置は、メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、第1の方向と垂直な第2の方向に複数配置された素子形成領域のうち、最外の素子形成領域上にはメモリセルとして機能するメモリセルを形成しないものである。 (4) A semiconductor integrated circuit device according to the present invention is an element formation region in which a memory cell is formed, and is partitioned by an insulating film, and the element formation region extending in the first direction is perpendicular to the first direction. Of the element formation regions arranged in the second direction, a memory cell functioning as a memory cell is not formed on the outermost element formation region.

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。 The effects obtained by the representative ones of the inventions disclosed by the present application will be briefly described as follows.

メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、前記第1の方向と垂直な第2の方向に2以上配置された素子形成領域の端部を、メモリセルを囲むように形成された導電性膜の下まで伸長したので、この伸長した領域に応力を集中させることができ、モリセルが形成される領域まで欠陥が延びず、メモリセルのリーク電流を低減することができる。 An element forming region in which a memory cell is formed, wherein two or more element forming regions defined by an insulating film and extending in a first direction are arranged in a second direction perpendicular to the first direction. Since the end of the formation region is extended under the conductive film formed so as to surround the memory cell, stress can be concentrated in this extended region, and the defect does not extend to the region where the Mori cell is formed. The leakage current of the memory cell can be reduced.

また、絶縁膜によって区画され、第1方向に延在する素子形成部を、第1の方向と垂直な第2の方向に2以上配置し、この素子形成部の端部を第2方向に延在する接続部で接続したので、応力の加わる方向を変化させることができ、メモリセルのリーク電流を低減することができる。 Further, two or more element forming portions that are partitioned by an insulating film and extend in the first direction are arranged in a second direction perpendicular to the first direction, and an end portion of the element forming portion extends in the second direction. Since the connection is performed at the existing connection portion, the direction in which the stress is applied can be changed, and the leakage current of the memory cell can be reduced.

また、メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、前記第1の方向と垂直な第2の方向に複数配置された素子形成領域のうち、最外の素子形成領域の前記第2方向の幅を、他の素子形成領域の幅より広くしたので、応力の影響を緩和することができ、メモリセルのリーク電流を低減することができる。 An element formation region in which a memory cell is formed, and a plurality of element formation regions which are partitioned by an insulating film and extend in the first direction are arranged in a second direction perpendicular to the first direction. Of the element formation regions, the width of the outermost element formation region in the second direction is wider than the width of other element formation regions, so that the influence of stress can be reduced and the leakage current of the memory cell is reduced. can do.

また、メモリセルが形成される素子形成領域であって、絶縁膜によって区画され、第1方向に延在する素子形成領域が、前記第1の方向と垂直な第2の方向に複数配置された素子形成領域のうち、最外の素子形成領域上にはメモリセルとして機能するメモリセルを形成していないので、この最外の素子形成領域に応力を集中させることができ、メモリセルのリーク電流を低減することができる。 An element formation region in which a memory cell is formed, and a plurality of element formation regions which are partitioned by an insulating film and extend in the first direction are arranged in a second direction perpendicular to the first direction. Since no memory cell that functions as a memory cell is formed on the outermost element formation region in the element formation region, stress can be concentrated on the outermost element formation region, and the leakage current of the memory cell Can be reduced.

その結果、製品の歩留まり向上や信頼性の向上を図ることができる。 As a result, it is possible to improve product yield and reliability.

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。 Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Note that components having the same function are denoted by the same reference symbols throughout the drawings for describing the embodiments, and the repetitive description thereof is omitted.

(実施の形態1)

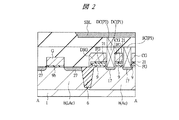

図1に本実施の形態の半導体集積回路装置の要部平面図を示す。図1の右部は、メモリセル形成領域MCFRを示し、左部は、周辺回路形成領域PCFRを示す。メモリセル形成領域MCFRには、NOR型の不揮発性メモリセルがアレイ状MCARに配置され、周辺回路形成領域には、周辺回路の一例として選択用MISFET Sが形成されている。図2は、図1のA−A断面の概略図であり、図3は、図1のB−B断面の概略図である。

(Embodiment 1)

FIG. 1 shows a plan view of the main part of the semiconductor integrated circuit device of the present embodiment. The right part of FIG. 1 shows the memory cell formation region MCFR, and the left part shows the peripheral circuit formation region PCFR. In the memory cell formation region MCFR, NOR-type nonvolatile memory cells are arranged in an array MCAR, and in the peripheral circuit formation region, a selection MISFET S is formed as an example of a peripheral circuit. 2 is a schematic view of the AA cross section of FIG. 1, and FIG. 3 is a schematic view of the BB cross section of FIG.

図1に示すように、メモリセル形成領域には、X方向に延在した素子形成領域(アクティブ)Acが、Y方向に一定の間隔毎に配置されている。この素子形成領域Acは、例えば、酸化シリコン膜6等よりなる絶縁膜6で区画(規定)されている。即ち、素子形成領域Ac間は、素子分離絶縁膜である絶縁膜6で分離されている。この絶縁膜6は、図2および図3に示すように、例えば、半導体基板中の溝の内部に埋め込まれたSTI構造で形成されている。また、素子形成領域Acは、p型ウエル8が半導体基板1表面に露出した領域である。

As shown in FIG. 1, in the memory cell formation region, element formation regions (active) Ac extending in the X direction are arranged at regular intervals in the Y direction. The element formation region Ac is partitioned (defined) by an

この素子形成領域AcのY方向の幅Wは、例えば、約0.3μmであり、素子形成領域Ac間の間隔SWは、例えば、約0.4μmである。また、素子形成領域Acの長さ(X方向の幅)は、X方向に形成される例えば、128ビットのメモリセルMCに対応し、約80μmである。即ち、素子形成領域Acには、X方向に複数のメモリセルMCが形成されている。 The width W of the element formation region Ac in the Y direction is, for example, about 0.3 μm, and the interval SW between the element formation regions Ac is, for example, about 0.4 μm. The length (width in the X direction) of the element formation region Ac corresponds to, for example, a 128-bit memory cell MC formed in the X direction, and is about 80 μm. That is, a plurality of memory cells MC are formed in the X direction in the element formation region Ac.

この素子形成領域Acの上部には、Y方向に延在する制御電極(第2電極)CGが、一定の間隔毎に配置されている。この制御電極CGのX方向の幅Lは、例えば、約0.3μmであり、制御電極CG間の間隔LSは、例えば、約0.35μmである。また、この制御電極CGは、Y方向に配置されるメモリセルMCの制御電極CGと一体に形成されるとともに、Y方向に延在するワード線WLとなる。 Control electrodes (second electrodes) CG extending in the Y direction are arranged at regular intervals above the element formation region Ac. The width L in the X direction of the control electrode CG is, for example, about 0.3 μm, and the distance LS between the control electrodes CG is, for example, about 0.35 μm. The control electrode CG is formed integrally with the control electrode CG of the memory cell MC arranged in the Y direction, and becomes a word line WL extending in the Y direction.

この制御電極CGと素子形成領域Acとの間には、図2および図3に示すように、例えば、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜が順次積層された積層膜(以下、ONO膜という)21等よりなる絶縁膜、浮遊電極(第1電極)FGおよび熱酸化膜等よりなるゲート絶縁膜9が形成されている。この浮遊電極FGは、メモリセル毎に独立して形成されている(図3参照)。

Between the control electrode CG and the element formation region Ac, as shown in FIGS. 2 and 3, for example, a laminated film (hereinafter referred to as an ONO film) in which a silicon oxide film, a silicon nitride film, and a silicon oxide film are sequentially laminated. An insulating film made of 21 or the like, and a

この制御電極CGの両端の素子形成領域Ac中には、n+型半導体領域17(ソース、ドレイン領域)が形成されており、ドレイン領域17上には、プラグ(ドレインコンタクト)DC(P1)が、ソース領域17上には、プラグ(ソースコンタクト)SC(P1)が形成されている。このプラグDC(P1)は、メモリセル毎に独立して形成されているが、プラグSC(P1)は、同一のワード線WLに接続されるメモリセルMCのソース領域17の各々に電気的に接続されるとともに、Y方向に延在するソース線SLを構成する。即ち、プラグ(ソースコンタクト)SC(P1)は、Y方向に延在する配線であり、ソース線SLを構成する。後述するように、プラグDC(P1)とプラグSC(P1)とは、同じ製造工程で形成される。

In the element formation regions Ac at both ends of the control electrode CG, n + type semiconductor regions 17 (source and drain regions) are formed, and plugs (drain contacts) DC (P1) are formed on the

また、ドレイン領域17上は、プラグDC(P1)およびプラグDC(P2)による2層構造となっており、このプラグDC(P2)上には、副ビット線SBLが形成されている。この副ビット線SBLは、X方向に延在している。

Further, the

また、プラグSC(P1)は、図1に示すように、このプラグSC(P2)を介して共通のソース線CSLに接続されている。この共通ソース線CSLもX方向に延在しており、副ビット線SBLと同層の配線層で形成される。後述するように、プラグDC(P2)とプラグSC(P2)とは、同じ製造工程で形成される。 Further, as shown in FIG. 1, the plug SC (P1) is connected to a common source line CSL via the plug SC (P2). This common source line CSL also extends in the X direction, and is formed of the same wiring layer as the sub-bit line SBL. As will be described later, the plug DC (P2) and the plug SC (P2) are formed in the same manufacturing process.

このように、メモリセルMCは、主に、ソース、ドレイン領域である一対のn+型半導体領域17と、それらの間に形成されたチャネル形成領域(p型ウエル)8(Ac)と、チャネル形成領域上に形成されたゲート絶縁膜9と、ゲート絶縁膜9上に形成された浮遊電極(フローティングゲート)FGと、浮遊電極FG上に形成された絶縁膜21と、絶縁膜21上に形成された制御電極(コントロールゲート)CGとで構成される。Y方向に隣接するメモリセルMCのソース、ドレイン領域17間は、絶縁膜6により分離され、Y方向に配置されるメモリセルMCの制御電極CGは、ワード線WLと一体に形成される。Y方向に配置されるメモリセルMCのドレイン領域17は、プラグDC(P1)、DC(P2)を介して、それぞれ異なる副ビット線SBLに電気的に接続され、Y方向に配置されるメモリセルMCのソース領域17のそれぞれは、ソース線SLにより電気的に接続される。また、X方向に隣接するメモリセルMCのドレイン領域は共通に構成され、副ビット線SBLに電気的に接続される。X方向に隣接するメモリセルMCのソース領域17は共通に構成されソース線SLに電気的に接続される。

Thus, the memory cell MC mainly includes a pair of n +

ここで、メモリセルの書き込み、読み出しおよび消去動作について説明する。 Here, writing, reading and erasing operations of the memory cell will be described.

まず、書き込み動作について説明する。メモリセルにデータを書き込むには、メモリセルの制御電極CG(ワード線WL)に例えば9Vの電圧を印加し、メモリセルのドレイン領域(副ビット線SBL)に例えば4Vの電圧を印加し、素子形成領域Ac(p型ウエル8)に例えば3Vの電圧を印加し、メモリセルのソース領域(ソース線SL)を例えば0V(接地電位)に維持する。その結果、メモリセルのチャネル領域(ソース、ドレイン領域間)にホットエレクトロンが発生し、これが浮遊電極FGに注入される。 First, the write operation will be described. In order to write data to the memory cell, for example, a voltage of 9V is applied to the control electrode CG (word line WL) of the memory cell, a voltage of 4V is applied to the drain region (subbit line SBL) of the memory cell, and the element For example, a voltage of 3V is applied to the formation region Ac (p-type well 8), and the source region (source line SL) of the memory cell is maintained at, for example, 0V (ground potential). As a result, hot electrons are generated in the channel region (between the source and drain regions) of the memory cell and injected into the floating electrode FG.

次に、読み出し動作について説明する。メモリセルのデータを読み出すには、メモリセルの制御電極CG(ワード線WL)に例えば2.7Vの電圧を印加し、メモリセルのドレイン領域(副ビット線SBL)に例えば0.8Vの電圧を印加し、素子形成領域Ac(p型ウエル8)およびメモリセルのソース領域(ソース線SL)を例えば0Vに維持する。この際メモリセルのソース、ドレイン領域間に電流が流れるか否かで、メモリセルのデータ(“1”もしくは“0”)を読み出す。電流が流れる場合は、メモリセルの浮遊電極FGには電子が注入されておらず(閾値電圧以下であり)、例えば、“0”のデータが記憶されていたことがわかる。また、電流が流れない場合は、メモリセルの浮遊電極FGには電子が注入されており(閾値電圧以上であり)、例えば、“1”のデータが記憶されていたことがわかる。 Next, the reading operation will be described. In order to read data in the memory cell, a voltage of, for example, 2.7 V is applied to the control electrode CG (word line WL) of the memory cell, and a voltage of, for example, 0.8 V is applied to the drain region (subbit line SBL) of the memory cell. The voltage is applied to maintain the element formation region Ac (p-type well 8) and the source region (source line SL) of the memory cell at, for example, 0V. At this time, data (“1” or “0”) of the memory cell is read out depending on whether or not a current flows between the source and drain regions of the memory cell. When the current flows, it can be seen that electrons are not injected into the floating electrode FG of the memory cell (below the threshold voltage), and for example, data of “0” is stored. When no current flows, it can be seen that electrons have been injected into the floating electrode FG of the memory cell (above the threshold voltage), and for example, data of “1” was stored.

次いで、消去動作について説明する。メモリセルに書き込まれたデータを消去するには、メモリセルの制御電極CG(ワード線WL)に例えば10.5Vの電圧を印加し、素子形成領域Ac(p型ウエル8)およびメモリセルのドレイン領域(副ビット線SBL)に例えば10.5Vの電圧を印加し、メモリセルのソース領域(ソース線SL)をフローティング状態(開放状態、open状態)に維持する。その結果、FN(Fowler-Nordheim)トンネル現象により、制御電極CGからメモリセルのチャネル領域(ソース、ドレイン領域間)に、電子の放出が行われる。 Next, the erase operation will be described. In order to erase the data written in the memory cell, a voltage of, for example, 10.5 V is applied to the control electrode CG (word line WL) of the memory cell, and the element formation region Ac (p-type well 8) and the drain of the memory cell For example, a voltage of 10.5 V is applied to the region (sub-bit line SBL), and the source region (source line SL) of the memory cell is maintained in a floating state (open state, open state). As a result, electrons are emitted from the control electrode CG to the channel region (between the source and drain regions) of the memory cell by the FN (Fowler-Nordheim) tunnel phenomenon.

また、メモリセルアレイの外周部には、制御電極CGと同じ層で形成されたダミー導電性膜DSGが形成されている。このダミー導電性膜DSGは、メモリセル形成時に生じる異物の影響を低減し、また、メモリセル形成領域と周辺回路形成領域との段差を少なくする等のために形成される。 A dummy conductive film DSG formed of the same layer as the control electrode CG is formed on the outer periphery of the memory cell array. This dummy conductive film DSG is formed in order to reduce the influence of foreign matter generated during the formation of the memory cell, and to reduce the level difference between the memory cell formation region and the peripheral circuit formation region.

このダミー導電性膜DSGも素子形成領域(p型ウエル8)上に形成され、これと素子形成領域Acとの間にも、例えば、ONO膜21等よりなる絶縁膜、浮遊電極(第1電極)FGおよび熱酸化膜等よりなるゲート絶縁膜9が形成されている(図2および図3参照)。

This dummy conductive film DSG is also formed on the element formation region (p-type well 8), and between this and the element formation region Ac, for example, an insulating film made of

一方、周辺回路形成領域にも、周辺回路用の素子形成領域LAcが形成され、この素子形成領域LAc上には、選択用MISFET Sのゲート電極Gを構成する導電性膜が形成されている。図2に示すように、このゲート電極Gは、制御電極CGと同じ層で形成され、その下には、ゲート絶縁膜9bが形成されている。このゲート電極Gの両端の素子形成領域LAc中には、n+型半導体領域27(ソース、ドレイン領域)が形成されている。

On the other hand, a peripheral circuit element forming region LAc is also formed in the peripheral circuit forming region, and a conductive film constituting the gate electrode G of the selection MISFET S is formed on the element forming region LAc. As shown in FIG. 2, the gate electrode G is formed of the same layer as the control electrode CG, and a

ここで、図1に示すように、メモリセル形成領域の素子形成領域Acは、最端のメモリセルのドレイン領域端部からX方向に長さDだけ延びている。この長さDのうち、距離d1は、素子形成領域Acを形成する最に用いられるマスクのずれ等を考慮した距離であり、距離d2は、結晶欠陥が生じる領域を考慮した距離である。本実施の形態においては、d1は、約0.2μmであり、d2は、約0.3μmである。このd2の大きさは、前述したルールでメモリセル形成した場合に素子形成領域Acに生じた結晶欠陥の長さが0.3μm程度であったことから、設定した。 Here, as shown in FIG. 1, the element formation region Ac of the memory cell formation region extends from the end of the drain region of the outermost memory cell by a length D in the X direction. Of the length D, the distance d1 is a distance considering the displacement of a mask used for forming the element formation region Ac, and the distance d2 is a distance considering a region where a crystal defect occurs. In the present embodiment, d1 is about 0.2 μm and d2 is about 0.3 μm. The size of d2 was set because the length of the crystal defect generated in the element formation region Ac when the memory cell was formed according to the above-described rule was about 0.3 μm.

このように、本実施の形態においては、素子形成領域Acの端部を伸長したので、素子形成領域Acに生じる結晶欠陥の影響を回避することができる。その結果、リーク電流の発生を低減でき、メモリセルの不良の発生率を低減することができる。 As described above, in the present embodiment, since the end portion of the element formation region Ac is extended, it is possible to avoid the influence of the crystal defects generated in the element formation region Ac. As a result, the occurrence of leakage current can be reduced, and the rate of occurrence of memory cell defects can be reduced.

即ち、図4に示すように、素子形成領域Ac間には、絶縁膜6が存在し、素子形成領域Acには、その外周部の絶縁膜6による応力(stress)が加わる。特に、メモリセル形成領域の外周部には、周辺回路との分離を図る等のために、広範囲に渡って絶縁膜6が形成されているため、素子形成領域Acの端部には、応力が集中する。このように大きな応力が加わると、素子形成領域Acを構成する結晶中に転位等の欠陥(De1、De2)が生じる。この欠陥を介してリーク電流が発生し、前述したように、このリーク電流が、センスアンプの動作電流以上になった場合には、不良となってしまう。

That is, as shown in FIG. 4, the insulating

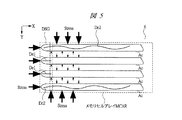

しかしながら、本実施の形態においては、素子形成領域Acの端部を伸長したので、図5に示すように、実質的なメモリセルが形成される領域(メモリセルアレイMCAR)までは、欠陥De1が延びず、メモリセルのリーク電流を低減することができる。 However, in the present embodiment, since the end of the element formation region Ac is extended, the defect De1 extends to a region where the substantial memory cell is formed (memory cell array MCAR) as shown in FIG. Therefore, the leakage current of the memory cell can be reduced.

なお、素子形成領域Acの伸長部分上には、ダミー導電性膜DSGが形成され、さらに、その下部には、ONO膜21等よりなる絶縁膜、浮遊電極(第1電極)FGおよび熱酸化膜等よりなるゲート絶縁膜9が形成されている。従って、その構成は、疑似メモリセル構造となっている(但し、ソース領域は存在しない)が、かかるダミー導電性膜DSGには、電位が印加されることなく、フローティング状態となっているため、チャネルが形成されず、リーク電流は発生しない。

A dummy conductive film DSG is formed on the extended portion of the element formation region Ac, and further, an insulating film made of the

また、本実施の形態においては、ダミー導電性膜DSGの下を利用し、素子形成領域Acを伸長したので、メモリセル形成領域を大きくすることなく、欠陥対策を行うことができる。 In the present embodiment, since the element formation region Ac is extended using the area under the dummy conductive film DSG, it is possible to take measures against defects without increasing the memory cell formation region.

次に、本実施の形態の半導体集積回路装置の製造方法の一例について説明する。図6〜図12は、本実施の半導体集積回路装置の製造方法を示す基板の要部断面図であり、図6〜図8は、図1のC−C断面部と対応し、図9〜図12は、図1のD−D断面部と対応する。 Next, an example of a method for manufacturing the semiconductor integrated circuit device of this embodiment will be described. 6 to 12 are cross-sectional views of the main part of the substrate showing the method of manufacturing the semiconductor integrated circuit device of the present embodiment. FIGS. 6 to 8 correspond to the CC cross-section of FIG. FIG. 12 corresponds to the DD cross section of FIG.

まず、図6に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンからなる半導体基板1を例えば、熱酸化することにより半導体基板1の表面に、パッド酸化膜(図示せず)を形成する。次いで、パッド酸化膜上に、例えば、窒化シリコン膜(図示せず)のような絶縁膜を堆積し、図示しないフォトレジスト膜(以下、単に「レジスト膜」という)をマスクに、素子分離領域上の窒化シリコン膜を除去する。

First, as shown in FIG. 6, for example, a

次いで、レジスト膜を除去し、窒化シリコン膜をマスクとして、半導体基板1をエッチングすることにより深さ250nm程度の素子分離溝4を形成する。

Next, the resist film is removed, and the

その後、半導体基板1を約1150℃でドライ酸化することによって、溝の内壁に、例えば、膜厚30nm程度の酸化シリコン膜5のような熱酸化膜を形成する。この酸化シリコン膜5は、溝の内壁に生じたドライエッチングのダメージを回復すると共に、次の工程で溝の内部に埋め込まれる酸化シリコン膜6と半導体基板1との界面に生じるストレスを緩和するために形成する。

Thereafter, the

次に、素子分離溝4の内部を含む半導体基板1上にCVD法で、例えば、膜厚600nm程度の酸化シリコン膜6よりなる絶縁膜を堆積し、次いで、1150℃で60分の熱処理(アニール)を施し、酸化シリコン膜6の緻密化を図る。次いで、CMP法で溝の上部の酸化シリコン膜6を研磨し、その表面を平坦化した後、窒化シリコン膜を除去する。なお、この際、窒化シリコン膜の膜厚分だけ酸化シリコン膜6の表面が半導体基板1の表面から突出しているが、以降の半導体基板1の洗浄工程や、表面酸化および酸化膜除去工程により酸化シリコン膜6の表面は、徐々に後退する。

Next, an insulating film made of, for example, a

以上の工程により、素子分離溝4内に、酸化シリコン膜6が埋め込まれた素子分離が形成される。

Through the above steps, element isolation in which the

次に、図7に示すように、半導体基板1の表面をウェット洗浄した後、半導体基板1を例えば、熱酸化することにより半導体基板1の表面に、スルー酸化膜(図示せず)のような絶縁膜を形成する。次いで、半導体基板1にp型不純物(例えば、ホウ素)をイオン打ち込みした後、熱処理を施し、前記不純物を拡散させることによって、メモリセル形成領域にp型ウエル8を形成する。このp型ウエル8が、半導体基板1の表面に露出した領域が、素子形成領域Acとなる。ここで、周辺回路形成領域においても、素子形成領域LAcを同様に形成する。

Next, as shown in FIG. 7, after the surface of the

次に、熱酸化によりp型ウエル8の表面に、例えば、膜厚8nm程度の熱酸化膜を形成した後(プレ酸化)、この熱酸化膜を除去し、半導体基板1(p型ウエル8)の表面を清浄化する。次いで、熱処理を施し、例えば、膜厚10.5nm程度の熱酸化膜を形成する。この熱酸化膜は、不揮発性メモリセルのゲート絶縁膜9を構成する。

Next, after a thermal oxide film having a film thickness of, for example, about 8 nm is formed on the surface of the p-type well 8 by thermal oxidation (pre-oxidation), the thermal oxide film is removed and the semiconductor substrate 1 (p-type well 8) is removed. Clean the surface. Next, heat treatment is performed to form, for example, a thermal oxide film having a thickness of about 10.5 nm. This thermal oxide film constitutes the

次に、ゲート絶縁膜9の上部に、例えば、膜厚100nm程度のリンをドープした多結晶シリコン膜10のような導電性膜をCVD法で堆積する。次に、レジスト膜(図示せず)をマスクにして多結晶シリコン膜10をドライエッチングすることにより、メモリセル形成領域に、X方向に長手方向が延在するストライプ状のパターンFG’(10)を形成する。

Next, a conductive film such as a

次いで、図8に示すように、半導体基板1上に、パターンFG’(10)と、後述する制御電極CGとを分離するため、例えば、ONO膜21のような絶縁膜を形成する。このONO膜21は、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜の積層膜であり、例えば、CVD法により膜厚5nm程度の酸化シリコン膜、膜厚7nm程度の窒化シリコン膜および膜厚4nm程度の酸化シリコン膜を順次堆積することにより形成する。なお、最上層の酸化シリコン膜上に、さらに、10nm程度の窒化シリコン膜を堆積してもよい。

Next, as illustrated in FIG. 8, an insulating film such as an

ここで、周辺回路形成領域においては、周辺回路形成領域上のONO膜21、多結晶シリコン膜10およびゲート絶縁膜9を除去する。次いで、周辺回路形成領域の半導体基板1の表面をウェット洗浄した後、周辺回路形成領域のp型ウエル8の表面に、例えば、熱酸化により膜厚8nm程度のゲート絶縁膜9bを形成する。このゲート絶縁膜9bは、周辺回路形成領域に形成される選択用MISFET Sのゲート絶縁膜9bとなる(図2参照)。

Here, in the peripheral circuit formation region, the

次いで、半導体基板1上に、導電性膜として、例えば、リンが4.75×1020/cm3程度ドープされた多結晶シリコン膜22をCVD法により200nm程度で堆積することで形成する。続いて、その上部に例えば、300nm程度の窒化シリコン膜24のような絶縁膜をCVD法で堆積する。この多結晶シリコン膜22は、周辺回路形成領域に形成される選択用MISFET Sのゲート電極Gとなり、また、メモリセル形成領域に形成される不揮発性メモリセルの制御電極CGとなる。

Next, as a conductive film, for example, a

次に、図9に示すように、メモリセル形成領域のレジスト膜(図示せず)をマスクにして窒化シリコン膜24、多結晶シリコン膜22、ONO膜21およびパターンFG’(多結晶シリコン膜10)をドライエッチングする。

Next, as shown in FIG. 9, using the resist film (not shown) in the memory cell formation region as a mask, the

このドライエッチングにより、多結晶シリコン22からなる制御電極CG(22)および多結晶シリコン膜10からなる浮遊電極FG(10)が形成される。浮遊電極FG(10)は、X方向に配置されるメモリセル毎に分割され、制御電極CGは、Y方向に延在するように形成され、ワード線WLを構成する。なお、制御電極CGは、多結晶シリコン膜22に限らず、高融点金属、シリサイド膜の単層膜または、積層膜、あるいは多結晶シリコン膜と高融点金属膜またはシリサイド膜との積層膜で構成してもよい。図9は、図8のE−E断面に対応し、また、図1のD−D断面と対応する。

By this dry etching, a control electrode CG (22) made of

ここで、周辺回路形成領域においては、レジスト膜(図示せず)をマスクにして窒化シリコン膜24および多結晶シリコン膜22をドライエッチングすることにより、選択用MISFET S用のゲート電極Gを形成する(図2参照)。

Here, in the peripheral circuit formation region, the gate electrode G for the selection MISFET S is formed by dry etching the

次に、メモリセル形成領域のp型ウエル8にn型不純物(例えば、ヒ素)をイオン打ち込みした後、熱処理を施し、前記不純物を拡散させることによって、n+型半導体領域17(ソース、ドレイン領域)を形成する。また、この際、p型不純物(例えば、ホウ素)を斜めイオン打ち込みすることによりゲート絶縁膜9の下にチャネルインプラ領域(図示せず)を形成してもよい。

Next, after ion-implanting an n-type impurity (for example, arsenic) into the p-type well 8 in the memory cell formation region, a heat treatment is performed to diffuse the impurity, whereby the n + -type semiconductor region 17 (source and drain regions). ). At this time, a channel implantation region (not shown) may be formed under the

ここで、周辺回路形成領域においては、p型ウエル8にn型不純物(例えば、ヒ素)をイオン打ち込みした後、熱処理を施し前記不純物を拡散させることによって、ゲート電極Gの両側に、n-型半導体領域(図示せず)を形成する。

Here, in the peripheral circuit formation region, an n-type impurity (for example, arsenic) is ion-implanted into the p-

次いで、例えば、850℃の熱処理(ライト酸化)を施すことにより多結晶シリコン膜10および22の側壁にライト酸化膜(熱酸化膜)26を形成する。このライト酸化膜26は、シリコン基板の表面にその膜厚が10nm程度の酸化シリコン膜が形成される条件と同様の条件で形成される。また、この膜は、前述の浮遊電極FG(多結晶シリコン膜10)や制御電極(多結晶シリコン膜22)のエッチングの際に、ゲート絶縁膜9の端部に生じたダメージを回復するために形成する。

Next, for example, a light oxide film (thermal oxide film) 26 is formed on the sidewalls of the

次いで、半導体基板1上に、例えば、CVD法で窒化シリコン膜28のような絶縁膜を堆積する。

Next, an insulating film such as a

ここで、周辺回路形成領域においては、窒化シリコン膜28を異方的にエッチングすることによって、周辺回路形成領域のゲート電極Gの側壁にサイドウォールスペーサ(図示せず)を形成する。次に、周辺回路形成領域のp型ウエル8にn型不純物(リンPまたはヒ素As)をイオン打ち込みした後、950℃で10秒の熱処理を施し、前記不純物を拡散させることによって、選択用MISFET S用のn+型半導体領域27(ソース、ドレイン領域)を形成する。

Here, in the peripheral circuit formation region, sidewall spacers (not shown) are formed on the sidewalls of the gate electrode G in the peripheral circuit formation region by anisotropically etching the

以上の工程により、メモリセル形成領域に、制御電極CG(多結晶シリコン膜22)、ONO膜21、浮遊電極FG(多結晶シリコン膜10)およびゲート絶縁膜9を有するNOR型不揮発性メモリセルが形成され、周辺回路形成領域に選択用MISFET Sが形成される。

Through the above process, the NOR type nonvolatile memory cell having the control electrode CG (polycrystalline silicon film 22), the

次いで、図10に示すように、窒化シリコン膜28の上部に、例えば、CVD法で200nm程度の酸化シリコン膜30のような絶縁膜を形成した後、酸化シリコン膜30に図1に示すプラグDC(P1)およびプラグSC(P1)のパターンを形成するため、レジスト膜(図示せず)をマスクにしたドライエッチングで酸化シリコン膜30をドライエッチングし、続いて窒化シリコン膜28をドライエッチングすることによって、n+型半導体領域17(ソース、ドレイン領域)上部にコンタクトホールC1および配線溝HM1を形成する。即ち、ドレイン領域(17)上には、コンタクトホールC1を形成し、ソース領域上(17)には、配線溝HM1を形成する。

Next, as shown in FIG. 10, after an insulating film such as a

上記酸化シリコン膜30のエッチングは、窒化シリコンに対する酸化シリコンのエッチングレートが大きくなるような条件で行い、窒化シリコン膜28が完全に除去されないようにする。

The etching of the

また、窒化シリコン膜28のエッチングは、シリコンや酸化シリコンに対する窒化シリコンのエッチングレートが大きくなるような条件で行い、基板1や酸化シリコン膜が深く削れないようにする。さらに、このエッチングは、窒化シリコン膜28が異方的にエッチングされるような条件で行い、制御電極CGや浮遊電極FGの側壁に窒化シリコン膜28を残すようにする。これにより、フォトリソグラフィの解像限界で決まる最小寸法よりも微細な径を有するコンタクトホールC1や微細な幅の配線溝HM1が制御電極CGや浮遊電極FGに対して自己整合(セルフアライン)で形成される。

Further, the etching of the

次に、コンタクトホールC1および配線溝HM1の内部を通じて、n型不純物(例えば、ヒ素)をイオン打ち込みした後、熱処理を施し、前記不純物を拡散させることによって、n+型半導体領域19を形成する。このn+型半導体領域19は、このコンタクトホールC1内に形成されるプラグとの接触抵抗を低減するために形成される。

Next, after ion-implanting an n-type impurity (for example, arsenic) through the contact hole C1 and the wiring trench HM1, an n + -

次いで、図11に示すように、コンタクトホールC1および配線溝HM1の内部を含む酸化シリコン膜30の上部に、例えば、薄い窒化シリコン膜32のような絶縁膜を形成する。次いで、エッチバックすることによって酸化シリコン膜30上およびコンタクトホールC1および配線溝HM1底部の窒化シリコン膜32を除去する。この窒化シリコン膜32は、後述する半導体基板1の洗浄の際、制御電極CGの上部の酸化シリコン膜30がエッチングされ、プラグ等の間がショートするのを防ぐために形成される。

Next, as shown in FIG. 11, an insulating film such as a thin silicon nitride film 32 is formed on the

次いで、半導体基板1を例えばフッ酸系の洗浄液を用いて洗浄した後、コンタクトホールC1および配線溝HM1内を含む酸化シリコン膜30上に、導電性膜を堆積する。例えば、10nm程度のTi(チタン)および80nm程度のTiN(窒化チタン)を順次スパッタ法により堆積(図示せず)し、さらに、350nm程度のW(タングステン)膜をCVD法により堆積する。

Next, after the

次いで、コンタクトホールC1および配線溝HM1外部のW膜、TiN膜およびTi膜からなる導電性膜をCMP法により除去することにより、プラグP1を形成する。即ち、ドレイン領域(17)上のコンタクトホールC1内に、プラグDC(P1)を形成し、ソース領域(17)上の配線溝HM1内にプラグSC(P1)を形成する。なお、前述したように、このプラグSC(P1)は、Y方向に延在する配線であり、ソース線SLを構成する。 Next, the plug P1 is formed by removing the conductive film made of the W film, the TiN film, and the Ti film outside the contact hole C1 and the wiring groove HM1 by the CMP method. That is, the plug DC (P1) is formed in the contact hole C1 on the drain region (17), and the plug SC (P1) is formed in the wiring groove HM1 on the source region (17). As described above, the plug SC (P1) is a wiring extending in the Y direction and constitutes the source line SL.

次いで、プラグP1上を含む酸化シリコン膜30上に、例えば、CVD法により300nm程度の酸化シリコン膜35のような絶縁膜を堆積する。

Next, an insulating film such as a

次いで、プラグP1上の酸化シリコン膜35を除去することによりコンタクトホールC2を形成する。なお、図12中には、ドレイン領域上のプラグDC(P1)上のコンタクトホールC2のみが表れており、ソース領域上のプラグSC(P1)上のコンタクトホールC2は、図12とは異なる断面に表れる。

Next, the contact hole C2 is formed by removing the

次いで、コンタクトホールC2内を含む酸化シリコン膜35上に、導電性膜を堆積する。例えば、100nm程度のW膜(図示せず)をスパッタ法により堆積し、さらに、250nm程度のW膜40をCVD法により堆積する。

Next, a conductive film is deposited on the

次いで、W膜40等からなる導電性膜を図示しないレジスト膜をマスクにドライエッチングすることによって第1層配線M1および第1層配線M1とプラグP1との接続部(プラグP2)とを形成する。即ち、プラグDC(P2)およびプラグSC(P2)を形成する。図中の第1層配線M1は、図1における副ビット線SBLとなり、図12に示す断面には表れないプラグSC(P2)上の第1層配線M1は、共通ソース線CSLとなる。

Next, the first layer wiring M1 and the connection portion (plug P2) between the first layer wiring M1 and the plug P1 are formed by dry etching the conductive film made of the

この後、第1層配線M1上を含む酸化シリコン膜35上に、例えば、CVD法により酸化シリコン膜のような絶縁膜を堆積し、さらに、その上に、W膜等からなる導電性膜を堆積することによって、第2層配線が形成されるが、これらの図示については、省略する。

Thereafter, an insulating film such as a silicon oxide film is deposited on the

以上、詳細に説明した半導体集積回路装置の製造方法においては、例えば、1)酸化シリコン膜6の緻密化のための熱処理、2)スルー酸化膜の形成の際の熱処理、3)半導体基板1(p型ウエル8)の表面の清浄化のための酸化(プレ酸化)、4)ゲート絶縁膜9の形成の際の熱処理、および5)ライト酸化膜26の形成の際の熱処理等、種々の熱処理工程を有する。

In the method of manufacturing a semiconductor integrated circuit device described in detail above, for example, 1) heat treatment for densification of the

このような熱処理工程において、半導体基板に形成した溝の内部に埋め込まれた酸化シリコン膜6、特に、溝の内壁に生じたドライエッチングのダメージを回復するために形成される薄い熱酸化膜(酸化シリコン膜5)の酸化が進行し、素子形成領域に加わる応力が大きくなる。

In such a heat treatment process, the

また、n+型半導体領域17(ソース、ドレイン領域)やn+型半導体領域19を形成する際のイオン打ち込みによっても、素子形成領域に応力が加わる。

Also, stress is applied to the element formation region by ion implantation when forming the n + type semiconductor region 17 (source and drain regions) and the n +

さらに、窒化シリコン膜は、膜応力の大きい膜であるため、例えば、コンタクトホールC1や配線溝HM1を自己整合的に形成するために用いられる窒化シリコン膜28の堆積時にも、素子形成領域に応力が加わる。

Further, since the silicon nitride film is a film having a large film stress, for example, even when the

しかしながら、本実施の形態によれば、前述した通り、素子形成領域Acの端部を伸長したので、前記応力が加わっても、メモリセルが形成される領域までは、欠陥が延びず、メモリセルのリーク電流を低減する等の効果を得ることができる。 However, according to the present embodiment, as described above, since the end portion of the element formation region Ac is extended, even if the stress is applied, the defect does not extend to the region where the memory cell is formed, and the memory cell The effect of reducing the leakage current can be obtained.

(実施の形態2)

図13に本実施の形態の半導体集積回路装置の要部平面図を示す。図13の右部は、メモリセル形成領域MCFRを示し、左部は、周辺回路形成領域PCFRを示す。メモリセル形成領域には、NOR型の不揮発性メモリセルがアレイ状に配置され、周辺回路形成領域には、周辺回路の一例として選択用MISFET Sが形成されている。本実施の形態の半導体集積回路装置は、図1と対比して明らかなように、素子形成部Ac1の端部が接続部Ac2で接続されている以外は、その構成が実施の形態1と同様であるため、詳細な説明は省略し、特徴的な部分のみ説明する。

(Embodiment 2)

FIG. 13 is a plan view of the main part of the semiconductor integrated circuit device according to the present embodiment. The right part of FIG. 13 shows the memory cell formation region MCFR, and the left part shows the peripheral circuit formation region PCFR. NOR type nonvolatile memory cells are arranged in an array in the memory cell formation region, and a selection MISFET S is formed in the peripheral circuit formation region as an example of a peripheral circuit. As apparent from the comparison with FIG. 1, the semiconductor integrated circuit device of the present embodiment has the same configuration as that of the first embodiment except that the end portion of the element forming portion Ac1 is connected by the connection portion Ac2. Therefore, detailed description is omitted, and only characteristic portions will be described.

即ち、図13に示すように、メモリセル形成領域には、X方向に延在した素子形成部Ac1が、Y方向に一定の間隔毎に配置されており、この素子形成部Ac1の端部は、Y方向に延在する接続部Ac2によって接続されている。 That is, as shown in FIG. 13, in the memory cell formation region, element formation portions Ac1 extending in the X direction are arranged at regular intervals in the Y direction, and the end portions of the element formation portions Ac1 are Are connected by a connecting portion Ac2 extending in the Y direction.

このように、本実施の形態においては、素子形成部Ac1の端部を、接続部Ac2によって接続したので、図14に示すように、応力の加わる方向を変化させることができる。従って、実施の形態1の効果に加え、さらに、応力が素子形成部Ac1に集中することを緩和することができる。その結果、実質的なメモリセルが形成される領域(メモリセルアレイMCFR)までは、欠陥De1が延びず、メモリセルのリーク電流を低減することができる。 Thus, in this Embodiment, since the edge part of element formation part Ac1 was connected by connection part Ac2, as shown in FIG. 14, the direction where stress is added can be changed. Therefore, in addition to the effect of the first embodiment, it is possible to further reduce the concentration of stress on the element formation portion Ac1. As a result, the defect De1 does not extend to a region where the substantial memory cell is formed (memory cell array MCFR), and the leakage current of the memory cell can be reduced.

なお、図13においては、素子形成部Ac1のすべてを接続部Ac2で接続したが、図15に示すように、いくつかの素子形成部Ac1毎に(図15の場合は、2つの素子形成部Ac1毎に)、接続部Ac2を設けてもよい。 In FIG. 13, all of the element forming portions Ac1 are connected by the connecting portion Ac2. However, as shown in FIG. 15, every two element forming portions Ac1 (in the case of FIG. 15, two element forming portions). A connecting portion Ac2 may be provided for each Ac1).

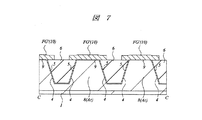

(実施の形態3)

図16に本実施の形態の半導体集積回路装置の要部平面図を示す。図16の右部は、メモリセル形成領域MCFRを示し、左部は、周辺回路形成領域PCFRを示す。メモリセル形成領域には、NOR型の不揮発性メモリセルがアレイ状に配置され、周辺回路形成領域には、周辺回路の一例として選択用MISFET Sが形成されている。本実施の形態の半導体集積回路装置は、図1と対比して明らかなように、メモリセル形成領域に、配置された複数の素子形成領域Ac、AcWのうち、最外の素子形成領域AcWの幅が、他の素子形成領域Acの幅より広くなっている以外は、その構成が実施の形態1と同様であるため、詳細な説明は省略し、特徴的な部分のみ説明する。

(Embodiment 3)

FIG. 16 is a plan view of the main part of the semiconductor integrated circuit device according to the present embodiment. The right part of FIG. 16 shows the memory cell formation region MCFR, and the left part shows the peripheral circuit formation region PCFR. NOR type nonvolatile memory cells are arranged in an array in the memory cell formation region, and a selection MISFET S is formed in the peripheral circuit formation region as an example of a peripheral circuit. As apparent from the comparison with FIG. 1, the semiconductor integrated circuit device of the present embodiment includes the outermost element formation region AcW among the plurality of element formation regions Ac and AcW arranged in the memory cell formation region. Since the configuration is the same as that of the first embodiment except that the width is wider than the width of the other element formation regions Ac, detailed description is omitted, and only characteristic portions will be described.

即ち、図16に示すように、メモリセル形成領域には、X方向に延在した素子形成領域Ac、AcWが、Y方向に一定の間隔毎に配置されており、この素子形成領域Ac、AcWのうち、Y方向について最端に位置する素子形成領域AcWのY方向の幅が、他の素子形成領域Acのそれより広くなっている。 That is, as shown in FIG. 16, in the memory cell formation region, element formation regions Ac, AcW extending in the X direction are arranged at regular intervals in the Y direction. The element formation regions Ac, AcW Among them, the width in the Y direction of the element formation region AcW located at the extreme end in the Y direction is wider than that of the other element formation regions Ac.

このように、本実施の形態においては、最外の素子形成領域AcWの幅を他の素子形成領域Acより広く形成したので、図17に示すように、応力の影響を緩和することができ、最外の素子形成領域AcWの欠陥(De2)の発生率を低減することができる。その結果、メモリセルのリーク電流を低減することができる。 Thus, in the present embodiment, since the outermost element formation region AcW is formed wider than the other element formation regions Ac, the influence of stress can be reduced as shown in FIG. The occurrence rate of defects (De2) in the outermost element formation region AcW can be reduced. As a result, the leakage current of the memory cell can be reduced.

また、実施の形態1で説明したように、素子形成領域Ac、AcWの端部を伸長すれば、メモリセルが形成される領域まで欠陥(De1)が延びることを防止することができ、実施の形態1で説明した効果を得ることができる。

Further, as described in the first embodiment, if the end portions of the element formation regions Ac and AcW are extended, it is possible to prevent the defect (De1) from extending to the region where the memory cell is formed. The effect demonstrated in the

(実施の形態4)

図18に本実施の形態の半導体集積回路装置の要部平面図を示す。図18の右部は、メモリセル形成領域MCFRを示し、左部は、周辺回路形成領域PCFRを示す。メモリセル形成領域には、NOR型の不揮発性メモリセルがアレイ状に配置され、周辺回路形成領域には、周辺回路の一例として選択用MISFET Sが形成されている。図19は、図18のA−A断面の概略図であり、図20は、図18のB−B断面の概略図である。

(Embodiment 4)

FIG. 18 is a plan view of the main part of the semiconductor integrated circuit device according to the present embodiment. The right part of FIG. 18 shows the memory cell formation region MCFR, and the left part shows the peripheral circuit formation region PCFR. NOR type nonvolatile memory cells are arranged in an array in the memory cell formation region, and a selection MISFET S is formed in the peripheral circuit formation region as an example of a peripheral circuit. 19 is a schematic view of the AA cross section of FIG. 18, and FIG. 20 is a schematic view of the BB cross section of FIG.

本実施の形態の半導体集積回路装置は、図13と対比して明らかなように、メモリセル形成領域に、配置された複数の素子形成部Ac1の最外に、素子形成領域DAcを設けたこと以外は、その構成が実施の形態2と同様であるため、詳細な説明は省略し、特徴的な部分のみ説明する。 In the semiconductor integrated circuit device according to the present embodiment, as apparent from the comparison with FIG. 13, the element formation region DAc is provided in the memory cell formation region at the outermost of the plurality of element formation portions Ac1 arranged. Since the configuration is the same as that of the second embodiment, detailed description is omitted and only characteristic portions will be described.

即ち、図18に示すように、メモリセル形成領域には、X方向に延在した素子形成部Ac1が、Y方向に一定の間隔毎に配置されており、この素子形成部Acのうち最外に位置する素子形成部Ac1のさらに外側に素子形成領域DAcが配置されている。 That is, as shown in FIG. 18, in the memory cell formation region, element formation portions Ac1 extending in the X direction are arranged at regular intervals in the Y direction. An element formation region DAc is arranged on the outer side of the element formation part Ac1 located in the position.

この素子形成領域DAc上には、メモリセルとして機能するメモリセルが形成されていない。即ち、素子形成領域DAc上には、Y方向に制御電極CGが延在しているが、この制御電極CGの両端には、プラグDCやプラグSCが形成されていない。 No memory cell that functions as a memory cell is formed on the element formation region DAc. That is, the control electrode CG extends in the Y direction on the element formation region DAc, but the plug DC and the plug SC are not formed at both ends of the control electrode CG.

また、制御電極CGのY方向の端部には、この制御電極CGの引き出し部(制御電極CGとさらに上層の配線との接続部)CAが交互に形成されている。図18においてかかる領域(CA)が形成されていない制御電極CGについては、図18には現れていない他の端部に前記引き出し部を有する。 In addition, lead portions (connection portions between the control electrodes CG and upper layer wirings) CA of the control electrodes CG are alternately formed at the ends of the control electrodes CG in the Y direction. The control electrode CG in which such a region (CA) is not formed in FIG. 18 has the lead-out portion at the other end that does not appear in FIG.

このように、本実施の形態においては、複数の素子形成部Ac1の最外に素子形成領域DAcを設けたので、この領域に応力を集中させることができ、モリセルが形成される領域、つまり、図21に示す素子形成部Ac1に、欠陥(De2)が延びず、メモリセルのリーク電流を低減することができる。 Thus, in the present embodiment, since the element formation region DAc is provided at the outermost part of the plurality of element formation portions Ac1, stress can be concentrated in this region, that is, the region where the Mori cell is formed, that is, The defect (De2) does not extend to the element formation portion Ac1 shown in FIG. 21, and the leakage current of the memory cell can be reduced.

また、引き出し部CAの下を利用し、素子形成領域DAcを形成したので、メモリセル形成領域を大きくすることなく、欠陥対策を行うことができる。 Further, since the element formation region DAc is formed using the area under the lead portion CA, it is possible to take a countermeasure against defects without increasing the memory cell formation region.

また、実施の形態2で説明したように、これらの素子形成部(Ac1、DAc)の端部を、接続部Ac2によって接続すれば、実施の形態2で説明した効果(欠陥De1の影響の低減)を得ることができる。 Further, as described in the second embodiment, if the end portions of these element forming portions (Ac1, DAc) are connected by the connection portion Ac2, the effect described in the second embodiment (reduction of the influence of the defect De1) is achieved. ) Can be obtained.

図22に、本実施の形態の半導体集積回路装置に対応する回路図を示す。図示するように、メモリセルMCがアレイ状に配置されている。但し、DAc(素子形成領域)上のメモリセルは、メモリセルとしての動作を行わない。また、DSG(ダミー導電性膜)上には、実施の形態1で説明した疑似メモリセルが形成される。なお、MBLは、主ビット線を表す。また、Sは、前述した選択用MISFETを表す。また、これらのメモリセルは、あるブロック(Block)を一つの単位としており、例えば、このブロック毎に、データを一括消去することができる。1つのウエル(WELL)を1ブロックとすることができる。なお、実施の形態1〜3で説明した半導体集積回路装置に対応する回路図は、図22のDAc(素子形成領域)上のメモリセルがないことを除き、同様である。 FIG. 22 shows a circuit diagram corresponding to the semiconductor integrated circuit device of the present embodiment. As shown in the figure, memory cells MC are arranged in an array. However, the memory cell on DAc (element formation region) does not operate as a memory cell. Further, the pseudo memory cell described in the first embodiment is formed on the DSG (dummy conductive film). MBL represents a main bit line. S represents the above-described selection MISFET. These memory cells use a block as one unit. For example, data can be erased at once for each block. One well (WELL) can be made one block. The circuit diagram corresponding to the semiconductor integrated circuit device described in the first to third embodiments is the same except that there is no memory cell on DAc (element formation region) in FIG.

以上、実施の形態1〜4を具体的に説明したが、本発明はかかる実施の形態に限定されるものではなく、例えば、実施の形態3の素子形成領域AcやAcWの端部を実施の形態2のように、接続部Ac2によって接続してもよい。また、実施の形態4の素子形成領域Ac1、DAcの端部を、接続部Ac2によって接続せず、実施の形態1のように、これらの素子形成領域の端部を伸長するだけでもよい。このように、これらの実施の形態中で説明した構成を適宜組み合わせてもよい。

Although the first to fourth embodiments have been specifically described above, the present invention is not limited to such embodiments. For example, the end portions of the element formation regions Ac and AcW of the third embodiment are implemented. You may connect by connection part Ac2 like the

(実施の形態5)

実施の形態1〜4で説明した半導体集積回路装置は、以下に説明するコンピュータシステムに利用することができる。

(Embodiment 5)

The semiconductor integrated circuit device described in

図23は、実施の形態1〜4で説明した半導体集積回路装置(不揮発性メモリ)が取り込まれたコンピュータシステムを示し、このシステムはシステムバスSBを介して相互に接続されたホストCPU(Central Processing Unit)231と、入出力装置232、RAM(Random Access Memory)233、メモリカード234とから構成されている。

FIG. 23 shows a computer system in which the semiconductor integrated circuit device (nonvolatile memory) described in the first to fourth embodiments is incorporated, and this system is connected to host CPUs (Central Processing) connected to each other via a system bus SB. Unit) 231, input /

メモリカード234は例えばハードデイスク記憶装置の置換用途として数十ギガバイトの大容量記憶の不揮発性メモリ(EEPROMチップ1〜チップ4)を含み、実施の形態1〜4で説明した不揮発性メモリの利点、例えば、装置内の欠陥の低減、リーク電流の低減、もしくは装置の歩留まり向上や信頼性の向上といった利点を享受するので、最終製品である記憶装置としても十分な産業的利点を有するものである。

The

尚、本発明は厚さの比較的薄いメモリカード234に限定されるものでは無く、厚さが比較的厚い場合であっても、ホストバスシステムとのインターフェイスとホストシステムのコマンドを解析して不揮発性メモリを制御することが可能なインテリジェントなコントローラとを含むどのような不揮発性記憶装置にも適用可能なことは言うまでもない。

The present invention is not limited to the relatively

長期間に記憶されるデータはこの不揮発性の記憶装置に記憶される一方、ホストCPU231によって処理されて頻繁に変更されるデータは揮発性メモリのRAM233に格納される。

Data stored for a long period of time is stored in this nonvolatile storage device, while data that is processed and frequently changed by the

カード234はシステムバスSBと接続されるシステムバスインターフェイスSBIを持ち、例えばATAシステムバスなどの標準バスインターフェイスを可能とする。システムバスインターフェイスSBIに接続されたコントローラCRは、システムバスSBに接続されたホストCPU231や入出力装置232のホストシステムからのコマンドとデータとを受け付ける。

The

コマンドがリード命令の場合は、コントローラCRは実施の形態1〜4で説明した不揮発性メモリを有する複数のチップ1〜4(CH1〜4)の必要なひとつまたは複数をアクセスして読み出しデータをホストシステムへ転送する。

When the command is a read command, the controller CR accesses one or more necessary ones of the plurality of

コマンドがライト命令の場合は、コントローラCRは複数のチップ1〜4(CH1〜4)の必要なひとつまたは複数をアクセスしてホストシステムからの書き込みデータをその内部に格納する。この格納動作は、不揮発性メモリの必要なブロックやセクターやメモリセルへのプログラム動作とベリファイ動作とを含んでいる。

When the command is a write command, the controller CR accesses one or more necessary ones of the plurality of

コマンドが消去命令の場合は、コントローラは複数のチップ1〜4(CH1〜4)の必要なひとつまたは複数をアクセスして、その内部に記憶されるデータを消去する。この消去動作は、不揮発性メモリの必要なブロック、セクターまたはメモリセルへの消去動作とベリファイ動作とを含んでいる。

When the command is an erase command, the controller accesses one or more necessary ones of the plurality of

本発明の実施例による不揮発性メモリは、1つのメモリセルにデジタルデータの1ビットを記憶させるためメモリセルに2値の閾値電圧を持たせる技術ばかりでなく、1つのメモリセルにデジタルデータの多ビットを記憶させるためメモリセルに4値あるいはそれ以上の多値の閾値電圧を持たせる技術にも適用可能であることは言うまでもない。 The non-volatile memory according to the embodiment of the present invention is not only a technique for storing one bit of digital data in one memory cell, but also a technique in which a binary threshold voltage is given to one memory cell. Needless to say, the present invention is also applicable to a technique in which a memory cell has a multilevel threshold voltage of four or more in order to store bits.

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。 As mentioned above, the invention made by the present inventor has been specifically described based on the embodiment. However, the present invention is not limited to the embodiment, and various modifications can be made without departing from the scope of the invention. Needless to say.

特に、本実施の形態においては、NOR型の不揮発性メモリを例に説明したが、AND型、NAND型等の不揮発性メモリを始め、細長い素子形成領域を有する半導体集積回路装置に広く適用可能である。 In particular, in this embodiment, a NOR type nonvolatile memory has been described as an example. However, the present invention can be widely applied to AND type, NAND type, and other semiconductor integrated circuit devices having an elongated element formation region. is there.

本発明は、半導体集積回路装置を製造する製造業に幅広く利用することができる。 The present invention can be widely used in the manufacturing industry for manufacturing semiconductor integrated circuit devices.

1 半導体基板

4 素子分離溝

5 酸化シリコン膜(熱酸化膜)

6 酸化シリコン膜(絶縁膜)

8 p型ウエル

9 ゲート絶縁膜

9b ゲート絶縁膜

10 多結晶シリコン膜

17 n+型半導体領域

19 n+型半導体領域

21 ONO膜(絶縁膜)

22 多結晶シリコン膜

24 窒化シリコン膜

26 ライト酸化膜

27 n+型半導体領域

28 窒化シリコン膜

30 酸化シリコン膜

32 窒化シリコン膜

35 酸化シリコン膜

40 W膜

Ac 素子形成領域

Ac1 素子形成部

Ac2 接続部

AcW 素子形成領域

DAc 素子形成領域

LAc 素子形成領域

C1 コンタクトホール

C2 コンタクトホール

CA 引き出し部

SC プラグ

DC プラグ

P1 プラグ

P2 プラグ

CG 制御電極

FG 浮遊電極

FG’ パターン

G ゲート電極

DSG ダミー導電性膜

De1、De2 欠陥

MBI 主ビット線

SBL 副ビット線

SL ソース線

WL ワード線

M1 第1層配線

D、d1、d2 距離

MC メモリセル

S 選択用MISFET

232 入出力装置

233 RAM

234 メモリカード

SB システムバス

SBI システムバスインターフェイス

CR コントローラ

CH1〜CH4 チップ

MCFR メモリセル形成領域

PCFR 周辺回路形成領域

MCAR メモリセルアレイ

6 Silicon oxide film (insulating film)

8 p-type well 9

22

232 I /

234 Memory card SB system bus SBI system bus interface CR controller CH1 to CH4 chip MCFR memory cell formation area PCFR peripheral circuit formation area MCAR memory cell array

Claims (7)

(b)前記素子形成領域の主表面に形成された複数のメモリセルと、

(c)前記複数のメモリセルからなるメモリセルアレイと、

(d)前記メモリセルアレイの外周部に、少なくとも前記第1および第2方向に延在するように形成された第1導電性膜と、

を有する半導体集積回路装置であって、

前記第1絶縁膜は、前記半導体基板に形成された溝内に埋め込まれて形成されており、

前記接続部は、前記第2方向に延在する前記第1導電性膜の下に形成されていることを特徴とする半導体集積回路装置。 (A) An element formation region formed on the surface of the semiconductor substrate and partitioned by the first insulating film and extending in the first direction in a second direction perpendicular to the first direction 3 a above, an element forming region and a connecting portion for connecting the ends of the three or more element forming portion, extending in the second direction,

(B) a plurality of memory cells formed on the main surface of the element formation region;

(C) a memory cell array composed of the plurality of memory cells;

(D) a first conductive film formed on the outer periphery of the memory cell array so as to extend at least in the first and second directions;

A semiconductor integrated circuit device comprising:

The first insulating film is embedded in a groove formed in the semiconductor substrate;

The semiconductor integrated circuit device , wherein the connection portion is formed under the first conductive film extending in the second direction .

(b)前記素子形成領域の主表面に形成された複数のメモリセルと、(B) a plurality of memory cells formed on the main surface of the element formation region;

(c)前記複数のメモリセルからなるメモリセルアレイと、(C) a memory cell array composed of the plurality of memory cells;

(d)前記メモリセルアレイの外周部に、少なくとも前記第1および第2方向に延在するように形成された第1導電性膜と、(D) a first conductive film formed on the outer periphery of the memory cell array so as to extend at least in the first and second directions;

を有する半導体集積回路装置であって、A semiconductor integrated circuit device comprising:

前記3以上の素子形成領域のうち、最外の素子形成領域の前記第2方向の幅は、他の素子形成領域の幅より広く、Of the three or more element formation regions, the width of the outermost element formation region in the second direction is wider than the width of other element formation regions,

前記第1絶縁膜は、前記半導体基板に形成された溝内に埋め込まれて形成されており、The first insulating film is embedded in a groove formed in the semiconductor substrate;

前記接続部は、前記第2方向に延在する前記第1導電性膜の下に形成されていることを特徴とする半導体集積回路装置。The semiconductor integrated circuit device, wherein the connection portion is formed under the first conductive film extending in the second direction.

(b)前記素子形成領域の主表面に形成された複数の不揮発性メモリセルと、(B) a plurality of nonvolatile memory cells formed on the main surface of the element formation region;

(c)前記複数の不揮発性メモリセルからなるメモリセルアレイと、(C) a memory cell array composed of the plurality of nonvolatile memory cells;

(d)前記メモリセルアレイの外周部に、少なくとも前記第1および第2方向に延在するように形成された第1導電性膜と、(D) a first conductive film formed on the outer periphery of the memory cell array so as to extend at least in the first and second directions;

を有する半導体集積回路装置であって、A semiconductor integrated circuit device comprising:

前記複数の不揮発性メモリセルはそれぞれ、Each of the plurality of nonvolatile memory cells is

(b1)前記素子形成領域上に第2絶縁膜を介して形成された第2導電性膜と、(B1) a second conductive film formed on the element formation region via a second insulating film;

(b2)前記第2導電性膜上に第3絶縁膜を介して形成され、前記第2方向に延在する第3導電性膜と、(B2) a third conductive film formed on the second conductive film via a third insulating film and extending in the second direction;

を有し、Have

前記第1導電性膜は、前記第3導電性膜と同層の層を含んで形成されており、The first conductive film is formed to include the same layer as the third conductive film,

前記第1絶縁膜は、前記半導体基板に形成された溝内に埋め込まれて形成されており、The first insulating film is embedded in a groove formed in the semiconductor substrate;

前記接続部は、前記第2方向に延在する前記第1導電性膜の下に形成されていることを特徴とする半導体集積回路装置。The semiconductor integrated circuit device, wherein the connection portion is formed under the first conductive film extending in the second direction.

前記不揮発性メモリセルにおける前記第2導電性膜は、前記不揮発性メモリセルのフローティングゲートを構成し、The second conductive film in the nonvolatile memory cell constitutes a floating gate of the nonvolatile memory cell,

前記不揮発性メモリセルにおける前記第3導電性膜は、前記不揮発性メモリセルのコントロールゲートを構成していることを特徴とする半導体集積回路装置。The semiconductor integrated circuit device, wherein the third conductive film in the nonvolatile memory cell constitutes a control gate of the nonvolatile memory cell.

前記3以上の素子形成領域のうち最外の素子形成領域上には、メモリセルとして機能するメモリセルを形成しないことを特徴とする半導体集積回路装置。2. A semiconductor integrated circuit device according to claim 1, wherein a memory cell functioning as a memory cell is not formed on the outermost element forming region among the three or more element forming regions.

前記第1導電性膜は、前記複数のメモリセルとは接続しないダミー導電性膜であることを特徴とする半導体集積回路装置。The semiconductor integrated circuit device, wherein the first conductive film is a dummy conductive film that is not connected to the plurality of memory cells.

前記第1導電性膜は、前記複数の不揮発性メモリセルとは接続しないダミー導電性膜であることを特徴とする半導体集積回路装置。The semiconductor integrated circuit device, wherein the first conductive film is a dummy conductive film that is not connected to the plurality of nonvolatile memory cells.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004179692A JP4939735B2 (en) | 2004-06-17 | 2004-06-17 | Semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004179692A JP4939735B2 (en) | 2004-06-17 | 2004-06-17 | Semiconductor integrated circuit device |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001263736A Division JP3597495B2 (en) | 2001-08-31 | 2001-08-31 | Semiconductor integrated circuit device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004336065A JP2004336065A (en) | 2004-11-25 |

| JP2004336065A5 JP2004336065A5 (en) | 2008-10-02 |

| JP4939735B2 true JP4939735B2 (en) | 2012-05-30 |

Family

ID=33509327

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004179692A Expired - Fee Related JP4939735B2 (en) | 2004-06-17 | 2004-06-17 | Semiconductor integrated circuit device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4939735B2 (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008218881A (en) * | 2007-03-07 | 2008-09-18 | Nec Electronics Corp | Semiconductor device |

| KR101192359B1 (en) | 2007-12-17 | 2012-10-18 | 삼성전자주식회사 | NAND flash memory device and method for manufacturing the same |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02196462A (en) * | 1989-01-24 | 1990-08-03 | Mitsubishi Electric Corp | semiconductor equipment |

| JPH0997762A (en) * | 1995-07-26 | 1997-04-08 | Toshiba Corp | Method for manufacturing semiconductor device |

| JPH1022480A (en) * | 1996-07-05 | 1998-01-23 | Hitachi Ltd | Nonvolatile semiconductor memory device and method of manufacturing the same |

| JP3110328B2 (en) * | 1996-11-19 | 2000-11-20 | 日本電気アイシーマイコンシステム株式会社 | Semiconductor storage device |

| JPH10242420A (en) * | 1997-02-27 | 1998-09-11 | Toshiba Corp | Semiconductor device and manufacturing method thereof |

| JP3519583B2 (en) * | 1997-09-19 | 2004-04-19 | 株式会社東芝 | Nonvolatile semiconductor memory device and method of manufacturing the same |

| JP2001332708A (en) * | 2000-05-19 | 2001-11-30 | Nec Corp | Nonvolatile semiconductor memory device and method of manufacturing the same |

-

2004

- 2004-06-17 JP JP2004179692A patent/JP4939735B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004336065A (en) | 2004-11-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4065572B2 (en) | Semiconductor device | |

| US8546239B2 (en) | Methods of fabricating non-volatile memory with air gaps | |

| US6995414B2 (en) | Semiconductor memory device including multi-layer gate structure | |

| JP3597495B2 (en) | Semiconductor integrated circuit device | |

| JPWO1998044567A1 (en) | Nonvolatile semiconductor memory device and method of manufacturing the same, and semiconductor device and method of manufacturing the same | |

| JP4053232B2 (en) | Semiconductor integrated circuit device and manufacturing method thereof | |

| JP2016072537A (en) | Semiconductor storage device and manufacturing method of the same | |

| CN100492647C (en) | Flash memory device and method of manufacturing the same | |

| JP2006019570A (en) | Nonvolatile semiconductor storage device and manufacturing method thereof | |

| CN110024084B (en) | non-volatile flash memory unit | |

| JP2003133444A (en) | Semiconductor storage device and method of manufacturing the same | |

| JP4939735B2 (en) | Semiconductor integrated circuit device | |

| JP2008053651A (en) | Nonvolatile semiconductor memory device | |

| US11205655B2 (en) | Method for manufacturing semiconductor device including fin-structured transistor | |

| KR20060048210A (en) | Nonvolatile Semiconductor Memory and Manufacturing Method Thereof | |

| JP2007049000A (en) | Semiconductor integrated circuit device and its manufacturing method | |

| CN101383323B (en) | Method for forming contact plug of semiconductor device | |

| JP2006114925A (en) | Semiconductor device and manufacturing method thereof | |

| JP3955610B2 (en) | Method for manufacturing nonvolatile semiconductor device | |

| JP2010171105A (en) | Semiconductor integrated circuit apparatus and method of manufacturing the same | |

| KR20060007176A (en) | Manufacturing method of nonvolatile memory device | |

| JP2007134534A (en) | Method of manufacturing semiconductor device | |

| JP2007067223A (en) | Semiconductor device and method for manufacturing same | |

| JP2006173452A (en) | Nonvolatile semiconductor memory, and manufacturing method thereof | |

| JP2006040985A (en) | Semiconductor device and its manufacturing method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080814 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080814 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110304 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120131 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120227 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150302 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4939735 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |