JP4908446B2 - 電子デバイスを製造するプロセス及び薄膜トランジスタを製造するプロセス - Google Patents

電子デバイスを製造するプロセス及び薄膜トランジスタを製造するプロセス Download PDFInfo

- Publication number

- JP4908446B2 JP4908446B2 JP2008077941A JP2008077941A JP4908446B2 JP 4908446 B2 JP4908446 B2 JP 4908446B2 JP 2008077941 A JP2008077941 A JP 2008077941A JP 2008077941 A JP2008077941 A JP 2008077941A JP 4908446 B2 JP4908446 B2 JP 4908446B2

- Authority

- JP

- Japan

- Prior art keywords

- dielectric constant

- phase

- constant polymer

- layer

- low

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/468—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics

- H10K10/478—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics the gate dielectric comprising a layer of composite material comprising interpenetrating or embedded materials, e.g. TiO2 particles in a polymer matrix

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/468—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics

- H10K10/471—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics the gate dielectric comprising only organic materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/464—Lateral top-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/466—Lateral bottom-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/10—Deposition of organic active material

- H10K71/12—Deposition of organic active material using liquid deposition, e.g. spin coating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K85/00—Organic materials used in the body or electrodes of devices covered by this subclass

- H10K85/10—Organic polymers or oligomers

- H10K85/111—Organic polymers or oligomers comprising aromatic, heteroaromatic, or aryl chains, e.g. polyaniline, polyphenylene or polyphenylene vinylene

- H10K85/113—Heteroaromatic compounds comprising sulfur or selene, e.g. polythiophene

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Composite Materials (AREA)

- Materials Engineering (AREA)

- Thin Film Transistor (AREA)

- Formation Of Insulating Films (AREA)

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

Description

Yiliang Wuらの米国特許出願第11/276,634号の発明の名称「TFT製造プロセス(TFT FABRICATION PROCESS)」は2006年3月8日に出願された。

半導体を含む層を堆積することと、

低誘電率材料および高誘電率材料および液体を含む誘電体組成物を液相堆積することとを含み、ここで、低誘電率材料および高誘電率材料は液相堆積の前に相分離されず、

さらにこのプロセスは、

相分離誘電体構造を形成するために、低誘電率材料および高誘電率材料の相分離を生成することを含み、ここで、低誘電率材料は、半導体を含む層に最も近い誘電体構造領域内の高誘電率材料の濃度に比べて高濃度であり、

半導体を含む層の堆積は、誘電体組成物を液相堆積する前、または相分離を生成した後になされる。

半導体を含む層を堆積することと、

低誘電率材料および高誘電率材料および液体を含む誘電体組成物を単一ステップで液相堆積することとを含み、ここで、低誘電率材料および高誘電率材料は液相堆積の前に相分離されず、

さらにこのプロセスは、

相分離誘電体構造を形成するために、低誘電率材料および高誘電率材料の相分離を生成することを含み、ここで、低誘電率材料は、半導体を含む層に最も近い誘電体構造領域内の低誘電率材料および高誘電率材料の総重量の約60%から100%の濃度であり、高誘電率材料は約40%から0%の濃度であり、

半導体を含む層の堆積は、誘電体組成物を液相堆積する前、または相分離を生成した後になされる。

半導体を含む層を堆積することと、

低誘電率材料および高誘電率材料および液体を含む誘電体組成物を液相堆積することとを含み、ここで、低誘電率材料および高誘電率材料は液体に溶解され、

さらにこのプロセスは、

多量の低誘電率材料/少量の高誘電率材料の第1相および多量の高誘電率材料/少量の低誘電率材料の第2相を備える相分離ゲート誘電体を形成するために、低誘電率材料および高誘電率材料の相分離を生成することを含み、ここで、低誘電率材料は、半導体を含む層に最も近い誘電体構造領域内の高誘電率材料の濃度に比べて高濃度であり、

半導体を含む層の堆積は、誘電体組成物を液相堆積する前、または相分離を生成した後になされる。

(1)中間相(層の形態の)は、第1相(層の形態の)と第2相(層の形態の)との間に現れる、

(2)1つの相は他の相の連続的なマトリクス内の複数の「点」を形成する、

(3)1つの相は他の相の連続的なマトリクス内の複数のロッド形状要素(例えばシリンダ)を形成する、および

(4)1つの相は他の相内に貫入して、同相ドメインを形成する。

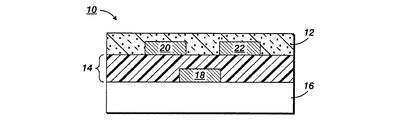

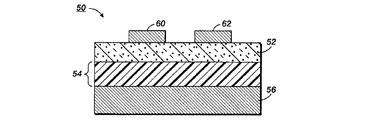

(基板)

基板は、例えばシリコン、ガラス板、プラスチックフィルムまたはシートから構成されてもよい。構造的に柔軟なデバイスでは、例えばポリエステル、ポリカーボネート、ポリイミドシートなどのプラスチック基板が好ましい。基板の厚みは、約10μmから約10mmを超えてもよく、例示的な厚みは特に柔軟なプラスチック基板では約50から約100mm、ガラス板またはシリコンウエハーなどの剛性の基板では約1から約10mmである。

(電極)

ゲート電極は、薄い金属フィルム、伝導性ポリマーフィルム、伝導性インクまたはペーストから作られる伝導性フィルムであってもよく、または基板自体がゲート電極、例えば高濃度ドープシリコンであってもよい。ゲート電極材料の例はアルミニウム、金、クロム、インジウムスズ酸化物、ポリスチレンスルホン酸ドープポリ(3,4−エチレンジオキシチオフェン)(PSS−PEDOT)、カーボンブラック/グラファイトからなる伝導性インク/ペーストまたはアチソン・コロイズ社(Acheson Colloids Company)から市販されている商標ELECTRODAGなどのポリマーバインダにコロイド状の銀を分散したものを含むが、これらに限定されない。ゲート電極層は、真空蒸着、金属または導電性金属酸化物のスパッタリング、スピンコーティングによる導電性ポリマー溶液または伝導性インクによるコーティング、キャスティング、または印刷によって調製される。ゲート電極層の厚みは、例えば金属フィルムでは約10から約200nm、ポリマー導電体では約1から約10μmである。

(半導体層)

有機半導体層としての使用に適した材料は、アントラセン、テトラセン、ペンタセンおよび代替ペンタセンなどのアセン、ペリレン、フラーレン、フタロシアニン、オリゴチオフェン、ポリチオフェンおよびこれらの代替誘導体を含む。いくつかの実施形態では、有機半導体層は液体プロセス可能材料から形成される。適切な半導体材料の例は、ポリチオフェン、オリゴチオフェンおよび米国特許出願公開番号第2003/0160234号として公開されている米国特許出願第10/042,342号、米国特許第6,621,099号、米国特許第6,774,393号および米国特許第6,770,904号に記載されている半導体ポリマーを含み、この全開示内容は、参照により本明細書に引用したものとする。これに加えて、適切な材料はC.D.ディミトラコポロス(C.D.Dimitrakopoulos)およびP.R.L.マレンファント(P.R.L.Malenfant)の「大面積電子回路における有機薄膜トランジスタ(Organic Thin Film Transistors for Large Area Electronics)」アドバンスド・マテリアルズ(Adv.Mater.)、第12巻、第2号、p.99〜117(2002)に開示されている半導体ポリマーを含み、この全開示内容は、参照により本明細書に組み込まれる。

(ゲート誘電体)

ゲート誘電体の組成および形成が本明細書では開示されている。いくつかの実施形態では、ゲート誘電体の第1相および第2相は相互に接触する。他の実施形態では中間相は第1相と第2相の間に存在する。いくつかの実施形態では、ゲート誘電体の第1相は半導体層と接触する。他の実施形態では、界面層は第1相と半導体層の間に存在する。いくつかの実施形態では、ゲート誘電体の第1相および第2相の両方は半導体層と接触する。他の実施形態では、ゲート誘電体の第1相および第2相の両方は半導体層と接触するが、半導体層と第1相との間の接触面積は薄膜トランジスタのチャネル領域(ソース電極とドレイン電極間の領域)における半導体層と第2相との間の接触面積より大きい。

(比較例1)

本比較例では、均一なゲート誘電体は以下のとおり調製された。0.08gポリ(4−ビニルフェノール)(PVP)(アルドリッチ、Mw=約20,000)は0.9g n−ブタノールで溶解された。0.08gポリ(メラミン−co−ホルムアルデヒド)(アルドリッチ、n−ブタノールにおいてメチル化84重量パーセント、Mn=432)は架橋剤として加えられた。誘電体組成物は最初に0.2ミクロンシリンジフィルタで濾過され、次にAlコーティングされたPET基板に2000rpmでスピンコーティングされた。ここではAl層はOTFTのゲート電極として機能する。80℃で10分間乾燥した後、誘電層は160℃で30分間熱的に架橋結合された。

(実施例1)

本実施例では、相分離誘電体構造は以下のとおり調製された。ポリ(メチルシルセスキオキサン)(PMSSQ)は、ポリチオフェン半導体との優れた適合性を提供するために低誘電率材料として使用され、ポリ(4−ビニルフェノール)(PVP)は高誘電率材料として使用され、n−ブタノールは液として使用された。PMSSQは以下の手順により前駆物質としてメチルトリメトキシシランを使用して調製された。水溶性0.1重量パーセント塩酸溶液0.88グラムとテトラヒドロフラン5.13グラムの混合物が、乾燥環境下で十分な攪拌により30分間にわたり氷浴で冷却された三つ口フラスコ中でメチルトリメトキシシラン0.48グラムとメチルイソブチルケトン9.24グラムの混合物に滴下で加えられた。結果として得られた混合物は、室温に温められ、その温度に5分間維持され、その後60℃に加熱され、24時間維持された。ポリ(メラミン−co−ホルムアルデヒド)が高誘電率材料PVPの架橋剤として加えられた。誘電体組成物は以下の表に示される材料の量を使用して生成された。

(比較例2)

本比較例では、ポリ(2−ヒドロキシエチル、メタクリレート)(サイエンティフィック・ポリマー・プロダクツ社(Scientific Polymer Products,Inc.)、Mw=1,000,000)が誘電体材料として使用され、Dowanol(ドワノール)を液体として使用して均一な誘電体構造が形成された。誘電体組成物は、0.0008gのp−トルエンスルホン酸が架橋結合の触媒として加えられたことを除いて、比較例1と同様に調製された。誘電体構造を備えるOTFTデバイスは約0.002−0.0043cm2/V.sおよび約104の電流on/off比の移動度を示した。

(実施例2)

本実施例では、ポリ(2−ヒドロキシエチル、メタクリレート)が高誘電率材料として使用され、Dowanolを液体として使用して、実施例1のPVPおよびn−ブタノールが置換された。誘電体組成物は0.0008gのp−トルエンスルホン酸が架橋結合の触媒として加えられたことを除いて、実施例1と同様に調製された。誘電体構造を備えるOTFTは約0.05〜0.06cm2/V.sおよび約104の電流on/off比の移動度を示した。

(比較例3)

この比較例では、均一なゲート誘電体はn−ブタノール溶液中のPMSSQから調製された。誘電体組成物は最初に0.2ミクロンシリンジフィルタで濾過され、次にAlコーティングされたPET基板に2000rpmでスピンコーティングされた。ここでAl層はOTFTのゲート電極として機能する。80℃で10分間乾燥した後、誘電体層は160℃で30分間熱的に架橋結合された。この誘電体構造を備えるOTFTデバイスは、誘電層の漏れのために、極めて低いデバイス歩留まり(<10%)を示した。機能デバイスは0.06cm2/V.sおよび100〜1000電流on/off比の移動度を示した。

Claims (5)

- 電子デバイスを製造するプロセスであって、該プロセスは、

有機半導体を含む層を堆積することと、

低誘電率ポリマー、当該低誘電率ポリマーより誘電率が高い高誘電率ポリマーおよび液体を含む誘電体組成物を、前記層に接するように、液相堆積することとを含み、かつ、前記低誘電率ポリマーおよび前記高誘電率ポリマーは液相堆積の前に相分離されず、

さらに前記プロセスは、

相分離誘電体構造を形成するために、前記低誘電率ポリマーおよび前記高誘電率ポリマーの相分離をし、

当該相分離誘電体構造の前記層に接する界面における前記低誘電率ポリマーの重量は、当該界面における前記高誘電率ポリマーの重量に比べて大きく、

前記層の堆積は、前記誘電体組成物を液相堆積する前、または相分離を生成した後になされる、前記プロセス。 - 電子デバイスを製造するプロセスであって、該プロセスは、

有機半導体を含む層を堆積することと、

低誘電率ポリマー、当該低誘電率ポリマーより誘電率が高い高誘電率ポリマーおよび液体を含む誘電体組成物を単一ステップで、前記層に接するように、液相堆積することとを含み、かつ、前記低誘電率ポリマーおよび前記高誘電率ポリマーは液相堆積の前に相分離されず、

さらに前記プロセスは、

相分離誘電体構造を形成するために、前記低誘電率ポリマーおよび前記高誘電率ポリマーの相分離をし、当該相分離誘電体構造の前記層に接する界面における前記低誘電率ポリマーの割合は、当該相分離誘電体構造の前記層に接する界面における前記低誘電率ポリマーおよび前記高誘電率ポリマーの総重量の60%から100%であり、当該界面における前記高誘電率ポリマーの割合は当該総重量の40%から0%であり、

前記層の堆積は、前記誘電体組成物を液相堆積する前、または相分離を生成した後になされる、前記プロセス。 - 薄膜トランジスタを製造するプロセスであって、該プロセスは、

有機半導体を含む層を堆積することと、

低誘電率ポリマーおよび当該低誘電率ポリマーより誘電率が高い高誘電率ポリマーおよび液体を含む誘電体組成物を、前記層に接するように、液相堆積することとを含み、かつ、前記低誘電率ポリマーおよび前記高誘電率ポリマーは前記液体に溶解され、

さらに前記プロセスは、

多量の低誘電率ポリマー/少量の高誘電率ポリマーの前記層に接する第1相および多量の高誘電率ポリマー/少量の低誘電率ポリマーの前記層に対する位置が当該第1相よりも遠い第2相を備える相分離ゲート誘電体を形成するために、前記低誘電率ポリマーおよび前記高誘電率ポリマーの相分離を生成することを含み、かつ、当該第1相の前記層に接する界面における前記低誘電率ポリマーの重量は、当該界面における前記高誘電率ポリマーの重量に比べて大きく、

前記層の堆積は、前記誘電体組成物を液相堆積する前、または相分離を生成した後になされ、

前記低誘電率ポリマーは、4.0未満の誘電率を有し、

前記高誘電率ポリマーは、4.0以上の誘電率を有する、

前記プロセス。 - 前記液相堆積は、単一ステップで達成される、請求項1のプロセス。

- 前記相分離を生成することは、熱アニーリングにより行われる、請求項1のプロセス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/695,131 | 2007-04-02 | ||

| US11/695,131 US7754510B2 (en) | 2007-04-02 | 2007-04-02 | Phase-separated dielectric structure fabrication process |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012003967A Division JP5451784B2 (ja) | 2007-04-02 | 2012-01-12 | エッジエミッティングレーザのモノリシックアレイ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008258609A JP2008258609A (ja) | 2008-10-23 |

| JP2008258609A5 JP2008258609A5 (ja) | 2011-05-12 |

| JP4908446B2 true JP4908446B2 (ja) | 2012-04-04 |

Family

ID=39495271

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008077941A Active JP4908446B2 (ja) | 2007-04-02 | 2008-03-25 | 電子デバイスを製造するプロセス及び薄膜トランジスタを製造するプロセス |

| JP2012003967A Active JP5451784B2 (ja) | 2007-04-02 | 2012-01-12 | エッジエミッティングレーザのモノリシックアレイ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012003967A Active JP5451784B2 (ja) | 2007-04-02 | 2012-01-12 | エッジエミッティングレーザのモノリシックアレイ |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7754510B2 (ja) |

| EP (1) | EP1978572B1 (ja) |

| JP (2) | JP4908446B2 (ja) |

| KR (1) | KR101409725B1 (ja) |

| CA (1) | CA2627393C (ja) |

| TW (1) | TWI422611B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI412125B (zh) * | 2007-07-17 | 2013-10-11 | Creator Technology Bv | 電子元件及電子元件之製法 |

| GB2458940B (en) * | 2008-04-03 | 2010-10-06 | Cambridge Display Tech Ltd | Organic thin film transistors |

| US8154080B2 (en) * | 2008-12-05 | 2012-04-10 | Xerox Corporation | Dielectric structure having lower-k and higher-k materials |

| JP5532669B2 (ja) * | 2009-04-30 | 2014-06-25 | 大日本印刷株式会社 | 有機半導体素子、およびその製造方法 |

| SG168450A1 (en) * | 2009-08-05 | 2011-02-28 | Sony Corp | Thin film transistor |

| US8221909B2 (en) * | 2009-12-29 | 2012-07-17 | Ut-Battelle, Llc | Phase-separated, epitaxial composite cap layers for electronic device applications and method of making the same |

| US8486864B2 (en) * | 2009-12-29 | 2013-07-16 | Ut-Battelle, Llc | Method for producing microstructured templates and their use in providing pinning enhancements in superconducting films deposited thereon |

| US9076975B2 (en) | 2010-04-27 | 2015-07-07 | Xerox Corporation | Dielectric composition for thin-film transistors |

| US8623447B2 (en) | 2010-12-01 | 2014-01-07 | Xerox Corporation | Method for coating dielectric composition for fabricating thin-film transistors |

| US8821962B2 (en) * | 2010-12-01 | 2014-09-02 | Xerox Corporation | Method of forming dielectric layer with a dielectric composition |

| KR20120060154A (ko) * | 2010-12-01 | 2012-06-11 | 제록스 코포레이션 | 박막 트랜지스터용 유전체 조성물 |

| JP5842008B2 (ja) * | 2011-10-24 | 2016-01-13 | パナソニック株式会社 | 薄膜トランジスタ、有機el発光素子及び薄膜トランジスタの製造方法 |

| US8871425B2 (en) * | 2012-02-09 | 2014-10-28 | Az Electronic Materials (Luxembourg) S.A.R.L. | Low dielectric photoimageable compositions and electronic devices made therefrom |

| US8658444B2 (en) * | 2012-05-16 | 2014-02-25 | International Business Machines Corporation | Semiconductor active matrix on buried insulator |

| JP6647780B2 (ja) * | 2014-10-27 | 2020-02-14 | ローム アンド ハース エレクトロニック マテリアルズ エルエルシーRohm and Haas Electronic Materials LLC | 有機金属材料および方法 |

| US20250006647A1 (en) * | 2023-06-29 | 2025-01-02 | International Business Machines Corporation | Crosstalk noise reduction by high permeability insulator |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61144639A (ja) * | 1984-12-19 | 1986-07-02 | Hitachi Ltd | 放射線感応性組成物及びそれを用いたパタ−ン形成法 |

| US5374453A (en) | 1991-05-24 | 1994-12-20 | Rogers Corporation | Particulate filled composite film and method of making same |

| JPH06230386A (ja) * | 1993-02-05 | 1994-08-19 | Toshiba Corp | 液晶表示素子の製造方法 |

| US6107117A (en) | 1996-12-20 | 2000-08-22 | Lucent Technologies Inc. | Method of making an organic thin film transistor |

| US5883219A (en) * | 1997-05-29 | 1999-03-16 | International Business Machines Corporation | Integrated circuit device and process for its manufacture |

| US6528218B1 (en) * | 1998-12-15 | 2003-03-04 | International Business Machines Corporation | Method of fabricating circuitized structures |

| US6280794B1 (en) | 1999-03-10 | 2001-08-28 | Conexant Systems, Inc. | Method of forming dielectric material suitable for microelectronic circuits |

| US6136702A (en) | 1999-11-29 | 2000-10-24 | Lucent Technologies Inc. | Thin film transistors |

| MY128644A (en) * | 2000-08-31 | 2007-02-28 | Georgia Tech Res Inst | Fabrication of semiconductor devices with air gaps for ultra low capacitance interconnections and methods of making same |

| KR100432152B1 (ko) | 2001-04-12 | 2004-05-17 | 한국화학연구원 | 다분지형 폴리알킬렌 옥시드 포로젠과 이를 이용한저유전성 절연막 |

| US6949762B2 (en) | 2002-01-11 | 2005-09-27 | Xerox Corporation | Polythiophenes and devices thereof |

| US6621099B2 (en) | 2002-01-11 | 2003-09-16 | Xerox Corporation | Polythiophenes and devices thereof |

| US6770904B2 (en) | 2002-01-11 | 2004-08-03 | Xerox Corporation | Polythiophenes and electronic devices generated therefrom |

| JP4014431B2 (ja) * | 2002-03-27 | 2007-11-28 | 富士通株式会社 | 半導体記憶装置及び半導体記憶装置の製造方法 |

| US6528409B1 (en) * | 2002-04-29 | 2003-03-04 | Advanced Micro Devices, Inc. | Interconnect structure formed in porous dielectric material with minimized degradation and electromigration |

| US20030227014A1 (en) | 2002-06-11 | 2003-12-11 | Xerox Corporation. | Process for forming semiconductor layer of micro-and nano-electronic devices |

| JP4272441B2 (ja) * | 2003-02-05 | 2009-06-03 | 株式会社リコー | 有機能動素子及びそれを有する表示素子 |

| US7098525B2 (en) * | 2003-05-08 | 2006-08-29 | 3M Innovative Properties Company | Organic polymers, electronic devices, and methods |

| KR100995451B1 (ko) * | 2003-07-03 | 2010-11-18 | 삼성전자주식회사 | 다층 구조의 게이트 절연막을 포함하는 유기 박막 트랜지스터 |

| JP2005072569A (ja) * | 2003-08-06 | 2005-03-17 | Mitsubishi Chemicals Corp | 有機電界効果トランジスタ |

| JP2005175386A (ja) * | 2003-12-15 | 2005-06-30 | Asahi Kasei Corp | 有機半導体素子 |

| JP2005243822A (ja) * | 2004-02-25 | 2005-09-08 | Seiko Epson Corp | 薄膜トランジスタの製造方法、薄膜トランジスタ、薄膜トランジスタ回路、電子デバイスおよび電子機器 |

| US7098150B2 (en) * | 2004-03-05 | 2006-08-29 | Air Liquide America L.P. | Method for novel deposition of high-k MSiON dielectric films |

| US20060214154A1 (en) | 2005-03-24 | 2006-09-28 | Eastman Kodak Company | Polymeric gate dielectrics for organic thin film transistors and methods of making the same |

| US7282735B2 (en) | 2005-03-31 | 2007-10-16 | Xerox Corporation | TFT having a fluorocarbon-containing layer |

| US20060231908A1 (en) | 2005-04-13 | 2006-10-19 | Xerox Corporation | Multilayer gate dielectric |

| US7348280B2 (en) * | 2005-11-03 | 2008-03-25 | International Business Machines Corporation | Method for fabricating and BEOL interconnect structures with simultaneous formation of high-k and low-k dielectric regions |

| US7795614B2 (en) | 2007-04-02 | 2010-09-14 | Xerox Corporation | Device with phase-separated dielectric structure |

-

2007

- 2007-04-02 US US11/695,131 patent/US7754510B2/en active Active

-

2008

- 2008-03-19 EP EP08152980.2A patent/EP1978572B1/en active Active

- 2008-03-25 CA CA2627393A patent/CA2627393C/en active Active

- 2008-03-25 JP JP2008077941A patent/JP4908446B2/ja active Active

- 2008-03-31 TW TW097111666A patent/TWI422611B/zh active

- 2008-04-02 KR KR1020080030862A patent/KR101409725B1/ko active Active

-

2009

- 2009-05-07 US US12/436,975 patent/US7829625B2/en active Active

-

2012

- 2012-01-12 JP JP2012003967A patent/JP5451784B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| TW200844134A (en) | 2008-11-16 |

| US20080242112A1 (en) | 2008-10-02 |

| KR101409725B1 (ko) | 2014-06-19 |

| US7829625B2 (en) | 2010-11-09 |

| CA2627393A1 (en) | 2008-10-02 |

| CA2627393C (en) | 2016-07-12 |

| TWI422611B (zh) | 2014-01-11 |

| EP1978572A3 (en) | 2011-05-18 |

| EP1978572B1 (en) | 2016-11-02 |

| KR20080090329A (ko) | 2008-10-08 |

| US20090234056A1 (en) | 2009-09-17 |

| JP2008258609A (ja) | 2008-10-23 |

| JP2012109594A (ja) | 2012-06-07 |

| US7754510B2 (en) | 2010-07-13 |

| JP5451784B2 (ja) | 2014-03-26 |

| EP1978572A2 (en) | 2008-10-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4908446B2 (ja) | 電子デバイスを製造するプロセス及び薄膜トランジスタを製造するプロセス | |

| JP4908447B2 (ja) | 電子デバイス及び薄膜トランジスタ | |

| US9076975B2 (en) | Dielectric composition for thin-film transistors | |

| CN102487125B (zh) | 介电组合物 | |

| US8154080B2 (en) | Dielectric structure having lower-k and higher-k materials | |

| US9058981B2 (en) | Dielectric composition for thin-film transistors | |

| JP7083106B2 (ja) | 有機半導体組成物及びその用途 | |

| KR20120060154A (ko) | 박막 트랜지스터용 유전체 조성물 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110324 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110324 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20110324 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20110426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110510 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110808 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110830 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110921 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111213 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4908446 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |