JP4877869B2 - 有機半導体素子の作製方法 - Google Patents

有機半導体素子の作製方法 Download PDFInfo

- Publication number

- JP4877869B2 JP4877869B2 JP2004359575A JP2004359575A JP4877869B2 JP 4877869 B2 JP4877869 B2 JP 4877869B2 JP 2004359575 A JP2004359575 A JP 2004359575A JP 2004359575 A JP2004359575 A JP 2004359575A JP 4877869 B2 JP4877869 B2 JP 4877869B2

- Authority

- JP

- Japan

- Prior art keywords

- organic semiconductor

- semiconductor film

- baking

- electrode

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 176

- 238000004519 manufacturing process Methods 0.000 title claims description 26

- 238000000034 method Methods 0.000 claims description 52

- 238000010438 heat treatment Methods 0.000 claims description 18

- 238000001771 vacuum deposition Methods 0.000 claims description 5

- 239000011261 inert gas Substances 0.000 claims description 4

- 230000008018 melting Effects 0.000 claims description 4

- 238000002844 melting Methods 0.000 claims description 4

- 239000010408 film Substances 0.000 description 166

- 239000000758 substrate Substances 0.000 description 45

- 239000000463 material Substances 0.000 description 42

- 239000010410 layer Substances 0.000 description 33

- 239000004973 liquid crystal related substance Substances 0.000 description 32

- 238000007740 vapor deposition Methods 0.000 description 28

- 230000006866 deterioration Effects 0.000 description 20

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 18

- -1 silver halide Chemical class 0.000 description 13

- 238000000151 deposition Methods 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 11

- 238000005259 measurement Methods 0.000 description 10

- 150000001875 compounds Chemical class 0.000 description 8

- PCCVSPMFGIFTHU-UHFFFAOYSA-N tetracyanoquinodimethane Chemical compound N#CC(C#N)=C1C=CC(=C(C#N)C#N)C=C1 PCCVSPMFGIFTHU-UHFFFAOYSA-N 0.000 description 8

- 229910052721 tungsten Inorganic materials 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 7

- 239000001301 oxygen Substances 0.000 description 7

- 229910052760 oxygen Inorganic materials 0.000 description 7

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 238000004528 spin coating Methods 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 238000013459 approach Methods 0.000 description 5

- 230000008859 change Effects 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 235000012239 silicon dioxide Nutrition 0.000 description 5

- 229920003002 synthetic resin Polymers 0.000 description 5

- 239000000057 synthetic resin Substances 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- MWPLVEDNUUSJAV-UHFFFAOYSA-N anthracene Chemical compound C1=CC=CC2=CC3=CC=CC=C3C=C21 MWPLVEDNUUSJAV-UHFFFAOYSA-N 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 229920000547 conjugated polymer Polymers 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 150000002678 macrocyclic compounds Chemical class 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 229920000620 organic polymer Polymers 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 229920000139 polyethylene terephthalate Polymers 0.000 description 4

- 239000005020 polyethylene terephthalate Substances 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- FHCPAXDKURNIOZ-UHFFFAOYSA-N tetrathiafulvalene Chemical compound S1C=CSC1=C1SC=CS1 FHCPAXDKURNIOZ-UHFFFAOYSA-N 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 229920001709 polysilazane Polymers 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- WCBPJVKVIMMEQC-UHFFFAOYSA-N 1,1-diphenyl-2-(2,4,6-trinitrophenyl)hydrazine Chemical group [O-][N+](=O)C1=CC([N+](=O)[O-])=CC([N+]([O-])=O)=C1NN(C=1C=CC=CC=1)C1=CC=CC=C1 WCBPJVKVIMMEQC-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 2

- 229920000265 Polyparaphenylene Polymers 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- XBDYBAVJXHJMNQ-UHFFFAOYSA-N Tetrahydroanthracene Natural products C1=CC=C2C=C(CCCC3)C3=CC2=C1 XBDYBAVJXHJMNQ-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 238000007611 bar coating method Methods 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 239000002041 carbon nanotube Substances 0.000 description 2

- 229910021393 carbon nanotube Inorganic materials 0.000 description 2

- 150000001746 carotenes Chemical class 0.000 description 2

- 235000005473 carotenes Nutrition 0.000 description 2

- 238000005266 casting Methods 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 229910052681 coesite Inorganic materials 0.000 description 2

- 229910052906 cristobalite Inorganic materials 0.000 description 2

- 238000007598 dipping method Methods 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- KNMNNEPMKDJBDW-UHFFFAOYSA-N n-[2-(3,4-dimethoxyphenyl)ethyl]-1-(2,6-dimethylphenoxy)propan-2-amine;hydrochloride Chemical compound Cl.C1=C(OC)C(OC)=CC=C1CCNC(C)COC1=C(C)C=CC=C1C KNMNNEPMKDJBDW-UHFFFAOYSA-N 0.000 description 2

- MZYHMUONCNKCHE-UHFFFAOYSA-N naphthalene-1,2,3,4-tetracarboxylic acid Chemical class C1=CC=CC2=C(C(O)=O)C(C(=O)O)=C(C(O)=O)C(C(O)=O)=C21 MZYHMUONCNKCHE-UHFFFAOYSA-N 0.000 description 2

- YTVNOVQHSGMMOV-UHFFFAOYSA-N naphthalenetetracarboxylic dianhydride Chemical compound C1=CC(C(=O)OC2=O)=C3C2=CC=C2C(=O)OC(=O)C1=C32 YTVNOVQHSGMMOV-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- WSRHMJYUEZHUCM-UHFFFAOYSA-N perylene-1,2,3,4-tetracarboxylic acid Chemical class C=12C3=CC=CC2=CC=CC=1C1=C(C(O)=O)C(C(O)=O)=C(C(O)=O)C2=C1C3=CC=C2C(=O)O WSRHMJYUEZHUCM-UHFFFAOYSA-N 0.000 description 2

- CLYVDMAATCIVBF-UHFFFAOYSA-N pigment red 224 Chemical compound C=12C3=CC=C(C(OC4=O)=O)C2=C4C=CC=1C1=CC=C2C(=O)OC(=O)C4=CC=C3C1=C42 CLYVDMAATCIVBF-UHFFFAOYSA-N 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920001197 polyacetylene Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920000128 polypyrrole Polymers 0.000 description 2

- 229920000123 polythiophene Polymers 0.000 description 2

- 229920002717 polyvinylpyridine Polymers 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 102000004169 proteins and genes Human genes 0.000 description 2

- 108090000623 proteins and genes Proteins 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 238000011160 research Methods 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 239000007858 starting material Substances 0.000 description 2

- 229910052682 stishovite Inorganic materials 0.000 description 2

- 125000001424 substituent group Chemical group 0.000 description 2

- IFLREYGFSNHWGE-UHFFFAOYSA-N tetracene Chemical compound C1=CC=CC2=CC3=CC4=CC=CC=C4C=C3C=C21 IFLREYGFSNHWGE-UHFFFAOYSA-N 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 229910052905 tridymite Inorganic materials 0.000 description 2

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 238000007743 anodising Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910021485 fumed silica Inorganic materials 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 150000002496 iodine Chemical class 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 239000011344 liquid material Substances 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- 239000012044 organic layer Substances 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 239000002002 slurry Substances 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

Images

Landscapes

- Thin Film Transistor (AREA)

Description

八木巌, 塚越一仁, 青柳克信 「表面処理を行ったSiO2/Si基板 上に作製したペンタセンFET」 第50回応用物理学関係連合講演会講演予稿 集(2003.3) p.1418下段

これにより、オンオフの閾値を0Vに近づけることができ、オンオフ比を上げることができる。

このように有機半導体素子の特性を改善することができる。

但し、本発 明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から 逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に 理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

本実施の形態では、ボトムコンタクト型の有機半導体素子として、有機TFTの作製方法について説明する。

本実施の形態では、実施の形態1とは異なり、有機半導体膜形成後、ソース電極及びドレイン電極を形成するトップコンタクト型の有機TFTの場合を、図2を用いて説明する。

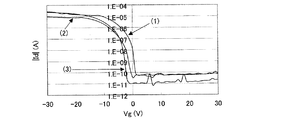

(1)ベークなし

(2)大気下において、120℃で、10分ベーク

(3)大気下において、150℃で、10分ベーク

(4)大気下において、200℃で、10分ベーク

(5)大気下において、250℃で、10分ベーク

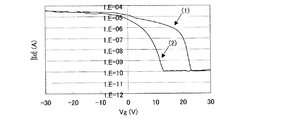

(1)蒸着後のベーク前

(2)(1)を大気下において、120℃で、10分ベーク

(3)(2)をさらに大気下において、120℃で、30分ベーク

以上から、蒸着後のベークは有機TFTの特性改善に有効であると考えられる。

(1)減圧下(1.2×104Pa)において、120℃で、10分ベーク

(2)減圧下(1.2×104Pa)において、150℃で、10分ベーク

(3)減圧下(1.2×104Pa)において、200℃で、10分ベーク

(1)減圧下(1.2×104Pa)において、150℃で、30分ベーク

(2)(1)を大気下において48時間放置

(3)(2)を減圧下(1.2×104Pa)において、150℃で、30分ベーク

(1)ベークなし

(2)120℃で、10分ベーク

(1)蒸着後ベークなし

(2)蒸着後に減圧下(1.2×104Pa)において、150℃で、10分ベーク

本発明の半導体装置を含む液晶装置の態様について、図11を用いて説明する。なお、液晶装置の構成について特に限定は無く、本形態で示した態様の他、例えば、素子基板上に、駆動回路が設けられたものであってもよい。また、液晶装置に限定されるものではなく、発光素子を有する表示装置のスイッチング素子等に本発明の有機半導体装置を用いても良い。

以上のような表示装置は、図13(A)、(B)、(C)に示すように、携帯電話機や、テレビ受像機等に実装される表示装置として用いることができる。IDカードの様な個人情報を管理する機能を有するカード等に実装してもよい。また、本発明の利用形態は図13に示した例に限定されず、様々な電子機器に利用することが可能である。

101 ゲート電極

102 ゲート絶縁膜

103 ソースまたはドレイン電極

104 有機半導体膜

110 素子基板

200 基板

201 ゲート電極

202 ゲート絶縁膜

203 有機半導体膜

204 電極

210 素子基板

301 ゲート電極

302 ソース電極

303 ドレイン電極

304 ソース電極用パッド

305 ドレイン電極用パッド

306 ゲート電極用パッド

1101 素子基板

1102 対向基板

1103 画素部

1104 端子部

1105 フレキシブルプリント配線

521 素子基板

522 ゲート電極

523 ゲート絶縁層

524 有機半導体膜

525 電極

526 電極

527 トランジスタ

528 絶縁層

529 画素電極

530 配向膜

531 対向基板

532 対向電極

533 配向膜

534 液晶層

535 スペーサ

551 素子基板

552 ゲート電極

553 ゲート絶縁層

554 電極

555 電極

556 有機半導体膜

557 トランジスタ

558a 絶縁層

558b 絶縁層

559 画素電極

560 配向膜

561 対向基板

562 対向電極

563 配向膜

564 液晶層

565 スペーサ

1301 表示部

1302 本体

1303 アンテナ

1304 音声出力部

1305 音声入力部

1306 操作スイッチ

1307 操作スイッチ

1311 表示部

1312 筐体

1313 スピーカー

1321 支持体

1322 表示部

1323 集積回路チップ

1324 集積回路

1325 集積回路

Claims (8)

- ゲート電極を形成し、

真空蒸着法により、前記ゲート電極上に有機半導体膜を形成し、

前記有機半導体膜を減圧下で加熱して前記有機半導体膜を大気中に放置後、減圧下で加熱し、

前記加熱された有機半導体膜上にソース電極及びドレイン電極を形成することを特徴とする有機半導体素子の作製方法。 - ゲート電極を形成し、

前記ゲート電極上にソース電極及びドレイン電極を形成し、

真空蒸着法により、前記ソース電極及びドレイン電極上に有機半導体膜を形成し、

前記有機半導体膜を減圧下で加熱して前記有機半導体膜を大気中に放置後、減圧下で加熱することを特徴とする有機半導体素子の作製方法。 - 請求項1又は請求項2において、

前記減圧下、かつ不活性ガス雰囲気において、前記有機半導体膜を加熱することを特徴とする有機半導体素子の作製方法。 - ゲート電極を形成し、

真空蒸着法により、前記ゲート電極上に有機半導体膜を形成し、

前記有機半導体膜を減圧下で加熱して前記有機半導体膜を大気中に放置後、大気圧下で加熱し、

前記加熱された有機半導体膜上にソース電極及びドレイン電極を形成することを特徴とする有機半導体素子の作製方法。 - ゲート電極を形成し、

前記ゲート電極上にソース電極及びドレイン電極を形成し、

真空蒸着法により、前記ソース電極及びドレイン電極上に有機半導体膜を形成し、

前記有機半導体膜を減圧下で加熱して前記有機半導体膜を大気中に放置後、大気圧下で加熱することを特徴とする有機半導体素子の作製方法。 - 請求項1乃至請求項5のいずれか一において、

前記有機半導体膜を加熱するときは、前記有機半導体膜の融点未満で加熱することを特徴とする有機半導体素子の作製方法。 - 請求項1乃至請求項6のいずれか一において、

前記有機半導体膜を加熱するときは、250℃未満で加熱することを特徴とする有機半導体素子の作製方法。 - 請求項1乃至請求項7のいずれか一において、

前記有機半導体膜を加熱するときは、前記有機半導体膜の粒界の大きさの平均値が10%以上成長しない温度で加熱することを特徴とする有機半導体素子の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004359575A JP4877869B2 (ja) | 2003-12-26 | 2004-12-13 | 有機半導体素子の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003434620 | 2003-12-26 | ||

| JP2003434620 | 2003-12-26 | ||

| JP2004359575A JP4877869B2 (ja) | 2003-12-26 | 2004-12-13 | 有機半導体素子の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005210087A JP2005210087A (ja) | 2005-08-04 |

| JP2005210087A5 JP2005210087A5 (ja) | 2007-11-08 |

| JP4877869B2 true JP4877869B2 (ja) | 2012-02-15 |

Family

ID=34914336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004359575A Expired - Fee Related JP4877869B2 (ja) | 2003-12-26 | 2004-12-13 | 有機半導体素子の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4877869B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007096129A (ja) * | 2005-09-29 | 2007-04-12 | Kyoto Univ | 分子トランジスタおよびその製造方法、並びにそれを用いた不揮発性メモリおよび圧電センサ |

| JP5380831B2 (ja) * | 2007-12-07 | 2014-01-08 | 株式会社リコー | 有機トランジスタ及びその製造方法 |

| JP2010199099A (ja) * | 2009-02-20 | 2010-09-09 | Univ Of Tokyo | 有機電界効果トランジスタにおけるしきい値電圧の制御方法 |

| JP2010199100A (ja) * | 2009-02-20 | 2010-09-09 | Univ Of Tokyo | 有機半導体素子の作製法 |

| JP5733612B2 (ja) * | 2011-03-08 | 2015-06-10 | 国立大学法人信州大学 | 有機半導体薄膜用材料、該材料を用いた有機半導体薄膜の形成方法および有機薄膜トランジスタ |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5574291A (en) * | 1994-12-09 | 1996-11-12 | Lucent Technologies Inc. | Article comprising a thin film transistor with low conductivity organic layer |

-

2004

- 2004-12-13 JP JP2004359575A patent/JP4877869B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005210087A (ja) | 2005-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8202760B2 (en) | Method for manufacturing an organic semiconductor element | |

| JP5412458B2 (ja) | 半導体装置の作製方法 | |

| CN102224580B (zh) | 薄膜晶体管制造方法、薄膜晶体管以及电子装置 | |

| US8227294B2 (en) | Manufacturing method of semiconductor device | |

| JP5025110B2 (ja) | 半導体装置の作製方法 | |

| JP4836446B2 (ja) | 半導体装置の作製方法 | |

| JP5477750B2 (ja) | 有機電界効果型トランジスタ | |

| US9634271B2 (en) | Semiconductor device, method of manufacturing the same, and electronic apparatus | |

| JP4877869B2 (ja) | 有機半導体素子の作製方法 | |

| JP4419425B2 (ja) | 有機薄膜トランジスタ素子 | |

| JP4856900B2 (ja) | 電界効果トランジスタの製造方法 | |

| JP5029938B2 (ja) | 電気泳動表示装置、電子機器、および電気泳動表示装置の製造方法 | |

| US20130193413A1 (en) | Stacking structure, organic semiconductor device, wiring, and display, and method of manufacturing organic semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070925 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070925 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110315 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110405 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111102 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111122 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111123 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4877869 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141209 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141209 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |