JP4875235B2 - 電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ - Google Patents

電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ Download PDFInfo

- Publication number

- JP4875235B2 JP4875235B2 JP2000101117A JP2000101117A JP4875235B2 JP 4875235 B2 JP4875235 B2 JP 4875235B2 JP 2000101117 A JP2000101117 A JP 2000101117A JP 2000101117 A JP2000101117 A JP 2000101117A JP 4875235 B2 JP4875235 B2 JP 4875235B2

- Authority

- JP

- Japan

- Prior art keywords

- total capacity

- battery

- capacity value

- cycles

- capacity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/28—Supervision thereof, e.g. detecting power-supply failure by out of limits supervision

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

Description

【発明の属する技術分野】

本発明は電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータに係り、特に、電力を供給可能なバッテリを備えた電源装置、電源装置に備えられたバッテリの総容量を示す容量情報を補正する電源容量情報補正装置、電源容量情報補正方法、及び該電源容量情報補正方法を適用したコンピュータに関する。

【0002】

【従来の技術】

近年、モービル・コンピューティングの普及と共に、様々な大きさや機能を有する携帯型パーソナル・コンピュータ(以下、ポータブルPCと呼ぶ)が開発されてきている。例えば、ノートブック型パーソナル・コンピュータ(PC)、サブノートブック型PC、パームトップ型PC、PDA(Personal Data Assistants;個人向け携帯型情報通信機器)などがある。

【0003】

ポータブルPCは、本体内に電池を内蔵している。この内蔵電池により、例えば、列車内などのように商用電源を利用することのできない環境下においても、ユーザは、ポータブルPCを使用することができる。上記内蔵電池には、充電することにより繰り返し使うことのできる2次電池を用いるのが一般的である。

【0004】

ところで、このようなポータブルPC等のコンピュータや様々な家庭用電化製品等に用いることができる2次電池として、電子回路が組み込まれたインテリジェント電池が注目されている。この電池によれば、内部に組み込まれた電子回路によって電池の残容量を外部に知らせることができる。従って、例えばポータブルPCの2次電池としてインテリジェント電池を用いることによって、ユーザは商用電源を利用することのできない環境下においてポータブルPCを使用している際に2次電池の残容量が尽きることを事前に知ることができ、使用中の突然のシャット・ダウンを回避することができる。

【0005】

このようなインテリジェント電池では、一般に、電池の総容量を示す容量情報を予め記憶しており、該容量情報によって示される総容量から、電池の放電電流値を積算することによって得られる放電量を減じることによって電池の残容量を得ている。

【0006】

ところで、2次電池は、放電及び充電が繰り返されるに従って、総容量が減少する特性を有している。図10には、定格電圧4.2Vのリチウム・イオン電池を3本直列接続して構成された実在の電池の、20°C及び40°Cの各環境下におけるサイクル特性の一例が示されている。なお、同図では、充電電流及び放電電流が共に2.5Aである場合について示されている。

【0007】

同図に示されるように、サイクル数が増加するほど、電池の容量は減少しており、この傾向は使用される環境の温度が高いほど顕著となっている。なお、上記「サイクル数」は、電池容量が0%から100%となるまで充電を行った後に、電池容量が0%となるまで放電した回数をいう。

【0008】

図10に示したサイクル特性はリチウム・イオン電池の一例であるが、リチウム・イオン電池以外のニッケル水素電池、ニッケル・カドミウム電池等の2次電池においても同様の傾向がある。

【0009】

このため、通常のインテリジェント電池では、図11に示されるように、電池の容量が零又は零近傍の所定容量となったときに、このときの電池の放電量が正確な電池の総容量であるものとして、該放電量に上記容量情報を置き換えることによって容量情報を学習している。これによって、その後に得られる残容量を高精度化することができる。

【0010】

【発明が解決しようとする課題】

しかしながら、上述した電池の容量が零又は零近傍の所定容量となったときに容量情報を学習する技術では、学習が行われない場合があり、この場合には残容量を高精度化することができない、という問題点があった。これは次の2つの理由によるものである。

【0011】

第1に、通常、2次電池は放電し切った後に充電を行うことは希であり、図11に示されるように、ある容量まで放電した後に充電を行うことが繰り返される場合が多く、この状態が連続したときには容量情報が学習されることがないためである。

【0012】

第2に、多くのPCにおいて採用されているオペレーティング・システムである米マイクロソフト社の“Windows98”では、2次電池を総容量の何%まで使用するかをユーザが設定できるようになっており、この設定のデフォルト値は3%となっている。この場合、ユーザが電池を空になるまで使用しようとしても、残容量が3%になったときにシステムはハイバネーション、又はスタンバイ状態となってしまう。このため、実使用状況において、電池の残容量が零になることはほとんどなく、電池の容量情報が学習されることは希である。

【0013】

以上のような場合には、電池を長時間使用し、電池の実際の総容量が減少してしまった場合でも、容量情報は電池出荷時のデフォルト値(新品電池の容量)のままとなり、このような状況でユーザが電池を使用すると、電池の残容量の容量飛び(例えば、残容量が50%から急に10%に減少するような現象)が発生してしまう。この場合、ユーザは電池の異常と判断するので、メーカは電池交換をしなければならない事態が多発することになる。

【0014】

本発明は上記事実を鑑みて成されたものであり、容量情報を的確に補正することのできる電源装置、電源容量情報補正装置、及び電源容量情報補正方法を得ると共に、内蔵された電源装置の容量情報を的確に補正することのできるコンピュータを得ることが目的である。

【0015】

【課題を解決するための手段】

本発明に係る電源装置は、バッテリと、前記バッテリの総容量を示す容量情報を記憶すると共に、前記バッテリのサイクル数に対する総容量を示しかつ前記容量情報を補正するための補正情報を記憶した情報記憶手段と、を備えている。ここで、上記バッテリには、リチウム・イオン電池、ニッケル水素電池、ニッケル・カドミウム電池、リチウム・ポリマー電池等が含まれる。また、上記情報記憶手段としてはあらゆる記憶媒体が適用できるが、EEPROM、フラッシュEEPROM等の電気的に書き換え可能な不揮発性メモリを適用することが好ましい。更に、上記補正情報としては、バッテリの所定サイクル数毎の各々に対する総容量をテーブル形式に構成したものや、バッテリのサイクル数に基づいて該サイクル数に対応する総容量を演算する関数等を適用することができる。

【0016】

このように、本発明の電源装置は、バッテリのサイクル数に対する総容量を示し、かつバッテリの総容量を示す容量情報を補正するための補正情報を記憶しているので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、上記補正情報を用いることによって、バッテリのサイクル数に基づき上記容量情報を的確に補正することができる。

【0017】

この容量情報の補正を電源装置自身によって行うためには、請求項2記載の発明のように、バッテリのサイクル数を計数する計数手段と、該計数手段によって計数されたサイクル数に対応する総容量を上記補正情報から取得して該総容量に基づいて容量情報を補正する補正手段と、を当該電源装置に備えておく必要がある。

【0018】

この電源装置では、計数手段によってバッテリのサイクル数が計数され、補正手段により、上記サイクル数に対応する総容量が上記補正情報から取得されて、該総容量に基づいて容量情報が補正される。なお、この容量情報の補正には、補正情報から取得された総容量に容量情報を置き換えることによる補正、補正情報から取得された総容量にバッテリの使用環境等を考慮した係数を乗じた容量に容量情報を置き換えることによる補正等を適用することができる。

【0019】

このように、本発明の電源装置に計数手段及び補正手段を備えることによって、簡易に容量情報を補正することができる。

【0020】

なお、上記計数手段は、バッテリの放電量又は充電量を検出し検出量について前記バッテリの総容量又は前記バッテリの総容量に所定係数を乗じた容量を単位サイクルとして前記バッテリのサイクル数を計数することができる。以下に、この根拠を説明する。

【0021】

図9には、実在するバッテリの部分放電及び100%放電を行った際のサイクル特性の実測結果例が示されている。このときの測定条件を以下に示す。

・バッテリ:リチウム・イオン電池単セル

・温度:25°C

・充電方法:定電圧・定電流充電方式(定電圧4.2V、定電流1.6A)

・充電時間:無条件に3時間の充電を実施

・容量測定方法:各部分放電が100サイクルに達したときに、1.6A定電流放電で、電池電圧2.75Vになるまで放電を行い、容量を測定

図9における横軸は100%放電に換算したときのサイクル数である。すなわち、20%部分放電の場合は、20%部分放電を5回繰り返したらサイクル数を1回と計算している。

【0022】

同図に示されるように、20%部分放電、30%部分放電、50%部分放電は何れもほぼ同一線上にのっている。なお、20%部分放電については、サイクル数350回以上でやや線から外れてくるが、この原因は、3時間の定時間充電を行っているために、劣化が発生したためと考えられている。すなわち、充電によって容量は短時間に100%に達するが、該充電をその後も継続して行っているため劣化が発生しているのである。ところが、電子機器では、通常、容量が100%に達した時点で充電を停止しているので、実使用環境では20%部分放電も30%部分放電、50%部分放電と同一線にのるものと考えられる。

【0023】

以上のことから、充電量又は放電量を積算し、該積算量がバッテリの総容量に所定係数(図9の電池の場合は約0.9)を乗じた量となったときが1サイクルとカウントし、サイクル数から電池容量を推定することができる。

【0024】

このように、バッテリの放電量又は充電量についてバッテリの総容量又はバッテリの総容量に所定係数を乗じた容量を単位サイクルとしてバッテリのサイクル数を計数することができるので、バッテリの容量が零又は零近傍の所定容量にならない場合であっても、簡易かつ高精度にサイクル数を計数することができる。

【0025】

一方、本発明の電源装置における補正手段は、前記バッテリの容量が零又は零近傍の所定容量になるまでの前記バッテリの総放電量に基づいて前記容量情報を補正すると共に、前記バッテリの容量が零又は零近傍の所定容量になったときの前記補正情報に示される総容量を、前記バッテリの総放電量に基づいて補正することが好ましい。

【0026】

すなわち、バッテリの容量が零又は零近傍の所定容量になるまでの当該バッテリの総放電量は、当該バッテリのその時点での総容量又は該総容量に近い量であるので、該総放電量に容量情報を置き換えること、該総放電量に基づく値に容量情報を置き換えること等によって、容量情報を、より正確なものに補正することができる。また、バッテリの容量が零又は零近傍の所定容量になったときの補正情報に示される総容量を、上記バッテリの総放電量に基づいて補正することによって、補正情報自身の誤差も補正することができる。

【0027】

更に、本発明の電源装置では、温度を検知する温度検知手段を更に備え、前記情報記憶手段に温度に対応する補正情報を含ませ、補正手段によって上記温度検知手段の検知温度に対応する補正情報に基づいて容量情報を補正することが好ましい。なお、上記温度には、バッテリの使用環境温度、バッテリの温度等が含まれる。これによって、温度も加味した、より高精度な容量情報の補正が可能となる。

【0028】

一方、本発明に係る電源容量情報補正装置及び電源容量情報補正方法は、内蔵されたバッテリの総容量を示す容量情報を記憶した容量情報記憶手段を備えた電源装置における前記容量情報を補正するものであって、前記バッテリのサイクル数に対する総容量を示しかつ前記容量情報を補正するための補正情報を記憶しておき、前記バッテリのサイクル数を計数すると共に、計数されたサイクル数に対応する総容量を前記補正情報から取得して該総容量に基づいて容量情報を補正するものである。

【0029】

従って、本発明に係る電源容量情報補正装置及び電源容量情報補正方法は、請求項2記載の電源装置と同様に作用するので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、バッテリのサイクル数に基づいて容量情報を的確に補正することができる。

【0030】

また、この電源容量情報補正装置及び電源容量情報補正方法においても、本発明に係る電源装置と同様に、バッテリの放電量又は充電量を検出し検出量について前記バッテリの総容量又は前記バッテリの総容量に所定係数を乗じた容量を単位サイクルとして前記バッテリのサイクル数を計数することができる。これによって、バッテリの容量が零又は零近傍の所定容量にならない場合であっても、簡易かつ高精度にサイクル数を計数することができる。

【0031】

また、この電源容量情報補正装置及び電源容量情報補正方法においても、本発明に係る電源装置と同様に、前記バッテリの容量が零又は零近傍の所定容量になるまでの前記バッテリの総放電量に基づいて前記容量情報を補正すると共に、前記バッテリの容量が零又は零近傍の所定容量になったときの前記補正情報に示される総容量を、前記バッテリの総放電量に基づいて補正することが好ましい。これによって、本発明に係る電源装置の場合と同様に、容量情報を、より正確なものに補正することができると共に、補正情報自身の誤差も補正することができる。

【0032】

更に、この電源容量情報補正装置及び電源容量情報補正方法においても、本発明に係る電源装置と同様に、温度に対応する補正情報を含ませ、検知温度に対応する補正情報に基づいて容量情報を補正することが好ましい。なお、上記検知温度には、バッテリの使用環境温度、バッテリの温度等が含まれる。これによって、温度も加味した、より高精度な容量情報の補正が可能となる。

【0033】

なお、本発明に係る電源容量情報補正方法を、バスによって相互接続されたCPU、記憶装置、表示装置、入力装置、内蔵されたバッテリの総容量を示す容量情報を記憶した電源装置を備えたコンピュータに適用する場合には、前記記憶装置を、前記電源装置で記憶されている容量情報を本発明の電源容量情報補正方法に従って補正するプログラムを記録したコンピュータ読み込み可能な記録媒体とすることによって実現することができる。このコンピュータによれば、電源装置の容量情報を的確に補正することができる。

【0034】

また、本発明に係る電源容量情報補正方法を、バスによって相互接続されたCPU、記憶装置、表示装置、入力装置、ネットワーク接続装置、内蔵されたバッテリの総容量を示す容量情報を記憶した電源装置を備えたコンピュータに適用する場合には、前記ネットワーク接続装置が接続するネットワーク上に配置されたサーバ・コンピュータの外部記憶装置を、前記電源装置で記憶されている容量情報を本発明の電源容量情報補正方法に従って補正するプログラムを記録したコンピュータ読み込み可能な記録媒体とすることによって実現することができる。このコンピュータによれば、電源装置の容量情報を的確に補正することができる。

【0035】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0036】

〔第1実施形態〕

図1には、本発明が適用された典型的なパーソナル・コンピュータ(PC)から成るコンピュータ・システム10のハードウェア構成がサブシステム毎に模式的に示されている。本発明を適用したPCの一例は、OADG(PC Open Architecture Developer's Group)仕様に準拠し、オペレーティング・システム(OS)として米マイクロソフト社の“Windows98又はNT”又は米IBM社の“OS/2”を搭載したノートブック型のPC12(図2参照)である。以下、コンピュータ・システム10の各部について説明する。

【0037】

コンピュータ・システム10全体の頭脳であるCPU14は、OSの制御下で、各種プログラムを実行する。CPU14は、例えば米インテル社製のCPUチップ“Pentium”や、AMD社等の他社製のCPUでも良いし、IBM社製の“PowerPC”でも良い。

【0038】

CPU14は、自身の外部ピンに直結されたプロセッサ直結バスとしてのFS(FrontSide)バス18、高速のI/O装置用バスとしてのPCI(Peripheral Component Interconnect)バス20、及び低速のI/O装置用バスとしてのISA(Industry Standard Architecture)バス22という3階層のバスを介して、後述の各ハードウェア構成要素と相互接続されている。

【0039】

FSバス18とPCIバス20は、一般にメモリ/PCI制御チップと呼ばれるCPUブリッジ(ホスト−PCIブリッジ)24によって連絡されている。

【0040】

メイン・メモリ16は、CPU14の実行プログラムの読み込み領域として、或いは実行プログラムの処理データを書き込む作業領域として利用される書き込み可能メモリである。

【0041】

なお、ここでいう実行プログラムには、Windows98等のOS、周辺機器類をハードウェア操作するための各種デバイスドライバ、特定業務に向けられたアプリケーション・プログラムや、フラッシュROM72に格納されたBIOS(Basic Input/Output System:キーボードやフロッピーディスク・ドライブ等の各ハードウェアの入出力操作を制御するためのプログラム)等のファームウェアが含まれる。

【0042】

PCIバス20は、比較的高速なデータ伝送が可能なタイプのバスであり、カードバス・コントローラ30のような比較的高速で駆動するPCIデバイス類がこれに接続される。

【0043】

ビデオ・サブシステム26は、ビデオに関連する機能を実現するためのサブシステムであり、CPU14からの描画命令を実際に処理し、処理した描画情報をビデオメモリ(VRAM)に一旦書き込むと共に、VRAMから描画情報を読み出して液晶ディスプレイ(LCD)28(図2参照)に描画データとして出力するビデオ・コントローラを含む。

【0044】

また、PCIバス20にはカードバス・コントローラ30、オーディオ・サブシステム32、ドッキング・ステーション・インタフェース(Dock I/F)34及びミニPCIスロット36が各々接続されている。カードバス・コントローラ30は、PCIバス20のバスシグナルをPCIカードバス・スロット38のインタフェース・コネクタ(カードバス)に直結させるための専用コントローラである。カードバス・スロット38には、例えばPC12本体の壁面に配設され、PCMCIA(Personal Computer Memory Association)/JEIDA(Japan Electronic Industry Development Association)が策定した仕様(例えば“PC Card Standard 95”)に準拠したPCカード40が装填される。

【0045】

Dock I/F34は、PC12とドッキング・ステーション(図示省略)を接続するためのハードウェアである。また、ミニPCIスロット36には、例えばコンピュータ・システム10をネットワーク(例えばLAN)に接続するためのネットワーク・アダプタ42が接続される。

【0046】

PCIバス20とISAバス22はI/Oブリッジ44によって相互に接続されている。I/Oブリッジ44は、PCIバス20とISAバス22とのブリッジ機能、IDE(Integrated Drive Electronics)インタフェース機能、USB(Universal Serial Bus)機能等を備えていると共に、リアルタイムクロック(RTC)を内蔵しており、例えばインテル社製のPIIX4というデバイス(コアチップ)を用いることができる。IDEインタフェース機能によって実現されるIDEインタフェースには、IDEハードディスク・ドライブ(HDD)46が接続される他、IDE CD−ROMドライブ48がATAPI(AT Attachment Packet Interface)接続される。

【0047】

また、I/Oブリッジ44にはUSBポートが設けられており、このUSBポートは、例えばPC12本体の壁面等に設けられたUSBコネクタ50と接続されている。

【0048】

更に、I/Oブリッジ44にはSMバスを介してEEPROM94が接続されている。EEPROM94はユーザによって登録されたパスワードやスーパーバイザー・パスワード、製品シリアル番号等の情報を保持するためのメモリであり、不揮発性で記憶内容を電気的に書き替え可能とされている。

【0049】

また、I/Oブリッジ44は電源回路54に接続されている。電源回路54はACアダプタ62、インテリジェント電池として構成されたメイン電池64A又はセカンド電池64Bを充電するための充電器68、及びコンピュータ・システム10で使用される5V、3.3V等の直流定電圧を生成するDC/DCコンバータ66等の回路を備えている。

【0050】

なお、本実施の形態におけるメイン電池64A及びセカンド電池64Bは、スマート・バッテリ仕様(Smart Battery Specification)に準拠するものとして構成されている。スマート・バッテリ仕様は米インテル社と米デュラセル社によって共同開発された仕様であり、内部に組み込まれた電子回路によって電池の残容量を外部に知らせることができるものである。また、スマート・バッテリ仕様では、製造者、シリアル・ナンバ、定格容量等の各種情報を内部に備えられたメモリに記憶しており、ユーザは該メモリに記憶されている各種情報をスマート・バッテリ仕様に従った各種コマンドによって取得することができる。

【0051】

一方、I/Oブリッジ44を構成するコアチップの内部には、コンピュータ・システム10の電源状態を管理するための内部レジスタと、該内部レジスタの操作を含むコンピュータ・システム10の電源状態の管理を行うロジック(ステートマシーン)が設けられている。

【0052】

上記ロジックは電源回路54との間で各種の信号を送受し、この信号の送受により、電源回路54からコンピュータ・システム10への実際の給電状態を認識し、電源回路54は上記ロジックからの指示に応じてコンピュータ・システム10への電力供給を制御する。

【0053】

ISAバス22はPCIバス20よりもデータ転送速度が低いバスであり、Super I/Oコントローラ70、EEPROM等から成るフラッシュROM72、CMOS74、ゲートアレイ・ロジック76に接続されたエンベデッド・コントローラ80に加え、キーボード/マウスコントローラのような比較的低速で動作する周辺機器類(何れも図示省略)を接続するのに用いられる。

【0054】

Super I/Oコントローラ70にはI/Oポート78が接続されている。Super I/Oコントローラ70は、フロッピーディスク・ドライブ(FDD)の駆動、パラレル・ポートを介したパラレル・データの入出力、シリアル・ポートを介したシリアル・データの入出力を制御する。

【0055】

フラッシュROM72は、BIOS等のプログラムを保持するためのメモリであり、不揮発性で記憶内容を電気的に書き替え可能とされている。また、CMOS74は揮発性の半導体メモリがバックアップ電源に接続されて構成されており、不揮発性でかつ高速の記憶手段として機能する。

【0056】

エンベデッド・コントローラ80は、図示しないキーボードのコントロールを行うと共に、内蔵されたパワー・マネージメント・コントローラによってゲートアレイ・ロジック76と協働して電源管理機能の一部を担う。

【0057】

図3には、メイン電池64Aの構成と、メイン電池64Aと他のコンポーネントとの接続状態が示されている。同図に示されるように、本第1実施形態に係るメイン電池64Aは、メイン電池64A全体の動作を司るCPU102、各種データを記憶するためのメモリ104、定格電圧4.2Vのリチウム・イオン電池を3本直列接続して構成されたバッテリ106、バッテリ106に対する充電量及び放電量を検出するための抵抗108、及び4つの外部端子T1、T2、T3、T4を含んで構成されている。なお、メモリ104としては、EPROM、EEPROM、フラッシュEEPROM等の読み書き可能で、かつ不揮発性のメモリを適用することができる。

【0058】

バッテリ106は一方の電極が外部端子T1に、他方の電極が抵抗108を介して外部端子T3に接続されている。また、CPU102にはメモリ104が接続されており、CPU102はメモリ104に対する各種データの書き込み及び読み出しを行うことができる。更に、CPU102は外部端子T2と外部端子T4に接続されており、CPU102は外部との各種情報の送受を行うことができる。また、抵抗108の両端子はCPU102に接続されており、CPU102はバッテリ106の他方の電極から外部端子T3に至る接続ラインの電流値に基づいてバッテリ106の充電量及び放電量を検出することができる。更に、CPU102にはバッテリ106の一方の電極が接続されており、CPU102はバッテリ106の電池電圧を検出することができる。

【0059】

一方、外部端子T1はPC12の内部回路120(メイン電池64A及びセカンド電池64B以外のコンポーネント)に含まれるDC/DCコンバータ66の入力端に接続されており、DC/DCコンバータ66にはメイン電池64Aからバッテリ106による電力が供給される。また、外部端子T2及び外部端子T4は内部回路120のエンベデッド・コントローラ80に接続されており、エンベデッド・コントローラ80はメイン電池64AのCPU102と各種情報の送受を行うことができる。更に、外部端子T3は内部回路120のグランド端子に接続されて接地されている。スマート・バッテリ仕様に準拠した電池を構成するには他にも回路、外部端子が必要であるが、これらは当業者には周知であり、また、本発明の要旨を構成するものではないので、本明細書中では説明を省略する。

【0060】

なお、セカンド電池64Bも図3に示されたメイン電池64Aと同様に構成されており、同図と同様にセカンド電池64Bの外部端子T1、T2、T3、T4はDC/DCコンバータ66、エンベデッド・コントローラ80、グランド端子に各々接続されている(図示省略)。

【0061】

また、本実施の形態に係るPC12にはバッテリパック収納部(図示省略)が設けられており、該バッテリパック収納部に上記メイン電池64A及びセカンド電池64Bは取り外し可能に装着されている。また、メイン電池64A及びセカンド電池64Bはバッテリパック収納部に装着された状態で、各々外部端子T1、T2、T3、T4を介してDC/DCコンバータ66、エンベデッド・コントローラ80、グランド端子に接続されている。

【0062】

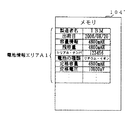

ここで、図4を参照して、本第1実施形態に係るメモリ104の記憶内容について説明する。同図に示すように、メモリ104には、一例として当該電池の「製造者名」、「出荷日」、「容量情報」、「残容量」、「シリアル・ナンバ」、「電池の種類」、「定格容量」、及び「定格電圧」の各々を示すデータを記憶するための電池情報エリアA1が予め定められており、製造者によって当該電池の出荷時に上記各データが対応するアドレスに記憶される。同図に示す例では、例えば、製造者名として‘IBM’が、出荷日として‘2000/08/20’が、各々出荷時に記憶される。なお、「容量情報」及び「残容量」は本発明に特に関係するものであり、製造者によって当該電池の出荷時に上記「定格容量」と同一のデータがデフォルト値として各々記憶される。ここで、「容量情報」はバッテリ106の総容量を示すものであり、本発明の容量情報に相当する。また、電池情報エリアA1には、本発明に関係するデータとして「電池電圧」及び「放電量」(共に図示省略)を記憶するための領域が設けられており、CPU102はバッテリ106の電池電圧を検出して上記「電池電圧」の値を常時更新していると共に、抵抗108を流れる電流の値に基づいてバッテリ106からの放電量を検出して上記「放電量」の値を常時更新している。

【0063】

また、メモリ104には補正情報エリアA2が予め定められており、該エリアA2には次の表1に示される、バッテリ106に関するサイクル数と容量の関係を示す補正情報が予め記憶されている。

【0064】

【表1】

【0065】

なお、本実施の形態における補正情報は、図10で示した40°Cにおけるサイクル特性に基づいて求めたものを適用している。

【0066】

一方、本第1実施形態に係るメイン電池64A及びセカンド電池64Bは、前述したようにスマート・バッテリ仕様に準拠したものであり、一例として表2に示すようなコマンド・セットが用意されている。

【0067】

【表2】

【0068】

例えば、本発明に特に関係する「残容量」についてはr(読み出し)のみが可能とされており、エンベデッド・コントローラ80によりメイン電池64A又はセカンド電池64BのCPU102に対してコマンドとして「0x0f」を送信することによってメモリ104からバッテリ106の残容量を読み出すことができる。

【0069】

また、例えば「容量情報」についてもr(読み出し)のみが可能とされており、エンベデッド・コントローラ80によりメイン電池64A又はセカンド電池64BのCPU102に対してコマンドとして「0x10」を送信することによってメモリ104からバッテリ106の容量情報を読み出すことができる。

【0070】

メイン電池64A及びセカンド電池64Bが請求項1〜請求項5記載の電源装置に、CPU102が請求項2〜請求項5記載の電源装置の計数手段及び補正手段に、メモリ104が請求項1〜請求項5記載の電源装置の情報記憶手段に、バッテリ106が本発明のバッテリに、各々相当する。

【0071】

なお、コンピュータ・システム10を構成するためには、図1及び図3に示した以外にも多くの電気回路が必要である。但し、これらは当業者には周知であり、また、本発明の要旨を構成するものではないので、本明細書中では説明を省略する。また、図面の錯綜を回避するため、図中の各ハードウェア・ブロック間の接続も一部しか図示していないことを付記しておく。

【0072】

次に、図5及び図6を参照して、メイン電池64A及びセカンド電池64BのCPU102によって実行される処理について説明する。なお、図5はCPU102によって実行される電池容量情報補正処理プログラムの流れを示すフローチャート、図6はCPU102によって実行されるサイクル数カウント処理プログラムの流れを示すフローチャートであり、各プログラムともメモリ104の所定領域に予め記憶されている。また、CPU102では、上記各プログラムを実行すると共に、メモリ104に記憶されている「容量情報」が示す総容量からバッテリ106の放電量を減じることによって残容量を得、該残容量をメモリ104の「残容量」に対応するアドレスに定期的に書き込む処理も行っている。

【0073】

図5のステップ200では初期設定として変数OFFSETに0(零)を代入すると共にサイクル数として0(零)を設定し、次のステップ202では後述するサイクル数カウント処理プログラムによってカウントされているサイクル数を取得する。

【0074】

次のステップ204では取得したサイクル数が増加したか否かを判定し、増加した場合(肯定判定の場合)はステップ206へ移行してメモリ104に記憶されている補正情報のこの時点のサイクル数に対応する容量値に変数OFFSETの値を加算することによって補正情報の容量値を補正し、その後にステップ208でメモリ104に記憶されている補正情報に基づいて容量情報を補正した後にステップ210へ移行する。なお、上記ステップ206の補正処理は、後述するステップ218において設定された変数OFFSETの値によって補正情報自身の誤差を補正する処理であるが、ステップ218の処理が一度も実施されていない場合には上記ステップ200の処理によって変数OFFSETには0(零)が代入されているので、補正情報の補正は行われない。また、上記ステップ208の補正処理は、上記ステップ202で取得したサイクル数に対応する容量(例えば、サイクル数が60である場合は4656mAH)にメモリ104に記憶されている容量情報を書き換えることによってなされる。

【0075】

一方、上記ステップ204において、取得したサイクル数は増加していないと判定された場合(否定判定された場合)には、上記ステップ206及びステップ208の処理を実行することなくステップ210へ移行する。

【0076】

ステップ210ではメモリ104に記憶されている「電池電圧」(図4では図示省略)を読み出し、次のステップ212において、読み出した電池電圧の値が該電池の容量が0(零)であるときに対応する所定電圧値(本実施の形態では9.0V)であるか否かを判定し、所定電圧値である場合(肯定判定の場合)はステップ214へ移行してメモリ104に記憶されている「放電量」(図4では図示省略)を読み出すことによってバッテリ106の放電量を取得し、次のステップ216にて、上記ステップ214で取得した放電量にメモリ104に記憶されている容量情報を書き換えることによって容量情報を学習する。

【0077】

次のステップ218では学習したデータ(上記ステップ214において取得した放電量)からメモリ104に記憶されている補正情報の対応する容量を減じた値を変数OFFSETに代入し、その後に上記ステップ202へ戻る。

【0078】

以上のステップ202乃至ステップ218の繰り返し処理によって、サイクル数が増加したときに、メモリ104に記憶されている補正情報自身の誤差が直前の学習で用いられた学習データ(放電量)に基づく変数OFFSETの値によって補正されると共に、該補正情報に基づいて容量情報が補正され、バッテリ106の電池電圧の値が残容量0に相当する所定電圧値となったときに、その時点で得られている放電量が正確な総容量であるものと見なして、メモリ104に記憶されている「容量情報」が該放電量に書き換えられて容量情報が学習されることになる。

【0079】

一方、上記ステップ212において電池電圧が上記所定電圧でないと判定された場合(否定判定された場合)、すなわち、バッテリ106の残容量が0(零)ではないと判定された場合には上記ステップ214〜ステップ218の処理を行うことなく上記ステップ202へ戻る。

【0080】

次に、図6を参照して、サイクル数カウント処理について説明する。

【0081】

同図のステップ250では充電量をクリアし、次のステップ252では抵抗108を流れる電流値に基づいて得られる充電量の積算を行い、次のステップ254ではメモリ104から容量情報を読み出すことによってバッテリ106の総容量を取得し、更に次のステップ256では、それまでに積算された充電量が上記ステップ254で取得した総容量に予め定められた係数(本実施の形態では0.9)を乗じた値以上であるか否かを判定し、肯定判定であった場合は1サイクル分充電が行われたものと見なしてステップ258に移行し、サイクル数を1インクリメントした後にステップ260で充電量をクリアし、その後に上記ステップ252へ戻る。

【0082】

一方、上記ステップ256で否定判定された場合には、上記ステップ258、ステップ260の処理を行うことなく上記ステップ252へ戻る。

【0083】

以上のステップ252〜ステップ260の繰り返し処理によって、各サイクル毎に充電量が積算されると共に、1サイクル分の充電が行われる毎にサイクル数がインクリメントされる。すなわち、本来、サイクル数は前述のように電池容量が0%から100%となるまで充電を行った後に、電池容量が0%となるまで放電した回数をいうが、本実施の形態では充電量の積算値に基づいて電池容量が0%から100%となるまで充電を行ったと見なされた場合に1サイクルとしている。このとき、充電量の積算値によって電池容量が0%から100%になったと見なすことができることの根拠は前述の通りである。

【0084】

なお、PC12の内部回路120においてメイン電池64A及びセカンド電池64Bの残容量を取得する場合には、エンベデッド・コントローラ80からメイン電池64A又はセカンド電池64BのCPU102に対してコマンドとして「0x0f」を送信する。これによってメモリ104からバッテリ106の残容量を示す値を読み出すことができる。

【0085】

以上詳細に説明したように、本第1実施形態に係るメイン電池及びセカンド電池では、バッテリのサイクル数に対する総容量を示し、かつバッテリの総容量を示す容量情報を補正するための補正情報を記憶しているので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、上記補正情報を用いることによって、バッテリのサイクル数に基づき上記容量情報を的確に補正することができる。

【0086】

また、本第1実施形態に係るメイン電池及びセカンド電池では、バッテリの充電量を検出し、該充電量についてバッテリの総容量に所定係数を乗じた容量を単位サイクルとしてバッテリのサイクル数を計数しているので、バッテリの容量が零又は零近傍にならない場合であっても、簡易かつ高精度にサイクル数を計数することができる。

【0087】

更に、本第1実施形態に係るメイン電池及びセカンド電池では、バッテリの電池電圧の値がバッテリの容量が零であると見なせる所定電圧値に達するまでのバッテリの放電量を本発明の総放電量と略同一であるものと見なして、該放電量に容量情報を置き換えることによって容量情報を学習すると共に、バッテリの容量が零又は零近傍になったときの補正情報に示される総容量を、上記バッテリの放電量に基づいて補正しているので、容量情報を、より正確なものとすることができると共に、補正情報自身の誤差も補正することができる。

【0088】

なお、本第1実施形態では、メイン電池64A及びセカンド電池64Bに内蔵されたCPU102によって容量情報や補正情報の補正を行う場合について説明したが、本発明はこれに限定されるものではなく、メイン電池64A及びセカンド電池64Bの外部に設けられたコントローラ、例えば図3におけるエンベデッド・コントローラ80によって、各電池の容量情報や補正情報の補正を行う形態とすることもできる。

【0089】

この場合は、補正情報は必ずしも電池内部に記憶しておく必要はなく、エンベデッド・コントローラ80によって読み出し可能なメモリを内部回路120に設けておき、該メモリに記憶しておく形態とすることもできる。

【0090】

なお、この場合はエンベデッド・コントローラ80において、図5及び図6に示されるフローチャートの処理と同様の処理が行われる。この場合、エンベデッド・コントローラ80が請求項6〜請求項9記載の発明の計数手段及び補正手段に相当することになる。この場合にも、本第1実施形態と同様の効果を奏することができる。

【0091】

また、本第1実施形態では、製造者名、出荷日等の電池に関する情報(図4の電池情報エリアA1に対応する情報)を記憶するメモリと補正情報を記憶するメモリとを同一のメモリ104とした場合について説明したが、本発明はこれに限定されるものではなく、メモリ104以外のメモリを備えておき、該メモリに補正情報を記憶する形態とすることもできることは言うまでもない。

【0092】

〔第2実施形態〕

上記第1実施形態では、CPUが内蔵されており、インテリジェント電池として構成されたメイン電池64A及びセカンド電池64Bに対して本発明を適用した場合の形態例について説明したが、本第2実施形態は、CPUが内蔵されていない電池を対象に本発明を実施する場合の一形態について説明する。なお、各電池の構成と、各電池と他のコンポーネントとの接続状態以外の構成については、上記第1実施形態と同様であるので、ここでの説明は省略する。

【0093】

図7には、本第2実施形態に係るメイン電池64A’の構成と、メイン電池64A’と他のコンポーネントとの接続状態が示されている。なお、同図における図3と同様の部分については図3と同一の符号を付して、その説明を省略する。

【0094】

同図に示されるように、本第2実施形態に係るメイン電池64A’は、上記第1実施形態に係るメイン電池64Aに比較して、CPU102及び抵抗108が備えられておらず、メモリ104’が直接に外部端子T2と外部端子T4に接続されている点が相違している。

【0095】

このように構成されたメイン電池64A’の外部端子T1は、PC12の内部回路120’内においてバッテリ106の充放電量を検出するための抵抗110を介してDC/DCコンバータ66の入力端に接続されており、DC/DCコンバータ66にはメイン電池64A’からバッテリ106による電力が供給される。また、抵抗110の両端子はエンベデッド・コントローラ80に接続されており、エンベデッド・コントローラ80はバッテリ106からDC/DCコンバータ66に至る電力供給ラインの電流値に基づいてバッテリ106の充放電量を検出することができると共に、抵抗110の外部端子T1側の端子の電位に基づいてバッテリ106の電池電圧を検出することができる。

【0096】

一方、外部端子T2及び外部端子T4は内部回路120’のエンベデッド・コントローラ80に接続されており、エンベデッド・コントローラ80はメモリ104に対する各種データの書き込みや読み出しを行うことができる。更に、外部端子T3は内部回路120’のグランド端子に接続されて接地されている。

【0097】

なお、セカンド電池も図7に示されたメイン電池64A’と同様に構成されており、同図と同様にセカンド電池の外部端子T1、T2、T3、T4はDC/DCコンバータ66、エンベデッド・コントローラ80、グランド端子に各々接続されている(図示省略)。

【0098】

図8には、本第2実施形態におけるメモリ104’の記憶内容が示されている。同図に示すように、メモリ104’は上記第1実施形態におけるメモリ104に設けられている電池情報エリアA1は設けられているが、補正情報エリアA2が設けられていない点がメモリ104と相違している。そして、本第2実施形態ではエンベデッド・コントローラ80内の図略のメモリに上記第1実施形態と同様の補正情報(表1も参照)が記憶されている。

【0099】

また、電池情報エリアA1には、本発明に関係するデータとして「電池電圧」及び「放電量」(共に図示省略)を記憶するための領域が設けられており、エンベデッド・コントローラ80はバッテリ106の電池電圧を検出して上記「電池電圧」の値を常時更新していると共に、抵抗110を流れる電流の値に基づいてバッテリ106からの放電量を検出して上記「放電量」の値を常時更新している。

【0100】

メイン電池64A’及びセカンド電池が請求項6〜請求項19記載の電源装置に、エンベデッド・コントローラ80が請求項6〜請求項9記載の電源容量情報補正装置の計数手段及び補正手段に、エンベデッド・コントローラ80に内蔵された図略のメモリが請求項6〜請求項9記載の電源容量情報補正装置の補正情報記憶手段に、各々相当する。

【0101】

本第2実施形態に係るエンベデッド・コントローラ80は、図5及び図6に示される電池容量情報補正処理プログラム及びサイクル数カウント処理プログラムをメモリ104’をメモリ104に見立てて第1実施形態と同様に実行する。但し、本第2実施形態では、補正情報がエンベデッド・コントローラ80に内蔵された図略のメモリに記憶されているので、補正情報をアクセスする際には該メモリをアクセスすることになる。

【0102】

このエンベデッド・コントローラ80の作用によって、本第2実施形態に係るPC12では、バッテリのサイクル数に対する総容量を示し、かつバッテリの総容量を示す容量情報を補正するための補正情報を記憶しているので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、上記補正情報を用いることによって、バッテリのサイクル数に基づき上記容量情報を的確に補正することができる。

【0103】

また、本第2実施形態に係るPC12では、バッテリの充電量を検出し、該充電量についてバッテリの総容量に所定係数を乗じた容量を単位サイクルとしてバッテリのサイクル数を計数しているので、バッテリの容量が零又は零近傍にならない場合であっても、簡易かつ高精度にサイクル数を計数することができる。

【0104】

更に、本第2実施形態に係るPC12では、バッテリの電池電圧の値がバッテリの容量が零であると見なせる所定電圧値に達するまでのバッテリの放電量を本発明の総放電量と略同一であるものと見なして、該放電量に容量情報を置き換えることによって容量情報を学習すると共に、バッテリの容量が零又は零近傍になったときの補正情報に示される総容量を、上記バッテリの放電量に基づいて補正しているので、容量情報を、より正確なものとすることができると共に、補正情報自身の誤差も補正することができる。

【0105】

なお、上記各実施形態では、各電池の充電量の積算値に基づいて対応する電池のサイクル数を計数する場合について説明したが、本発明はこれに限定されるものではなく、各電池の放電量の積算値に基づいて対応する電池のサイクル数を計数する形態とすることもできる。この場合も上記各実施形態と同様の効果を奏することができる。

【0106】

また、上記各実施形態では、所定温度(実施形態では40°C)における補正情報を記憶しておき、該補正情報に基づいて容量情報を補正する場合について説明したが、本発明はこれに限定されるものではなく、サーミスタ等の温度検知手段を備えておくと共に、複数の温度における補正情報を記憶しておき、実際に電池が使用される環境温度に最も近い温度の補正情報に基づいて容量情報を補正する形態とすることもできる。この場合は、上記各実施形態に比較して、より高精度に容量情報を補正することができる。

【0107】

ところで、上述したように各実施形態による電源容量情報補正方法は、種々のプログラミング言語を用いてプログラムにすることができる。

【0108】

このプログラムは、コンピュータ読み込み可能な記録媒体に記録することができる。記録媒体には、ROM(Read Only Memory)、EEPROM(Electricaly Erasable Programmable Read Only Memory)、及びフラッシュEEPROM(Flash EEPROM)等の、コンピュータ・システムに実装される記憶装置、フロッピー・ディスク(FD)、CD−ROM(コンパクト・ディスクを用いた読み取り専用メモリ)、及びMO(光磁気)ディスク等の可搬記録媒体、あるいはネットワークに接続されたサーバ・コンピュータ等に設けられた外部記憶装置等を用いることができる。

【0109】

記録媒体に記録されたプログラムは、次のようにしてコンピュータ内に取り込む。上記プログラムを記録した記録媒体が可搬記録媒体の場合、駆動装置に装填して、その可搬記録媒体に記録されているプログラムを読み込む。読み込んだプログラムは、メイン・メモリに格納する。

【0110】

記録媒体がネットワーク上の外部記憶装置である場合には、ネットワーク接続装置を介してその外部記憶装置に記録されているプログラムをダウン・ロードする。ダウン・ロードしたプログラムは、メイン・メモリに格納する。

【0111】

【発明の効果】

以上説明したように本発明に係る電源装置によれば、バッテリのサイクル数に対する総容量を示し、かつバッテリの総容量を示す容量情報を補正するための補正情報を記憶しているので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、上記補正情報を用いることによって、バッテリのサイクル数に基づき上記容量情報を的確に補正することができる、という優れた効果を有する。

【0112】

また、本発明に係る電源容量情報補正装置及び電源容量情報補正方法によれば、本発明に係る電源装置と同様に作用するので、電池容量が零又は零近傍の所定容量となることがないような場合であっても、バッテリのサイクル数に基づいて容量情報を的確に補正することができる、という優れた効果を有する。

【0113】

更に、本発明に係るコンピュータによれば、本発明に係る電源容量情報補正方法を適用しているので、電源装置の容量情報を的確に補正することができる、という優れた効果を有する。

【図面の簡単な説明】

【図1】 実施の形態に係るコンピュータ・システムの概略構成を示すブロック図である。

【図2】 ノートブック型PCの外観を示す斜視図である。

【図3】 第1実施形態に係るノートブック型PCのメイン電池の構成と、メイン電池と他のコンポーネントとの接続状態を示すブロック図である。

【図4】 第1実施形態に係るメモリ104の記憶内容の一例を示す模式図である。

【図5】 第1実施形態に係るメイン電池及びセカンド電池のCPUによって実行される電池容量情報補正処理プログラムの流れを示すフローチャートである。

【図6】 第1実施形態に係るメイン電池及びセカンド電池のCPUによって実行されるサイクル数カウント処理プログラムの流れを示すフローチャートである。

【図7】 第2実施形態に係るノートブック型PCのメイン電池の構成と、メイン電池と他のコンポーネントとの接続状態を示すブロック図である。

【図8】 第2実施形態に係るメモリ104’の記憶内容の一例を示す模式図である。

【図9】 本発明の有効性の説明に供するグラフである。

【図10】 従来技術の問題点の説明に供するグラフである。

【図11】 従来技術の説明に供するグラフである。

【符号の説明】

10 コンピュータ・システム

54 電源回路

64A、64A’ メイン電池

64B セカンド電池

80 エンベデッド・コントローラ

102 CPU

104 メモリ

104’ メモリ

106 バッテリ

108 抵抗

110 抵抗

120、120’ 内部回路

Claims (20)

- プロセッサとバッテリィを含む電源装置において前記バッテリィの総容量を補正する方法であって、

前記バッテリィの現在の総容量値と、充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報とを記憶するメモリを提供するステップと、

前記プロセッサが現在の前記サイクル数をカウントするステップと、

前記プロセッサが前記カウントしたサイクル数に対応する前記補正総容量値で前記現在の総容量値を補正するステップと、

前記プロセッサが前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正するステップと

を有する方法。 - 前記現在のサイクル数をカウントするステップが、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントするステップを有し、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項1に記載の方法。

- 前記メモリに前記補正総容量値が環境温度ごとに記憶され、前記プロセッサは実測した環境温度と前記カウントしたサイクル数とに対応する前記補正総容量値で前記現在の総容量値を補正する請求項1または請求項2に記載の方法。

- 前記電源装置の製造時に前記現在の総容量値として前記メモリに前記バッテリィの定格容量が記憶される請求項1から請求項3のいずれかに記載の方法。

- コントローラがバッテリィの総容量を補正する方法であって、

前記バッテリィの現在の総容量値と、充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報を記憶するメモリを提供するステップと、

前記コントローラが現在の前記サイクル数をカウントするステップと、

前記コントローラが前記カウントしたサイクル数に対応する前記補正総容量値で前記現在の総容量値を補正するステップと、

前記コントローラが前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正するステップと

を有する方法。 - 前記サイクル数をカウントするステップが、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントするステップを有し、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項5に記載の方法。

- 前記メモリに前記補正総容量値が環境温度ごとに記憶され、前記プロセッサは実測した環境温度と前記カウントしたサイクル数とに対応する前記補正総容量値で前記現在の総容量値を補正する請求項5または請求項6に記載の方法。

- バッテリィと、

前記バッテリィの現在の総容量値と、充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報を記憶するメモリと、

現在の前記サイクル数をカウントし、前記サイクル数に対応する前記補正総容量値で前記現在の総容量値を補正し、前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正するプロセッサと

を有する電池パック。 - 前記プロセッサは、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントし、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項8に記載の電池パック。

- 環境温度を測定する温度センサを有し、前記メモリに前記補正総容量値が環境温度ごとに記憶され、前記プロセッサは前記温度センサが測定した環境温度と前記カウントしたサイクル数とに対応する前記補正総容量値で前記現在の総容量値を補正する請求項8または請求項9に記載の電池パック。

- バッテリィと、該バッテリィの充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報と現在の総容量値とを記憶するメモリと、プロセッサとを有する電源装置において、前記プロセッサに、

現在の前記サイクル数をカウントするステップと、

前記カウントしたサイクル数に対応する前記補正総容量値で前記現在の総容量値を補正するステップと、

前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正するステップと

を有する処理を実行させるコンピュータ・プログラムを記録した記録媒体。 - 前記サイクル数をカウントするステップが、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントするステップを有し、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項11に記載の記録媒体。

- 前記メモリに前記補正総容量値が環境温度ごとに記憶されており、実測した環境温度と前記カウントしたサイクル数とに対応する前記補正総容量値で前記現在の総容量値を補正するステップを有する請求項11または請求項12に記載の記録媒体。

- 請求項11から請求項13のいずれかに記載された記録媒体を有する電源装置。

- バッテリィと該バッテリィの現在の総容量値を記憶するメモリとを備える電池パックが装着され、前記バッテリィの充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報を記憶するメモリを含むコンピュータに、

現在の前記サイクル数をカウントするステップと、

前記カウントしたサイクル数に対応する前記補正総容量値で前記現在の総容量値を補正するステップと、

前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正するステップと

を有する処理を実行させるコンピュータ・プログラムを記録した記録媒体。 - 前記サイクル数をカウントするステップが、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントするステップを有し、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項15に記載の記録媒体。

- 請求項15または請求項16に記載された記録媒体を有するコンピュータ。

- バッテリィと、

前記バッテリィの現在の総容量値を記憶する第1のメモリと、

前記バッテリィの充電または放電のサイクル数と該サイクル数に対応する補正総容量値を含む補正情報を記憶する第2のメモリと、

現在の前記サイクル数をカウントするカウント手段と、

前記カウントしたサイクル数に対応する前記補正総容量値で前記現在の総容量値を補正する総容量補正手段と、

前記バッテリィの電圧が前記現在の総容量値を補正する容量学習ができる程度まで低下したときの放電量を取得して該放電量で前記補正総容量値を補正する補正情報補正手段と

を有する電源システム。 - 前記カウント手段が、100%未満の放電をしたときの充電量または放電量の積算値が前記現在の総容量値または前記現在の総容量値に所定の係数を乗じた値に到達したときに1サイクルをカウントし、前記所定の係数が前記積算値によりカウントしたサイクル数を100%放電のサイクル数に関連付ける係数である請求項18に記載の電源システム。

- 温度検出手段を有し、前記第2のメモリに前記補正総容量値が環境温度ごとに記憶されており、前記総容量補正手段は前記温度検出手段が測定した環境温度と前記カウントしたサイクル数とに対応する前記補正総容量値で前記現在の総容量値を補正する請求項18または請求項19に記載の電源システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000101117A JP4875235B2 (ja) | 2000-04-03 | 2000-04-03 | 電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ |

| US09/824,256 US6910143B2 (en) | 2000-04-03 | 2001-04-02 | Electronic power unit with a battery and a compensator for calculating the actual charge capacity of the battery |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000101117A JP4875235B2 (ja) | 2000-04-03 | 2000-04-03 | 電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001283929A JP2001283929A (ja) | 2001-10-12 |

| JP4875235B2 true JP4875235B2 (ja) | 2012-02-15 |

Family

ID=18615224

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000101117A Expired - Fee Related JP4875235B2 (ja) | 2000-04-03 | 2000-04-03 | 電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6910143B2 (ja) |

| JP (1) | JP4875235B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3807965B2 (ja) * | 2001-09-19 | 2006-08-09 | インターナショナル・ビジネス・マシーンズ・コーポレーション | インテリジェント電池、電気機器、コンピュータ装置及び電池の劣化度を求める方法 |

| US20050104977A1 (en) * | 2002-01-11 | 2005-05-19 | Nikon Corporation | Digital camera |

| CN100438603C (zh) * | 2002-01-31 | 2008-11-26 | 株式会社尼康 | 数码相机 |

| US20050151858A1 (en) * | 2002-02-18 | 2005-07-14 | Nikon Corporation | Digital camera |

| JP4100353B2 (ja) * | 2003-02-19 | 2008-06-11 | 松下電器産業株式会社 | 複数ルータ間調停方法、ルータ優先度計算装置及びルータ装置 |

| JP4104476B2 (ja) * | 2003-03-25 | 2008-06-18 | 三洋電機株式会社 | リチウム二次電池の使用方法及びリチウム二次電池 |

| US7482784B2 (en) * | 2003-07-15 | 2009-01-27 | Panasonic Corporation | Degradation judgment circuit for secondary battery |

| US7363525B2 (en) * | 2004-10-07 | 2008-04-22 | Cisco Technology, Inc. | Bidirectional inline power port |

| JP5279199B2 (ja) * | 2007-05-23 | 2013-09-04 | キヤノン株式会社 | 充電装置及び充電制御方法 |

| JP5335207B2 (ja) * | 2007-07-05 | 2013-11-06 | キヤノン株式会社 | 電子機器 |

| US9806606B2 (en) * | 2009-08-11 | 2017-10-31 | Lenovo (Singapore) Pte. Ltd. | Multi-modal battery pack |

| US20120198262A1 (en) * | 2011-01-31 | 2012-08-02 | Hand Held Products, Inc. | Mobile device and method for extending battery life |

| US10234512B2 (en) | 2011-06-11 | 2019-03-19 | Sendyne Corporation | Current-based cell modeling |

| JP6344709B2 (ja) | 2013-11-12 | 2018-06-20 | パナソニックIpマネジメント株式会社 | 電池パック、および、この電池パックを備える電気機器 |

| US10367237B2 (en) | 2015-02-06 | 2019-07-30 | Hewlett-Packard Development Company, L.P. | Battery calibration |

| EP3109654A1 (de) * | 2015-06-24 | 2016-12-28 | HILTI Aktiengesellschaft | Verfahren zum ermitteln eines ladungsspeichervermögens eines akkus |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5444378A (en) * | 1988-07-13 | 1995-08-22 | Electronic Development Inc. | Battery state of charge monitor |

| JP2761327B2 (ja) * | 1991-07-08 | 1998-06-04 | 本田技研工業株式会社 | バッテリの残容量検出装置及び残容量検出方法 |

| US5712795A (en) * | 1995-10-02 | 1998-01-27 | Alaris Medical Systems, Inc. | Power management system |

| KR980012672A (ko) * | 1996-07-16 | 1998-04-30 | 손욱 | 지능형 배터리 장치 |

| JPH1138106A (ja) * | 1997-07-16 | 1999-02-12 | Oki Electric Ind Co Ltd | 電子装置 |

| JPH11329512A (ja) * | 1998-05-20 | 1999-11-30 | Fuji Photo Film Co Ltd | 二次電池の容量劣化判断方法およびその判断装置 |

| JPH11344544A (ja) * | 1998-06-03 | 1999-12-14 | Fuji Film Celltec Kk | バッテリーパックの電池容量測定方法 |

| US6307349B1 (en) * | 2000-02-24 | 2001-10-23 | Intermec Ip Corp. | Battery pack having memory |

-

2000

- 2000-04-03 JP JP2000101117A patent/JP4875235B2/ja not_active Expired - Fee Related

-

2001

- 2001-04-02 US US09/824,256 patent/US6910143B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20020144160A1 (en) | 2002-10-03 |

| JP2001283929A (ja) | 2001-10-12 |

| US6910143B2 (en) | 2005-06-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4126144B2 (ja) | 充電システム、インテリジェント電池、および充電方法 | |

| JP4875235B2 (ja) | 電源装置、電源容量情報補正装置、電源容量情報補正方法及びコンピュータ | |

| JP3807965B2 (ja) | インテリジェント電池、電気機器、コンピュータ装置及び電池の劣化度を求める方法 | |

| US6842708B2 (en) | Method and apparatus for determining battery life | |

| US7663374B2 (en) | Electrical apparatus, computer system, intelligent battery, battery diagnosis method, batter-state display method, and program | |

| JP3611316B2 (ja) | 電気機器、コンピュータ装置、電源切換装置、および電源切換方法 | |

| US6424123B1 (en) | Battery charging system and charge control apparatus | |

| US8339095B2 (en) | Battery pack, charging device, and electronic device | |

| JP3854175B2 (ja) | 電気機器、コンピュータ装置、コントローラ、電池切換方法、およびプログラム | |

| JP4068275B2 (ja) | 充電制御方法及びコンピュータ | |

| JP3718767B2 (ja) | 電気機器、コンピュータ装置、予備充電状態表示方法、およびユーティリティプログラム | |

| JP2012226410A (ja) | バッテリ制御システム、バッテリモジュール、及び電子機器 | |

| JP3900469B2 (ja) | 電気機器、コンピュータ装置、インテリジェント電池、および電池の制御方法 | |

| JP3785377B2 (ja) | 電気機器、コンピュータ装置、インテリジェント電池、およびacアダプタの確認方法 | |

| US6829545B2 (en) | Method of calculating capacity of intelligent battery, intelligent battery and portable electronic device | |

| JP3678185B2 (ja) | 電気機器、コンピュータ装置、インテリジェント電池、電池診断方法、プログラム、および記憶媒体 | |

| US6820205B2 (en) | Electric power unit with a battery and a memory for recording the date of first use of the battery |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A625 | Written request for application examination (by other person) |

Free format text: JAPANESE INTERMEDIATE CODE: A625 Effective date: 20070322 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20070405 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20090717 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20090806 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090903 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101026 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101029 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20101126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111122 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111125 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141202 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141202 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |