JP4792125B2 - 情報記録再生装置 - Google Patents

情報記録再生装置 Download PDFInfo

- Publication number

- JP4792125B2 JP4792125B2 JP2010505229A JP2010505229A JP4792125B2 JP 4792125 B2 JP4792125 B2 JP 4792125B2 JP 2010505229 A JP2010505229 A JP 2010505229A JP 2010505229 A JP2010505229 A JP 2010505229A JP 4792125 B2 JP4792125 B2 JP 4792125B2

- Authority

- JP

- Japan

- Prior art keywords

- recording

- recording layer

- layer

- region

- electrode layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B11/00—Recording on or reproducing from the same record carrier wherein for these two operations the methods are covered by different main groups of groups G11B3/00 - G11B7/00 or by different subgroups of group G11B9/00; Record carriers therefor

- G11B11/002—Recording on or reproducing from the same record carrier wherein for these two operations the methods are covered by different main groups of groups G11B3/00 - G11B7/00 or by different subgroups of group G11B9/00; Record carriers therefor using recording by perturbation of the physical or electrical structure

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B9/00—Recording or reproducing using a method not covered by one of the main groups G11B3/00 - G11B7/00; Record carriers therefor

- G11B9/04—Recording or reproducing using a method not covered by one of the main groups G11B3/00 - G11B7/00; Record carriers therefor using record carriers having variable electric resistance; Record carriers therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B9/00—Recording or reproducing using a method not covered by one of the main groups G11B3/00 - G11B7/00; Record carriers therefor

- G11B9/12—Recording or reproducing using a method not covered by one of the main groups G11B3/00 - G11B7/00; Record carriers therefor using near-field interactions; Record carriers therefor

- G11B9/14—Recording or reproducing using a method not covered by one of the main groups G11B3/00 - G11B7/00; Record carriers therefor using near-field interactions; Record carriers therefor using microscopic probe means, i.e. recording or reproducing by means directly associated with the tip of a microscopic electrical probe as used in Scanning Tunneling Microscopy [STM] or Atomic Force Microscopy [AFM] for inducing physical or electrical perturbations in a recording medium; Record carriers or media specially adapted for such transducing of information

- G11B9/1463—Record carriers for recording or reproduction involving the use of microscopic probe means

- G11B9/149—Record carriers for recording or reproduction involving the use of microscopic probe means characterised by the memorising material or structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5685—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using storage elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/003—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B11/00—Recording on or reproducing from the same record carrier wherein for these two operations the methods are covered by different main groups of groups G11B3/00 - G11B7/00 or by different subgroups of group G11B9/00; Record carriers therefor

- G11B11/08—Recording on or reproducing from the same record carrier wherein for these two operations the methods are covered by different main groups of groups G11B3/00 - G11B7/00 or by different subgroups of group G11B9/00; Record carriers therefor using recording by electric charge or by variation of electric resistance or capacitance

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/565—Multilevel memory comprising elements in triple well structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/31—Material having complex metal oxide, e.g. perovskite structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/50—Resistive cell structure aspects

- G11C2213/53—Structure wherein the resistive material being in a transistor, e.g. gate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/50—Resistive cell structure aspects

- G11C2213/56—Structure including two electrodes, a memory active layer and a so called passive or source or reservoir layer which is NOT an electrode, wherein the passive or source or reservoir layer is a source of ions which migrate afterwards in the memory active layer to be only trapped there, to form conductive filaments there or to react with the material of the memory active layer in redox way

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/75—Array having a NAND structure comprising, for example, memory cells in series or memory elements in series, a memory element being a memory cell in parallel with an access transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/78—Array wherein the memory cells of a group share an access device, all the memory cells of the group having a common electrode and the access device being not part of a word line or a bit line driver

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Nanotechnology (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Semiconductor Memories (AREA)

Description

しかし、抵抗変化型の新たな記録材料を用いた新規情報記録媒体は実現されていないのが現状である。その理由として、メモリスイッチングにおける繰り返し劣化が大きいこと、及び、各抵抗状態の熱安定性が低いこと、さらに、ポストアニール処理による記録層/電極層の耐熱性(プロセス耐性)が問題となっている。

本発明の例に係わる情報記録再生装置は、ダイオードと、ダイオードと共に積層構造を構成し、典型元素と遷移元素を少なくとも1種類ずつ含み、典型元素の移動により異なる電気抵抗率の2つの状態が記録される記録層と、記録層の一端に配置され、記録層に電圧又は電流を与える電極層とを備える。記録層は、電極層に接する第1領域と、第1領域以外の第2領域とを有し、第1及び第2領域は、組成が相違しており、第1領域は、第2領域内の典型元素の濃度よりも高い濃度の典型元素を添加物として含んでいる。

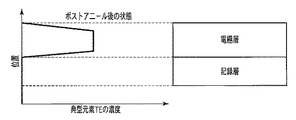

新規固体メモリを実用化するためには、耐熱性が良好な記録媒体又は記録素子を開発することが必要である。ここで、耐熱性を良好にするとは、記録媒体又は記録素子を形成した後にポストアニール処理(熱処理)を行っても、記録層内の拡散イオンとしての典型元素が電極層に拡散しないこと、即ち、ポストアニール処理の前後において記録層内の拡散イオンとしての典型元素の濃度を一定に保つこと、を意味する。

本発明に用いられる記録層の記録動作の基本原理について説明する。

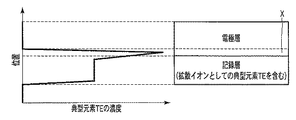

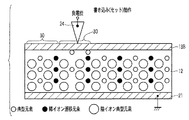

図1は、本発明の前提となる記録部の構造を示している。

11は電極層、12は記録層、13Aは電極層(又は保護層)、14はメタル層である。大きな白丸は、陰イオン典型元素(酸素イオン)、小さな黒丸は、陽イオン遷移元素(母体陽イオン)Y、小さな白丸は、拡散イオンとしての典型元素(陽イオン)Xである。

Mは、Ti, Zr, Hf, V, Nb, Ta のグループから選択される少なくとも1種類の元素である。Nは、窒素である。

Mは、Ti, V, Cr, Mn, Fe, Co, Ni, Cu, Zr, Nb, Mo, Ru, Rh, Pd, Ag, Hf, Ta, W, Re, Ir, Os, Pt のグループから選択される少なくとも1種類の元素である。モル比xは、1≦x≦4を満たすものとする。

Aは、La, K, Ca, Sr, Ba, Ln(Lanthanide) のグループから選択される少なくとも1種類の元素である。

Aは、K, Ca, Sr, Ba, Ln(Lanthanide) のグループから選択される少なくとも1種類の元素である。

記録層は、拡散イオンとしての典型元素(typical element)TEを含み、典型元素TEの移動により異なる電気抵抗率の2以上の状態をとる。記録層は、例えば、ZnMn2O4である。

図3は、ポストアニール処理前の拡散イオンとしての典型元素TEの濃度分布であり、図4は、ポストアニール処理後の拡散イオンとしての典型元素TEの濃度分布である。

記録層は、拡散イオンとしての典型元素TEを含み、典型元素TEの移動により異なる電気抵抗率の2以上の状態をとる。記録層は、例えば、ZnMn2O4である。

第三の基本構造が上述の第一及び第二の基本構造と異なる点は、記録層の一端及び他端にそれぞれ電極層が配置されている点にある。

次に、最良と思われるいくつかの実施形態について説明する。

以下では、本発明の例を、プローブ型固体メモリに適用した場合とクロスポイント型固体メモリに適用した場合の2つについて説明する。

A. 構造

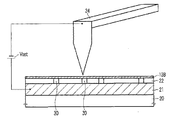

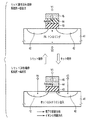

図7及び図8は、本発明の例に係わるプローブ型固体メモリを示している。

図7及び図8のプローブ型固体メモリの記録/再生動作について説明する。

記録部(記録媒体)22は、半導体チップ20上の電極層21上に形成される。記録部22は、保護層13Bにより覆われる。

再生動作に関しては、電圧パルスを記録層12の記録単位30に流し、記録層12の記録単位30の抵抗値を検出することにより行う。但し、電圧パルスは、記録層12の記録単位30を構成する材料が相変化を起こさない程度の微小な値とする。

このようなプローブ型固体メモリによれば、現在のハードディスクやフラッシュメモリよりも高記録密度及び低消費電力を実現できる。

A. 構造

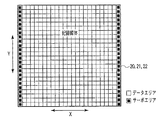

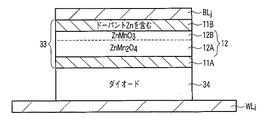

図12は、本発明の例に係わるクロスポイント型固体メモリを示している。

ワード線WLi上にダイオード34が形成され、ダイオード34上にメモリセル33が形成される。メモリセル33は、電極層11A/記録層12/電極層11Bのスタック構造を有する。メモリセル33上にビット線BLjが形成される。

ワード線WLi上にダイオード34が形成され、ダイオード34上にメモリセル33が形成される。メモリセル33は、電極層11A/記録層12/電極層11Bのスタック構造を有する。さらに、記録層12は、電極層11Bに接する領域に存在する組成相違記録層12Bとその他の領域に存在する記録層本体12Aとから構成される。メモリセル33上にビット線BLjが形成される。

第三例は、第一例と第二例とを組み合わせた構造を有する。

第四例は、第一例の応用例であり、その特徴は、記録層12の両端に存在する電極層11A,11B内に、添加物(ドーパント)として、記録層12内の拡散イオンとしての典型元素を含ませた点にある。

第五例は、第二例の応用例であり、その特徴は、記録層本体12Aの両端にそれぞれ組成相違記録層12A,12Bを配置した点にある。

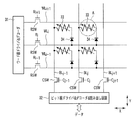

図12、図13及び図16を用いて記録/再生動作を説明する。

ここでは、点線Aで囲んだメモリセル33を選択し、これについて記録/再生動作を実行するものとする。

このようなクロスポイント型固体メモリによれば、現在のハードディスクやフラッシュメモリよりも高記録密度及び低消費電力を実現できる。

本実施形態では、プローブ型固体メモリとクロスポイント型固体メモリの2つについて説明したが、本発明の例で提案する材料及び原理を、現在のハードディスクやDVDなどの記録媒体に適用することも可能である。

(1) 構造

本発明の例は、フラッシュメモリに適用することも可能である。

図21を用いて基本動作について説明する。

セット(書き込み)動作は、コントロールゲート電極45に電位V1を与え、半導体基板41に電位V2を与えることにより実行する。

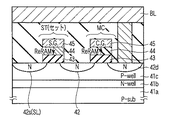

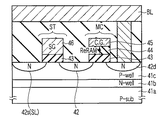

図22は、NANDセルユニットの回路図を示している。図23は、本発明の例に係るNANDセルユニットの構造を示している。

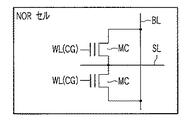

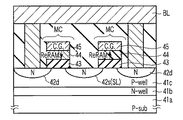

図26は、NORセルユニットの回路図を示している。図27は、本発明の例に係るNORセルユニットの構造を示している。

図28は、2トラセルユニットの回路図を示している。図29は、本発明の例に係る2トラセルユニットの構造を示している。

本発明によれば、高記録密度及び低消費電力の不揮発性の情報記録再生装置を実現できる。

Claims (9)

- ダイオードと、前記ダイオードと共に積層構造を構成し、典型元素と遷移元素を少なくとも1種類ずつ含み、前記典型元素の移動により異なる電気抵抗率の2つの状態が記録される記録層と、前記記録層の一端に配置され、前記記録層に電圧又は電流を与える電極層とを具備し、

前記電極層は、前記記録層に接する第1領域を有し、前記記録層は、前記電極層に接する第2領域を有し、前記第1及び第2領域は、対向し、前記第1領域は、前記第2領域内の前記典型元素の濃度よりも高い濃度の前記典型元素を添加物として含んでいる

ことを特徴とする情報記録再生装置。 - ダイオードと、前記ダイオードと共に積層構造を構成し、典型元素と遷移元素を少なくとも1種類ずつ含み、前記典型元素の移動により異なる電気抵抗率の2つの状態が記録される記録層と、前記記録層の一端に配置され、前記記録層に電圧又は電流を与える電極層とを具備し、

前記記録層は、前記電極層に接する第1領域と、前記第1領域以外の第2領域とを有し、前記第1及び第2領域は、組成が相違しており、前記第1領域は、前記第2領域内の前記典型元素の濃度よりも高い濃度の前記典型元素を添加物として含んでいる

ことを特徴とする情報記録再生装置。 - 前記典型元素は、Zn、Cd、Hg、Al、Ga、In、Ti、Be、Mg、Caのグループから選択される元素であることを特徴とする請求項1又は2に記載の情報記録再生装置。

- 前記電極層は、Ti、Zr、Hf、V、Nb、Ta、Cr、Mo、W、Ru、Ni、Pd、Pt、Cu、Ag、Auのグループから選択される元素を主成分とすることを特徴とする請求項1又は2に記載の情報記録再生装置。

- 前記電極層は、20nm以下の厚さを有することを特徴とする請求項1又は2に記載の情報記録再生装置。

- 前記記録層は、

化学式: AxMyX4(0.1≦x≦2.2、1.5≦y≦2)

但し、Aは、Zn、Cd、Hgのグループから選択される典型元素、Mは、Cu、Mo、W、Mn、Tc、Re、Feのグループから選択される遷移元素、Xは、O、Nのグループから選択される元素である。

で表される材料を含むことを特徴とする請求項1又は2に記載の情報記録再生装置。 - 前記記録層は、スピネル構造、イルメナイト構造、ウルフラマイト構造、デラフォサイト構造のグループから選択される結晶構造を有することを特徴とする請求項1又は2に記載の情報記録再生装置。

- 前記記録層は、50nm以下の厚さを有することを特徴とする請求項1又は2に記載の情報記録再生装置。

- 前記積層構造の一端に接続され、第一の方向に延びる第一の導電線と、前記積層構造の他端に接続され、前記第一方向に交差する第二の方向に伸びる第二の導電線とをさらに具備し、前記第一の導電線と前記第二の導電線との間に前記電圧又は前記電流を与えて前記記録層の状態を変化させることを特徴とする請求項1に記載の情報記録再生装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2008/056499 WO2009122572A1 (ja) | 2008-04-01 | 2008-04-01 | 情報記録再生装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2009122572A1 JPWO2009122572A1 (ja) | 2011-07-28 |

| JP4792125B2 true JP4792125B2 (ja) | 2011-10-12 |

Family

ID=41134992

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010505229A Expired - Fee Related JP4792125B2 (ja) | 2008-04-01 | 2008-04-01 | 情報記録再生装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8431920B2 (ja) |

| JP (1) | JP4792125B2 (ja) |

| TW (1) | TWI406407B (ja) |

| WO (1) | WO2009122572A1 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9070876B2 (en) * | 2011-03-18 | 2015-06-30 | Nec Corporation | Variable resistance element and semiconductor storage device |

| US8711601B2 (en) * | 2011-12-28 | 2014-04-29 | Industrial Technology Research Institute | Resistive random access memory cell and resistive random access memory module |

| JP5798052B2 (ja) * | 2012-01-31 | 2015-10-21 | 株式会社東芝 | 記憶装置 |

| US8664632B2 (en) * | 2012-01-31 | 2014-03-04 | Kabushiki Kaisha Toshiba | Memory device |

| TWI572074B (zh) * | 2015-02-04 | 2017-02-21 | 力晶科技股份有限公司 | 電阻式隨機存取記憶體及其製造方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2005101420A1 (en) * | 2004-04-16 | 2005-10-27 | Matsushita Electric Industrial Co. Ltd. | Thin film memory device having a variable resistance |

| JP2006140412A (ja) * | 2004-11-15 | 2006-06-01 | Sony Corp | 記憶素子及び記憶装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5825046A (en) * | 1996-10-28 | 1998-10-20 | Energy Conversion Devices, Inc. | Composite memory material comprising a mixture of phase-change memory material and dielectric material |

| JP3974756B2 (ja) * | 2001-06-05 | 2007-09-12 | 株式会社日本触媒 | 金属酸化物系粒子の製法 |

| KR100906056B1 (ko) * | 2002-03-19 | 2009-07-03 | 파나소닉 주식회사 | 정보 기록매체와 그 제조 방법 |

| US7719875B2 (en) * | 2003-03-18 | 2010-05-18 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US7326950B2 (en) * | 2004-07-19 | 2008-02-05 | Micron Technology, Inc. | Memory device with switching glass layer |

| US7733684B2 (en) * | 2005-12-13 | 2010-06-08 | Kabushiki Kaisha Toshiba | Data read/write device |

-

2008

- 2008-04-01 WO PCT/JP2008/056499 patent/WO2009122572A1/ja not_active Ceased

- 2008-04-01 JP JP2010505229A patent/JP4792125B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-30 TW TW098110468A patent/TWI406407B/zh not_active IP Right Cessation

-

2010

- 2010-09-17 US US12/884,880 patent/US8431920B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2005101420A1 (en) * | 2004-04-16 | 2005-10-27 | Matsushita Electric Industrial Co. Ltd. | Thin film memory device having a variable resistance |

| JP2006140412A (ja) * | 2004-11-15 | 2006-06-01 | Sony Corp | 記憶素子及び記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110062407A1 (en) | 2011-03-17 |

| WO2009122572A1 (ja) | 2009-10-08 |

| US8431920B2 (en) | 2013-04-30 |

| TWI406407B (zh) | 2013-08-21 |

| TW201003909A (en) | 2010-01-16 |

| JPWO2009122572A1 (ja) | 2011-07-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5351144B2 (ja) | 情報記録再生装置 | |

| JP4792107B2 (ja) | 情報記録再生装置 | |

| JP5216847B2 (ja) | 情報記録再生装置 | |

| JP4792008B2 (ja) | 情報記録再生装置 | |

| JP4792007B2 (ja) | 情報記録再生装置 | |

| JP4792009B2 (ja) | 情報記録再生装置 | |

| JP4792006B2 (ja) | 情報記録再生装置 | |

| JP4908555B2 (ja) | 情報記録再生装置 | |

| JPWO2009122569A1 (ja) | 情報記録再生装置 | |

| KR20070062937A (ko) | 데이터 판독/기입 디바이스 | |

| JP4791948B2 (ja) | 情報記録再生装置 | |

| JP4792125B2 (ja) | 情報記録再生装置 | |

| JP2008251108A (ja) | 情報記録再生装置 | |

| JP4792108B2 (ja) | 情報記録再生装置 | |

| JP4977158B2 (ja) | 情報記録再生装置 | |

| JPWO2009116139A1 (ja) | 情報記録再生装置 | |

| WO2009122571A1 (ja) | 情報記録再生装置 | |

| JP2008276904A (ja) | 情報記録再生装置 | |

| JP2012138512A (ja) | 情報記録再生装置 | |

| JP2008251107A (ja) | 情報記録再生装置 | |

| JP2008251126A (ja) | 情報記録再生装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110509 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110628 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110722 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140729 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |