JP4635291B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4635291B2 JP4635291B2 JP2000101326A JP2000101326A JP4635291B2 JP 4635291 B2 JP4635291 B2 JP 4635291B2 JP 2000101326 A JP2000101326 A JP 2000101326A JP 2000101326 A JP2000101326 A JP 2000101326A JP 4635291 B2 JP4635291 B2 JP 4635291B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- layer

- insulating film

- forming

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Electrodes Of Semiconductors (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Light Receiving Elements (AREA)

Description

【発明の属する技術分野】

本発明は固体撮像装置およびその製造方法に関し、特に電荷結合素子を有する固体撮像装置およびその製造方法に関する。

【0002】

【従来の技術】

固体撮像装置、例えばCCD(Charge Coupled device )には、一般にインターライン方式やフレームトランスファー方式等がある。

上記のフレームトランスファー方式においては、例えばp型シリコン基板表面部に複数個のピクセルと呼ばれる受光エレメントが形成され、受光部と転送(蓄積)部に区別される。各部に設けられたピクセルにおいては、基板上にゲート絶縁膜を介してゲート電極が形成されており、そのゲート電極に正電位を印加することにより、基板の表面部位にポテンシャル井戸が形成され、受光部のピクセルに光が一定時間照射されると、光量に比例した信号電荷が発生し、上記ポテンシャル井戸に集積される。

【0003】

複数個並んだピクセルのゲート電極に例えば異なった2つのタイミングを持ったクロック電圧パルスを印加すると、ポテンシャル井戸の障壁が順次開閉されて信号電荷が受光部から転送部へ順次に転送される。

更に転送された信号電荷はレジスター部において上記クロックとは異なるタイミングを持ったクロックによって出力され、出力アンプ等を経てビデオ信号として出力することができる。

このようにCCDは光信号を信号電荷に変換することができ、現在広く工業用、民生用撮像機器に使用されている。

【0004】

上記のCCDなどの固体撮像装置においては、信号電荷がポテンシャル井戸の容量を越えた場合に、溢れた信号電荷が他のピクセルのポテンシャル井戸に補足されたりするのを防止するため、通常、余剰な信号電荷を掃き捨てるオーバーフロードレインが備えられている。オーバーフロードレインは、縦型オーバーフロードレイン(Vertical Overflow Drain ;VOD)と、横型オーバーフロードレイン(Lateral Overflow Drain;LOD)の2種類に大別される。

【0005】

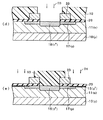

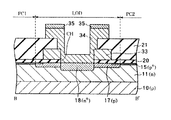

図3(a)は、上記の横型オーバーフロードレインの第1従来例の断面図である。

横型オーバーフロードレインLODは、不図示のチャネル分離層により分離されて隣接する2つのピクセル(PC1,PC2)の境界に、上記チャネル分離層を分断するように形成されている。

上記ピクセル(PC1,PC2)領域において、p型半導体基板10中にCCD転送路となるn型埋め込みチャネル11が形成されており、その表層部にp+ 反転層15が形成されている。

一方、上記2つのピクセル領域(PC1,PC2)の境界にある横型オーバーフロードレイン領域LODにおいても、上記n型埋め込みチャネル11が連通して形成されている。横型オーバーフロードレイン領域LODの中央部におけるn型埋め込みチャネル11の表層部には、n型埋め込みチャネル11に接続するようにn+ 領域18が形成されている。さらに、上記n+ 領域18とp+ 反転層15の間を含むn+ 領域18のリング状の外周部におけるn型埋め込みチャネル11の表層部には、完全には反転しない程度にp型不純物が導入されたp型領域17が形成されている。

上記基板の上層には酸化シリコンのゲート絶縁膜20が形成されており、ゲート絶縁膜20の上層にリング状のゲート電極33が形成されており、さらに当該リング形状の中央部におけるゲート絶縁膜20の開口部CHを埋め込んでn+ 領域18に接続し、さらにゲート電極33にも接続するようにして、例えばアルミニウムあるいはシリコンを含有するアルミニウムなどからなる配線層34が形成されている。

【0006】

上記の構造においては、n+ 領域18をドレイン、ピクセル領域(PC1,PC2)のn型埋め込みチャネル11をソースとし、ゲート絶縁層20の上層のゲート電極33と、n+ 領域18の外周部においてリング状のチャネル形成領域を有し、ドレインとゲートが短絡されたMOS電界効果トランジスタが構成されている。

【0007】

図3(b)は、上記の構造の横型オーバーフロードレインLODのp型半導体基板10の表面と平行な方向に対するポテンシャル図である。

ピクセル領域(PC1,PC2)のn型埋め込みチャネル11とn+ 領域18の境界部分に形成されたp型領域17は信号電荷に対するバリア(電位障壁)を形成し、その外側方向(ピクセル領域(PC1,PC2)方向)にウェル(ポテンシャル井戸)が形成されて、信号電荷(電子)が蓄積される。

信号電荷がポテンシャル井戸の容量を越えると、余剰な信号電荷はp型領域17が形成するバリアを乗り越え、n+ 領域(ドレイン)18へと掃き捨てられる。

【0008】

上記の横型オーバーフロードレインLODの製造方法について説明する。

まず、図4(a)に示すように、p型のシリコン半導体基板10上に、例えば熱酸化法あるいはCVD法などにより酸化シリコン層を成膜し、ゲート絶縁膜となるゲート絶縁膜20を形成する。

次に、例えばリンなどのn型の導電性不純物D1を全面にイオン注入して、n型埋め込みチャネル11を形成する。

【0009】

次に、図4(b)に示すように、フォトリソグラフィー工程により横型オーバーフロードレインの形成領域を開口するパターンのレジスト膜R1をパターニング形成し、ホウ素などのp型の不純物D2を完全には反転しない程度にイオン注入して、n型のチャネル形成領域11の表層部にp型領域17を形成する。

【0010】

次に、図4(c)に示すように、レジスト膜R1を除去した後、例えばCVD法により全面に導電性不純物を含有するポリシリコンを成膜し、リング形状のゲート電極のパターンのレジスト膜(不図示)を形成してRIE(反応イオンエッチング)などのエッチングを施して、リング形状のゲート電極33を形成する。

【0011】

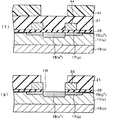

次に、図5(d)に示すように、フォトリソグラフィー工程によりドレインとなる領域を開口するパターンのレジスト膜R2をパターニング形成し、砒素などのn型の不純物D3をイオン注入して、n型埋め込みチャネル11に接続するようにn+ 領域18を形成する。

ここで、上記のn型の不純物D3のイオン注入は、ゲート電極33をマスクとするので、レジスト膜R2は、ゲート電極33を半分程度遮蔽するパターンで形成する。

【0012】

次に、図5(e)に示すように、レジスト膜R2を除去した後、ドレインとなる領域を覆うレジスト膜R3をパターニング形成し、p型の不純物D4をイオン注入して表面のp+ 反転層15を形成する。ここで、上記のp型領域17の形成パターンはゲート電極33の形成パターンよりも広くしてあり、p型領域17はゲート電極33の下部からはみ出して形成されており、このために、上記のp+ 反転層15とp型領域17とはある程度の重なり部分により接続される。

【0013】

次に、図6(f)に示すように、レジスト膜R3を除去し、例えばCVD法によりゲート電極33を被覆して全面に酸化シリコンを堆積させ、層間絶縁膜21を形成する。

次に、フォトリソグラフィー工程により、上記レジスト膜R2と同様のドレインとなる領域を開口するパターンのレジスト膜R4をパターニング形成する。

【0014】

次に、図6(g)に示すように、例えばRIEなどのエッチングにより、レジスト膜R4をマスクとし、ゲート電極33に対して選択比を有するようにして、層間絶縁膜21およびゲート絶縁膜20をエッチング加工し、n+ 領域18を露出させる開口部CHを形成する。この後、レジスト膜R4を除去する。

【0015】

次に、上記n+ 領域18およびゲート電極33に接続するように、例えばDCマグネトロン放電によるスパッタリング法などにより、アルミニウムあるいは1%程度のシリコンを含有するアルミニウムを全面に堆積させ、開口部CH内を埋め込む。その後、フォトリソグラフィー工程およびドライエッチング工程などを経て配線層34を形成し、図3(a)に示す構造に至る。

【0016】

上記のCCDにおいては、画素サイズの縮小化に伴い、ゲート設計寸法(設計ルール)の縮小化がなされ、例えば最先端デバイスにおいてはゲート最小設計寸法がハーフミクロンからサブハーフミクロンに至ろうとしており、上記n+ 領域18に接続する配線層34などの配線においても、コンタクト径あるいはビアホール径がハーフミクロン(0.5μm)程度にまで縮小化されつつある。

【0017】

【発明が解決しようとする課題】

しかしながら、上記の画素サイズやコンタクト径などの縮小化が進められ、図17に示すように、コンタクト径(φCH)が縮小化されて、0.8μm以下となり、さらにコンタクトホールのアスペクト比(コンタクトホールの深さDP:コンタクト径φCH)が1:1よりも高アスペクト比の領域となってくると、例えば上記の配線層をアルミニウムあるいは1%程度のシリコンを含有するアルミニウムなどの導電性材料により形成する場合、形成される膜のオーバーハングが大きくなり、段差被覆性が良好ではないので、コンタクト底部近傍の壁面部分が上記導電性材料で被覆されないコンタクト被覆不良Fが発生しやすいという問題がある。

【0018】

また、上記の配線層をアルミニウムにより形成する場合には、アルミニウムとシリコン基板が接触しているために、図18に示すように、水素処理による界面準位の除去、トランジスタの閾値調整やアルミニウムの結晶化促進など、種々の目的で行うシンター工程(例えば450℃、30分)などを含む各種処理工程において、アルミニウムが基板のシリコンを吸い上げる、あるいは、アルミニウムが基板中に拡散するなどにより、アルミニウムのアロイスパイクSが発生しやすく、これにより浅いp−n接合あるいはn−p接合に著しいリーク電流を生じさせることになる。

【0019】

また、上記のアロイスパイクSの形成を回避するためには、基板に接触する配線層となるアルミニウムに予め1%程度のシリコンを含有させることで、基板からのシリコンの吸い上げなどを防止してアロイスパイクSが形成されるのを防ぐ方法があるが、この場合には、図19に示すように、上記配線層形成後の処理工程において、コンタクト底部部分Rのシリコン濃度が高くなる(シリコンが析出する)ため、コンタクトホールの径を比較的大きな1.4μm程度にしても、コンタクト抵抗が3000Ω程度の高抵抗となってしまうという問題が発生しやすくなっている。

【0020】

上記のアロイスパイク発生やコンタクト抵抗上昇などの問題を回避するため、DRAM(Dynamic Random Access Memory)やロジックデバイスなどにおいては、チタン(Ti)/窒化チタン(TiN)積層膜であるバリアメタル膜をコリメーションスパッタリング法などにより形成した後、適当なアニール処理を施し、さらにタングステン(W)膜をCVD法により積層させて形成する方法が知られており、広く用いられている。

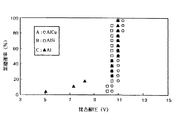

図20(a)は、上記の方法を横型オーバーフロードレインのコンタクト接続用に適用した場合の横型オーバーフロードレイン部の断面図である。Ti/TiN積層膜であるバリアメタル膜34aを形成した後、適当なアニール処理を施し、さらにW膜34bを積層させて形成する。

しかしながら、上記のTi/TiN積層膜であるバリアメタル膜34aとW膜34bを積層させた構造をCCDに適用すると、上記のアロイスパイク発生やコンタクト抵抗上昇などの問題を解決することができるものの、暗電流が劇的に増加してしまうという撮像装置にとっては致命的な問題が新たに生じてしまう。

【0021】

図20(b)は、1.4μmφのコンタクト径を有する仮想ゲート構造のCCD(7.2μm画素)において、コンタクト接続用の配線を(A)1%程度のシリコンを含有させたアルミニウム、(B)Ti(膜厚50nm)/TiN/W積層膜、(C)Ti(膜厚100nm)/TiN/W積層膜でそれぞれ形成したときの暗電流(相対値)を測定し、累積確率に対してプロットした図である。

図20(b)から、Ti/TiN/W積層膜を用いることで暗電流が著しく増加し、Ti膜厚を厚くすることで、さらに増加してしまうことが確認された。

【0022】

上記のコンタクト用の配線を形成するために、DRAMやロジックデバイスなどにおいては、アルミニウムリフロー法や高圧アルミニウム埋め込み法、あるいはCVDアルミニウム法などが開発されているが、いずれも上記のTi系バリアメタルが必要となり、暗電流が悪化する問題を引き起こす。

【0023】

本発明は上記の問題点に鑑みてなされたものであり、本発明は、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができるオーバーフロードレインなどにおけるコンタクト接続を有する固体撮像装置を提供すること、さらにコンタクト被覆不良の発生を防止しつつ上記固体撮像装置を形成することができる固体撮像装置の製造方法を提供することを目的とする。

【0024】

【課題を解決するための手段】

上記の目的を達成するため、本発明の固体撮像装置は、第1導電型の半導体基板と、上記半導体基板の主面に形成されている第2導電型の半導体層と、上記半導体基板の主面に上記半導体層を区画するように形成されている第1導電型の分離領域と、上記半導体基板の主面において上記分離領域により区画される半導体層の間に上記分離領域に隣接して形成されている環状の第1導電型の第1の半導体領域と、上記半導体基板の主面において上記第1の半導体領域の内側に上記第1の半導体領域に接するように形成されている第2導電型の第2の半導体領域と、上記第1の半導体領域上に環状に形成されている第1の絶縁膜と、上記第1の絶縁膜に形成されている開口部を介して上記第2の半導体領域に接続するように上記第1の絶縁膜上に形成されている電極とを有し、上記電極が銅を含有するアルミニウムで構成され、上記第1の半導体領域、上記第2の半導体領域、上記第1の絶縁膜及び上記電極により電荷掃き捨て部が構成されている。

【0025】

本発明の固体撮像装置は、好適には、上記銅の含有量が0.4〜5重量%の範囲、さらに好適には、0.5〜0.8重量%の範囲にある。

【0026】

本発明の固体撮像装置は、横型オーバーフロードレイン(LOD)におけるコンタクトなど、シリコン層などの導電層と直接接続される電極の材料として銅を含有するアルミニウムを用いる。電極の材料に銅を含有するアルミニウムを用いることで、固体撮像装置における暗電流の増大を抑制しつつ、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができる。

【0027】

アルミニウム中の銅の含有量が、0.4重量%未満ではアロイスパイクの発生防止能力が十分ではなく、アロイスパイクを防ぐためには製造工程温度に対する制約が大きくなってしまい、製造が困難となる。また、上記含有量が5重量%を越えると、エッチングなどの加工適性がなくなってしまい、製造が困難となる。上記銅の含有量の最も好ましい範囲は0.5〜0.8重量%であり、加工適性などを悪化させることなく、容易に本発明の効果を享受できる。

【0028】

また、上記の目的を達成するため、本発明の固体撮像装置の製造方法は、第1導電型の半導体基板の主面に第2導電型の半導体層を形成する工程と、上記半導体基板の主面に上記半導体層を区画するための第1導電型の分離領域を形成する工程と、上記半導体層上に第1の絶縁層を形成する工程と、上記第1の絶縁層をエッチングすることにより上記分離領域により区画される半導体層の間に上記半導体層が露出する第1の開口部を形成する工程と、上記第1の絶縁層をマスクとして第1導電型の不純物を注入して第1導電型の第1の半導体領域を形成する工程と、上記第1の開口部を含む上記第1の絶縁層上に第2の絶縁層を形成する工程と、上記第2の絶縁層を全面的にエッチングすることにより上記第1の開口部の周縁部に環状の第1の絶縁膜を形成するとともに上記第1の絶縁膜の内側に上記半導体層が露出する第2の開口部を形成する工程と、上記第1の絶縁膜をマスクとして第2導電型の不純物を注入して上記第1の半導体領域の内側に第2導電型の第2の半導体領域を形成する工程と、上記第2の開口部を介して上記第2の半導体領域に接続される電極を上記第1の絶縁膜上に形成する工程とを有し、上記電極が銅を含有するアルミニウムで構成される。

【0029】

本発明の固体撮像装置の製造方法においては、好適には、上記電極がコヒーレントスパッタリング法により形成される。

【0030】

また、本発明の固体撮像装置の製造方法においては、好適には、上記電極を形成する工程後に行なわれるシンター処理が350℃以下の温度で行なわれる。

【0031】

また、本発明の固体撮像装置の製造方法においては、好適には、上記銅の含有量が0.4〜5重量%の範囲、さらに好適には、0.5〜0.8重量%の範囲にある。

【0032】

本発明の固体撮像装置の製造方法によれば、電極の材料に銅を含有するアルミニウムを用いることで、固体撮像装置における暗電流の増大を抑制しつつ、コンタクト抵抗の上昇、アロイスパイクの発生を防止して固体撮像装置を製造することができ、さらにコヒーレントスパッタリング法により銅を含有するアルミニウムからなる電極を形成することで、コンタクト被覆不良の発生を防止することができる。電極形成の後に行なわれるシンター処理を350℃以下の温度で行なうことで、効果的にアロイスパイクの発生を防止することが可能である。

【0033】

アルミニウム中の銅の含有量が0.4重量%未満ではアロイスパイクの発生防止能力が十分ではなく、アロイスパイクを防ぐためには製造工程温度に対する制約が大きくなってしまい、製造が困難となる。また、アルミニウム中の銅の含有量が5重量%を越えると、エッチングなどの加工適性がなくなってしまい、製造が困難となる。上記銅の含有量の最も好ましい範囲は0.5〜0.8重量%であり、加工適性などを悪化させることなく、容易に本発明の効果を享受できる。

【0034】

【発明の実施の形態】

以下に、本発明の実施の形態について、図面を参照して説明する。

【0035】

第1実施形態

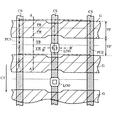

図1は、本実施形態にかかる固体撮像装置(CCD)の平面図であり、仮想ゲート構造を持った埋め込みチャネル型の単相駆動型CCDである。

p型シリコン半導体基板のp型チャネル分離層CSで分離された領域に、n型の導電性不純物を含有するシリコン層からなり、矢印CTの方向に信号電荷を転送するn型埋め込みチャネルが形成されている。

n型埋め込みチャネルの上層に例えば酸化シリコンからなるゲート絶縁膜を介して、n型埋め込みチャネルの形成方向と垂直な方向に、例えばポリシリコンからなるゲート電極Gが形成されている。

ゲート電極Gの下部領域において、バリアとなるPB部と、ウェルとなるPW部が矢印CTの方向に順に形成されており、一方、2つのゲート電極Gの間隙領域において、バリアとなるVB部と、ウェルとなるVW部が矢印CTの方向に順に形成されている。PB部、PW部、VB部およびVW部から、1つのピクセルが構成される。PB部およびPW部を合わせてポリ相(ポリシリコンからなるゲートの相)PPと呼び、VB部およびVW部を合わせて仮想ゲート相VPと呼ぶ。

さらに、隣接する2つのピクセル(PC1,PC2)の境界となるチャネル分離層CSを分断する位置に、信号電荷がPW部やVW部などのポテンシャル井戸の容量を越えた場合に、溢れた信号電荷が他のピクセルのポテンシャル井戸に補足されたりするのを防止するため、余剰な信号電荷を掃き捨てる横型オーバーフロードレインLODが備えられている。

【0036】

図2(a)は図1中のA−A’における断面図である。

p型シリコン半導体基板10のp型チャネル分離層(不図示)で分離された領域に、n型の導電性不純物を含有するシリコン層からなるn型埋め込みチャネル11が形成されており、その上層に例えば酸化シリコンのゲート絶縁膜20が形成されており、その上層に例えばポリシリコンからなるゲート電極30が形成されている。ゲート電極30の下層のチャネル形成領域11中にはn型の導電性不純物の高濃度領域である第1n+ 領域13が形成されており、この領域がPW部となる。PW部を除く領域のゲート電極30の下層の領域がPB部となる。

【0037】

各ゲート電極30の間隙部において、n型埋め込みチャネル11中にはp型の導電性不純物を含有する第1p+ 反転層15と、第1p+ 反転層15よりもp型の導電性不純物を高濃度に含有する第2p+ 反転層16が形成されており、さらに第1p+ 反転層15および第2p+ 反転層16の下層のn型埋め込みチャネル11中にはn型の導電性不純物の高濃度領域である第2n+ 領域14が形成されており、仮想ゲート領域を構成する。第1p+ 反転層15の下層の領域がVW部となり、第2p+ 反転層16の下層の領域がVB部となる。

上記のように、一つのゲート電極30と一つの仮想ゲート、即ち、PB部、PW部、VB部、およびVW部の4相から、一つのCCDセル(ピクセル)が構成されており、これら4相が信号電荷の転送方向に繰り返し形成されている。

上記のゲート電極30の上層に、ゲート電極30を被覆して層間絶縁膜21が形成されている。

【0038】

図2(b)は、上記のCCDセル(ピクセル)のポテンシャル図であり、PB部、PW部、VB部、およびVW部の4相のポテンシャルおよび信号電荷の転送方法について説明する。

各セルのゲート電極30は共通の電圧パルス(高(High)と低(Low))が与えられ、一方で仮想ゲート領域においては第1p+ 反転層15および第2p+ 反転層16により隣接するゲート電極の影響を受けず、一定ポテンシャルとなる。つまり、仮想ゲート領域は電極が無くとも一定電位の電極があるのと同様に動作する。

信号電荷は、ゲート電極30が高(High)から低(Low)へ変わったときにPW部からVW部へ、低(Low)から高(High)へ変わったときにVW部からPW部へ転送される。このとき、転送動作を円滑に行うため、PB部およびVB部は信号電荷の逆流を防ぐためのバリアとして働き、PW部およびVW部は信号電荷を蓄えるためのウェルとして働く。

【0039】

図3(a)は、図1中のB−B’における断面図である。

横型オーバーフロードレインLODは、不図示のチャネル分離層により分離されて隣接する2つのピクセル(PC1,PC2)の境界に、上記チャネル分離層を分断するように形成されている。

上記ピクセル(PC1,PC2)領域において、p型半導体基板10中にCCD転送路となるn型埋め込みチャネル11が形成されており、その表層部にp+ 反転層15が形成されている。

一方、上記2つのピクセル領域(PC1,PC2)の境界にある横型オーバーフロードレイン領域LODにおいても、上記n型埋め込みチャネル11が連通して形成されている。横型オーバーフロードレイン領域LODの中央部におけるn型埋め込みチャネル11の表層部には、n型埋め込みチャネル11に接続するようにn+ 領域18が形成されている。さらに、上記n+ 領域18とp+ 反転層15の間を含むn+ 領域18のリング状の外周部におけるn型埋め込みチャネル11の表層部には、完全には反転しない程度にp型不純物が導入されたp型領域17が形成されている。

上記基板の上層には酸化シリコンのゲート絶縁膜20が形成されており、ゲート絶縁膜20の上層にリング状のゲート電極33が形成されており、さらに当該リング形状の中央部におけるゲート絶縁膜20の開口部CHを埋め込んでn+ 領域18に接続し、さらにゲート電極33にも接続するようにして、銅を含有するアルミニウムからなる配線層34が形成されている。この配線層34は、チャネル分離層の上層においてピクセル領域を横切らない配線として形成されている。

【0040】

上記の構造においては、n+ 領域18をドレイン、ピクセル領域(PC1,PC2)のn型埋め込みチャネル11をソースとし、ゲート絶縁層20の上層のゲート電極32と、n+ 領域18の外周部においてリング状のチャネル形成領域を有し、ドレインとゲートが短絡されたMOS電界効果トランジスタが構成されている。

【0041】

図3(b)は、上記の構造の横型オーバーフロードレインLODのp型半導体基板10の表面と平行な方向に対するポテンシャル図である。

ピクセル領域(PC1,PC2)のn型埋め込みチャネル11とn+ 領域18の境界部分に形成されたp型領域17は信号電荷に対するバリア(電位障壁)を形成し、その外側方向(ピクセル領域(PC1,PC2)方向)にウェル(ポテンシャル井戸)が形成されて、信号電荷(電子)が蓄積される。

信号電荷がポテンシャル井戸の容量を越えると、余剰な信号電荷はp型領域17が形成するバリアを乗り越え、n+ 領域(ドレイン)18へと掃き捨てられる。

さらに、配線層34に印加する電圧を制御することで、p型領域17が形成する電位障壁を緩和あるいは消滅させ、蓄積電荷を全て掃き捨てることが可能である。このように、一度全ての信号電荷を除去した後、所定のタイミングから改めて信号電荷を蓄積するように制御することで、本実施形態のCCDに電子シャッターの機能を付与することができる。

【0042】

上記の本実施形態のCCDにおいては、横型オーバーフロードレイン(LOD)におけるシリコン基板表層のn+ 領域18に対するコンタクトにおいて、シリコン基板(n+ 領域18)と直接接触する配線材料として銅を含有するアルミニウムを用いる。

これにより、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができる。

上記のアルミニウム中の銅の含有量は、0.4重量%未満ではアロイスパイクの発生防止能力が十分ではなく、アロイスパイクを防ぐためには製造工程温度に対する制約が大きくなってしまい、製造が困難となる。また、5重量%を越えると、エッチングなど加工適性がなくなってしまい、製造が困難となる。0.5〜0.8重量%の範囲が最も好ましい範囲であり、加工適性などを悪化させることなく、容易に本発明の効果を享受できる。

【0043】

上記の横型オーバーフロードレインLODを有するCCDの製造方法について説明する。

まず、図4(a)に示すように、p型のシリコン半導体基板10上に、例えば熱酸化法あるいはCVD(Chemical Vapor Deposition )法などにより酸化シリコン層を成膜し、ゲート絶縁膜となるゲート絶縁膜20を形成する。

次に、例えばリンなどのn型の導電性不純物D1を全面にイオン注入して、n型埋め込みチャネル11を形成する。

【0044】

次に、図4(b)に示すように、フォトリソグラフィー工程により横型オーバーフロードレインの形成領域を開口するパターンのレジスト膜R1をパターニング形成し、ホウ素などのp型の不純物D2を完全には反転しない程度にイオン注入して、n型のチャネル形成領域11の表層部にp型領域17を形成する。

【0045】

次に、図4(c)に示すように、レジスト膜R1を除去した後、例えばCVD法により全面に導電性不純物を含有するポリシリコンを成膜し、リング形状のゲート電極のパターンのレジスト膜(不図示)を形成してRIE(反応性イオンエッチング)などのエッチングを施して、リング形状のゲート電極33を形成する。

【0046】

次に、図5(d)に示すように、フォトリソグラフィー工程によりドレインとなる領域を開口するパターンのレジスト膜R2をパターニング形成し、砒素などのn型の不純物D3をイオン注入して、n型埋め込みチャネル11に接続するようにn+ 領域18を形成する。

ここで、上記のn型の不純物D3のイオン注入は、ゲート電極33をマスクとするので、レジスト膜R2は、ゲート電極33を半分程度遮蔽するパターンで形成する。

【0047】

次に、図5(e)に示すように、レジスト膜R2を除去した後、ドレインとなる領域を覆うレジスト膜R3をパターニング形成し、p型の不純物D4をイオン注入して表面のp+ 反転層15を形成する。ここで、上記のp型領域17の形成パターンはゲート電極33の形成パターンよりも広くしてあり、p型領域17はゲート電極33の下部からはみ出して形成されており、このために、上記のp+ 反転層15とp型領域17とはある程度の重なり部分により接続される。

【0048】

次に、図6(f)に示すように、レジスト膜R3を除去した後、例えばCVD法によりゲート電極33を被覆して全面に酸化シリコンを堆積させ、層間絶縁膜21を形成する。

次に、フォトリソグラフィー工程により、上記レジスト膜R2と同様のドレインとなる領域を開口するパターンのレジスト膜R4をパターニング形成する。

【0049】

次に、図6(g)に示すように、例えばRIEなどのエッチングにより、レジスト膜R4をマスクとし、ゲート電極33に対して選択比を有するようにして、層間絶縁膜21およびゲート絶縁膜20をエッチング加工し、n+ 領域18を露出させる開口部CHを形成する。この後、レジスト膜R4を除去する。

【0050】

次に、上記n+ 領域18およびゲート電極33に接続するように、例えば遠距離スパッタリング法、コリメータスパッタリング法、あるいは、IMPスパッタリング法などのコヒーレントスパッタリング法により、銅を含有するアルミニウムを全面に堆積させ、開口部CH内を埋め込む。その後、フォトリソグラフィー工程およびドライエッチング工程などを経て配線層34を形成し、図3(a)に示す構造に至る。

遠距離スパッタリング法とは、通常のDCマグネトロン放電によるスパッタリング法において、10cm程度に設定されているターゲットと被処理基板との離間距離を20〜25cm程度に設定するスパッタリング法で、被処理基板に対してイオンを垂直に入射させることができる。

また、コリメータスパッタリング法とは、被処理基板に対して水平方向に進行するイオンをマスクで除去し、垂直成分のみを透過させることで、被処理基板に対してイオンを垂直に入射させるスパッタリング法である。

また、IMP法とは、イオンに電圧を印加して、被処理基板に対して垂直に入射するように加速させる方法である。

上記の各種コヒーレントスパッタリング法では、被覆率を向上させて成膜することができ、コンタクトホールなどのアスペクト比が高くなってもコンタクト被覆不良の発生を防止することができる。

【0051】

以降の工程としては、シンター工程を含む処理工程を、全て350℃以下の温度で行う。また、350℃の温度がかけられる処理の処理時間の総計が2時間以内となるように設定する。

例えば、TEOS(tetraethylorthosilicate )を原料とするプラズマCVD法により(350℃、5分)の条件で全面に酸化シリコン膜を堆積させ、SOG膜のコート・キュア工程を(350℃、60分)の条件で行い、SOG膜のエッチバックの後、さらにTEOSを原料とするプラズマCVD法により(350℃、5分)の条件で全面に酸化シリコン膜を堆積させる。

次に、フォトリソグラフィー工程によりビアパターンのレジスト膜をパターン形成し、RIEなどのエッチングによりビアホールを開口する。

次に、上記と同様にして、コヒーレントスパッタリング法により、銅を含有するアルミニウムを全面に堆積させ、ビアホール内を埋め込み、フォトリソグラフィー工程およびドライエッチング工程などを経て上層配線とする。

次に、TEOSを原料とするプラズマCVD法により(350℃、5分)の条件で全面に酸化シリコン膜を堆積させてパッシベーション膜を形成し、(350℃、30分)の条件でシンター処理を行う。さらにパッド部分を開口して、所望のCCDとすることができる。

【0052】

上記の本実施形態のCCDの製造方法によれば、横型オーバーフロードレインLODのコンタクトの配線材料に銅を含有するアルミニウムを用いることで、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止した固体撮像装置を製造することができる。

さらにコヒーレントスパッタリング法により銅を含有するアルミニウムからなる配線層を形成することで、コンタクト被覆不良の発生を防止することができる。

また、コンタクトに接続する配線層形成以降のシンター工程を含む処理工程を全て350℃以下の温度で行うことで、効果的にアロイスパイクの発生を防止することが可能である。

【0053】

第2実施形態

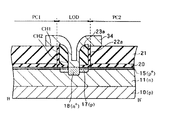

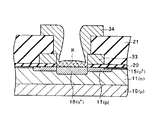

本実施形態に係るCCDの横型オーバーフロードレインLODは、図7に示す断面構造を有する。

横型オーバーフロードレインLODは、p+ チャネル分離層(不図示)により分離されて隣接する2つのピクセル(PC1,PC2)の境界に、上記p+ チャネル分離層を分断するように形成されている。

上記ピクセル(PC1,PC2)領域において、p型半導体基板10中にCCD転送路となるn型埋め込みチャネル11が形成されており、その表層部にp+ 反転層15が形成されている。

一方、上記2つのピクセル領域(PC1,PC2)の境界にある横型オーバーフロードレイン領域LODにおいても、上記n型埋め込みチャネル11が連通して形成されている。上記のようにn型埋め込みチャネル11が形成されている半導体基板の上層には、ゲート絶縁膜20と層間絶縁膜21が積層して形成されており、横型オーバーフロードレインLOD領域において、半導体基板を露出するようにゲート絶縁膜20と層間絶縁膜21に第1開口部CH1が形成されている。

【0054】

上記の第1開口部CH1内において、スクリーン酸化膜22aを介して、例えば窒化シリコンあるいは導電性不純物を含有しないポリシリコンなどの絶縁膜からなるサイドウォール絶縁膜23aが内壁面を被覆して半導体基板10上に形成されて、第1開口部CH1よりも開口径が狭い第2開口部CH2が構成される。

即ち、第2開口部CH2の開口径φは、第1開口部CH1の開口径よりもスクリーン酸化膜22aとサイドウォール絶縁膜23aの幅分狭められている。

上記のサイドウォール絶縁膜23aの下部のリング状の領域におけるn型埋め込みチャネル11の表層部に、完全には反転しない程度にp型不純物が導入されたp型領域17が形成されており、第2開口部CH2におけるn型埋め込みチャネル11の表層部に、n型不純物を高濃度に含有するn+ 領域18が形成されている。

さらに、第2開口部CH2内を埋め込み、n+ 領域18に接続するように、銅を含有するアルミニウムからなる配線層34が形成されている。アルミニウム中の銅の含有量は、第1実施形態と同様とする。この配線層34は、チャネル分離層の上層においてピクセル領域を横切らない配線として形成されている。

【0055】

上記の構造の横型オーバーフロードレインLODを有するCCDにおいては、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができる。

また、上記の構造の横型オーバーフロードレインLODはさらなる縮小化に対応可能で、2つのピクセルで共有したときのバリアの高さのばらつきを抑制することができる。

【0056】

上記の横型オーバーフロードレインLODを有するCCDの製造方法について説明する。

まず、図8(a)に示すように、p型のシリコン半導体基板10上に、例えば熱酸化法あるいはCVD法などにより酸化シリコン層を成膜し、ゲート絶縁膜20を形成する。

【0057】

次に、図8(b)に示すように、例えばリンなどのn型の導電性不純物D5およびホウ素などのp型の導電性不純物D6を全面にイオン注入して、n型埋め込みチャネル11および第1p+ 反転層15を形成する。

図示はしていないが、上記の導電性不純物D5は隣接するピクセル領域においても同様に全面に導入されてn型埋め込みチャネルを形成し、一方で導電性不純物D6は、ピクセル領域においては仮想ゲート領域にのみ導入される。

【0058】

次に、図8(c)に示すように、例えばTEOSなどを原料とする減圧CVD法などにより酸化シリコンを全面に堆積させ、層間絶縁膜21を形成する。

次に、フォトリソグラフィー工程により横型オーバーフロードレインの形成領域を開口するパターンのレジスト膜R5をパターニング形成し、RIEなどのエッチングを施して、横型オーバーフロードレインの形成領域の半導体基板を露出させる第1開口部CH1を形成する。第1開口部CH1の開口径は、例えば0.5〜2.0μm程度である。

【0059】

次に、図9(d)に示すように、第1開口部CH1内壁を被覆して、例えばTEOSなどを原料とする減圧CVD法あるいはその他のCVD法などにより、例えば10nmの膜厚で酸化シリコンを全面に堆積させ、スクリーン酸化膜22を形成する。

【0060】

次に、図9(e)に示すように、スクリーン酸化膜22を通過させて、層間絶縁膜21をマスクとし、ホウ素などのp型不純物D7を完全には反転しない程度にイオン注入し、第1開口部CH1内におけるn型埋め込みチャネル11の表層部にp型領域17を形成する。

ここで、上記のp型領域17の形成領域には、既に第1p+ 反転層15が形成されていることから、p型領域17と第1p+ 反転層15は接続されて形成されることになる。

【0061】

次に、図9(f)に示すように、第1開口部CH1の内側を含めてスクリーン酸化膜22の上層に全面に、例えばCVD法により窒化シリコンあるいは導電性不純物を含有しないポリシリコンなどの絶縁体を、例えば0.2〜0.4μmの膜厚で堆積させ、サイドウォール絶縁膜用層23を形成する。

【0062】

次に、図10(g)に示すように、スクリーン酸化膜22に対してエッチング選択比を有するRIEなどのエッチングによりエッチバックして、第1開口部CH1の内壁を被覆する部分を残して上記サイドウォール絶縁膜用層23除去し、サイドウォール絶縁膜23aに形状加工する。サイドウォール絶縁膜用層23の膜厚を例えば0.2〜0.4μmとした場合には、サイドウォール絶縁膜23aの幅を同様に0.2〜0.4μmとすることができる。

上記のように第1開口部CH1内にサイドウォール絶縁膜23aを形成したことにより、その内側の第2開口部CH2の開口径は、例えば0.2〜1.0μm程度に狭められる。

【0063】

次に、図10(h)に示すように、スクリーン酸化膜22を通過させて、サイドウォール絶縁膜23aをマスクとし、砒素などのn型不純物D8を高濃度にイオン注入し、第2開口部CH2内におけるn型埋め込みチャネル11の表層部に、n型埋め込みチャネル11に接続するようにn+ 領域(ドレイン)18を形成する。

【0064】

次に、図10(i)に示すように、例えば窒化シリコンなどのサイドウォール絶縁膜23aに対してエッチング選択比を有してスクリーン酸化膜22を除去できる条件のRIEなどのエッチングにより、第2開口部CH2内のスクリーン酸化膜22を除去して、n+ 領域18を露出させる。このエッチングにおいて、層間絶縁膜21上のスクリーン酸化膜22も除去され、第1開口部CH1の内壁を被覆する部分のスクリーン酸化膜22aのみが残される。

【0065】

次に、上記n+ 領域18に接続するように、例えば遠距離スパッタリング法、コリメータスパッタリング法、あるいは、IMPスパッタリング法などのコヒーレントスパッタリング法により、銅を含有するアルミニウムを全面に堆積させ、開口部CH内を埋め込む。その後、フォトリソグラフィー工程およびドライエッチング工程などを経て配線層34を形成し、図7に示す構造に至る。

【0066】

以降の工程としては、第1実施形態と同様に、シンター工程を含む処理工程を、全て350℃以下の温度で行う。また、350℃の温度がかけられる処理の処理時間の総計が2時間以内となるように設定する。

【0067】

上記の本実施形態のCCDの製造方法によれば、横型オーバーフロードレインLODのコンタクトの配線材料に銅を含有するアルミニウムを用いることで、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止した固体撮像装置を製造することができる。

さらにコヒーレントスパッタリング法により銅を含有するアルミニウムからなる配線層を形成することで、コンタクト被覆不良の発生を防止することができる。

また、コンタクトに接続する配線層形成以降のシンター工程を含む処理工程を全て350℃以下の温度で行うことで、効果的にアロイスパイクの発生を防止することが可能である。

【0068】

第3実施形態

本実施形態に係るCCDの横型オーバーフロードレインLODは、図11に示す断面構造を有しており、第1実施形態と実質的に同様であるが、配線層34の上層にTiN膜などの反射防止膜35が形成されていることが異なる。

TiN膜はシリコン基板に接していないので、暗電流を悪化させることはなく、コンタクトの配線材料に銅を含有するアルミニウムを用いることで、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができる。

また、反射防止膜35が形成されているので、フォトリソグラフィー工程においてレジスト膜をパターン形成するための露光の光の反射を防止し、形成されるレジスト膜のパターン不良を防止できる。

【0069】

第4実施形態

本実施形態に係るCCDは、図12(a)に示す断面構造を有し、これは図1中のC−C’における断面図に相当する。

即ち、p型シリコン半導体基板10のp+ 型チャネル分離層12の延伸方向に沿った断面であり、p型シリコン半導体基板10中にp+ 型チャネル分離層12が形成されており、その上層に例えば酸化シリコンのゲート絶縁膜20が形成されており、その上層に例えばポリシリコンからなるゲート電極30が形成されており、その上層にゲート電極30を被覆して酸化シリコンの層間絶縁膜21が形成されている。

層間絶縁膜21には、ゲート電極30に達する開口部CHG が開口されており、開口部CHG を埋め込んでゲート電極30に接続するようにして、銅を含有するアルミニウムからなる配線層36が形成されている。アルミニウム中の銅の含有量は、第1実施形態における横型オーバーフロードレインにおいてシリコン基板に接続する配線層の場合と同様とする。この配線層36は、チャネル分離層の上層においてピクセル領域を横切らない配線として形成されている。

【0070】

上記の配線層36を銅を含有するアルミニウムにより形成することで、コンタクト抵抗の上昇を抑制し、さらにコンタクトにおけるTiの使用を避けられるので、シンター工程におけるTiへの水素吸着による界面準位数の増加を防止でき、暗電流の増大を抑制でき、さらにアロイスパイクも形成されない。

上記の本実施形態に係るCCDは、配線層36を形成するときに、第1実施形態に記載のコヒーレントスパッタリング法を用いて形成することで、その他は一般的な方法により形成可能である。

【0071】

また、図12(b)に示すように、配線層36の上層にさらに酸化シリコンなどの上層絶縁膜21’が形成され、配線層36に達する開口部CHW が開口されており、開口部CHW を埋め込んで配線層36に接続するようにして、銅を含有するアルミニウムからなる上層配線層37が形成される構成とすることも可能である。この場合にも、アルミニウム中の銅の含有量は、第1実施形態における横型オーバーフロードレインにおいてシリコン基板に接続する配線層の場合と同様とする。この例においても、図12(a)に示す構造のCCDと同様の効果を得ることができる。

【0072】

(実施例1)

図13(a)の断面図に示すように、p型シリコン半導体基板10の表層部分に、面積が180×320μm2 で接合深さXjが0.4μmのn+ 領域19を形成し、その上層に全面に酸化シリコンの層間絶縁膜21を形成し、開口径φCHが0.6μmであり、n+ 領域19に達するコンタクトホールを約10000個開口した。

上記のコンタクトホール内を被覆して、全面に、配線層38を形成した。さらに、配線層38の上層に不図示の酸化シリコン膜を形成し、350℃で2時間の熱処理を行い、試料を作成した。

【0073】

上記において、配線層38を形成する条件は下記4条件として、(A)〜(D)の4種の試料を作成した。

上記の配線層38は、それぞれ、(A)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により600nmの膜厚で形成、(B)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により800nmの膜厚で形成、(C)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により1000nmの膜厚で形成、(D)Ti/TiN積層膜をスパッタリング法により成膜してバリアメタルとし、さらにCVD法によりタングステン(W)を堆積して形成した。

【0074】

上記の(A)〜(D)の各試料に対して、350℃の熱処理を行う前後に、それぞれコンタクト部分の透過型電子顕微鏡写真を撮影したところ、各試料とも熱処理の前後でアロイスパイクが形成されている様子は観察されなかった。

【0075】

上記の(A)〜(D)の各試料に対して、n+ 領域19とp型シリコン半導体基板10の間に8Vの逆バイアスを印加したときのリーク電流を測定した。

得られた結果を累積確率に対してプロットしたものが図13(b)である。

この図から、配線層38として(A)〜(C)の0.5重量%の銅を含有するアルミニウムを形成した試料のリーク電流値は、(D)Ti/TiN/Wを成膜した試料と同様であり、0.5重量%の銅を含有するアルミニウムを形成した試料のリーク電流は十分に低く、アロイスパイクが形成されていないことが確認された。

【0076】

(実施例2)

実施例1と同様にして、p型シリコン半導体基板10の表層部分にn+ 領域19を形成し、その上層に全面に層間絶縁膜21を形成し、開口径φCHが1.4μmであり、n+ 領域19に達するコンタクトホールを開口した。

上記のコンタクトホール内を被覆して、全面に、下記3条件にて配線層38を形成して、それぞれ酸化シリコンの上層絶縁膜を積層させた後、350℃で2時間の熱処理を施して、(A)〜(C)の3種の試料を作成した。

上記の配線層38は、それぞれ、(A)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により形成、(B)1.0重量%のシリコンを含有するアルミニウムをスパッタリング法により形成、(C)アルミニウムをスパッタリング法により形成した。

【0077】

上記(A)〜(C)の各試料に対して、リーク電流10nAに達するときのn+ /p接合耐圧を測定した。

得られた結果を累積確率に対してプロットしたものが図14である。

この図から、配線層38として(C)のアルミニウムを用いた試料は、一部接合耐圧が低下して、アロイスパイクが形成されていることを示しているが、(A)の0.5重量%の銅を含有するアルミニウムを用いた試料の接合耐圧は(B)シリコンを含有するアルミニウムと同程度であり、0.5重量%の銅を含有するアルミニウムを用いた試料は十分に高い接合耐圧を有しており、アロイスパイクが形成されていないことが確認された。

【0078】

上記のように、アルミニウム中に銅を添加することで、アルミニウム中のシリコンの固溶限界を低下させることになり、350℃の熱処理に対してアロイスパイクの発生を完全に防止することができる。

【0079】

(実施例3)

実施例1と同様にして、p型シリコン半導体基板10の表層部分にn+ 領域19を形成し、その上層に全面に層間絶縁膜21を形成し、開口径φCHが0.6μmであり、n+ 領域19に達するコンタクトホールを開口した。

上記のコンタクトホール内を被覆して、全面に、下記3条件にて配線層38を形成して、それぞれ酸化シリコンの上層絶縁膜を積層させた後、350℃で2時間の熱処理を施して、(A)〜(D)の4種の試料を作成した。

上記の配線層38は、それぞれ、(A)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により600nmの膜厚で形成、(B)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により800nmの膜厚で形成、(C)0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により1000nmの膜厚で形成、(D)Ti/TiN積層膜をスパッタリング法により成膜してバリアメタルとし、さらにCVD法によりタングステン(W)を堆積して形成した。

【0080】

上記(A)〜(D)の各試料に対して、n+ 領域へのコンタクト抵抗を測定した。

得られた結果を累積確率に対してプロットしたものが図15(a)である。

この図から、配線層38として(A)〜(C)の0.5重量%の銅を含有するアルミニウムを用いた試料のコンタクト抵抗は、若干分布が広がっているものの、(D)Ti/TiN/Wを成膜した試料と同様に十分低い値となっており、シリコンを含有するアルミニウムのようにコンタクト底部にシリコンが析出して高抵抗となることはなかった。

【0081】

また、n型シリコン半導体基板の表層部分にp+ 領域を形成して、上記と同様にp+ 領域へのコンタクト抵抗を測定した。

得られた結果を累積確率に対してプロットしたものが図15(b)である。

配線層38として(A)〜(C)の0.5重量%の銅を含有するアルミニウムを用いた試料のコンタクト抵抗は、n+ 領域へのコンタクト抵抗と同様に十分低く、さらに(D)Ti/TiN/Wを成膜した試料よりも低い値となっていた。

【0082】

(実施例4)

第1実施形態に示す構造と同様の横型オーバーフロードレインを有するCCDを作成した。横型オーバーフロードレイン部分には、リング状のポリシリコンのゲート電極の内径である0.6μmの開口径を有するコンタクトホールを開口し、開口部内に0.5重量%の銅を含有するアルミニウムを遠距離スパッタリング法により形成した試料と、Ti/TiN積層膜をスパッタリング法により成膜してバリアメタルとし、さらにCVD法によりタングステン(W)を堆積して形成した試料を作成した。

さらに、酸化シリコンなどの上層絶縁膜の形成工程やシンター工程などを含む350℃での熱処理時間の総計が2時間程度である処理工程を経て、CCDを完成させた。

上記の各試料の暗電流値を測定した結果、0.5重量%の銅を含有するアルミニウムを用いた試料の暗電流値は、Ti/TiN/Wを成膜した試料の26%程度の値であり、暗電流絶対値として問題がないことが確認された。

【0083】

(実施例5)

実施例4で作成した2種の試料((A)0.5重量%の銅を含有するアルミニウムを用いた試料と、(B)Ti/TiN/Wを成膜した試料に対して、暗電流の温度依存性を測定し、アレニウスプロットから、活性化エネルギーを求めた。

図16(a)および(b)は、それぞれ(A)と(B)の試料の活性化エネルギーの分布を示す図である。

【0084】

Ti/TiN/Wの積層膜が、Siのエネルギーバンドの禁制帯中央部付近(0.65eV)にシャープな分布を示すのに対して、コヒーレントスパッタリング法による銅を含有するアルミニウム合金膜では、ほぼ同様な位置に分布の中心を示すものの、ブロードになっている。即ち、Ti/TiN/W積層膜の使用では、暗電流に対して0.65eV付近の深い準位からの寄与が支配的となるのに対して、銅を含有するアルミニウム合金膜では緩和させる方向にあると結論付けられる。

【0085】

本発明は、上記の実施形態に限定されない。

例えば、本発明の固体撮像装置としては、CCDの他、CMOS撮像素子などの他の固体撮像装置にも適用することが可能である。

また、配線層として銅を含有するアルミニウムを用いるコンタクトとしては、オーバーフロードレインにおけるコンタクトの他、ゲート電極やチャネル分離層に対するコンタクトなど種々のコンタクトに適用可能である。

ゲート電極などは単層構成としているが、2層以上の構成としてもよい。

CCD転送部としては、仮想ゲート構造を有さなくてもよく、単相駆動方式の他、二相以上の駆動方式でもよい。

また、ゲート電極やその他の部材を構成する材料は上記の実施形態に記載したもの以外のものも使用できる。

その他、本発明の要旨を逸脱しない範囲で種々の変更を行うことができる。

【0086】

【発明の効果】

本発明の固体撮像装置によれば、コンタクトの配線材料に銅を含有するアルミニウムを用いることで、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止することができる。

【0087】

また、本発明の固体撮像装置の製造方法によれば、コンタクトの配線材料に銅を含有するアルミニウムを用いることで、暗電流の増大を抑制しながら、コンタクト抵抗の上昇、アロイスパイクの発生を防止した固体撮像装置を製造することができ、さらにコヒーレントスパッタリング法により銅を含有するアルミニウムからなる配線層を形成することで、コンタクト被覆不良の発生を防止することができる。配線層形成以降のシンター工程を含む処理工程を、例えば全て350℃以下の温度で行うことで、効果的にアロイスパイクの発生を防止することが可能である。

【図面の簡単な説明】

【図1】図1は本発明の第1実施形態に係るCCDの平面図である。

【図2】図2(a)は図1中のA−A’における断面図であり、(b)はCCD転送を説明するためのポテンシャル図である。

【図3】図3(a)は本発明の第1実施形態および従来例に係るCCDのオーバーフロードレイン部分の断面図であり、(b)は同一断面におけるポテンシャル図であり、図1中のB−B’における断面に相当する。

【図4】図4は図3に示すオーバーフロードレインを有するCCDの製造方法の製造工程を示す断面図であり、(a)はn型埋め込みチャネルの形成工程まで、(b)はp型領域の形成工程まで、(c)はゲート電極のパターン形成工程までを示す。

【図5】図5は図4の続きの工程を示し、(d)はn+ 領域の形成工程まで、(e)はp+ 反転層の形成工程までを示す。

【図6】図6は図5の続きの工程を示し、(f)は層間絶縁膜の形成工程まで、(g)はn+ 領域に達する開口部の開口工程までを示す。

【図7】図7は本発明の第2実施形態に係るCCDのオーバーフロードレイン部分の断面図である。

【図8】図8は図7に示すオーバーフロードレインを有するCCDの製造方法の製造工程を示す断面図であり、(a)はゲート絶縁膜の形成工程まで、(b)はn型埋め込みチャネルおよび第1p+ 反転層の形成工程まで、(c)は層間絶縁膜への第1開口部の形成工程までを示す。

【図9】図9は図8の続きの工程を示し、(d)はスクリーン酸化膜の形成工程まで、(e)はp型領域の形成工程まで、(f)はサイドウォール絶縁膜用層の形成工程までを示す。

【図10】図10は図9の続きの工程を示し、(g)はサイドウォール絶縁膜の形成工程まで、(h)はn+ 領域の形成工程まで、(i)は第2開口部底部のスクリーン酸化膜の除去工程までを示す。

【図11】図11は本発明の第3実施形態に係るCCDのオーバーフロードレイン部分の断面図である。

【図12】図12(a)および(b)は本発明の第4実施形態に係るCCDのオーバーフロードレイン部分の断面図である。

【図13】図13(a)は実施例1に係るコンタクト構造を有するダイオードの断面図であり、(b)はリーク電流を累積確率に対してプロットした図である。

【図14】図14は実施例2に係る接合耐圧を累積確率に対してプロットした図である。

【図15】図15(a)は実施例3に係るn+ 領域へのコンタクト抵抗値を累積確率に対してプロットした図であり、(b)はp+ 領域へのコンタクト抵抗値を累積確率に対してプロットした図である。

【図16】図16は実施例5に係る暗電流の活性化エネルギー分布を示す図であり、(a)は0.5重量%の銅を含有するアルミニウムを用いた試料、(b)はTi/TiN/Wを成膜した試料である。

【図17】図17は従来例の問題点を示す断面図である。

【図18】図18は従来例の問題点を示す断面図である。

【図19】図19は従来例の問題点を示す断面図である。

【図20】図20(a)は、CCDのオーバーフロードレイン部分にTi/TiN/Wを成膜したときの断面図であり、(b)はシリコンを含有するアルミニウムとTi/TiN/W積層膜との暗電流の差を示す図である。

【符号の説明】

10…p型半導体基板、11…n型埋め込みチャネル、12…p型チャネル分離層、13…第1n+ 領域、14…第2n+ 領域、15…(第1)p+ 反転層、16…第2p+ 反転層、17…p型領域、18,19…n+ 領域、20…ゲート絶縁膜、21…層間絶縁膜、21’…上層絶縁膜、22,22a…スクリーン酸化膜、23…サイドウォール絶縁膜用層、23a…サイドウォール絶縁膜、30…ゲート電極、33…(LOD用)ゲート電極、34…配線層、34a…バリアメタル層、34b…タングステン層、CH,CH1,CH2…開口部、D1〜D8…導電性不純物、R1〜R5…レジスト膜、CS…チャネル分離層、G…ゲート電極、LOD…横型オーバーフロードレイン、CT…電荷転送方向、PC1,PC2…ピクセル、PP…ポリ相、VP…仮想ゲート相。

Claims (6)

- 第1導電型の半導体基板の主面に第2導電型の半導体層を形成する工程と、

上記半導体基板の主面に上記半導体層を区画するための第1導電型の分離領域を形成する工程と、

上記半導体層上に第1の絶縁層を形成する工程と、

上記第1の絶縁層をエッチングすることにより上記分離領域により区画される半導体層の間に上記半導体層が露出する第1の開口部を形成する工程と、

上記第1の絶縁層をマスクとして第1導電型の不純物を注入して第1導電型の第1の半導体領域を形成する工程と、

上記第1の開口部を含む上記第1の絶縁層上に第2の絶縁層を形成する工程と、

上記第2の絶縁層を全面的にエッチングすることにより上記第1の開口部の周縁部に環状の第1の絶縁膜を形成するとともに上記第1の絶縁膜の内側に上記半導体層が露出する第2の開口部を形成する工程と、

上記第1の絶縁膜をマスクとして第2導電型の不純物を注入して上記第1の半導体領域の内側に第2導電型の第2の半導体領域を形成する工程と、

上記第2の開口部を介して上記第2の半導体領域に接続される電極を上記第1の絶縁膜上に形成する工程と、

を有し、

上記分離領域で区画される上記半導体層が受光部を構成し、上記第1の半導体領域と上記第1の絶縁膜と上記第2の半導体領域と上記電極とが電荷掃き捨て部を構成し、上記電極が銅を含有するアルミニウムで構成される、固体撮像装置の製造方法。 - 上記第1の半導体領域の形成のための第1導電型の不純物の注入が全面に形成された第3の絶縁層を介して行なわれる、請求項1に記載の固体撮像装置の製造方法。

- 上記電極がコヒーレントスパッタリング法により形成される、請求項1又は2に記載の固体撮像装置の製造方法。

- 上記電極を形成する工程の後に行われるシンター処理が350℃以下の温度で行われる、請求項1、2又は3に記載の固体撮像装置の製造方法。

- 上記銅の含有量が0.4〜5重量%の範囲にある、請求項1、2、3又は4に記載の固体撮像装置の製造方法。

- 上記銅の含有量が0.5〜0.8重量%の範囲にある、請求項1、2、3又は4に記載の固体撮像装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000101326A JP4635291B2 (ja) | 2000-03-31 | 2000-03-31 | 半導体装置の製造方法 |

| US09/821,936 US6507054B2 (en) | 2000-03-31 | 2001-03-30 | Solid-state imaging device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000101326A JP4635291B2 (ja) | 2000-03-31 | 2000-03-31 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001284569A JP2001284569A (ja) | 2001-10-12 |

| JP4635291B2 true JP4635291B2 (ja) | 2011-02-23 |

Family

ID=18615398

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000101326A Expired - Fee Related JP4635291B2 (ja) | 2000-03-31 | 2000-03-31 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6507054B2 (ja) |

| JP (1) | JP4635291B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001257339A (ja) * | 2000-01-06 | 2001-09-21 | Texas Instr Japan Ltd | 固体撮像装置およびその製造方法 |

| CN100587560C (zh) | 2003-04-01 | 2010-02-03 | 夏普株式会社 | 发光装置用组件、发光装置、背侧光照射装置、显示装置 |

| US20050029553A1 (en) * | 2003-08-04 | 2005-02-10 | Jaroslav Hynecek | Clocked barrier virtual phase charge coupled device image sensor |

| JP4739706B2 (ja) * | 2004-07-23 | 2011-08-03 | 富士フイルム株式会社 | 固体撮像素子及びその製造方法 |

| JP4696596B2 (ja) * | 2005-03-02 | 2011-06-08 | ソニー株式会社 | 撮像素子及び撮像素子の製造方法 |

| JP2007189022A (ja) * | 2006-01-12 | 2007-07-26 | Fujifilm Corp | Ccd型固体撮像素子及びその製造方法 |

| US20080007622A1 (en) * | 2006-06-08 | 2008-01-10 | Eastman Kodak Company | Method of improving solid-state image sensor sensitivity |

| EP2147465B1 (en) * | 2007-03-30 | 2016-02-24 | Panasonic Intellectual Property Management Co., Ltd. | Ccd image pickup device with twofold frame storage portion and method for using the device |

| US8772891B2 (en) * | 2008-12-10 | 2014-07-08 | Truesense Imaging, Inc. | Lateral overflow drain and channel stop regions in image sensors |

| KR20110096033A (ko) * | 2008-12-10 | 2011-08-26 | 이스트맨 코닥 캄파니 | 횡 오버플로우 드레인을 갖는 이미지 센서 |

| JP5679459B2 (ja) * | 2008-12-10 | 2015-03-04 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 横型オーバフロードレインを有するイメージセンサを製造する方法 |

| JP2010232387A (ja) * | 2009-03-26 | 2010-10-14 | Panasonic Corp | 固体撮像素子 |

| JP5300577B2 (ja) * | 2009-04-23 | 2013-09-25 | 三菱電機株式会社 | Tdi方式のイメージセンサ、及び該イメージセンサの駆動方法 |

| US9304283B2 (en) * | 2014-05-22 | 2016-04-05 | Texas Instruments Incorporated | Bond-pad integration scheme for improved moisture barrier and electrical contact |

| US10341590B2 (en) * | 2016-08-12 | 2019-07-02 | Semiconductor Components Industries, Llc | Methods and apparatus for a CCD image sensor |

| KR102750165B1 (ko) * | 2018-08-27 | 2025-01-08 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 제조 방법 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57114253A (en) * | 1981-01-07 | 1982-07-16 | Toshiba Corp | Semiconductor device and manufacture thereof |

| JPS62172754A (ja) * | 1986-01-27 | 1987-07-29 | Canon Inc | フオトセンサ |

| JPS63169063A (ja) * | 1987-01-05 | 1988-07-13 | Nec Corp | 半導体装置 |

| JP2792041B2 (ja) * | 1988-09-08 | 1998-08-27 | 富士ゼロックス株式会社 | イメージセンサ |

| JPH06310508A (ja) * | 1993-04-26 | 1994-11-04 | Kawasaki Steel Corp | 半導体装置の製造方法 |

| JP3310404B2 (ja) * | 1993-07-23 | 2002-08-05 | 浜松ホトニクス株式会社 | 冷却型固体撮像装置 |

| JP3712516B2 (ja) * | 1998-01-13 | 2005-11-02 | 日本テキサス・インスツルメンツ株式会社 | 固体撮像装置及びその製造方法 |

-

2000

- 2000-03-31 JP JP2000101326A patent/JP4635291B2/ja not_active Expired - Fee Related

-

2001

- 2001-03-30 US US09/821,936 patent/US6507054B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6507054B2 (en) | 2003-01-14 |

| JP2001284569A (ja) | 2001-10-12 |

| US20020140003A1 (en) | 2002-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4635291B2 (ja) | 半導体装置の製造方法 | |

| JP2667390B2 (ja) | 半導体装置の製法 | |

| US9514976B2 (en) | Trench isolation implantation | |

| US6177333B1 (en) | Method for making a trench isolation for semiconductor devices | |

| US20060163627A1 (en) | Deuterated structures for image sensors and methods for forming the same | |

| US6962862B2 (en) | Manufacturing method of semiconductor device | |

| US11121169B2 (en) | Metal vertical transfer gate with high-k dielectric passivation lining | |

| JP2005072236A (ja) | 半導体装置および半導体装置の製造方法 | |

| EP0502521B1 (en) | Solid-state image pickup device and method of manufacturing the same | |

| US20040262494A1 (en) | Solid-state imaging device and manufacturing method thereof | |

| US7498253B2 (en) | Local interconnection method and structure for use in semiconductor device | |

| JP2001036062A (ja) | 固体撮像素子の製造方法および固体撮像素子 | |

| US7429496B2 (en) | Buried photodiode for image sensor with shallow trench isolation technology | |

| US20150311306A1 (en) | Metal-oxide-semiconductor (mos) transistor structure integrated with a resistance random access memory (rram) and the manufacturing methods thereof | |

| US7473953B2 (en) | Method for fabricating metallic bit-line contacts | |

| US6716734B2 (en) | Low temperature sidewall oxidation of W/WN/poly-gatestack | |

| US20080124830A1 (en) | Method of manufacturing image sensor | |

| KR100468611B1 (ko) | 암신호 감소를 위한 이미지센서 제조 방법 | |

| JP3381291B2 (ja) | 固体撮像装置およびその製造方法 | |

| KR20060077244A (ko) | 씨모스 이미지 센서 및 그의 제조 방법 | |

| JPS60111457A (ja) | 半導体装置の製造方法 | |

| KR20040003901A (ko) | 반도체 소자의 제조방법 | |

| JPH06120476A (ja) | 固体撮像装置の製造方法 | |

| US20060141779A1 (en) | Method for forming an aluminum contact | |

| KR20000039715A (ko) | 디램의 셀 트랜지스터 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070315 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090928 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635291 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |