JP4589665B2 - 増幅器及びそれを用いた高周波電力増幅器 - Google Patents

増幅器及びそれを用いた高周波電力増幅器 Download PDFInfo

- Publication number

- JP4589665B2 JP4589665B2 JP2004184669A JP2004184669A JP4589665B2 JP 4589665 B2 JP4589665 B2 JP 4589665B2 JP 2004184669 A JP2004184669 A JP 2004184669A JP 2004184669 A JP2004184669 A JP 2004184669A JP 4589665 B2 JP4589665 B2 JP 4589665B2

- Authority

- JP

- Japan

- Prior art keywords

- amplifier

- class

- voltage

- output

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000010354 integration Effects 0.000 claims description 12

- 230000007423 decrease Effects 0.000 claims description 5

- 238000009499 grossing Methods 0.000 claims description 5

- 230000010355 oscillation Effects 0.000 claims description 5

- 230000000694 effects Effects 0.000 claims description 4

- 230000002238 attenuated effect Effects 0.000 claims description 2

- 239000003990 capacitor Substances 0.000 claims description 2

- 230000005669 field effect Effects 0.000 claims 19

- 230000005684 electric field Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 11

- 230000014509 gene expression Effects 0.000 description 11

- 238000004891 communication Methods 0.000 description 10

- 241001125929 Trisopterus luscus Species 0.000 description 4

- 230000003321 amplification Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 238000003199 nucleic acid amplification method Methods 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 1

- 244000145845 chattering Species 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000013016 damping Methods 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 238000007429 general method Methods 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/02—Modifications of amplifiers to raise the efficiency, e.g. gliding Class A stages, use of an auxiliary oscillation

- H03F1/0205—Modifications of amplifiers to raise the efficiency, e.g. gliding Class A stages, use of an auxiliary oscillation in transistor amplifiers

- H03F1/0211—Modifications of amplifiers to raise the efficiency, e.g. gliding Class A stages, use of an auxiliary oscillation in transistor amplifiers with control of the supply voltage or current

- H03F1/0216—Continuous control

- H03F1/0222—Continuous control by using a signal derived from the input signal

- H03F1/0227—Continuous control by using a signal derived from the input signal using supply converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/432—Two or more amplifiers of different type are coupled in parallel at the input or output, e.g. a class D and a linear amplifier, a class B and a class A amplifier

Description

Vbp−Vba≧Vop−Voa, Vba≧Voa−Vom …(1)

である。ピークファクタFp=Vop/Voa、Fm=Vom/Voaを用いると、式(1)は、

Vbp−Vba≧(Fp−1)Voa, Vba≧(1−Fm)Voa …(2)

となる。

Kbp−Kba≧Fp−1, Kba≧1−Fm …(3)

となる。これが、本発明の基本式である。特に、制御係数Kba=1またはKbp=1とした場合には、

Kba=1, Kbp≧Fp, Fm≧0 …(4)

Kbp=1, 2−Fp≧Kba≧1−Fm, 1≧Fp−Fm …(5)

となる。これらの場合は制御が簡単になるので、実用上特に有用である。

Claims (19)

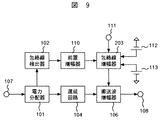

- 入力信号の第1の低周波成分を増幅して、第1の出力信号及び前記第1の出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、

前記入力信号の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給される

ことを特徴とする増幅器。 - 請求項1において、

前記第1の出力信号と前記B級増幅器の電源電圧とが一定比となるように制御される

ことを特徴とする増幅器。 - 請求項2において、

前記一定比は、前記増幅器を用いるシステムのピークファクタとほぼ等しい

ことを特徴とする増幅器。 - 請求項2において、

前記B級増幅器への入力信号の前記第2の低周波成分が前記入力信号の高周波成分に対して減衰している

ことを特徴とする増幅器。 - 請求項1において、

前記DC/DCコンバータは、前記第1の出力信号を出力する第1のS級変調器と前記第2の出力信号を出力する第2のS級変調器とを含んで成る

ことを特徴とする増幅器。 - 請求項1において、

前記増幅器の出力信号を入力信号側に帰還する負帰還ループが形成されている

ことを特徴とする増幅器。 - 請求項1において、

前記増幅器の出力信号にオフセットを付加してオフセット電圧を補正する回路を更に具備する

ことを特徴とする増幅器。 - 請求項5において、

前記第1のS級増幅器の電源電圧よりも高い電源電圧を前記第2のS級増幅器に供給する第2のDC/DCコンバータを具備する

ことを特徴とする増幅器。 - 請求項5において、

前記第1及び第2のS級増幅器にはローパスフィルタを経た前記入力信号が与えられ、前記ローパスフィルタのカットオフ周波数が、前記第1及び第2の出力信号の電圧値を設定するために用いられる鋸歯形信号の周波数よりも低い

ことを特徴とする増幅器。 - 請求項1において、

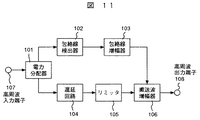

前記増幅器は、

第1のオペアンプと第1および第2の抵抗素子とを含んで成るシュミット回路と、第2のオペアンプと第3の抵抗素子と第1の容量素子とを含んで成る積分回路と、前記第1のオペアンプと前記第2のオペアンプへのバイアス電圧を供給するためのバイアス端子とを含んで成る発振器と、

第4の抵抗素子と第2の容量素子とを含んで成るローパスフィルタと、

第3のオペアンプと第1の電界効果トランジスタと第1のダイオードとを含んで成る第1のS級変調器と、

第4のオペアンプと第2の電界効果トランジスタと第2のダイオードとを含んで成る第2のS級変調器と、

第5のオペアンプと第4および第5の抵抗素子とを含んで成る前段増幅器と、第3および第4の電界効果トランジスタと第3および第4のダイオードと第6および第7の抵抗素子とを含んで成る後段増幅器とを有するB級増幅器と、

前記B級増幅器の入力に接続された第6のオペアンプと、

第7のオペアンプと第5の電界効果トランジスタと第5のダイオードとインダクタと第3の容量素子とを含んで成る昇圧型DC/DCコンバータと、

前記昇圧型DC/DCコンバータの入力に接続された第8のオペアンプとを具備して成り、

前記シュミット回路の出力は前記積分回路に接続され、前記積分回路の出力は前記シュミット回路に帰還され、

前記バイアス端子に電源電圧の略1/2のバイアス電圧が印加されるよう構成され、

前記ローパスフィルタのカットオフ周波数は前記発振器の発振周波数より低くなるよう構成され、

前記第3のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記ローパスフィルタからの入力電圧とを比較して前記第1の電界効果トランジスタをオンオフ動作させるよう構成され、

前記第4のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記ローパスフィルタからの入力電圧とを比較して前記第2の電界効果トランジスタをオンオフ動作させるよう構成され、

前記前段増幅器は前記第6のオペアンプからの入力信号を非反転増幅し、前記後段増幅器は非反転増幅された前記入力信号を電流増幅し、

前記第3および第4のダイオードのバイアス電流は前記第6および第7の抵抗素子から供給され、

前記第7のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記第8のオペアンプからの入力電圧とを比較して前記第5の電界効果トランジスタをオンオフ動作させるよう構成され、

前記第6のオペアンプの出力信号が前記ローパスフィルタに入力され、

前記第3の電界効果トランジスタのソース電極に前記第2のS級変調器の出力信号が供給され、

前記B級増幅器は、前記第6のオペアンプの入力信号の高周波成分を増幅して出力し、前記第1のS級変調器は、前記第6のオペアンプの入力信号の低周波成分を増幅して出力する

ことを特徴とする増幅器。 - 請求項10において、

前記シュミット回路の出力電圧は電源電圧によって示される正または接地電圧によって示される0のいずれかの値を取り、前記シュミット回路の出力電圧が正の場合、前記積分回路の出力電圧は略一定のスロープで減少し、

前記積分回路の出力電圧が前記シュミット回路のしきい電圧より小さい場合、前記シュミット回路の出力電圧は0であり、かつ、前記積分回路の出力電圧は略一定のスロープで増加し、

前記積分回路の出力電圧が前記シュミット回路のしきい電圧より大きい場合、前記シュミット回路の出力電圧は正であり、かつ、前記積分回路の出力電圧は略一定のスロープで減少する

ことを特徴とする増幅器。 - 請求項10において、

前記発振器からの入力電圧は三角波であり、該三角波の周期で前記第1の電界効果トランジスタはオンオフ動作し、

前記ローパスフィルタからの入力電圧が低い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が高い期間が長くなり、前記第1の電界効果トランジスタがオフである期間が長くなり、

前記ローパスフィルタからの入力電圧が高い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が低い期間が長くなり、前記第1の電界効果トランジスタがオンである期間が長くなる

ことを特徴とする増幅器。 - 請求項10において、

前記第1の電界効果トランジスタのソース電極に電源電圧が印加され、前記第1の電界効果トランジスタのオン時に前記第1のS級変調器の出力が前記電源電圧まで上昇し、前記第1の電界効果トランジスタのオフ時に前記第1のS級変調器の出力が前記第1のダイオードにクリップされるまで下降し、

前記第1のS級変調器の出力は平滑化され、前記ローパスフィルタからの入力電圧に比例した信号となる

ことを特徴とする増幅器。 - 請求項10において、

前記第2の電界効果トランジスタのソース電極に前記昇圧型DC/DCコンバータの出力電圧が印加され、前記第2の電界効果トランジスタのオン時に前記第2のS級変調器の出力が前記昇圧型DC/DCコンバータの出力電圧まで上昇し、前記第2の電界効果トランジスタのオフ時に前記第2のS級変調器の出力が前記第2のダイオードにクリップされるまで下降し、

前記第2のS級変調器の出力は平滑化され、前記ローパスフィルタからの入力電圧に比例した信号となる

ことを特徴とする増幅器。 - 請求項10において、

前記昇圧型DC/DCコンバータの昇圧比をjとした場合、前記第2のS級変調器の出力を平滑化した信号レベルは、前記第1のS級変調器の出力を平滑化した信号レベルのj倍である

ことを特徴とする増幅器。 - 請求項10において、

前記第3および第4のダイオードはレベルシフトダイオードであり、前記第3および第4のトランジスタのしきい電圧相当分、信号電圧をシフトさせるものである

ことを特徴とする増幅器。 - 請求項10において、

前記発振器からの入力電圧は三角波であり、該三角波の周期で前記第5の電界効果トランジスタはオンオフ動作し、

前記第8のオペアンプからの入力電圧が高い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が低い期間が長くなり、前記第5の電界効果トランジスタがオフである期間が長くなり、前記昇圧型DC/DCコンバータの出力電圧が増加し、

前記第8のオペアンプからの入力電圧が低い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が高い期間が長くなり、前記第5の電界効果トランジスタがオンである期間が長くなり、前記昇圧型DC/DCコンバータの出力電圧が減少する

ことを特徴とする増幅器。 - 入力された高周波信号を飽和動作によって増幅する搬送波増幅器と、

前記高周波信号の包絡線成分を増幅し、増幅後の出力信号を前記搬送波増幅器の電源電圧として出力する包絡線増幅器とを備え、

前記包絡線増幅器は、

前記高周波信号の包絡線成分の第1の低周波成分を増幅して、第1の出力信号及び前記第1の出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、

前記高周波信号の包絡線成分の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給される

ことを特徴とする高周波電力増幅器。 - 入力された高周波信号を飽和動作によって増幅する搬送波増幅器と、

電源電圧制御信号を入力して該搬送波増幅器の電源電圧を生成する電源電圧調整回路とを備え、

前記電源電圧調整回路は、

前記電源電圧制御信号の第1の低周波成分を増幅して、第1の出力信号及び前記第1の出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、

前記電源電圧制御信号の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給される

ことを特徴とする高周波電力増幅器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004184669A JP4589665B2 (ja) | 2003-08-29 | 2004-06-23 | 増幅器及びそれを用いた高周波電力増幅器 |

| CNB2004100578431A CN100527605C (zh) | 2003-08-29 | 2004-08-19 | 放大器及使用它的高频功率放大器 |

| US10/922,146 US7102427B2 (en) | 2003-08-29 | 2004-08-20 | Amplifier and radio frequency power amplifier using the same |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003305657 | 2003-08-29 | ||

| JP2004184669A JP4589665B2 (ja) | 2003-08-29 | 2004-06-23 | 増幅器及びそれを用いた高周波電力増幅器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005102146A JP2005102146A (ja) | 2005-04-14 |

| JP2005102146A5 JP2005102146A5 (ja) | 2007-04-12 |

| JP4589665B2 true JP4589665B2 (ja) | 2010-12-01 |

Family

ID=34220771

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004184669A Expired - Fee Related JP4589665B2 (ja) | 2003-08-29 | 2004-06-23 | 増幅器及びそれを用いた高周波電力増幅器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7102427B2 (ja) |

| JP (1) | JP4589665B2 (ja) |

| CN (1) | CN100527605C (ja) |

Families Citing this family (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7620371B2 (en) * | 2004-07-30 | 2009-11-17 | Broadcom Corporation | Transmitter signal strength indicator |

| US7317352B2 (en) * | 2004-11-05 | 2008-01-08 | Zarbana Digital Fund Llc | Power amplifier |

| US7869542B2 (en) * | 2006-02-03 | 2011-01-11 | Quantance, Inc. | Phase error de-glitching circuit and method of operating |

| US7933570B2 (en) * | 2006-02-03 | 2011-04-26 | Quantance, Inc. | Power amplifier controller circuit |

| US7761065B2 (en) * | 2006-02-03 | 2010-07-20 | Quantance, Inc. | RF power amplifier controller circuit with compensation for output impedance mismatch |

| CN101401261B (zh) * | 2006-02-03 | 2012-11-21 | 匡坦斯公司 | 功率放大器控制器电路 |

| US8095090B2 (en) * | 2006-02-03 | 2012-01-10 | Quantance, Inc. | RF power amplifier controller circuit |

| US8032097B2 (en) | 2006-02-03 | 2011-10-04 | Quantance, Inc. | Amplitude error de-glitching circuit and method of operating |

| US7917106B2 (en) * | 2006-02-03 | 2011-03-29 | Quantance, Inc. | RF power amplifier controller circuit including calibrated phase control loop |

| JP4836253B2 (ja) | 2006-09-01 | 2011-12-14 | ソニー・エリクソン・モバイルコミュニケーションズ株式会社 | 電力増幅装置および携帯電話端末 |

| JP5022792B2 (ja) * | 2007-07-02 | 2012-09-12 | 株式会社日立国際電気 | Dcdcコンバータユニット、電力増幅器、及び基地局装置 |

| GB0715254D0 (en) | 2007-08-03 | 2007-09-12 | Wolfson Ltd | Amplifier circuit |

| JP2009044268A (ja) * | 2007-08-06 | 2009-02-26 | Sharp Corp | 音声信号処理装置、音声信号処理方法、音声信号処理プログラム、及び、記録媒体 |

| US8451886B2 (en) * | 2007-08-16 | 2013-05-28 | St-Ericsson Sa | Apparatus method and computer readable medium for a transmitter |

| DE102007046341A1 (de) * | 2007-09-27 | 2009-04-23 | Infineon Technologies Ag | Schaltungsanordnung zum Verarbeiten eines hochfrequenten Signals |

| US7970091B2 (en) * | 2007-11-30 | 2011-06-28 | Nautel Limited | Method for reducing spectral regrowth in a spectrally efficient digital modulation scheme |

| JP5081612B2 (ja) * | 2007-12-26 | 2012-11-28 | 株式会社日立国際電気 | 電源回路並びにそれを用いた電力増幅器及び基地局装置 |

| JP5472115B2 (ja) | 2008-10-16 | 2014-04-16 | 日本電気株式会社 | 電力増幅器 |

| GB2465146B (en) * | 2008-11-04 | 2014-05-28 | Nujira Ltd | Improved power supply stage |

| US8666337B2 (en) | 2010-03-05 | 2014-03-04 | Skyworks Solutions, Inc. | System and method for power amplifier control saturation detection and correction |

| US8493141B2 (en) | 2010-04-19 | 2013-07-23 | Rf Micro Devices, Inc. | Pseudo-envelope following power management system |

| JP5355496B2 (ja) * | 2010-05-24 | 2013-11-27 | 三菱電機株式会社 | バイアス制御増幅器 |

| JP2011259083A (ja) * | 2010-06-07 | 2011-12-22 | Renesas Electronics Corp | Rf電力増幅装置およびその動作方法 |

| WO2012047738A1 (en) | 2010-09-29 | 2012-04-12 | Rf Micro Devices, Inc. | SINGLE μC-BUCKBOOST CONVERTER WITH MULTIPLE REGULATED SUPPLY OUTPUTS |

| US8975960B2 (en) | 2011-02-01 | 2015-03-10 | Mediatek Singapore Pte. Ltd. | Integrated circuit wireless communication unit and method for providing a power supply |

| US9166538B2 (en) | 2011-02-01 | 2015-10-20 | Mediatek Singapore Pte. Ltd. | Integrated circuit wireless communication unit and method for providing a power supply |

| US8665018B2 (en) | 2011-02-01 | 2014-03-04 | Mediatek Singapore Pte. Ltd. | Integrated circuit, wireless communication unit and method for a differential interface for an envelope tracking signal |

| US8803605B2 (en) | 2011-02-01 | 2014-08-12 | Mediatek Singapore Pte. Ltd. | Integrated circuit, wireless communication unit and method for providing a power supply |

| US20120287952A1 (en) * | 2011-05-10 | 2012-11-15 | Honeywell International Inc. | Apparatus and methods for high voltage amplification with low noise |

| US9002303B2 (en) * | 2011-05-27 | 2015-04-07 | Samsung Electronics Co., Ltd. | Method and apparatus for programmable envelope shaping circuit based on piecewise linear interpolation |

| US8698558B2 (en) * | 2011-06-23 | 2014-04-15 | Qualcomm Incorporated | Low-voltage power-efficient envelope tracker |

| US9813036B2 (en) | 2011-12-16 | 2017-11-07 | Qorvo Us, Inc. | Dynamic loadline power amplifier with baseband linearization |

| WO2014018861A1 (en) * | 2012-07-26 | 2014-01-30 | Rf Micro Devices, Inc. | Programmable rf notch filter for envelope tracking |

| JP6315834B2 (ja) * | 2012-08-10 | 2018-04-25 | 日本テキサス・インスツルメンツ株式会社 | スイッチトモードアシストリニアレギュレータ |

| US8754707B2 (en) * | 2012-10-24 | 2014-06-17 | Qualcomm Incorporated | Boost converter control for envelope tracking |

| CN103795352A (zh) * | 2012-10-30 | 2014-05-14 | Dsp集团有限公司 | 包含微调单元的dc-dc转换器 |

| US9627975B2 (en) | 2012-11-16 | 2017-04-18 | Qorvo Us, Inc. | Modulated power supply system and method with automatic transition between buck and boost modes |

| WO2014116933A2 (en) | 2013-01-24 | 2014-07-31 | Rf Micro Devices, Inc | Communications based adjustments of an envelope tracking power supply |

| US9250694B1 (en) * | 2013-05-10 | 2016-02-02 | Sridhar Kotikalapoodi | Method and apparatus for fast, efficient, low noise power supply |

| CN103490735A (zh) * | 2013-09-12 | 2014-01-01 | 昆山新金福精密电子有限公司 | 一种高频放大器 |

| KR102114726B1 (ko) * | 2013-10-23 | 2020-06-05 | 삼성전자주식회사 | 전력 증폭 장치 및 방법 |

| US9614476B2 (en) | 2014-07-01 | 2017-04-04 | Qorvo Us, Inc. | Group delay calibration of RF envelope tracking |

| US9912297B2 (en) | 2015-07-01 | 2018-03-06 | Qorvo Us, Inc. | Envelope tracking power converter circuitry |

| US9941844B2 (en) | 2015-07-01 | 2018-04-10 | Qorvo Us, Inc. | Dual-mode envelope tracking power converter circuitry |

| US11121620B2 (en) | 2016-01-29 | 2021-09-14 | Dolby Laboratories Licensing Corporation | Multi-channel cinema amplifier with power-sharing, messaging and multi-phase power supply |

| US9973147B2 (en) | 2016-05-10 | 2018-05-15 | Qorvo Us, Inc. | Envelope tracking power management circuit |

| US10476437B2 (en) | 2018-03-15 | 2019-11-12 | Qorvo Us, Inc. | Multimode voltage tracker circuit |

| CN109314491B (zh) * | 2018-03-16 | 2022-08-16 | 深圳市汇顶科技股份有限公司 | 功率放大器及平衡数字输出信号的上升和下降时间的方法 |

| US11444577B2 (en) | 2019-06-07 | 2022-09-13 | Samsung Electronics Co., Ltd. | Boost amplifier |

| CN111176278B (zh) * | 2019-12-31 | 2023-05-09 | 宁波奇亚园林工具有限公司 | 一种基于交流磁场的智能割草机传感器控制电路与方法 |

| CN113055782A (zh) * | 2021-02-02 | 2021-06-29 | 头领科技(昆山)有限公司 | 一种分频优化处理的音频芯片及耳机 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3486128A (en) * | 1968-02-07 | 1969-12-23 | Us Army | Power amplifier for amplitude modulated transmitter |

| JPS55149512A (en) * | 1979-05-10 | 1980-11-20 | Nippon Gakki Seizo Kk | Amplifier |

| JPH06252647A (ja) * | 1993-03-01 | 1994-09-09 | Kokusai Electric Co Ltd | Ssb放送機の高電力段変調方式 |

| JPH10224159A (ja) * | 1996-11-26 | 1998-08-21 | Motorola Inc | 時間遅延補償広帯域クラスs変調器およびその方法 |

| JP2001519612A (ja) * | 1997-10-06 | 2001-10-23 | モトローラ・インコーポレイテッド | 高周波数広帯域電力増幅器 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69426650T2 (de) * | 1994-11-07 | 2001-09-06 | Alcatel Sa | Mischer für Sender, mit einem Eingang im Strom-Modus |

| US6130910A (en) * | 1997-11-03 | 2000-10-10 | Motorola, Inc. | Method and apparatus for high efficiency wideband power amplification |

| US6590940B1 (en) * | 1999-05-17 | 2003-07-08 | Ericsson Inc. | Power modulation systems and methods that separately amplify low and high frequency portions of an amplitude waveform |

| JP4014072B2 (ja) * | 2000-03-31 | 2007-11-28 | 株式会社ルネサステクノロジ | 電力増幅器モジュール |

-

2004

- 2004-06-23 JP JP2004184669A patent/JP4589665B2/ja not_active Expired - Fee Related

- 2004-08-19 CN CNB2004100578431A patent/CN100527605C/zh not_active Expired - Fee Related

- 2004-08-20 US US10/922,146 patent/US7102427B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3486128A (en) * | 1968-02-07 | 1969-12-23 | Us Army | Power amplifier for amplitude modulated transmitter |

| JPS55149512A (en) * | 1979-05-10 | 1980-11-20 | Nippon Gakki Seizo Kk | Amplifier |

| JPH06252647A (ja) * | 1993-03-01 | 1994-09-09 | Kokusai Electric Co Ltd | Ssb放送機の高電力段変調方式 |

| JPH10224159A (ja) * | 1996-11-26 | 1998-08-21 | Motorola Inc | 時間遅延補償広帯域クラスs変調器およびその方法 |

| JP2001519612A (ja) * | 1997-10-06 | 2001-10-23 | モトローラ・インコーポレイテッド | 高周波数広帯域電力増幅器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7102427B2 (en) | 2006-09-05 |

| JP2005102146A (ja) | 2005-04-14 |

| US20050046474A1 (en) | 2005-03-03 |

| CN100527605C (zh) | 2009-08-12 |

| CN1592089A (zh) | 2005-03-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4589665B2 (ja) | 増幅器及びそれを用いた高周波電力増幅器 | |

| US7965140B2 (en) | Power amplifier | |

| CN101401261B (zh) | 功率放大器控制器电路 | |

| US7808323B2 (en) | High-efficiency envelope tracking systems and methods for radio frequency power amplifiers | |

| US7642847B2 (en) | Power supply processing for power amplifiers | |

| US7554394B2 (en) | Power amplifier circuit | |

| EP1898521B1 (en) | Power amplifying apparatus and mobile communication terminal | |

| EP1638204A1 (en) | Power amplifier and transmitter | |

| US20050127992A1 (en) | Power control and modulation of switched-mode power amplifiers with one or more stages | |

| WO2009125555A1 (ja) | 高周波増幅器 | |

| US8198950B2 (en) | Power amplifier | |

| JP5275590B2 (ja) | 増幅回路 | |

| JP2002084144A (ja) | 電力増幅器および無線通信装置 | |

| US8432228B1 (en) | Power control circuit for radio frequency power amplifiers | |

| US7701285B2 (en) | Power amplifiers having improved startup linearization and related operating methods | |

| US7265627B2 (en) | Self adaptable bias circuit for enabling dynamic control of quiescent current in a linear power amplifier | |

| EP1344312B1 (en) | Linearized class c amplifier with dynamic biasing | |

| JP2689011B2 (ja) | 線形送信装置 | |

| CN112803905B (zh) | 一种补偿电路 | |

| KR102221543B1 (ko) | 전력 증폭 회로 | |

| US6600344B1 (en) | Predistortion circuit for RF detector | |

| JP2010283556A (ja) | 高周波増幅器及びそれを用いた高周波モジュール | |

| JP4549163B2 (ja) | Eerシステム及びeerシステムにおける高周波飽和増幅器の効率最適化調整方法 | |

| JP2006093896A (ja) | E級増幅器、及びeer変調増幅装置 | |

| JP5389567B2 (ja) | 高周波増幅器および高効率化方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070223 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070223 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070223 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090915 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090929 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091126 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100510 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100805 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100824 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100910 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130917 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |