JP4548561B2 - プラズマエッチング中のマスクの腐食を軽減する方法 - Google Patents

プラズマエッチング中のマスクの腐食を軽減する方法 Download PDFInfo

- Publication number

- JP4548561B2 JP4548561B2 JP2000530927A JP2000530927A JP4548561B2 JP 4548561 B2 JP4548561 B2 JP 4548561B2 JP 2000530927 A JP2000530927 A JP 2000530927A JP 2000530927 A JP2000530927 A JP 2000530927A JP 4548561 B2 JP4548561 B2 JP 4548561B2

- Authority

- JP

- Japan

- Prior art keywords

- mask

- power cycle

- cycle

- etching

- during

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32623—Mechanical discharge control means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32697—Electrostatic control

- H01J37/32706—Polarising the substrate

Description

【発明の背景】

この発明は、半導体集積回路(IC’s)の製造に関し、特に、基板層内の特徴部をエッチングする際に、マスクが腐食されるのを軽減する技術に関する。

【0002】

例えばフラットパネルディスプレイや集積回路等の半導体製品の製造では、堆積および/またはエッチングの工程が複数回実施される。堆積の工程では、基板の表面(ガラスパネルまたはウエハの表面等)上に、材料が堆積される。これに対してエッチングの工程は、基板表面上の所定の領域から材料を除去することを目的として実施される。

【0003】

エッチングの工程において、フォトレジスト等の適切なマスク材料で形成されたマスクは、フォトレジスト層の下地層においてエッチングされるべき領域を確定するのに使用される。代表的なフォトレジスト技術では、先ず、エッチングする予定の下地層の上にフォトレジスト層を堆積させる。続いて、フォトレジスト材料を、適切なリソグラフィシステム内で露光させてパターン形成し、現像することにより、後段のエッチング工程を容易にするためのマスクを形成する。適切なエッチャントを使用すると、下地層のうちマスクで保護されていない領域が、適切なエッチャントソースガスでエッチングされて、下地層内にトレンチ(溝)またはビア(管)等の特徴部が形成される。

【0004】

議論を容易にするため、図1に、マスク102と、下地層104と、基板106とを含んだ代表的な基板スタック100を示した。上述したように、マスク102はフォトレジストマスクとして形成しても良いし、または、ハードマスク材料を含む任意の適切なマスク材料で形成されていても良い。下地層104は、エッチングされる予定の1枚またはそれ以上の層として示した。議論を容易にするため、ここで言う下地層は不伝導性の層(例えば、ドーピングされたまたはドーピングされていないシリコン二酸化物含有層)を表わしているが、用途に応じ、例えばポリシリコンや金属等を含む任意のエッチング可能な材料で形成されても良い。基板106は、エッチングされる予定の層の下に存在する層および特徴部を含み、半導体ウエハやガラスパネル自体を含んでも良い。基板106の組成は、本発明の目的に無関係である。

【0005】

マスク102内には、マスクのパターン形成で形成される開口部108が示されている。エッチャント(またはこのようなエッチャントから形成されたプラズマ)は、開口部108を経て下地層104の材料と反応し、下地層内の特徴部(例えばビア(管)またはトレンチ(溝))をエッチングする。

【0006】

どんな従来のエッチングにおいても、その課題とするところは、望ましい垂直なエッチングプロファイルを保ちながら、且つ保護マスクに不必要なダメージを与えることなく、高いエッチング速度で下地層をエッチングすることができるエッチング工程を実現することであった。なかでも後者の要件は、もしエッチング中の不注意でマスクが損傷されると、下地層のうち保護マスク材料の下に配置された領域がエッチングされ、結果として得られる半導体製品に欠陥が生じてしまうため、特に重要である。

【0007】

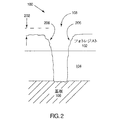

マスクの腐食に関する議論を明確にするため、図2に、従来のプラズマエッチング工程を使用して基板スタック100をエッチングした結果を示した。図2からわかるように、マスクの腐食が原因で、マスク102は図中の厚さ202のように幾らか除去される。マスク102内の開口部108付近では、マスク材料が垂直方向(大量のロス202の原因となる)と水平方向の両方向に腐食されて、ファセット206を形成する。図2には示されていないが、マスクが過度に腐食されると、下地材料層104がエッチャントに曝されるのに十分な大きさのファセットが形成されて、開口部108付近の下地層104を損傷させる恐れが生じる。

【0008】

マスクの腐食は、現代の高密度集積回路の製造において解決すべき、大きな課題である。回路のより一層の高密度化を達成するため、現代では、より細いデザインルールにもとづいて集積回路を縮小している。その結果、集積回路上の隣接したデバイス間を最小単位で分離するケースが徐々に増加してきた。例えば、高密度集積回路の製造において、0.18ミクロンまたはそれ以下のデザインルールが利用されることは珍しくない。この場合、隣接したデバイス同士がより密集して配置されるため、マスク層の最大許容厚さに限界が生じる。これは、例えば使用したデザインルールに対してマスクが徒に厚いと、エッチングのためのマスクを適切にパターン形成することができない可能性があるためである。マスク層は、高密度集積回路の細いデザインルールに対応してどんどん薄くせざる得ない。従って、マスクが予定外の腐食を受けないようにするためには、エチャントに対するマスクの選択性がますます重要となる。以上から、望ましい垂直なエッチングプロファイルをほぼ維持するとともに、全体のエッチング速度およびマスクの選択性を最大化できるような、エッチング工程が必要とされていることがわかる。

【0009】

【発明の概要】

一実施形態を通して理解される本発明は、マスクの下に存在する第1の層内に特徴部をエッチングする際に、マスクの腐食を軽減する方法に関する。第1の層は、基板上に配置されており、基板は、プラズマ処理チャンバ内のチャック上に配置されている。この方法は、プラズマ処理チャンバ内にエッチャントソースガスを流し、そのエッチャントソースガスからプラズマを形成する工程を含む。この方法はさらに、ラジオ波(RF波)電源を既定のパルス周波数で拍動させ、拍動されたラジオ波電力をチャンクに供給する工程を含む。拍動されたラジオ波電力は、第1の周波数を有し、パルス周波数で、高電力サイクルと低電力サイクルとを交互に切り換える。パルス周波数は、低電力サイクル時にマスク上にポリマが堆積し得るように、十分低い周波数が選択される。

【0010】

別の一実施形態における本発明は、フォトレジストマスクの下地層である不導電性の層内にビア(管)をエッチングする際の、フォトレジストの選択性を向上させるための方法に関する。不導電性の層はウエハ上に配置されており、ウエハは、プラズマ処理チャンバ内のチャック上に配置されている。この方法は、プラズマ処理チャンバ内にエッチャントソースガスを流す工程を含む。エッチャントソースガスは、フッ化炭化水素含有ガスと本質的に不活性なガスとを含む。この方法はさらに、第1のラジオ波電力の波形を、プラズマ処理チャンバに関連付けられた第1の電極に供給する工程を含む。この方法はまた、エッチャントソースガスからプラズマを形成する段階を含む。エッチャントソースガスは、フッ化炭化水素含有ガスを含む。また、拍動されたラジオ波電力の波形をチャックに供給する工程も含まれる。拍動されたRF電力の波形は、第1の周波数を有し、パルス周波数において高電力サイクルと低電力サイクルとを交互に繰り返す。低電力サイクル時の最大電力レベルおよびそのパルス周波数は、低電力サイクル時にマスク上にポリマが堆積し得るように選択される。

【0011】

以下の詳細な説明および各種図面により、本発明の上記およびその他の利点を、より一層明らかにする。

【0012】

【発明の実施の形態】

添付の図面に示される幾つかの好ましい実施形態に関連させて、以下、本発明を詳細に説明する。以下の説明では、本発明の完全な理解を促すために多くの項目を特定している。しかしながら、当業者には明らかなように、本発明は、これらの項目の一部または全てを特定しなくても実施することができる。また、本発明の説明の簡明さを図って、周知の処理工程および/または構造の説明は省略した。

【0013】

本発明の一特徴部によれば、拍動するラジオ波(以下、「RF」と記載する)バイアス電力を使用して、プラズマ処理システム内で基板スタックをエッチングすることにより、マスクの腐食を最小化することができるという利点が得られる。ここで言う「マスク」は、例えばポリシリコン、フォトレジスト、またはハードマスク材料等を含む、あらゆるタイプのマスク材料を含む概念である。エッチングは、基板がプラズマ処理チャンバ内のチャック上に配置されている際に実施される。既定のRF周波数を有する拍動されたRF電力は、チャックに供給され、既定のパルス周波数において高電力サイクルと低電力サイクルとを交互に繰り返す。パルス周波数、デューティサイクル、および電力レベルを適切に選択し、拍動されたRFバイアス電力が低電力サイクルにある際に、マスクの表面上にポリマが堆積できるようにすることにより、マスクの腐食を全体的に軽減することができる。高電力サイクル時には、マスク内の開口部を経て下地層がエッチングされる。一実施形態では、高電力サイクル時のパルス周波数、デューティサイクル、および電力レベルを適切に選択し、エッチングされた特徴部の側壁および底部に沿って堆積されたポリマを好ましい形でほぼ全て除去することにより、エッチングプロファイルを改善することができる。

【0014】

本発明によるマスクの腐食を軽減するための技術は、RF電力の供給が低電力レベルと高電力レベルの間で拍動され得る任意の適切なプラズマ処理システム内で、実施できると考えられる。例えば、本発明にもとづくエッチングは、ドライエッチング、プラズマエッチング、反応性イオンエッチング(RIE)、または磁気強化反応性イオンエッチング(MERIE)等に適合した、任意の周知のプラズマ処理装置内で実施することができる。これは、プラズマへのエネルギ供給が、静電結合平行電極板、電子サイクロトロン共鳴(ECR)ソース、マイクロ波プラズマソース、または、ヘリコン共振器、ヘリカル共振器、および誘導コイル(平面状または非平面状によらない)等の誘導結合RFソースのいずれを通じてなされるかに無関係である。なかでもECRおよびTCPブランド(トランス結合プラズマ)のプラズマ処理システムは、カリフォルニア州フリーモント市に所在のラム・リサーチ・コーポレーションから入手することができる。

【0015】

上述したように、任意の従来型および適切なプラズマ処理システムの利用が可能であるが、本発明の一実施形態は、ラム・リサーチ・コーポレーションから入手可能なTCP(商標)9100低圧・高密度プラズマリアクタで実施するものとした。図3は、プラズマ処理チャンバ302を含むプラズマリアクタ300(TCP9100)の概略を描いた図である。チャンバ302の上方には電極304が配置されており、この電極304は、図3の例では誘導コイルで具現化されている。コイル304は、整合回路網(図3には示されていない)を介してRFジェネレータ306により通電される。コイル304に供給されるRF電力は、例えばその周波数を、13.56MHz等のRF周波数とすることができる。

【0016】

チャンバ302内には、ガス分布プレート308が提供される。このプレートは、望ましくは、複数の穴を備え、エッチャントソースガス等のガス状のエッチャントソース材料を、この複数の穴と基板310の間に位置するRF誘導プラズマ領域に分布させる。ガス状のソース材料はまた、チャンバの側壁自体に組み込まれたポートから放出されるものとしても良い。基板310は、チャンバ302に導入されてチャック312上に配置される。このチャック312は、底部電極として作用し、高周波ジェネレータ314により(加えて典型的には整合回路網を介して)バイアスをかけられることが好ましい。RFジェネレータ314に供給されるRFエネルギは、例えば4MHzのRF周波数を有していても良いが、その他のRF周波数を使用しても良い。チャック312は、任意の適切なワークホルダを用いることができ、例えば静電(ESC)チャック、メカニカルチャック、および真空チャック等で具現されても良い。プラズマエッチング中は、チャンバ内の圧力を低く維持することが好ましく、例えば一実施形態における圧力は約1〜50ミリトールである。

【0017】

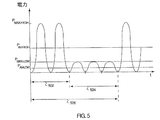

本発明の一特徴によれば、エッチング中のマスクの腐食を軽減するために、例えばチャック312等の底部電極に供給されるRFバイアス電力を、既定のパルス周波数で高電力レベルと低電力レベルの間で交互に繰り返させる。本発明のこの特徴に関する議論を明確するため、従来技術によるエッチングにおける典型的な連続したRFバイアス電力の波形と、本発明にもとづいてマスクの腐食を軽減するために利用される拍動されるRFバイアス電力の波形との対比を、図4および図5に示した。図4からわかるように、従来技術による連続したRFバイアス電力の波形は、例えば4MHzの既定のRF周波数と、既定の最大電力レベルPMAXとを有し、これらから平均電力レベルPAVを得ることができる。図4に示される従来技術によるRFバイアス電力の波形は、エッチング時のその振幅が既定の最大電力レベルPMAX から変化しないことから、連続していると考えられる。

【0018】

図5において、RF電力は(本発明では一定のRF周波数は必要とされないものの)やはり既定のRF周波数で供給される。しかしながら、図4の連続したRFバイアス電力の波形と異なり、図5に示されたRFバイアス電力の波形の最大振幅は、高電力レベルPMAX-HIGHと低電力レベルPMAX-LOW との間で交互に繰り返される。このため、低電力サイクル時にチャック電極に送られる平均電力(PAV-LOW)は、高電力サイクル時にチャック電極に送られる平均電力(PAV-HIGH)よりも小さい。RFバイアス電力の波形は、図示されたパルス時間(506)の逆数である既定のパルス周波数fPULSE を1サイクルとして、低電力レベルと高電力レベルとを交互に繰り返す。デューティサイクルは、高電力サイクル(502)の継続時間のパルス時間(506)に対する比で定義される。

【0019】

本発明の一実施形態によれば、パルス周波数(すなわち、チャック電極に供給されるRF電力が、低電力レベルと高電力レベルとを繰り返す際の周波数)は、低電力サイクル時にポリマがマスク表面に堆積し得るように、十分低く選択される。高電力サイクルの開始時において、この堆積されたポリマは、その下に存在するマスク材料に何らかの保護を与える犠牲層として作用する。このため、たとえ堆積されたポリマが高電力サイクル時に全厚さに渡って腐食されたとしても、同サイクルの開始時には堆積されたポリマが存在するため、マスク材料が同サイクル中にエッチャント材料に曝される時間は短く、このためエッチングにより失われるマスク材料を低減することができる。

【0020】

本発明のこの特徴は、通常のプラズマエッチング工程では2つの独立したメカニズムが互いに競合して作動している、という認識から導かれるものである。一般に、下地層のエッチング時には、チャック電極に供給されるRF電力によって、プラズマからのイオンが基板の表面に向かって加速され、下地層のうちマスク内の開口部に露出した領域がエッチングされる。同時に、基板上、ならびにエッチングされた特徴部の側壁および底部に沿って、ポリマが堆積される。堆積されたポリマは、エッチングの際に、例えばエッチャントの攻撃から側壁を保護してエッチングプロファイルを保つ等の有用な機能を果たすことができる。

【0021】

また一般に、チャック電極に供給されるRF電力が低下すると、ポリマの堆積が増加して、マスクの腐食が軽減される(すなわちマスクの選択性が増加する)。しかしながら、チャック電極に供給されるRF電力が低下すると、イオンのエネルギが減少するため、結果として全体のエッチング速度が低下してしまう。RFバイアス電力が、フォトレジストマスクのエッチング速度または腐食速度、および下地層のエッチング速度におよぼす影響を明らかにするため、図6に、仮想的なエッチング工程におけるエッチング速度とRFバイアス電力の関係を示した。理解を容易にするため、図6におけるRF電力の波形は、連続である(すなわち拍動されていない)と想定した。

【0022】

図6の曲線602は、下地層(例えば、マスクの下に存在する不導電性の層)がエッチングされる速度を示す。図6に示されるように、下地層のエッチングは、RFバイアス電力が既定値PA を上回る場合に生じる。RFバイアス電力が既定値PA の場合は、エッチングのメカニズムとポリマの堆積メカニズムとが打ち消し合う結果、下地層に対するエッチング速度はゼロになる。RFバイアス電力が既定値PA を下回る場合は、ポリマの堆積メカニズムが優勢となり、下地層がエッチングされることなくポリマが堆積される。

【0023】

曲線604は、RFバイアス電力の一機能としてマスクがエッチングまたは腐食される速度を示す。マスクの腐食は、RFバイアス電力が既定値PB を上回る場合に生じる。RFバイアス電力が既定値PB の場合は、エッチングのメカニズムとポリマの堆積メカニズムとが打ち消し合う結果、マスクに対するエッチング速度はゼロになる。RFバイアス電力が既定値PB を下回る場合は、ポリマの堆積メカニズムが優勢となり、マスクがエッチングされることなくポリマが堆積される。

【0024】

図6に示されるように、下地層のエッチングは、マスクの腐食がほぼ最小化されるPA とPB の間においても生じ得る。しかしながら、連続したRF電力を、上記状況でのみエッチングが生じるレベルまで低下させた場合、このエッチング速度は、一般に実用的であるには小さすぎる。さらに、エッチングの進行にともない特徴部の深さが増すと、特徴部の底部に到達するイオン数が減少するため、特徴部の底部におけるエッチング速度が、下地層のエッチングを生じないレベルまで低下する。このため、連続RF電力波形を使用した従来技術にもとづくエッチングでは、PB より実質的に大きい値に設定した連続RFバイアス電力を利用することにより、エッチング速度を増加させ、あるいは速度を増加させないとしても、エッチングされる特徴部の深さが増してもエッチングが確実に持続するようにしている。

【0025】

以上から、RFバイアス電力の電力レベルを、低電力レベル(例えば、ポリマがマスク上に堆積できるようになる値PB より下)と高電力レベル(例えば、下地層のエッチングは増加するが堆積されたポリマ/マスクの腐食もまた増加する値PA より上)で交互に繰り返すことにより、マスクの腐食を軽減できると考えられる。また、低電力サイクル時にマスク上に堆積されるポリマは、高電力サイクルの再開時に先ず腐食される犠牲層の役割を果たすことが、本発明の発明者らによって確認されている。このようにすれば、たとえ堆積されたポリマが高電力サイクル時のある時点で全てエッチングされた場合であっても、やはりマスク材料の腐食を軽減することができる。

【0026】

さらに、ポリマは、マスクの表面上での方が、エッチングされた特徴部の底部または側壁に沿ってよりも速く堆積することが、本発明の発明者らによって確認されている。低電力サイクル時に、エッチングされた特徴部の側壁および底部に沿ってポリマが堆積されることは少ないため、ポリマの堆積物が原因で、下地層の底部におけるエッチング速度が大きく低下したり、エッチングプロファイルが(ポリマが側壁に過度に堆積することが原因で)大きく劣化したりすることはない。場合によっては、ポリマがマスク上に堆積される間、エッチングされた特徴部の底部にはポリマが少量しかまたは全く堆積されない(または、下地層が幾らかエッチングされることもある)ように、低電力サイクル時のエッチングの条件(例えば、電力レベル、デューティサイクル、パルス周波数等)を設定することが可能である。高電力サイクル時のエッチングの内容は、低電力サイクル時に特徴部の側壁および底部に沿って堆積されたポリマが、高電力サイクル時にほぼ全て除去されることにより、エッチングプロファイルの保持、および下地層のエッチングの促進が図れるように、構成されることが好ましい。

【0027】

低電力サイクル時にポリマが堆積できるように、パルス時間を十分小さくすることが重要である。パルス周波数が高すぎる場合、例えば大抵のプラズマ処理システムに関してパルス周波数が1kHzより大きい場合は、低電力サイクル時におけるポリマの堆積は生じない。理論に拘束されることは望まないが、ポリマの堆積は、RFバイアス電力の波形が高電力サイクルから低電力サイクルに移行した直後には生じないと考えられる。これは、基板、チャック、および関連の電子部品が、RF電力レベルが変化する際に、無視し得ないのキャパシタンスおよび自然な傾斜速度(充放電時間)を有しているためである。さらに、プラズマからのイオンは、通常、ある程度の大きさの慣性を幾らか有しており、エネルギを失うまでに(すなわち、エッチングメカニズムを減少させるまでに)時間が必要だと考えられる。従って、高電力レベルから低電力レベルに移行してからマスク上でポリマの堆積が生じるまでに、幾らかの時間が必要である。このため、パルス周波数がポリマの堆積を生じ得るほど十分に小さくすれば、RFバイアス電力を高電力レベルと低電力レベルの間で単に繰り返させるだけでは、マスクの選択性を改善できる形でポリマを堆積させることができる。これは、低電力サイクルごとにデューティサイクルを低く維持した場合でも同様である。

【0028】

図7ないし図9は、各レベルのRFバイアス電力が、代表的な基板スタック上におけるエッチングのメカニズムおよびポリマの堆積メカニズムにおよぼす影響を示した図である。図7において、RFバイアス電力レベルはゼロに設定されている。この例では、ゼロのRFバイアス電力レベル(または非常に低いRFバイアス電力レベル)により、マスク702の上、ならびにエッチングされた特徴部704の側壁および底部に沿って、ポリマが堆積される。しかしながら、エッチングされた特徴部の側壁および底部に沿ってよりも、マスク702の上の方で、より多くのポリマが堆積される。高電力サイクル時には、エッチングされた特徴部の底部に沿って堆積されたポリマが除去されて、下地層706のエッチングが進行する。高電力サイクル時のマスクの腐食は、マスク上面に沿って堆積された分厚いポリマによって阻止される。

【0029】

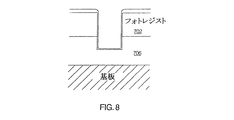

RFバイアス電力の増大がエッチングにおよぼす影響を示すため、図8に示す例では、RFバイアス電力レベルを、図7におけるRF電力レベルよりも高く設定した。この例では、マスク702の上にポリマが堆積されている。しかしながら、RFバイアス電力レベルが高いため、エッチングされた特徴部の側壁および底部に沿って低電力サイクル中に堆積されるポリマは、たとえあるとしてもごく僅かである。さらに、この低電力サイクル中には下地層のエッチングも幾らか生じ得る。図6と関連させて上述したように、下地層のエッチングは、マスク表面上においてポリマの堆積が続いている際にも生じ得る。高電力サイクルが再開すると、特徴部の底部におけるエッチングが続行する一方で、マスク表面上に堆積された分厚いポリマによってマスクの腐食が阻止される。

【0030】

高電力サイクル中の効果を示すため、図9に示す例では、RFバイアス電力を、図7または図8の場合よりもさらに高く設定した。RFバイアス電力のレベルが比較的高い場合は、下地層706が、大きくエッチングされる。この高電力サイクルに低電力サイクルが先立つ場合は、その先立つ低電力サイクル中に堆積されたポリマの大部分(または全て)が除去されることが好ましい。マスク材料のうちの幾らかは、高電力サイクルの終了時にようやく除去される可能性があるが、堆積されたポリマが高電力サイクルの開始時に存在することにより、高電力サイクル時に除去されるマスク材料の量を少なく抑えることができる。

【0031】

エッチングを最適化して各基板スタックの必要を満たすためには、パルス周波数を変化させることができる。パルス周波数が低くなると、ポリマの堆積速度(よってマスクの選択性)は一般に増加する。エッチング工程をさらに最適化するためには、デューティサイクルを変化させることができる。デューティサイクルが高くなると、マスクの選択性は一般に低下する。RFバイアス電力波形のデューティサイクルが100%に近づくにつれて、エッチングの結果は、従来技術による連続したRFバイアス波形のそれに近づく。

【0032】

上述したように、高電力サイクル時に望ましいエッチング結果を達成するためには、高電力レベルを変化させればよい。例えば、高電力レベルを増加させると、マスクの腐食速度が大きいにもかかわらず、エッチング速度が増大して垂直なエッチングプロファイルが改善される。同様に、低電力サイクル時において、エッチングのメカニズムとポリマの堆積メカニズムとを望ましい状態で釣り合わせるためには、電力の最低レベルを変化させることができる。例えば、低電力レベルを増加させると、エッチング速度が増大してポリマの堆積量が減少する。図7および図8に示されるように、低電力レベルが増加するとポリマの堆積ラインは下がる。逆に、低電力レベルが低下するとエッチング速度が減少し、より多くのポリマが低電力サイクル時に堆積するようになる。上述したように、マスクの上面でポリマが幾らか堆積する(エッチング時のマスクの選択性を高めるため)際でも、エッチングされた特徴部の底部ではポリマがほとんどまたは全く堆積されない(そうして下地層のエッチング速度に対するマイナスの影響を最小化する)ように、低電力レベルを選択して良い場合もある。

【0033】

実施例

ある特定の用途において、二酸化シリコン含有層(例えばBPSG)等の絶縁層を上に有する200mmのウエハを、上述したTCP(商標)9100プラズマ処理システム内でエッチングした。マスク材料はフォトレジスト層とし、エッチャントはフッ化炭化水素含有ガス(例えば、フッ化炭化水素ガスまたはC2HF5等のフッ化炭化水素ガス)を含むものを用いた。もとより、当業者には明らかなように、選択されたエッチャントの種類は、選択されたエッチングの内容および/またはエッチングされる下地層の組成に依存する。

【0034】

高RFバイアス電力レベルは約1600ワットである。しかしながら、この高RFバイアス電力レベルを最適化して、与えられたシステムおよび/または基板スタックに対し、適切な絶縁層全体のエッチング速度およびフォトレジストの選択性を達成し、望ましいエッチングプロファイルを維持すればよい。高RFバイアス電力レベルは、約600〜2500ワットとすることができる。低電力レベルは、約0ワットから高電力レベルの約2分の1までとすることができ、好ましくは約0ワットから高電圧レベルの約5分の1までとすることができる。本実施例では、低電力レベルは約150ワットとした。

【0035】

デューティサイクルは、約10%から100%未満の範囲であらゆる値をとって良く、より好ましくは約30〜75%の範囲で可変すればよい。本実施例におけるデューティサイクルは約50%である。パルス時間は、0.1Hzから1000Hz未満の範囲の任意の値をとることができ、より好ましくは約1〜100Hzで変化して良く、好ましくは約5Hzである。

【0036】

また本実施例では、上記TCP(商標)9100リアクタ内のエッチング中の圧力を、約5mTに維持した。電力の最高値は、約1500ワットに設定した。本実施例における最高RF電力は連続しているが、必要に応じて拍動される。処理チャンバ内には、アルゴンが標準状態で、毎分約100立方センチメートル(cc/m)で流される。しかしながら、ほぼ不活性な任意の適切なガス(例えば希ガスまたはN2 を含んだもの)を利用しても良い。CHF3 であれぱ毎分約45立方センチメートル(cc/m)流され、でもC2HF5であれば毎分約20cc/mで、CH2F2であれぱ毎分約5cc/m流される。しかしながら、本発明は、特定の実施形態における圧力、最高電力設定、流量、およびエッチャントガスの組成に限定されるものではない点に、注意が必要である。当業者であれば、これらのパラメータが各プラズマ処理システムおよび/または各基板の要請に見合うように変化し得ることは、この発明の説明から容易に理解することができる。

【0037】

本発明で開示した拍動されたRF電力波形を使用して基板をエッチングすると、フォトレジストの選択性が、エッチングプロファイルおよび/またはエッチング速度に目立ったマイナス影響をおよぼすことなく約3:1から約7:1に向上する。連続したRF電力波形によるエッチングで既に高いマスクの選択性が得られている場合でも、やはり改善が見られることが期待できる。マスクの選択性を改善したすなわちマスクの腐食を軽減した結果、しばしばエッチングプロファイルの劣化、および/または下地層全体のエッチング速度の低下が生じる(そして逆の場合は、エッチングプロファイルの改善が、しばしばマスクの選択性すなわちマスクの腐食を犠牲にしてなされる)ような、連続したRF電力波形のみを利用した従来技術によるエッチングにおいて、大きな改善が見られた。

【0038】

以上、本発明をいくつかの好ましい実施形態にもとづいて説明したが、本発明の範囲内において、他の選択肢、変形、および同等物を実施することも可能である。また、本発明による方法および装置が、多くの代替の方式により具現化できる点に注意が必要である。このため、添付した請求の範囲は、本発明の真の精神および範囲を逸脱しない全ての選択肢、変形、および同等物を含むものとして解釈される。

【図面の簡単な説明】

【図1】 議論を促進するため、マスクと、エッチングされる下地層と、基板とを含む代表的な基板スタックを描いた説明図である。

【図2】 マスクの腐食に関する議論を明確にするため、従来のプラズマエッチング工程を使用して図1の基板スタックをエッチングした結果を示した説明図である。

【図3】 本発明を実施するのに適したプラズマ処理システムであるTCP(商標)9100プラズマ処理システムの概略構成図である。

【図4】 従来技術における連続したRF電力の波形を示した説明図である。

【図5】 エッチング中のマスクの腐食を軽減するためにチャック電極に供給される、拍動されたRF電力の波形を示した説明図である。

【図6】 プラズマエッチング時に存在する競合メカニズムに関して議論を明確にするため、仮想的なエッチング工程における、エッチング速度とRFバイアス電力の関係を示した説明図である。

【図7】 RFバイアス電力をある値に設定した際の、エッチングの結果を描いた説明図である。

【図8】 RFバイアス電力をある値に設定した際の、エッチングの結果を描いた説明図である。

【図9】 RFバイアス電力をある値に設定した際の、エッチングの結果を描いた説明図である。

【符号の説明】

100…基板スタック

102…マスク

104…下地層

106…基板

108…開口部

202…除去される厚さ

206…ファセット

300…プラズマリアクタ

302…プラズマ処理チャンバ

304…電極

305…RFジェネレータ

308…ガス分布プレート

310…基板

312…チャック

314…RFジェネレータ

502…高電力サイクル

504…低電力サイクル

506…パルス時間

702…マスク

704…エッチングされた特徴部

706…下地層

Claims (17)

- マスクの下に存在する第1の層内に、特徴部をエッチングする際の前記マスクの腐食を軽減する方法であって、

前記第1の層は基板上に配置され、前記基板はプラズマ処理チャンバ内のチャック上に配置されており、

前記方法は、

前記プラズマ処理チャンバ内にエッチャントソースガスを流す工程と、

前記エッチャントソースガスを用いてプラズマを形成する工程と、

ラジオ波電力ソースを既定のパルス周波数で拍動させて、拍動された電力を前記チャックに供給する工程であって、前記拍動されたラジオ波電力は第1の周波数を有し、前記パルス周波数で高電力サイクルと低電力サイクルを交互に繰り返し、前記パルス周波数が、前記低電力サイクル時にポリマが前記マスク上に堆積するよう十分に低い周波数が選択された工程と

を備え、

前記パルス周波数を、5Hzから100Hzの間とした方法。 - 請求項1記載の方法であって、

前記エッチャントソースガスはフッ化炭化水素ガスを含む方法。 - 請求項1記載の方法であって、

前記プラズマ処理チャンバは誘導結合されたプラズマ処理チャンバである方法。 - 請求項1記載の方法であって、

前記低電力サイクル時の最大電力レベルを、前記高電力サイクル時の最大電力レベルの約2分の1未満とした方法。 - 請求項1記載の方法であって、前記第1の層は絶縁層である方法。

- 請求項5記載の方法であって、前記マスクはフォトレジストマスクである方法。

- 請求項1記載の方法であって、

前記高電力レベルは、前記特徴部の底部にあるほぼ全てのポリマ堆積物が前記高電力サイクル時に除去されるように選択された方法。 - フォトレジストマスクの下に存在する絶縁層内にビアをエッチングする際のフォトレジストの選択性を改善する方法であって、

前記絶縁層はウエハ上に配置され、前記ウエハはプラズマ処理チャンバ内のチャック上に配置されており、

前記方法は、

フッ化炭化水素含有ガスとほぼ非活性ガスとを含むエッチャントソースガスを、前記プラズマ処理チャンバ内に流す工程と、

前記プラズマ処理チャンバに関連付けられた第1の電極に、フッ化炭化水素含有ガス含む前記エッチャントソースガスからプラズマを形成するように、第1のラジオ波電力波形を供給する工程と、

拍動されたラジオ波電力波形を前記チャックに供給する工程であって、前記拍動されたラジオ波電力波形は第1の周波数を有し、パルス周波数で高電力サイクルと低電力サイクルを交互に繰り返し、前記パルス周波数は、前記低電力サイクル時にポリマが前記マスク上に堆積するように選択された工程と

を備え、

前記パルス周波数を、5Hzから100Hzの間とした方法。 - 請求項8記載の方法であって、

前記低電力サイクル中の最大電力レベルを、前記高電力サイクル中の最大電力レベルの約2分の1未満とした方法。 - フォトレジストマスクの下に存在する絶縁層内にピアをエッチングする際の、フォトレジストの選択性を改善するための方法であって、

前記絶縁層は基板上に配置され、前記基板はプラズマ処理チャンバ内のチャック上に配置されており、

前記方法は、

フッ化炭化水素含有ガスとほぼ非活性ガスとを含むエッチャントソースガスを、前記プラズマ処理チャンバ内に流す工程と、

前記エッチャントソースガスからプラズマを形成する工程と、

拍動されたラジオ波電力波形を前記チャックに供給する工程であって、前記拍動されたラジオ波電力波形は第1の周波数を有し、パルス周波数で高電力サイクルと低電力サイクルを交互に繰り返し、前記低電力サイクル時の最大電力レベル、および前記パルス周波数は、前記低電力サイクル時にポリマが前記マスク上に堆積するように選択された工程と

を備え、

前記パルス周波数を、5Hzから100Hzの間とした方法。 - 請求項10記載の方法であって、

前記高電力サイクル時の最大電力レベルは、前記ビアの底部にある絶縁材料のエッチングが前記高電力サイクル時に可能となるように選択された方法。 - 請求項10記載の方法であって、

前記高電力サイクル時の最大電力レベルは、前記高電力サイクルの終了時までに、前記低電力サイクル時に前記ビアの底部に沿って堆積されたほぼ全てのポリマが除去されるように選択された方法。 - 請求項12記載の方法であって、

前記高電力サイクル時の最大電力レベルは、前記高電力サイクルの前記終了時までに、前記低電力サイクル時に前記ビアの側壁に沿って堆積されたほぼ全てのポリマが除去されるように選択された方法。 - 請求項10記載の方法であって、

前記低電力サイクル中の最大電力レベルを、前記高電力サイクル中の最大電力レベルの約2分の1未満とした方法。 - 請求項10記載の方法であって、さらに、

前記プラズマ処理チャンバの、前記基板の上に配置された上部電極にラジオ波電力を供給する工程を備えた方法。 - 請求項15記載の方法であって、前記上部電極は誘導コイルである方法。

- 請求項10記載の方法であって、

前記高電力レベルは、前記特徴部の底部にあるほぼ全てのポリマ堆積物が前記高電力サイクル時に除去されるように選択された方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/018,448 US6093332A (en) | 1998-02-04 | 1998-02-04 | Methods for reducing mask erosion during plasma etching |

| US09/018,448 | 1998-02-04 | ||

| PCT/US1999/002224 WO1999040607A1 (en) | 1998-02-04 | 1999-02-02 | Methods for reducing mask erosion during plasma etching |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002503029A JP2002503029A (ja) | 2002-01-29 |

| JP2002503029A5 JP2002503029A5 (ja) | 2006-04-27 |

| JP4548561B2 true JP4548561B2 (ja) | 2010-09-22 |

Family

ID=21787981

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000530927A Expired - Lifetime JP4548561B2 (ja) | 1998-02-04 | 1999-02-02 | プラズマエッチング中のマスクの腐食を軽減する方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6093332A (ja) |

| EP (1) | EP1053563B1 (ja) |

| JP (1) | JP4548561B2 (ja) |

| KR (1) | KR100604741B1 (ja) |

| AT (1) | ATE244453T1 (ja) |

| DE (1) | DE69909248T2 (ja) |

| WO (1) | WO1999040607A1 (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100521120B1 (ko) * | 1998-02-13 | 2005-10-12 | 가부시끼가이샤 히다치 세이사꾸쇼 | 반도체소자의 표면처리방법 및 장치 |

| WO1999046810A1 (fr) | 1998-03-12 | 1999-09-16 | Hitachi, Ltd. | Procede permettant de traiter la surface d'un echantillon |

| US6492277B1 (en) * | 1999-09-10 | 2002-12-10 | Hitachi, Ltd. | Specimen surface processing method and apparatus |

| KR100768610B1 (ko) * | 1998-12-11 | 2007-10-18 | 서페이스 테크놀로지 시스템스 피엘씨 | 플라즈마 처리장치 |

| US6255221B1 (en) * | 1998-12-17 | 2001-07-03 | Lam Research Corporation | Methods for running a high density plasma etcher to achieve reduced transistor device damage |

| JP4351755B2 (ja) * | 1999-03-12 | 2009-10-28 | キヤノンアネルバ株式会社 | 薄膜作成方法および薄膜作成装置 |

| KR100750420B1 (ko) * | 1999-08-17 | 2007-08-21 | 동경 엘렉트론 주식회사 | 플라즈마 보조 처리 실행 방법 및 플라즈마 보조 처리실행 리액터 |

| JP2001168086A (ja) | 1999-12-09 | 2001-06-22 | Kawasaki Steel Corp | 半導体装置の製造方法および製造装置 |

| US20020185226A1 (en) * | 2000-08-10 | 2002-12-12 | Lea Leslie Michael | Plasma processing apparatus |

| DE10309711A1 (de) * | 2001-09-14 | 2004-09-16 | Robert Bosch Gmbh | Verfahren zum Einätzen von Strukturen in einem Ätzkörper mit einem Plasma |

| EP1444726A4 (en) * | 2001-10-22 | 2008-08-13 | Unaxis Usa Inc | METHOD AND DEVICE FOR Etching PHOTOMASCIC SUBSTRATES USING PULSED PLASMA |

| TW567394B (en) * | 2001-10-22 | 2003-12-21 | Unaxis Usa Inc | Apparatus for processing a photomask, method for processing a substrate, and method of employing a plasma reactor to etch a thin film upon a substrate |

| US20030077910A1 (en) * | 2001-10-22 | 2003-04-24 | Russell Westerman | Etching of thin damage sensitive layers using high frequency pulsed plasma |

| TWI315966B (en) * | 2002-02-20 | 2009-10-11 | Panasonic Elec Works Co Ltd | Plasma processing device and plasma processing method |

| US20030235998A1 (en) * | 2002-06-24 | 2003-12-25 | Ming-Chung Liang | Method for eliminating standing waves in a photoresist profile |

| US20040097077A1 (en) * | 2002-11-15 | 2004-05-20 | Applied Materials, Inc. | Method and apparatus for etching a deep trench |

| US6759339B1 (en) * | 2002-12-13 | 2004-07-06 | Silicon Magnetic Systems | Method for plasma etching a microelectronic topography using a pulse bias power |

| US7976673B2 (en) * | 2003-05-06 | 2011-07-12 | Lam Research Corporation | RF pulsing of a narrow gap capacitively coupled reactor |

| US7446050B2 (en) * | 2003-08-04 | 2008-11-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Etching and plasma treatment process to improve a gate profile |

| JP2005072260A (ja) * | 2003-08-25 | 2005-03-17 | Sanyo Electric Co Ltd | プラズマ処理方法、プラズマエッチング方法、固体撮像素子の製造方法 |

| US7879510B2 (en) * | 2005-01-08 | 2011-02-01 | Applied Materials, Inc. | Method for quartz photomask plasma etching |

| US7642193B2 (en) * | 2006-08-07 | 2010-01-05 | Tokyo Electron Limited | Method of treating a mask layer prior to performing an etching process |

| KR101346897B1 (ko) * | 2006-08-07 | 2014-01-02 | 도쿄엘렉트론가부시키가이샤 | 에칭 방법 및 플라즈마 처리 시스템 |

| US7449414B2 (en) * | 2006-08-07 | 2008-11-11 | Tokyo Electron Limited | Method of treating a mask layer prior to performing an etching process |

| US7572386B2 (en) | 2006-08-07 | 2009-08-11 | Tokyo Electron Limited | Method of treating a mask layer prior to performing an etching process |

| US8192576B2 (en) * | 2006-09-20 | 2012-06-05 | Lam Research Corporation | Methods of and apparatus for measuring and controlling wafer potential in pulsed RF bias processing |

| JP5192209B2 (ja) | 2006-10-06 | 2013-05-08 | 東京エレクトロン株式会社 | プラズマエッチング装置、プラズマエッチング方法およびコンピュータ読取可能な記憶媒体 |

| JP5514413B2 (ja) * | 2007-08-17 | 2014-06-04 | 東京エレクトロン株式会社 | プラズマエッチング方法 |

| JP5295748B2 (ja) * | 2008-12-18 | 2013-09-18 | 東京エレクトロン株式会社 | 構成部品の洗浄方法及び記憶媒体 |

| US9105705B2 (en) * | 2011-03-14 | 2015-08-11 | Plasma-Therm Llc | Method and apparatus for plasma dicing a semi-conductor wafer |

| CN103871865B (zh) * | 2012-12-18 | 2016-08-17 | 中微半导体设备(上海)有限公司 | 一种清洁等离子体反应腔侧壁的方法 |

| US9818841B2 (en) | 2015-05-15 | 2017-11-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor structure with unleveled gate structure and method for forming the same |

| US9583485B2 (en) | 2015-05-15 | 2017-02-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin field effect transistor (FinFET) device structure with uneven gate structure and method for forming the same |

| JP6670692B2 (ja) | 2015-09-29 | 2020-03-25 | 株式会社日立ハイテク | プラズマ処理装置およびプラズマ処理方法 |

| US11417501B2 (en) | 2015-09-29 | 2022-08-16 | Hitachi High-Tech Corporation | Plasma processing apparatus and plasma processing method |

| US10886136B2 (en) * | 2019-01-31 | 2021-01-05 | Tokyo Electron Limited | Method for processing substrates |

| US11915932B2 (en) | 2021-04-28 | 2024-02-27 | Applied Materials, Inc. | Plasma etching of mask materials |

| KR20230147594A (ko) * | 2022-04-13 | 2023-10-23 | 주식회사 히타치하이테크 | 플라스마 처리 방법 및 플라스마 처리 디바이스 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FI62692C (fi) * | 1981-05-20 | 1983-02-10 | Valmet Oy | Pappersmaskinspress med bred presszon |

| US4500563A (en) * | 1982-12-15 | 1985-02-19 | Pacific Western Systems, Inc. | Independently variably controlled pulsed R.F. plasma chemical vapor processing |

| KR890004881B1 (ko) * | 1983-10-19 | 1989-11-30 | 가부시기가이샤 히다찌세이사꾸쇼 | 플라즈마 처리 방법 및 그 장치 |

| DE3733135C1 (de) * | 1987-10-01 | 1988-09-22 | Leybold Ag | Vorrichtung zum Beschichten oder AEtzen mittels eines Plasmas |

| DE69017744T2 (de) * | 1989-04-27 | 1995-09-14 | Fujitsu Ltd | Gerät und Verfahren zur Bearbeitung einer Halbleitervorrichtung unter Verwendung eines durch Mikrowellen erzeugten Plasmas. |

| US4889588A (en) * | 1989-05-01 | 1989-12-26 | Tegal Corporation | Plasma etch isotropy control |

| US5468341A (en) * | 1993-12-28 | 1995-11-21 | Nec Corporation | Plasma-etching method and apparatus therefor |

| US5683538A (en) * | 1994-12-23 | 1997-11-04 | International Business Machines Corporation | Control of etch selectivity |

| US5614060A (en) * | 1995-03-23 | 1997-03-25 | Applied Materials, Inc. | Process and apparatus for etching metal in integrated circuit structure with high selectivity to photoresist and good metal etch residue removal |

| US5983828A (en) * | 1995-10-13 | 1999-11-16 | Mattson Technology, Inc. | Apparatus and method for pulsed plasma processing of a semiconductor substrate |

-

1998

- 1998-02-04 US US09/018,448 patent/US6093332A/en not_active Expired - Lifetime

-

1999

- 1999-02-02 EP EP99904542A patent/EP1053563B1/en not_active Expired - Lifetime

- 1999-02-02 KR KR1020007008510A patent/KR100604741B1/ko active IP Right Grant

- 1999-02-02 JP JP2000530927A patent/JP4548561B2/ja not_active Expired - Lifetime

- 1999-02-02 DE DE69909248T patent/DE69909248T2/de not_active Expired - Lifetime

- 1999-02-02 AT AT99904542T patent/ATE244453T1/de active

- 1999-02-02 WO PCT/US1999/002224 patent/WO1999040607A1/en active IP Right Grant

-

2000

- 2000-07-05 US US09/610,303 patent/US6489245B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP1053563A1 (en) | 2000-11-22 |

| EP1053563B1 (en) | 2003-07-02 |

| US6489245B1 (en) | 2002-12-03 |

| WO1999040607A1 (en) | 1999-08-12 |

| KR20010040638A (ko) | 2001-05-15 |

| US6093332A (en) | 2000-07-25 |

| JP2002503029A (ja) | 2002-01-29 |

| KR100604741B1 (ko) | 2006-07-26 |

| DE69909248D1 (de) | 2003-08-07 |

| ATE244453T1 (de) | 2003-07-15 |

| DE69909248T2 (de) | 2004-05-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4548561B2 (ja) | プラズマエッチング中のマスクの腐食を軽減する方法 | |

| US9865484B1 (en) | Selective etch using material modification and RF pulsing | |

| KR100590370B1 (ko) | 플라즈마 에칭 방법 | |

| JP4657458B2 (ja) | 低容量の誘電体層をエッチングするための技術 | |

| US5429710A (en) | Dry etching method | |

| US4496448A (en) | Method for fabricating devices with DC bias-controlled reactive ion etching | |

| US6235640B1 (en) | Techniques for forming contact holes through to a silicon layer of a substrate | |

| JP2603217B2 (ja) | 表面処理方法及び表面処理装置 | |

| JP2006148156A (ja) | 基板をエッチングするための方法と装置 | |

| US10193066B2 (en) | Apparatus and techniques for anisotropic substrate etching | |

| JPH09326383A (ja) | プラズマ処理装置及びプラズマ処理方法 | |

| US5849641A (en) | Methods and apparatus for etching a conductive layer to improve yield | |

| KR20170000791A (ko) | 에칭 방법 | |

| JPH11195641A (ja) | プラズマ処理方法 | |

| US20230081352A1 (en) | Pulsed Capacitively Coupled Plasma Processes | |

| US20030003748A1 (en) | Method of eliminating notching when anisotropically etching small linewidth openings in silicon on insulator | |

| JP5041696B2 (ja) | ドライエッチング方法 | |

| WO2023199371A1 (ja) | プラズマ処理方法 | |

| KR100420533B1 (ko) | 플라즈마 공정장치 및 이를 이용한 플라즈마 식각방법 | |

| WO2001048789A1 (en) | Plasma processing methods |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060202 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060202 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081225 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090106 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090403 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090410 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090703 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100405 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100608 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100629 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |