JP4544772B2 - 半導体メモリ装置 - Google Patents

半導体メモリ装置 Download PDFInfo

- Publication number

- JP4544772B2 JP4544772B2 JP2001095260A JP2001095260A JP4544772B2 JP 4544772 B2 JP4544772 B2 JP 4544772B2 JP 2001095260 A JP2001095260 A JP 2001095260A JP 2001095260 A JP2001095260 A JP 2001095260A JP 4544772 B2 JP4544772 B2 JP 4544772B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- area

- bits

- address

- read

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Static Random-Access Memory (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

本発明は、記憶容量が2Nバイトで示されない半導体メモリを具備する半導体メモリ装置に関するものである。

【0002】

【従来の技術】

半導体メモリ装置の一般的な構成を図5に示す。主なブロックとしては、データを記憶するメモリセルの集合体であるメモリセルアレイ1、書込/読み出しをするアドレス情報をラッチするアドレスバッファ2、アドレスバッファ2の情報から特定のメモリセルを選択するためのデコーダ3、メモリセルを駆動するワードドライバ4、書込/読み出し信号の信号路を決定し、読み出し時にメモリセルからの信号を検出・増幅するマルチプレクサ・センス回路5、書込信号をラッチするデータ入力バッファ6、メモリセルからの読み出し信号をラッチすると共に外部に送出するデータ出力バッファ7からなる。

【0003】

まず、書込動作について説明する。アドレス情報が入力されると、アドレスバッファ2にアドレス情報がラッチされ、これに基づいてデコーダ3が特定のメモリセル行を駆動するワードドライバ4を活性化する。また、アドレスバッファ2にラッチされるアドレス情報に基づいて、マルチプレクサ・センス回路5が特定のビット線を選択し、特定のメモリセル列を選択する。特定のメモリセルが選択された状態で、データ入力バッファ6にラッチされる信号に応じて、メモリセルの状態が強制的に書き換えられ、データの書込が行われる。

【0004】

次に読出動作について説明する。アドレス情報が入力されると、アドレスバッファ2にアドレス情報がラッチされ、これに基づいてデコーダ3が特定のメモリセル行を駆動するワードドライバを活性化する。このときメモリセルの状態に応じて、記憶されていたデータがビット線を介してマルチプレクサ・センス回路5に送られる。マルチプレクサ・センス回路5は、デコーダ3と特定のビット線を接続し、読み出すべきデータの信号を増幅する。増幅された信号がデータ出力バッファ7を介して、外部にデータとして出力される。これにより、メモリセルに記憶されるデータの読み出しが行われる。

【0005】

【発明が解決しようとする課題】

一般的にメモリの記憶容量は、1Mbit、2Mbit、4Mbit、8Mbitに代表されるように、2Nbitで示されるものが広く用いられている。これは、所定桁数のアドレスで示される領域を最大限、記憶領域として利用するためである。しかしながら、最近では、市場の要求等により、必ずしも2Nbitで示されるような記憶容量のメモリではなく、例えば、4.5Mbitのような記憶容量が好まれる場合がある。図6は、4.5Mbitメモリの記憶領域を示した模式図である。

【0006】

領域Eは、4.5Mbitメモリの記憶領域を示すものであり、領域Nは、8Mbitメモリの記憶領域から領域Eを差し引いたものである。4.5Mbitメモリの記憶領域Eを示すには、アドレス00000000000000000000〜10001111111111111111の20ビットの桁数が必要である。これは、8Mbitメモリの記憶領域を示すアドレス00000000000000000000〜11111111111111111111と同一の桁数である。このため、20ビットのアドレスで示す領域には、4.5Mbitメモリで実際には存在しない領域Nのアドレス10010000000000000000〜11111111111111111111が含まれている。

【0007】

領域E内のアドレスを指定したにもかかわらず、何かのエラーで、この領域Nを指定するようなアドレスが入ってくると、回路が誤動作を生じる恐れがある。

したがって、入力アドレスが記憶領域内を指定するものであるか否かを判別し、記憶領域に対するアクセスのみを有効とする制御が必要となる。

【0008】

そこで、本発明は、上述の問題に鑑み、回路の誤動作を防止する半導体メモリ装置を提供することを目的とする。

【0009】

【課題を解決するための手段】

本発明は、上述の課題を解決するためになされたもので、その特徴とするところは、書き込みアドレス、又は、読み出しアドレスに対応するアドレスデータの入力に応答してメモリセルアレイの特定アドレスを指定し、データの書き込み、又は、読み出しを行う半導体メモリ装置において、データの書き込み、又は、読み出しが可能な記憶領域を示すエリアデータを保持するデータ保持手段と、前記アドレスデータと前記エリアデータを比較して、前記アドレスデータで示すアドレスが前記記憶領域内であるか否かの判定動作を行う判定部と、前記判定部で前記アドレスデータの示すアドレスが前記記憶領域内にないと判断されたとき、前記メモリセルアレイへのアクセスを停止する制御部と、を備え、前記判定部は、前記アドレスデータと前記エリアデータとを2ビット単位で比較し、特定の2ビットが一致したとき、この2ビットに続く下位2ビットの比較に基づいて前記判定動作を行うにある。

【0010】

本発明によれば、記憶領域外へのアクセスが無効となり、記憶領域外への不正アクセスを防止することができる。

【0011】

【発明の実施の形態】

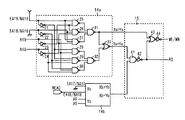

図1は、本発明の半導体メモリ装置の実施形態を示すブロック図であり、例えば、記憶容量が4.5Mbitの半導体メモリを具備する。

【0012】

本発明の半導体メモリ装置は、記憶部10、制御回路12及び判定部13で構成される。記憶部10に具備されるメモリセルアレイ11は、例えば、4.5Mbitの記憶領域を有する半導体メモリであり、その記憶領域は、図7に示す通り、アドレス00000000000000000000〜10001111111111111111で示される。尚、記憶部10に具備されるその他の回路は、図5に示すものと同様であり、同一符号が付してある。制御回路12は、記憶部10と判定部13の間に接続され、判定部13の出力に応答して、外部から入力される書き込みアドレスデータWA及び読み出しアドレスデータRAを記憶部10に出力する。

【0013】

判定部13は、2ビット比較器14a、14bと、判定回路15とで構成され、入力される書き込みアドレスデータWA、読み出しアドレスデータRAが4.5Mbitメモリの記憶領域内を示すものであるかを判定する。メモリセルアレイ11が4.5Mbitの半導体メモリである場合、その最終アドレスは、図6に示すように、10001111111111111111であるから、入力されたアドレスデータの上位4ビットが1000以下であれば、そのアドレスが記憶領域内であると判定することができ、逆に大きければ、そのアドレスが記憶領域外であると判定することができる。

【0014】

したがって、この判定部13は、書き込みアドレスデータWAの判定を行う場合、書き込みアドレスデータWAの上位4ビットWA19〜WA16と記憶領域の最終アドレスの上位4ビット1000(以下、有効エリアデータEAと略記する)とを比較し、一方、読み出しアドレスデータRAの判定を行う場合、読み出しアドレスデータRAの上位4ビットRA19〜RA16と記憶領域外の最初のアドレスの上位4ビット1001(以下、無効エリアデータNAと略記する)とを比較する構成となっている。

【0015】

2ビット比較器14aは、4つの入力を備え、その内の2つの入力は、有効エリアデータEA、又は、無効エリアデータNAの上位2ビットEA19、18、NA19、18に対応する。また、別の2つの入力は、書き込みアドレスデータWA、又は、読み出しアドレスデータRAの上位2ビットWA19、18、RA19、18に対応する。それぞれの入力には、例えば、入力されるアドレスの単ビットの1に対応してHレベルの信号が入力され、0に対応してLレベルの信号が入力される。このため、有効エリアデータEA、又は、無効エリアデータNAに対応する2つの入力には、例えば、電源電位VC(Hレベル)と接地電位VD(Lレベル)がそれぞれ接続され、有効エリアデータEAの上位2ビットを保持している。

【0016】

2ビット比較器14bは、2ビット比較器14aと同様に、4つの入力を備え、それぞれ2つの入力が、有効エリアデータEA、無効エリアデータNAの下位2ビットと、書き込みアドレスデータWA、読み出しアドレスデータRAの下位2ビットに対応する。この2ビット比較器14bは、有効エリアデータEA、又は、無効エリアデータNAの下位2ビットに対応する2つの入力のうち、第3ビットに対応する入力に接地電位VG(Lレベル)が接続され、第4ビットに対応する入力にREAD端子が接続される。

【0017】

このREAD端子には、書き込みアドレスデータWAの判定を行う場合、Lレベルの信号が入力され、一方、読み出しアドレスデータRAの判定を行う場合、Hレベルの信号が入力され、有効エリアデータEA、或いは、無効エリアデータNAの下位2ビットを保持している。これにより、書き込みアドレスデータWAの判定を行うときは、有効エリアデータEAの第3、第4ビット00が対応し、読み出しアドレスデータRAの判定を行うときは、無効エリアデータNAの第3、第4ビット01が対応する。尚、有効エリアデータEA及び無効エリアデータNAは、レジスタ等に保持されて、メモリセルアレイ11の記憶容量に応じて変更可能としても良い。

【0018】

これらの2ビット比較器14a、14bは、書き込みアドレスデータWAと有効エリアデータEAの上位4ビットの比較と、読み出しアドレスデータRAと無効エリアデータNAの上位4ビットの比較とを2ビットずつで行い、大小判定、或いは一致判定を行う。その判定結果に応じて、比較出力CS1、CS2を判定回路15に出力する。

【0019】

判定回路15は、複数の論理回路で構成され、2ビット比較器14a、14bの比較出力CS1、CS2を論理合成して、書き込みアドレスデータWA、又は、読み出しアドレスデータRAがメモリセルアレイ11の記憶領域内であるか否かを判定する。書き込みアドレスデータWAを判定するとき、書き込みアドレスデータWAが記憶領域内であれば、記憶部10へのアクセスを許可する許可信号WEを出力し、記憶領域外であれば、アクセスを無効とする無効信号WNを出力する。一方、読み出しアドレスデータRAを判定するとき、読み出しアドレスデータRAが記憶領域外を指定すれば、読み出しアドレスデータRAを記憶領域の最初のアドレスにリセットするリセット信号RSを出力する。

【0020】

図2は、判定部13の構成を示す回路図である。2ビット比較器14aは、インバータ21〜24、NANDゲート25〜32及びNORゲート33で構成される。インバータ21〜24は、2ビット比較器14aの4つの入力に入力される有効エリアデータEA、無効エリアデータNA、書き込みアドレスデータWA及び読み出しアドレスデータRAに対応する信号を反転し、その反転信号を出力する。NANDゲート25〜30は、各アドレスに対応する信号及びその反転信号を受けて、論理積を取得する。NANDゲート31は、NANDゲート25〜27から出力される信号の論理積を取得して、その出力信号をXa>Ya出力に供給すると共に、NORゲート33の一方の入力に出力する。NANDゲート32は、NANDゲート28〜30から出力される信号の論理積を取得して、その出力信号をNORゲート33の他方の入力に出力する。NORゲート33は、NANDゲート31、32から出力される信号の論理和を取得して、その出力信号をXa=Ya出力に供給する。

【0021】

ここで、Xa=EA19EA18(NA19NA18)、Ya=WA19WA18(RA19RA18)とし、Xb=EA17EA16(NA17NA16)、Yb=WA17WA16(NA17NA16)とする。2ビット比較器14aは、その比較結果が、Xa>Yaであれば、Xa>Ya出力よりHレベルの信号を出力し、Xa=Ya出力よりLレベルの信号を出力する。Xa=Yaであれば、Xa>Ya出力よりLレベルの信号を出力し、Xa=Ya出力よりLレベルの信号を出力する。尚、2ビット比較器14bは、2ビット比較器14aと同様の回路構成であるが、その出力にXb=Yb出力のみを備える。

【0022】

判定回路15は、NANDゲート41と、インバータ42、44と、NORゲート43とで構成される。NANDゲート41は、入力に2ビット比較器14aのXa=Ya出力、2ビット比較器14bのXb=Yb出力を受け、論理合成した出力をインバータ42に供給する。インバータ42は、NANDゲート41から出力される出力を反転し、その反転出力をNORゲート43の入力の一方に供給する。また、インバータ42の出力は、読み出しアドレスデータRAの判定を行うときのリセット信号RSとして、制御回路12(図1)に出力される。NORゲート43は、インバータ42より出力された反転出力を入力の一方に受けると共に、2ビット比較器14aのXa>Ya出力を入力の他方に受ける。そして、それぞれの入力を論理合成して、その論理和をインバータ44に出力する。インバータ44は、NORゲート43から出力される出力を反転させ、その出力を書き込みアドレスデータWAの判定を行うときの有効信号WE、或いは無効信号WNとして出力する。この有効信号WE及び無効信号WNが制御回路12に出力されて、メモリセルアレイ11へのデータの書き込みが制御される。

【0023】

続いて、書き込みアドレスデータWA及び読み出しアドレスデータRAの判定動作を説明する。先ず、書き込みアドレスデータWAの判定を行う場合を説明する。以下に書き込みアドレスデータWAと有効エリアデータEAのそれぞれの2ビットずつを比較する際の条件式を示す。尚、この条件式は、データの書き込みを許可するための条件式である。

1)Xa>Ya ・・・・・・OK

2)Xa=Ya and Xb=Yb ・・・・・・OK

上記の条件式に従い、書き込みアドレスデータWAが入力されたときの判定部15の動作を説明する。例えば、上位4ビットが0111の書き込みアドレスデータWAが入力された場合、最初に条件式1)に従い、2ビット比較器14aにおいて、書き込みアドレスデータWAと有効エリアデータEAの上位2ビットずつを比較する。このとき、(Xa=10)>(Ya=01)であるので、2ビット比較器14aのXa>Ya出力からHレベルの信号がNORゲート43に出力され、許可信号WEが出力される。即ち、書き込みアドレスデータWAと有効エリアデータEAの上位から2ビットずつを比較していって、上位2ビットを比較する2ビット比較器14aのXa>Ya出力からHレベルの信号が出力された時点で、書き込みアドレスデータWAがメモリセルアレイ11の記憶領域内であると判定する。

【0024】

例えば、上位4ビットのアドレスが1011の書き込みアドレスデータWA(即ち、有効エリアデータEAよりも大きい)が入力された場合を説明する。最初に、条件式1)に従い、(Xa=10)=(Ya=10)であるので、2ビット比較器14aのXa>Ya出力からLレベルの信号がNORゲート43に出力され、Xa=Ya出力からHレベルの信号がNANDゲート41に出力される。この時点では、NANDゲート41、NORゲート43のどちらの論理も決定してないので、続いて、条件式2)に従い、下位の2ビットを比較する。2ビット比較器14bにおいて、(Xb=00)<(Yb=11)であるので、2ビット比較器14bのXb=Yb出力からLレベルの信号がNANDゲート41に出力される。

【0025】

NANDゲート41の入力には、2ビット比較器14aのXa=Yb出力からHレベルの信号が、2ビット比較器14bのXb=Yb出力からLレベルの信号がそれぞれ供給されるので、NANDゲート41は、Hレベルの信号をインバータ42に出力する。インバータ42は、NANDゲート41の出力を反転して、Lレベルの信号をNORゲート43に出力する。これにより、NORゲート43の論理が決定され、NORゲート43は、Hレベルの信号をインバータ44に出力する。インバータ44は、NORゲート43の出力を反転して、Lレベルの無効信号WNを出力する。即ち、条件式1)、2)を満たさなければ、データの書き込みを無効とする無効信号WNを出力する。

【0026】

次に、読み出しアドレスデータRAを判定する場合を説明する。ここで、本実施形態においては、データの読み出し方法として、インクリメントリード方式を使用する場合を説明する。このインクリメントリード方式とは、N番地のデータを読み出したあと、デバイス側でN+1、N+2、……番地のようにデータを読み出していくアドレスを順次インクリメントしていって、記憶領域の最終アドレスに到達した後、記憶領域の最初のアドレスに戻って、また読み出しを繰り返していくシステムのことである。このため、読み出しアドレスデータRAの判定を行うときは、読み出しアドレスデータRAと無効エリアデータNAの上位4ビットを比較し、読み出しアドレスデータRAが記憶領域外に到達したか否かを判定する。

【0027】

そして、読み出しアドレスデータRAが無効エリアデータNAに等しくなったとき、Hレベルのリセット信号RSを出力して、読み出しアドレスデータRAを記憶領域の最初のアドレスにリセットする。これにより、記憶領域の最初からデータが読み出される。

【0028】

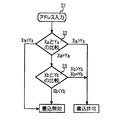

図3は、メモリセルアレイ11へのデータの書き込み動作の制御を説明するフローチャートであり、図4は、読み出し動作の制御を説明するフローチャートである。先ず、図3に従い、データの書き込みの制御のステップを説明する。ステップS1で、書き込みアドレスデータWAが入力されると、続くステップS2で、有効エリアデータEAの上位2ビットXa=EA19EA18と書き込みアドレスデータWAの上位2ビットYa=WA19WA18が比較される。この比較において、Xa>Yaであれば、書き込みアドレスデータWAが記憶領域内を指定するものであると判定し、メモリセルアレイ11へのアクセスが許可される。一方、Xa<Yaであれば、書き込みアドレスデータWAが記憶領域外と判定され、メモリセルアレイ11へのアクセスが無効とされる。また、ステップS2の比較において、Xa=Ybであれば、次のステップS3に進む。

【0029】

次のステップS3では、有効エリアデータEAの第3、第4ビットXb=EA17EA16と書き込みアドレスデータWAの第3、第4ビットYb=A17A16が比較される。この比較において、Xb>Yb或いはXb = =Ybであれば、書き込みアドレスデータWAが記憶領域内であると判定され、メモリセルアレイ11へのアクセスが許可される。ステップ3の比較において、Xb<Ybであれば、書き込みアドレスデータWAが記憶領域外であると判定され、メモリセルアレイ11へのアクセスが無効とされる。

【0030】

次に、図4に従い、メモリセルアレイ11からのデータの読み出しを制御するときのステップを説明する。ステップS11で、読み出しアドレスデータRAが入力されると、続くステップS12で、無効エリアデータNAの上位2ビットXa=NA19NA18と読み出しアドレスデータRAの上位2ビットYa=A19A18が比較される。この比較において、Xa>Yaであれば、読み出しアドレスデータRAが記憶領域内であると判定され、ステップS14bに進み、指定されたアドレスのデータが読み出される。ステップS12の比較において、Xa=Yaであれば、次のステップS13に進む。

【0031】

次のステップS13では、無効エリアデータNAの第3、第4ビットXb=NA17NA16と読み出しアドレスデータRAの第3、第4ビットYb=A17A16が比較される。この比較において、Xb>Ybであれば、読み出しアドレスデータRAが記憶領域内であると判定される。そして、ステップS14bに進み、指定されたアドレスのデータの読み出しが行われて、次のステップS15に進む。また、ステップS13の比較において、Xb=Ybであれば、読み出しアドレスデータRAが記憶領域外の最初のアドレスに到達したと判定され、ステップS14aに進む。ステップ14aでは、読み出しアドレスデータRAがリセットされ、記憶領域の最初のアドレスから繰り返しデータが読み出される。ステップS15で、データの読み出しを終了するコマンドが入力されると、データの読み出しが終了される。また、データの読み出しを終了するコマンドの入力がなければ、ステップS12に戻り、次のデータを読み出すための比較判定が順次行われる。

【0032】

以上の判定動作によって、入力されるアドレスが記憶領域であるか否かが判定され、データの書き込み及び読み出しの制御が行われる。

【0033】

以上、本発明を実施例に基づき説明したが、記憶容量が4.5Mbitメモリに限定されるものではなく、2Nbitで示されない記憶容量のメモリであれば、各種条件を変更して適用することができる。

【0034】

【発明の効果】

本発明によれば、入力されたアドレスが記憶領域内を指定するものであるかを判別することができ、記憶領域外への不正アクセスを防止することができる。これにより、回路の誤動作の防止を可能としている。

【0035】

また、判定部に複数の2ビット比較器を用いることで、いかなる容量の不揮発性メモリ装置においてアドレス比較を行う場合でも、システム的に平易とすることができ、汎用性を高くすることができる。

【図面の簡単な説明】

【図1】本発明の半導体メモリ装置の実施形態を示すブロック図である。

【図2】判定部の構成を示す回路図である。

【図3】データの書き込みの制御を説明するフローチャートである。

【図4】データの読み出しの制御を説明するフローチャートである。

【図5】従来の半導体メモリ装置の構成を示すブロック図である。

【図6】4.5Mbitメモリのマッピングを示す模式図である。

【符号の説明】

1、11:メモリセルアレイ

2:アドレスバッファ

3:デコーダ

4:ワードドライバ

5:マルチプレクサ・センス回路

6:データ入力バッファ

7:データ出力バッファ

10:記憶部

12:制御回路

13:判定部

14a、14b:2ビット比較器

15:判定回路

41:NANDゲート

42、44:インバータ

43:NORゲート

Claims (4)

- 書き込みアドレスデータ及び読み出しアドレスデータの桁数で示される領域よりも小さい容量の記録領域を有し、かつ、データの読み出し方式としてインクリメントリード方式を採用した半導体メモリ装置において、

前記記憶領域の最終のアドレスの上位ビットを示す有効エリアデータ及び前記記憶領域の範囲外の最初のアドレスの上位ビットを示す無効エリアデータを保持し、前記書き込みアドレスデータの上位ビットと前記有効エリアデータとについて大小判定及び一致判定を行い、前記読み出しアドレスデータの上位ビットと前記無効エリアデータとについて一致判定を行う比較器と、を備え、

前記比較器の判定の結果、前記書き込みアドレスデータが前記記憶領域内であればアクセスを許可し、前記記憶領域の範囲外であればアクセスを無効とし、また、前記読み出しアドレスデータの上位ビットが前記無効エリアデータと一致すれば前記読み出しアドレスデータを前記記憶領域の最初のアドレスにリセットすることを特徴とする半導体メモリ装置。 - 前記有効エリアデータ及び前記無効エリアデータのデータの異なる1ビットはREAD端子の入力信号によって決定されることを特徴とする請求項1記載の半導体メモリ装置。

- 前記有効エリアデータ及び前記無効エリアデータのデータが同じビットは、Hレベル又はLレベルの固定データによって決定されることを特徴とする請求項1又は2に記載の半導体メモリ装置。

- 前記比較器は、前記書き込みアドレスデータ又は前記読み出しアドレスデータの上位ビットと前記有効エリアデータ又は前記無効エリアデータとを上位から2ビット単位で順次比較し、特定の2ビットが一致したとき、この2ビットに続く下位の2ビットの比較に基づいて前記判定を行うことを特徴とする請求項1乃至3のいずれか1項に記載の半導体メモリ装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001095260A JP4544772B2 (ja) | 2001-03-29 | 2001-03-29 | 半導体メモリ装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001095260A JP4544772B2 (ja) | 2001-03-29 | 2001-03-29 | 半導体メモリ装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002298584A JP2002298584A (ja) | 2002-10-11 |

| JP4544772B2 true JP4544772B2 (ja) | 2010-09-15 |

Family

ID=18949332

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001095260A Expired - Fee Related JP4544772B2 (ja) | 2001-03-29 | 2001-03-29 | 半導体メモリ装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4544772B2 (ja) |

-

2001

- 2001-03-29 JP JP2001095260A patent/JP4544772B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002298584A (ja) | 2002-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6556504B2 (en) | Nonvolatile semiconductor memory device and data input/output control method thereof | |

| JP3730423B2 (ja) | 半導体記憶装置 | |

| JP5311784B2 (ja) | 半導体装置 | |

| JP5038292B2 (ja) | 不揮発性メモリのキャッシュ動作におけるデータラッチの使用 | |

| US5202969A (en) | Single-chip-cache-buffer for selectively writing write-back and exclusively writing data-block portions to main-memory based upon indication of bits and bit-strings respectively | |

| US7203791B2 (en) | Flash memory device with partial copy-back mode | |

| JPH10500801A (ja) | フラッシュ様コアを有するeepromアレイ | |

| JPH0778997B2 (ja) | 不揮発性半導体メモリ | |

| CN100550190C (zh) | 非易失性存储器装置及操作其分页缓冲器的方法 | |

| US20080080237A1 (en) | Method of programming a multi level cell | |

| JP2002329396A (ja) | バンク構成を変更可能なフラッシュメモリ | |

| JP2004030784A (ja) | 半導体記憶装置 | |

| JP2010277672A (ja) | 多値nandフラッシュメモリ | |

| US6862672B1 (en) | Semiconductor memory device and method of controlling same | |

| JP2010118123A (ja) | 半導体記憶装置 | |

| US5206866A (en) | Bit error correcting circuit for a nonvolatile memory | |

| CN101563675B (zh) | 具有高写入并行度的用于快闪存储器的列冗余 | |

| US8275934B2 (en) | Nonvolatile memory device and cache read method using the same | |

| JP4463680B2 (ja) | 半導体メモリのワード線ラッチ | |

| JPH05282882A (ja) | 不揮発性半導体メモリ | |

| JPWO2006046281A1 (ja) | 不揮発性記憶装置の情報設定方法、および不揮発性記憶装置 | |

| JP4544772B2 (ja) | 半導体メモリ装置 | |

| JP4254932B2 (ja) | メモリコントローラ及びフラッシュメモリシステム | |

| US5982665A (en) | Non-volatile memory array having a plurality of non-volatile memory status cells coupled to a status circuit | |

| JP4642017B2 (ja) | 不揮発性半導体記憶装置用セクタ保護回路、セクタ保護方法、および不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040913 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20051227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070731 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071001 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080108 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080125 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080317 |

|

| A912 | Removal of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20080404 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100506 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100629 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |