本発明は、インクジェット法に代表される液滴吐出法を用いて形成した配線基板、及び半導体素子を有する半導体装置、並びにその作製方法に関するものである。

従来、薄膜トランジスタ(以下「TFT」ともいう。)やMOSトランジスタに代表される半導体素子によって構成される所謂アクティブマトリクス駆動方式の表示パネル、又は半導体集積回路は、フォトマスクを使った光露光工程(以下、フォトリソグラフィー工程と示す。)により、各種薄膜をパターニングすることにより製造されている。

フォトリソグラフィー工程は、レジストを基板全面に塗布しプリベークを行った後、フォトマスクを介して紫外線等を照射し、現像によってレジストパターンを形成する。この後、該レジストパターンをマスクパターンとして、膜パターンや配線となるべき部分以外に存在する薄膜(半導体材料、絶縁体材料、又は導電体材料で形成される膜)をエッチング除去して、膜パターンや配線を形成している。

また、成膜に要する原料のロスを低減するため、レジストをノズルから細径の線状に連続吐出できる装置を用いて、半導体ウェハ上に成膜を行う技術が特許文献1に記載されている。

特開2000−188251号公報

しかしながら、従来のフォトリソグラフィー工程を用いた配線や膜パターンの形成工程において、配線や膜パターン及びレジストの材料の大部分が無駄になると共に、配線やマスクパターンを形成するための工程数が多く、スループットが低下するという問題がある。

また、フォトリソグラフィー工程に用いられる露光装置は、大面積基板を一度に露光処理することが困難である。このため、大面積基板を用いた半導体装置の作製方法においては、複数の露光回数を必要とし、隣り合うパターンとの不整合が生じることにより、歩留まりが低下するという問題がある。

また、微細で、占有面積の小さな半導体素子を液滴吐出法で形成するためには、液滴径の小さな原料溶液を吐出する必要がある。このためには、吐出口の径を小さくすればよいが、この場合、原料溶液の組成物が吐出口の先端に付着、乾燥、固化して目詰まり等が生じてしまい、一定量の原料溶液を連続且つ安定的に吐出することが困難である。この結果、該半導体素子で形成される半導体装置のスループットや歩留まりの低下を招くという問題がある。

本発明は、このような状況に鑑みなされたものであり、少ない工程数で大面積基板に配線を形成する方法、及びそれにより形成された配線基板を提供することを目標とする。

また、少ない工程数及び原料の削減により、コスト削減及びスループットの向上が可能であり、かつ微細構造の半導体素子を有する半導体装置、及びその作製方法を提供することを目的とする。

本発明は、基板上に設けられた金属粒子と有機樹脂とで形成される組成物にレーザ光を照射し、金属粒子の一部を焼成して、配線、電極等に代表される導電層を有する基板を形成することを要旨とする。

また、本発明は、上記焼成された導電層を配線又は電極として有する半導体装置を形成することを要旨とする。

組成物は、バインダー、溶媒、分散剤、及び被覆剤として機能する有機樹脂から選ばれた一つ又は複数の有機樹脂中に、金属粒子が分散又は溶解されている。このため、レーザ光を組成物に照射することにより、有機樹脂の一部が蒸発すると共に、金属粒子同士が焼成・癒着して導電層を形成することができる。このとき、導電層の一側面又は両側面に組成物が残存する。

また、レーザ光のビームスポットの幅を適宜制御することによって、任意の幅の導電層を形成することができる。このため、レーザビーム直接描画装置等を用い、組成物の幅よりも狭いビームスポット幅のレーザ光を照射することで、より幅の狭い導電層(代表的には、10μm以下、好ましくは、0.3〜1μm、さらに好ましくは0.5〜0.8μm)を形成することが可能である。このような導電層をゲート電極に用いることにより、短チャネル構造の半導体素子を形成することが可能であり、高速動作であり、且つ素子が高密度に集積された半導体装置を作製することが可能である。

また、導電層の一側面又は両側面に残存した組成物は、溶媒として機能する有機樹脂中に金属粒子が分散されている。このため、金属粒子の密度によって導電性、又は絶縁性を呈する。即ち、金属粒子の密度が高く、粒子同士の接触面積が高い場合、導電層の脇に設けられた組成物は導電性を呈する。一方、金属粒子の密度が低く、金属粒子の周りが有機樹脂で覆われている場合、導電層の一側面又は両側面に残存した組成物は絶縁性を示す。このため、導電層の一側面又は両側面に残存した組成物が絶縁性を示す場合、レーザ光が照射され形成された導電層のみが、配線又は電極として機能する。このため、縦横比が大きい(縦の長さ>横の長さ)導電層でも、倒れにくく安定した導電層を形成することができる。また、後に形成される絶縁層や半導体層のカバレッジ(被覆率)を高めることが可能であり、信頼性の高い半導体素子を形成することができる。

本発明は、以下の構成を包含する。

本発明の一は、基板上に形成された配線を有し、配線は第1の金属粒子が焼成された導電層であり、また、配線の側面には、第2の金属粒子が分散された有機樹脂層が設けられ、第1の金属粒子及び前記第2の金属粒子は、同一の金属元素で構成される配線基板である。このときの金属元素は、複数の金属元素で構成されていてもよい。

また、配線及び有機樹脂層に接する導電層、絶縁層又は半導体層が形成されていても良い。なお、有機樹脂層は配線の両側面又は一側面にのみ設けられている。このときの、配線は線状である。

また、有機樹脂層における金属元素の割合より、配線における金属元素の割合の方が大きい。

また、有機樹脂層における有機樹脂の割合より、配線における有機樹脂の割合の方が少ない。

また、配線の断面は、概略直角四角形又は概略台形状である。台形状の場合、配線表面の幅よりも基板に接する配線の幅が狭くとも良い。また、配線表面の幅よりも前記基板に接する配線の幅が広くともよい。

また、配線の幅は、0.3μm以上1μm以下、好ましくは、0.5μm以上0.8μm以下である。

また、本発明の一は、基板上に金属粒子と有機樹脂とで形成される組成物を吐出してパターンを形成し、パターンの一部にレーザ光を照射して、パターンに含まれる金属粒子の一部を焼成して配線を形成することを特徴とする配線基板の作製方法である。

また、本発明の一は、基板上に金属粒子と有機樹脂とで形成される組成物を吐出してパターンを形成し、パターンの一部にレーザ光を照射して、レーザ光が照射された領域の導電性を向上させることを特徴とする配線基板の作製方法である。

なお、レーザ光は、パターンの長軸と平行な方向へ走査することが好ましい。また、レーザ光は連続発振のレーザ光、又はパルス発振のレーザ光である。

また、本発明の一は、当該配線をゲート電極として有する半導体素子で構成される半導体装置である。半導体素子としては、TFT、電界効果トランジスタ(FET)、MOSトランジスタ、バイポーラトランジスタ、有機半導体トランジスタ、MIM素子、記憶素子、ダイオード、光電変換素子、容量素子、抵抗素子等が挙げられる。また、TFTとしては、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型TFT又はチャネル保護型TFT)、ボトムゲートTFT、トップゲートTFTのコプレナー型TFTがあげられる。

また、本発明の一は、基板上に金属粒子と有機樹脂とで形成される組成物を吐出してパターンを形成し、パターンの一部にレーザ光を照射して、パターンに含まれる金属粒子の一部を焼成してゲート電極を形成した後、ゲート電極及びマスクパターンのレーザ光が照射されなかった領域上に薄膜を成膜することを特徴とする半導体装置の作製方法である。

また、本発明において、半導体装置としては、半導体素子で構成された集積回路、表示装置、無線タグ、ICタグ等が挙げられる。表示装置としては、代表的には液晶表示装置、発光表示装置、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示装置があげられる。

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバイスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント配線(FPC:Flexible Printed Circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)やCPUが直接実装されたモジュールも全て表示装置に含むものとする。

本発明のように、金属粒子と有機樹脂とで形成される組成物の一部にレーザビームを直接照射して、金属粒子を焼成することにより、フォトマスクを用いずとも微細な幅の導電層を形成することができる。また、レーザビームの幅が狭く、組成物の一部にレーザビームを照射することで、液滴吐出法で形成した膜パターンの微細加工が可能となり、微細構造の半導体素子を形成することができる。更には、該導電層をゲート電極として用いることにより、チャネル長の短い半導体素子を形成することが可能であるため、高速動作が可能な半導体素子が高密度に集積された半導体装置を作製することが可能である。

また、液滴吐出法で滴下した組成物に含まれる金属粒子を、炉等を用いた加熱処理をせずに焼成し、導電層を形成することが可能である。このため、耐熱性の低いプラスチック基板や可とう性を有する基板を用いた配線基板及び半導体装置を作製することが可能である。このため、軽量で薄型の半導体装置及びそれを有する液晶テレビジョン並びにELテレビジョンを製造することが可能である。

また、膜パターンを形成する際に、液滴吐出法を用いることによって、それらの膜の材料を含む液滴の吐出口であるノズルと、基板との相対的な位置を変化させて任意の場所に液滴を吐出できる。また、ノズル径、液滴の吐出量、及びノズルと吐出物が形成される基板との移動速度の相対的な関係によって、形成する膜パターンの厚さや太さを調整できる。このため、一辺が1〜2mを越えるような大面積の基板上においても、所望の箇所に膜パターンを精度良く吐出形成することができる。また、隣り合う膜パターンとの不整合が生じないため、歩留まりを向上させることができる。この結果、少ない工程数で、歩留まり高く半導体装置を作製することが可能である。

さらには、上記の作製工程により形成された半導体装置を有する液晶テレビジョン並びにELテレビジョンを、低コストで、かつスループットや歩留まりを高く作製することができる。

以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

(実施の形態1)

本実施形態においては、レーザビーム(以下、レーザ光とも示す。)を照射して、幅の細い配線を形成する工程を図1〜図3を用いて説明する。

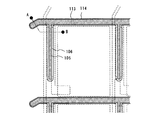

図2は、画素がマトリクス状に配列された基板101の上面図である。基板101上には、後に形成される半導体素子のゲート配線として機能する第2の導電層113及びそれに接続されるゲート電極として機能する第1の導電層105が実線で示されている。なお、破線は、後に形成される半導体素子のソース配線、半導体領域、ソース電極、ドレイン電極、画素電極等を示している。

図1は、図2のA−Bの断面を前面から見た斜視図である。図1(A)に示すように、基板101上に液滴吐出法により第1のパターンの材料を吐出し、乾燥させて第1のパターン102を形成する。なお、ここでは、液滴吐出法とは、調製された組成物の液滴を微細な孔から吐出して所定の形状のパターンを形成する方法をいう。

基板101としては、ガラス基板、石英基板、アルミナなどのセラミック基板、プラスチック基板、シリコンウェハ、金属板等を用いることができる。また、基板101としてガラス基板を用いる場合、320mm×400mm、370mm×470mm、550mm×650mm、600mm×720mm、680mm×880mm、1000mm×1200mm、1100mm×1250mm、1150mm×1300mmのような大面積基板を用いることができる。

プラスチック基板の代表例としては、PET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、またはポリフタールアミドからなるプラスチック基板、直径数nmの無機粒子が分散された有機材料で形成される基板等が挙げられる。また、基板の表面は平面である必要はなく、凹凸又は曲面を有するものでもよい。

第1のパターンの材料として吐出口から吐出する組成物は、導電体(金属粒子)を、有機樹脂に溶解又は分散させたものを用いる。金属粒子としては、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属、ハロゲン化銀の微粒子、又は分散性ナノ粒子を用いることができる。または、透明導電膜として用いられるITO(酸化インジウム酸化スズ合金)、酸化ケイ素を有するITO、有機インジウム、有機スズ、酸化亜鉛(ZnO)等の酸化物導電性材料を用いることができる。また、これらの材料からなる導電層を積層して第1のパターン102を形成することができる。また有機樹脂は、金属粒子のバインダー、溶媒、分散剤、及び被覆剤として機能する有機樹脂から選ばれた一つ又は複数を用いることができる。代表的には、ポリイミド、アクリル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂等や、公知の有機樹脂が挙げられる。

なお、組成物の粘度は5〜20mPa・s以下が好適であり、これは、乾燥が起こることを防止し、吐出口から金属粒子を円滑に吐出できるようにするためである。また、表面張力は40mN/mが好ましい。なお、用いる溶媒や用途に合わせて、組成物の粘度等は適宜調整するとよい。一例として、ITO、酸化ケイ素を有するITO、有機インジウム、有機スズを有機樹脂に溶解又は分散させた組成物の粘度は5〜20mPa・s、銀を有機樹脂に溶解又は分散させた組成物の粘度は5〜20mPa・s、金を有機樹脂に溶解又は分散させた組成物の粘度は10〜20mPa・sである。

また、組成物の導電体含有量は、30〜70wt%、望ましくは40〜60wt%であることが好ましい。組成物の溶媒を乾燥させて第1のパターンを形成するため、第1のパターンの導電体含有率は、組成物の導電体含有率より高い。

金属粒子の径は、各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細なパターンの作製のため、なるべく小さい方が好ましく、好適には粒径0.1μm以下が好ましい。金属粒子は、電解法、アトマイズ法又は湿式還元法等の公知の方法で形成されるものであり、その粒子サイズは、一般的に約0.5nm〜10μmである。ただし、ガス中蒸発法で形成すると、分散剤で保護されたナノ分子は約7nmと微細である。またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶媒中に凝集がなく、室温で安定に分散し、液体とほぼ同じ挙動を示す。

組成物を吐出する工程は、減圧下で行っても良い。これは、組成物を吐出して被処理物に着弾するまでの間に、該組成物の有機樹脂が揮発し、金属粒子の焼成の工程において、レーザ光のエネルギー密度を弱めることができるためである。

次にレーザビーム直接描画装置を用いて、第1のパターン102にレーザ光103を照射する。ここでは、矢印104に示す方向にレーザ光を移動する。本工程により、レーザ光が照射された領域における組成物中の有機樹脂を揮発させて除去する。また、レーザ光のエネルギーにより金属粒子の融合が進行し、図1(B)に示すような第1の導電層105が形成される。

レーザ光を第1のパターンに照射し、第1のパターン中の有機樹脂を揮発し除去するため、第1の導電層105の導電体含有率は、第1のパターンの導電体含有率より高い。

金属粒子が複数の金属元素で構成される場合、第1の導電層は、金属粒子と同様の組成となる。なお、照射されるレーザ光のエネルギーが高い場合、第1の導電層は、金属粒子とは異なる組成の合金となりうる。しかし、この場合においても第1の導電層に含まれる金属元素は、金属粒子と同様である。

レーザ光103が照射されない領域は、第1のパターンのまま残存する。第1の導電層の両側面に残存した第1のパターンを第1の有機樹脂層106と示す。なお、ここでは、第1の導電層の両側面に第1の有機樹脂層106が設けられるが、これに限られず、第1の導電層の片側面にのみ、第1の有機樹脂層106が設けられていても良い。第1の有機樹脂層は、金属粒子の分散割合に応じて導電性または絶縁性を有する。レーザ光の照射時の雰囲気は、酸素雰囲気、窒素雰囲気又は空気で行う。但し、金属粒子を溶解又は分散している有機樹脂が除去されやすい酸素雰囲気下で行うことが好適である。

ここで、レーザビーム直接描画装置について、図11を用いて説明する。図に示すように、レーザビーム描画装置1001は、レーザビームを照射する際の各種制御を実行するパーソナルコンピュータ(以下、PCと示す。)1002と、レーザビームを出力するレーザ発振器1003と、レーザ発振器1003の電源1004と、レーザビームを減衰させるための光学系(NDフィルタ)1005と、レーザビームの強度を変調するための音響光学変調器(AOM)1006と、レーザビームの断面の拡大又は縮小をするためのレンズ、光路を変更するためのミラー等で構成される光学系1007、Xステージ及びYステージを有する基板移動機構1009と、PCから出力される制御データをデジタルーアナログ変換するD/A変換部1010と、D/A変換部から出力されるアナログ電圧に応じて音響光学変調器1006を制御するドライバ1011と、基板移動機構1009を駆動するための駆動信号を出力するドライバ1012とを備えている。

レーザ発振器1003としては、紫外光、可視光、又は赤外光を発振することが可能なレーザ発振器を用いることができる。レーザ発振器としては、KrF、ArF、XeCl、Xe等のエキシマレーザ発振器、He、He−Cd、Ar、He−Ne、HF等の気体レーザ発振器、YAG、YVO4、YLF、YAlO3などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使った固体レーザ発振器、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザ発振器を用いることができる。なお、固体レーザ発振器においては、基本波の第2高調波〜第5高調波を適用するのが好ましい。

次に、レーザビーム直接描画装置を用いたレーザ光の照射方法について述べる。基板1008が基板移動機構1009に装着されると、PC1002は図外のカメラによって、基板に付されているマーカーの位置を検出する。次いで、PC1002は、検出したマーカーの位置データと、予め入力されている描画パターンデータとに基づいて、基板移動機構1009を移動させるための移動データを生成する。この後、PC1002が、ドライバ1011を介して音響光学変調器1006の出力光量を制御することにより、レーザ発振器1003から出力されたレーザビームは、光学系1005によって減衰された後、音響光学変調器1006によって所定の光量になるように光量が制御される。一方、音響光学変調器1006から出力されたレーザビームは、光学系1007で光路及びビーム形状を変化させ、レンズで集光した後、基板上の組成物(第1のパターン)に該ビームを照射して、組成物中の金属粒子を焼成する。このとき、PC1002が生成した移動データに従い、基板移動機構1009をX方向及びY方向に移動制御する。この結果、所定の場所にレーザビームが照射され、組成物中の金属粒子の焼成が行われる。

ここでは、レーザビームをX−Y軸方向に移動してレーザビームを照射する。この場合、光学系1007にポリゴンミラーやガルバノミラーを用いることが好ましい。

ここでは、Agを含む組成物(以下「Agペースト」という。)を選択的に吐出し、上記に示すようなレーザビームをAgペーストの一部に照射してAg粒子の焼成を適宜行い、膜厚600〜800nmの第1の導電層105を形成する。ここでは、レーザビームが照射された領域が第1の導電層となる。このため、レーザビームを一度走査した場合は、第1の導電層の幅は、概略ビームスポットの幅となる。このため、より微細な幅の第1の導電層を形成するためには、より低波長のレーザビームを照射することが好ましい。本実施形態においては、紫外光乃至赤外光のいずれかの波長を有するレーザ光を用いる。この結果、ビームスポットの幅を狭くすることが可能である。また、第1の導電層105は、ゲート電極として機能する。このため、第1のパターン102によりビームスポット幅の狭いレーザ光103を照射することで、短チャネル構造の半導体素子を形成することが可能である。このときの第1の導電層の幅は、0.3〜1μm、好ましくは0.5〜0.8μmであることが望ましい。この結果、短チャネル構造の半導体素子を形成することができる。また、第1の導電層105の両側面には、金属粒子が分散された有機樹脂層106が形成される。

なお、本実施形態では、第1のパターンにレーザ光を照射して導電層を形成する例を示したが、導電層の代わりに、半導体層、又は絶縁層を適宜形成することが可能である。この場合、第1のパターンに半導体材料又は絶縁材料を適宜用いればよい。

次に、図1(C)に示すように、第1の導電層105の一部をオーバーラップするように、第1のパターン102にレーザ光111を照射する。ここでは、矢印112の方向にレーザ光111を移動する。ここでは、ゲート配線を形成するため、レーザ光103よりもビーム幅の広いレーザ光111を照射することが好ましい。この結果、図1(D)に示すように、第2の導電層113が形成される。第2の導電層113は、金属粒子が焼成された導電層であり、その両側面に金属粒子が分散された第2の有機樹脂層114が形成される。なお、第2の有機樹脂層は、第2の導電層の片側面にのみ、設けられても良い。

このときの基板の上面図を図2に示す。ゲート電極として機能する第1の導電層105の両側面に金属粒子が分散された第1の有機樹脂層106が形成される。また、ゲート配線として機能する第2の導電層113の両側面に金属粒子が分散された第2の有機樹脂層114が形成される。また、第1の導電層105と第2の導電層113とは接続されている。

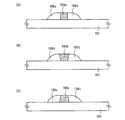

ここで、第1の導電層105の断面形状について、図3を用いて説明する。

図3(A)は、第1の導電層105において、レーザ光の走査方向(図1(A)の矢印104)に対して垂直な断面の拡大図である。第1の導電層105aの両側面に、金属粒子が分散された有機樹脂層106aが形成される。第1の導電層105aの断面形状は、概略直角四角形である。即ち、第1の導電層において、上表面の幅と、基板と接する面の幅とが概略一致する。

図3(B)は、図3(A)と同様の断面の拡大図である。第1の導電層105bの両側面に、金属粒子が分散された有機樹脂層106bが形成される。第1の導電層105bの断面形状は、概略台形状であり、第1の導電層の上表面の幅よりも、基板と接する第1の導電層の表面の幅の方が狭い。レーザビームのエネルギー強度が、ガウシアン形状を有し、基板に対してレーザビームのエネルギー分布が凸状である場合にこのような形状となる。

図3(C)は、図3(A)と同様の断面の拡大図である。第1の導電層105cの両側面に、金属粒子が分散された有機樹脂層106cが形成される。第1の導電層105cの断面形状は、概略台形状であり、第1の導電層の上表面の幅よりも、基板と接する第1の導電層の表面の幅の方が広い。基板101の熱伝導率が高い場合、照射されたレーザ光のエネルギーが横方向(基板表面に沿った方向)に伝導し、基板101側の導電層の幅が広くなり、このような形状となる。

なお、図3においては、第1の導電層105a〜105cは、基板表面まで導電層が形成されているが、この構造に限られず、第1の導電層と基板101との間に、金属粒子が分散された有機樹脂層が設けられていても良い。

次に、図3(A)において、焼成された金属粒子及び分散された金属粒子の様子を図31を用いて説明する。レーザ光が照射された第1の導電層105aは、複数の金属粒子が焼成された大きな金属粒子151が凝集している。このため、第1の導電層における有機樹脂の割合は少ない。一方、金属粒子が分散された有機樹脂層106aでは、多数の金属粒子153が有機樹脂152中に分散されている。このため、有機樹脂層における有機樹脂の割合は、第1の導電層における有機樹脂の割合と比較して高い。

以上の工程により、微細な幅の膜パターンを有する配線を形成することができる。

(実施の形態2)

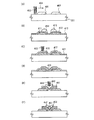

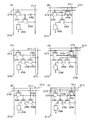

本実施形態では、半導体素子の作製方法について図4を用いて説明する。本実施形態では、半導体素子として、ボトムゲートTFTのチャネルエッチ型TFTを用いて説明する。

図4(A)に示すように、基板201上に第1のパターン202を液滴吐出法により形成する。第1のパターン202の材料としては、実施の形態1で示した第1のパターン102の材料を適宜用いることができる。

本実施形態では、第1のパターン202は、数nmの銀粒子が分散されたAgペーストを選択的に吐出する。

次に、レーザビーム直接描画装置を用いて、第1のパターン202の一部にレーザ光203を照射して、図4(B)に示すような、第1の導電層211を形成する。このとき、レーザ光203が照射されなかった領域は、Agペーストのまま残存する。以下、当該Agペーストのまま残存した領域を、金属粒子が分散された有機樹脂層212と示す。第1の導電層211は、導電体である微粒子が3次元に不規則に重なり合って形成されている。即ち、3次元凝集体粒子で構成されている。このため、表面は微細な凹凸を有する。また、Agペーストの加熱温度及び加熱時間により、微粒子が溶融し微粒子の集合体となる。このときの集合体の大きさは、Agペーストの加熱温度及び加熱時間により増大するため、表面の高低差が大きい導電層となる。なお、微粒子が溶融した領域は、多結晶構造となる場合もある。第1の導電層211の幅は、レーザビーム径に依存する。このため、ビーム径の小さなレーザ光を第1のパターンに照射することにより、幅の狭い第1の導電層を形成することができる。第1の導電層は後のゲート電極として機能するため、短チャネル構造のTFTを形成することができる。

このとき、オーバーラップしないように複数のレーザ光を第1のパターンに照射することで、マルチゲート電極を形成することができる。このため、後にマルチゲート構造のTFTを形成することができる。このとき、複数のレーザ光は平行となるように照射することが好ましい。

次に、図4(C)に示すように、第1の導電層211及び金属粒子が分散された有機樹脂層212上にゲート絶縁膜として機能する第1の絶縁層221、第1の半導体膜222、導電性を有する第2の半導体膜223を形成する。ここでは、第1のパターン202の材料となる組成物に含まれる有機樹脂が反応する温度よりも低い温度で、第1の絶縁層221以降の膜を形成することが好ましい。第1の絶縁層221以降の膜を有機樹脂の反応温度よりも高い温度で成膜すると、有機樹脂が反応してガスを放出する。このガスが原因となって、膜剥がれが生じ、半導体素子及びそれを有する半導体装置の歩留まりが低下する。よって、有機樹脂の反応温度よりも低い温度で成膜することで、歩留まりを向上させることが可能である。

第1の絶縁層221はプラズマCVD法またはスパッタリング法などの薄膜形成法を用い、窒化シリコン、酸化シリコン、その他の珪素を含む絶縁膜の単層又は積層構造で形成する。また、第1の絶縁層をゲート電極に接する側から、窒化珪素膜(窒化酸化珪素膜)、酸化珪素膜、及び窒化珪素膜(窒化酸化珪素膜)の積層構造とすることが好ましい。この構造では、ゲート電極が、窒化珪素膜と接しているため、酸化による劣化を防止することができる。

第1の半導体膜222としては、非晶質半導体(AS)、非晶質状態と結晶状態とが混在したセミアモルファス半導体(SASとも表記する)、非晶質半導体中に0.5nm〜20nmの結晶粒を観察することができる微結晶半導体、及び結晶性半導体から選ばれたいずれかの状態を有する膜で形成する。特に、0.5nm〜20nmの結晶を粒観察することができる微結晶状態はいわゆるマイクロクリスタル(μc)と呼ばれている。いずれも、シリコン、シリコン・ゲルマニウム(SiGe)等を主成分とする膜厚は、10〜60nmの半導体膜を用いることができる。

SASは、非晶質構造と結晶構造(単結晶、多結晶を含む)との中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体である。また短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。そして少なくとも膜中の一部の領域には、0.5〜20nmの結晶領域を観測することができ、珪素を主成分とする場合にはラマンスペクトルが520cm-1よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また未結合手(ダングリングボンド)を終端化させるために、SASは水素或いはハロゲンを1原子%、又はそれ以上含んでいる。

SASは、珪化物気体をグロー放電分解法により得ることができる。代表的な珪化物気体としては、SiH4であり、その他にもSi2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4などを用いることができる。珪化物気体を水素又はフッ素、若しくは水素又はフッ素とヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種又は複数種の希ガス元素とで希釈して用いることにより、SASの形成を容易なものとすることができる。このとき希釈率が10倍〜1000倍の範囲となるように、珪化物気体を希釈すると好ましい。またSi2H6及びGeF4を用い、ヘリウムガスで希釈する方法を用いてSASを形成することができる。グロー放電分解法による被膜の反応生成は減圧下で行うと好ましく、圧力は概略0.1Pa〜133Paの範囲で行えばよい。グロー放電を形成するための電力は1MHz〜120MHz、好ましくは13MHz〜60MHzの高周波電力を供給すればよい。基板温度は300度以下が好ましく、100〜250度の基板温度が推奨される。

また、結晶性半導体膜は、非晶質半導体膜又はSASを、加熱又はレーザ照射により結晶化して形成することができる。また、直接、結晶性半導体膜を形成してもよい。この場合、GeF4、又はF2等のフッ素系ガスと、SiH4、又はSi2H6等のシラン系ガスとを用い、熱又はプラズマを利用して直接、結晶性半導体膜を形成することができる。

第2の半導体膜223は導電性を有する。nチャネル型のTFTを形成する場合には、15属の元素、代表的にはリンまたはヒ素を添加する。また、pチャネルTFTを形成する場合には、13属の元素、代表的にはボロンを添加する。第2の半導体膜は、珪化物気体にボロン、リン、ヒ素のような13属又は15属の元素を有する気体を加えたプラズマCVD法で成膜する。また、半導体膜を成膜したのち、13属または15属の元素を有する溶液を半導体膜上に塗布しレーザビームを照射して導電性を有する第2の半導体膜を形成することができる。レーザビームとしては、公知のパルス発振のレーザ又は連続発振のレーザから照射されるレーザビームを適宜用いる。

次に、第2の半導体膜223上に第1のマスクパターン224を形成する。第1のマスクパターンは、耐熱性高分子材料を用いて形成することが好ましく、芳香環または複素環を主鎖にもち、脂肪族部分が少なく、且つ高極性のヘテロ原子基を含む高分子を液滴吐出により吐出して形成することが好ましい。そのような高分子物質の代表例としてはポリイミド又はポリベンゾイミダゾールなどが挙げられる。ポリイミドを用いる場合には、ポリイミドを含む溶液を、吐出口から第2の半導体膜223上に吐出し、200℃で30分焼成して形成することができる。

次に、第1のマスクパターン224を用いて第2の半導体膜223をエッチングし、図4(D)に示す第2の半導体領域232を形成する。次に、第1のマスクパターン224を用いて第1の半導体膜222をエッチングして、第1の半導体領域231を形成する。この後、第1のマスクパターンを除去する。

第1の半導体膜及び第2の半導体膜は、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3などを代表とするフッ素系ガス、あるいはO2を用いてエッチングすることができる。

次に、第2の半導体領域232上にソース電極及びドレイン電極として機能する第2のパターン251、252を、導電材料を用いて形成する。ここでは、数nmの銀粒子が分散された溶液Agペーストを選択的に吐出する。次に、レーザビーム直接描画装置を用いて、第2のパターン251、252の一部にレーザ光を照射して、図4(F)に示すような第2の導電層261、262を形成する。第2の導電層は、第1の導電層と同様に、金属粒子が焼成された導電層である。第2の導電層の両側面には、金属粒子が分散された有機樹脂層が形成されていてもよい。

次に、第2の導電層261、262をマスクとして、第2の半導体領域232の露出部をエッチングして分断してソース領域及びドレイン領域254、255を形成する。このとき、第1の半導体領域231の露出部が一部エッチングされる場合がある。

なお、第1の半導体領域がSASで形成されている場合、本実施形態のように、ソース領域及びドレイン領域がゲート電極を覆っている構造のほかに、ソース領域及びドレイン領域の端部とゲート電極の端部が一致しているいわゆるセルフアライン構造とすることができる。さらには、ソース領域及びドレイン領域がゲート電極を覆わず、一定の距離を隔てて形成されている構造とすることができる。この構造の場合、オフ電流を低減することができるため、該構成を有するTFTを表示装置のスイッチング素子として用いた場合、コントラストを向上させることができる。さらに、第2の半導体領域が複数のゲート電極を覆ういわゆるマルチゲート構造のTFTとしても良い。この場合も、オフ電流を低減することができる。

次に、第2の導電層261、262上に、パッシベーション膜を成膜することが好ましい。パッシベーション膜は、プラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化窒化アルミニウム、または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、その他の絶縁性材料を用いて形成することができる。

以上の工程により、ゲート電極の幅の狭いチャネルエッチ型TFTを作製することができる。該半導体素子は、チャネル長が短いため、高速動作が可能である。

(実施の形態3)

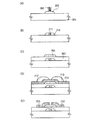

本実施形態では、半導体素子としてボトムゲートTFTにおいて、チャネル保護型TFTを、図5を用いて説明する。

図5(A)に示すように、実施の形態2と同様の工程により基板201上にゲート電極として機能する第1の導電層211及びその両側面に設けられた金属粒子が分散された有機樹脂層212を形成した後、ゲート絶縁膜として機能する第1の絶縁層221、第1の半導体膜222を形成する。次に、第1の半導体膜222上であって、且つ第1の導電層211に重畳する領域に保護膜301を形成する。保護膜301の形成方法及び材料は、実施の形態2に示す第1のマスクパターン224と同様のものを用いることができる。

次に、図5(B)に示すように、第2の半導体膜(導電性を有する半導体膜)302を成膜する。なお、第2の半導体膜302は、実施の形態2の第2の半導体膜223と同様の材料及び作製方法により形成することができる。次に、第1のマスクパターン224を形成する。

次に、第1のマスクパターンを用いて、図5(C)に示すように、第2の半導体膜をエッチングして、第2の半導体領域332を形成する。また、第1の半導体膜をエッチングして、第1の半導体領域231を形成する。この後、第1のマスクパターンを除去する。

次に、図5(D)に示すように、第2の導電層341を、導電材料を用いて形成する。導電材料としては、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、及びTiから選ばれる一つ又は複数を用いることができる。第2の導電層341は、CVD法、スパッタリング法、印刷法、液滴吐出法等公知の手法により形成する。ここでは、スパッタリング法により第2の導電層341を成膜する。

次に、第2の導電層341上に感光性樹脂342を吐出又は塗布したのち、乾燥させる。感光性樹脂は、紫外光から赤外光に感光する材料、ネガ型感光性樹脂又はポジ型感光性樹脂を用いる。

感光性樹脂としては、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の感光性を示す樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの感光性を示す有機材料等を用いることができる。代表的なポジ型感光性樹脂として、ノボラック樹脂やフェノール樹脂と感光剤であるナフトキノンジアジド化合物とを有する感光性樹脂が挙げられ、ネガ型感光性樹脂として、上記した樹脂等をベース樹脂として用い、ジフェニルシランジオール及び酸発生剤などを有する感光性樹脂が挙げられる。本実施形態では、ネガ型感光性樹脂を用いる。

次に、感光性樹脂342にレーザビーム直接描画装置を用いてレーザビーム343を照射した後、現像する。この結果、図5(E)に示すような、第2のマスクパターン351、352を形成する。

次に、図5(F)に示すように、第2のマスクパターン351、352をマスクとして、第2の導電層341をエッチングしてソース電極及びドレイン電極361、362を形成する。また、第2のマスクパターンをマスクとして第2の半導体領域332をエッチングしてソース領域及びドレイン領域363、364を形成する。この工程により、保護膜301が露出される。

なお、ソース電極及びドレイン電極の形成方法は、本実施形態に限られず実施の形態2に示される手法を用いても良い。また、本実施形態のソース電極及びドレイン電極の形成工程を実施の形態2に適用しても良い。

以上の工程により、ゲート電極の幅の狭いチャネル保護型TFTを作製することができる。該半導体素子は、チャネル長が短いため、高速動作が可能である。

(実施の形態4)

本実施形態においては、トップゲートTFTの中でも順スタガ型TFTの作製方法について、図6を用いて説明する。

図6(A)に示すように、基板201上に第1のパターン401、402を形成する。この材料及び作製方法は、実施の形態1の第1のパターン102と同様のものを適宜用いることができる。次に、第1のパターン401、402にレーザ光403を照射する。ここでは、矢印404の方向にレーザ光を照射して、図6(B)に示すような、金属粒子が焼成された第1の導電層411、412を形成する。

次に、第1の導電層上に導電性を有する第1の半導体膜413を成膜する。第1の半導体膜413は、実施の形態2に示される第2の半導体膜222と同様の材料及び作製方法により作製することができる。つぎに、第1の半導体膜413上に第1のマスクパターン414、415を形成する。第1のマスクパターンは、実施の形態2に示される第1のマスクパターン224と同様の材料及び作製方法を適宜用いて作製することができる。

次に、図6(C)に示すように、第1のマスクパターンを用いて第1の半導体膜をエッチングして第1の半導体領域416、417を形成する。なお、第1の半導体領域はソース領域及びドレイン領域として機能する。次に、第2の半導体膜421を成膜する。第2の半導体膜421は、実施の形態2に示される第1の半導体膜222と同様の材料及び手法を適宜用いて作製することが可能である。

次に、第2の半導体膜421の一部の表面にレーザビーム直接描画装置を用いてレーザ光を照射して、図6(D)に示すような、酸化珪素膜431を形成する。酸化珪素膜431は、第2の半導体膜421をエッチングするためのマスクとして機能する。次に、TMAH(テトラメチルアンモニウムハイドロオキサイド)を用いて、第2の半導体膜の露出部をエッチングして、図6(E)に示すように第2の半導体領域441を形成する。ここで、レーザビーム直接描画装置を用いて第2の半導体膜にレーザ光を照射することで、任意の領域を酸化し、酸化珪素膜を形成することが可能である。このため、公知のフォトリソグラフィー工程を用いずとも、所定の場所に半導体領域を形成することが可能である。また、レーザビームのスポット径を小さくすることで、レーザ光の照射面積を狭めることができる。即ち、微細な形状の酸化珪素膜及びそれをマスクとして形成される半導体領域を形成することができる。よって、半導体素子の高集積化が可能である。また、半導体領域の形状(矩形状、円形状、所定の形状等)のレーザ光を一度に照射して、酸化珪素膜を形成することで、スループットを向上させることが可能である。

次に、図6(E)に示すように、酸化珪素膜431上に、第2のパターン442を形成する。酸化珪素膜431はゲート絶縁膜として機能する。なお、酸化珪素膜431を除去した後、新たに実施の形態2の第1の絶縁層221と同様の手法及び材料を適宜用いて、ゲート絶縁膜として機能する絶縁層を形成しても良い。次に、第2のパターン442にレーザ光443を照射して、図6(F)に示すように、金属粒子が焼成された第2の導電層451及び金属粒子が分散された有機樹脂層452、453を形成することができる。第2の導電層451はゲート電極として機能する。

以上の工程により、順スタガ型TFTを作製することができる。

(実施の形態5)

本実施形態ではトップゲートTFTの中でもコプレナー型TFTの作製方法について、図7を用いて説明する。

図7(A)に示すように、基板201上に第1の絶縁層501を成膜する。第1の絶縁層501は、基板からの不純物が後に形成される半導体領域に拡散するのを防止するためのブロッキング膜として機能する。このため、第1の絶縁層501としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜を形成する。下地膜は単層膜または2層以上積層させた構造で形成する。

次に、第1の絶縁層501上に半導体膜502を形成する。半導体膜は、非晶質構造を有する半導体膜を公知の手段(スパッタリング法、LPCVD法、またはプラズマCVD法等)により成膜した後、公知の結晶化処理(パルス発振のレーザから射出されるレーザ光を用いたレーザ結晶化法、熱結晶化法、またはニッケルなどの金属触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜、又は実施の形態2で示したSAS、AS等で成膜する。

次に、半導体膜502の所定の領域に、実施の形態4と同様に、レーザビーム直接描画装置によってレーザ光503を照射して、図7(B)に示すような酸化珪素膜511を成膜する。ここでは、矢印504方向にレーザ光503を走査して、後に半導体領域を形成する領域にレーザ光を照射する。

次に、酸化珪素膜511をマスクとして、TMAHを用いて半導体膜502をエッチングして、半導体領域512を形成する。

次に、図7(C)に示すように、酸化珪素膜511を除去した後、半導体領域512及び第1の絶縁層501上にゲート絶縁膜として機能する第2の絶縁層521を成膜する。第2の絶縁層521としては、実施の形態2に示した第1の絶縁層221と同様の材料及び作製方法を用いて形成することができる。

次に、第1のパターン522を形成する。第1のパターンとしては、実施の形態1に示す第1のパターン102と同様の材料を用いて形成する。次に、第1のパターン522の一部にレーザ光523を照射して、図7(D)に示すような金属粒子が焼成された第1の導電層531及び金属粒子が分散された有機樹脂層532を形成することができる。なお、第1の導電層531は、ゲート電極として機能する。

次に、図7(E)に示すように、第1の導電層531及び金属粒子が分散された有機樹脂層532をマスクとして半導体領域512に不純物を添加する。次に、水素を含む絶縁膜を成膜した後、400〜550度に加熱して半導体領域に添加された不純物元素を活性化し、また半導体領域の水素化を行って、不純物領域(ソース領域及びドレイン領域)541、542を形成する。また、第1の導電層531及び金属粒子が分散された有機樹脂層532に覆われる半導体領域は、チャネル形成領域543として機能する。なお、活性化又は水素化の工程として、加熱処理の代わりに、GRTA法、LRTA法、レーザー・アニール法を用いることもできる。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体膜を結晶化させている場合、活性化と同時にゲッタリングを行うことができる。

なお、本実施形態では、シングルゲート構造のTFTを示したが、これに限らずマルチゲート構造のものでもよい。また、セルフアライン構造のTFTを示したが、これに限らず低濃度ドレイン(LDD:Lightly Doped Drain)構造若しくはGOLD(Gate−drain Overlapped LDD)構造のTFTを用いることができる。LDD構造は、チャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。この構造のTFTは、オフ電流値を低減することができる。GOLD構造は、ゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた構造であり、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。

また、金属粒子が分散された有機樹脂層532をサイドウォールとして用いて半導体領域に不純物元素を添加し、LDD領域を形成してもよい。

次に、基板上に第3の絶縁層544を形成する。第3の絶縁層の材料としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシリカガラスに代表されるシロキサンポリマー系材料を出発材料として形成されたSi−O−Si結合を含む無機シロキサン材料、アルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表される珪素に結合される水素がメチルやフェニルのような有機基によって置換された有機シロキサンポリマー系の絶縁材料を用いることができる。形成方法としては、CVD法、塗布法、印刷法等公知の手法を用いて形成する。なお、塗布法で形成することにより、第2の絶縁層の表面を平坦化することが可能であり、後の画素電極の形成に適している。ここでは、塗布法によりアルキルシロキサンポリマーを塗布し焼成して第3の絶縁層544を形成する。

次に、液滴吐出法によりマスクパターンを形成し、該マスクパターンを用いて第2の絶縁層544及び第2の絶縁層521の一部を除去して、半導体領域の不純物領域541、542の一部を露出して、開口部を形成する。次に、開口部に実施の形態2又は実施の形態3に記載の手法を適宜用いて、第2の導電層545、546を形成する。第2の導電層545、546はソース電極及びドレイン電極として機能する。

以上の工程により、ゲート電極の幅の狭いコプレナー型TFTを作製することができる。該半導体素子は、チャネル長が短いため、高速動作が可能である。

(実施の形態6)

本実施形態では、有機半導体トランジスタの作製工程を、図8を用いて説明する。

図8(A)及び図8(B)に示すように、実施の形態2と同様に基板201上に第1のパターン202を形成した後、第1のパターン202の一部にレーザ光203を照射することで、金属粒子が焼成された第1の導電層211及びその両側面に設けられた金属粒子が分散された有機樹脂層212を形成する。ここでは、基板201にプラスチックを用いる。

次に、図8(C)に示すように、基板201、第1の導電層211、及び有機樹脂層212上にゲート絶縁膜として機能する第1の絶縁層601を形成する。第1の絶縁層としては、実施の形態2で示される第1の絶縁層221の材料及び手法を適宜用いることができる。また、液滴吐出法、塗布法等を用いて、絶縁性を有する溶液を塗布して形成することができる。また、第1の導電層211を陽極酸化して、第1の絶縁層を形成してもよい。絶縁性を有する溶液の代表例としては、無機酸化物の微粒子が分散された溶液、ポリイミド、ポリアミド、ポリエステル、アクリル、PSG(リンガラス)、BPSG(リンボロンガラス)、シリケート系SOG(Spin on Glass)、アルコキシシリケート系SOG、シロキサンポリマー等を適宜用いることができる。このときは、絶縁性を有する溶液を乾燥、材料によっては焼成する。

次に、第2の導電層602を形成する。ここでは、実施の形態3の第2の導電層341と同様の手法及び材料により形成することができる。次に、第2の導電層602上に第1のマスクパターン603、604を形成する。該マスクパターンは、実施の形態2の第1のマスクパターン224と同様の材料を用いて形成する。第1のマスクパターン603、604は、後のソース電極及びドレイン電極を形成するためのマスクパターンである。

次に、図8(D)に示すように、第1のマスクパターン603、604を用いて第2の導電層602をエッチングして、第3の導電層611、612を形成する。第3の導電層611、612はソース電極及びドレイン電極として機能する。次に、ソース電極及びドレイン電極の間に、有機半導体材料を用いて半導体領域613を形成する。

半導体領域613の形成方法としては、印刷法、スプレー法、液滴吐出法などを適宜用いることが可能である。この手法により、エッチング工程が必要ないため、工程数を削減することが可能である。また、有機半導体材料としては、公知の有機半導体材料を適宜用いることができる。代表例としては、骨格が共役二重結合から構成されるπ電子共役系の高分子材料が望ましい。代表的には、ポリチオフェン、ポリ(3−アルキルチオフェン)、ポリチオフェン誘導体、ペンタセン等の可溶性の高分子材料を用いることができる。

その他にも、可溶性の前駆体を成膜した後で処理することにより半導体領域を形成することができる。なお、このような前駆体を経由する有機半導体材料としては、ポリチエニレンビニレン、ポリ(2,5−チエニレンビニレン)、ポリアセチレン、ポリアセチレン誘導体、ポリアリレンビニレンなどがある。

前駆体を有機半導体に変換する際には、加熱処理だけではなく塩化水素ガスなどの反応触媒を添加することがなされる。また、これらの可溶性有機半導体材料を溶解させる代表的な溶媒としては、トルエン、キシレン、クロロベンゼン、ジクロロベンゼン、アニソール、クロロホルム、ジクロロメタン、γ−ブチルラクトン、ブチルセルソルブ、シクロヘキサン、NMP(N−メチル−2−ピロリドン)、シクロヘキサノン、2−ブタノン、ジオキサン、ジメチルホルムアミド(DMF)または、THF(テトラヒドロフラン)などを適用することができる。

さらに、半導体領域613とソース電極及びドレイン電極として機能する導電層611、612との間に、コンタクト層を設けても良い。コンタクト層の材料としては、ポリアセチレン、ポリアニリン、PEDOT(poly−ethylenedioxythiophen)、PSS(poly−styrenesulphonate)のような有機導電性材料で形成される導電層を形成することができる。また、コンタクト層に金属元素で形成される導電層を用いることができる。この場合、多くの有機半導体材料がキャリアとして正孔を輸送するp型半導体であることからその半導体層とオーミック接触を取るために仕事関数の大きい金属を用いることが望ましい。代表的には、金や白金、クロム、パラジウム、アルミニウム、インジウム、モリブデン、ニッケル等の金属又は合金等が望ましい。これらの金属又は合金材料を用いた導電性ペーストを用いて印刷法、液滴吐出法で形成することができる。

以上の工程により、短チャネル構造の有機薄膜トランジスタを形成することができる。

(実施の形態7)

本実施形態においては、実施の形態6において、ソース電極及びドレイン電極と半導体領域との位置関係が異なる半導体素子の作製方法について、図9を用いて説明する。

図9(A)及び図9(B)に示すように、実施の形態2と同様に基板201上に第1のパターン202を形成した後、第1のパターン202の一部にレーザ光203を照射する。つぎに、金属粒子が焼成された第1の導電層211及びその両側面に設けられた金属粒子が分散された有機樹脂層212を形成する。

次に、図9(C)に示すように、基板201、第1の導電層211、及び有機樹脂層212上にゲート絶縁膜として機能する第1の絶縁層601を形成する。次に、第1の絶縁層601上に、半導体領域701を形成する。半導体領域701の材料及び形成方法は、実施の形態6に記載の材料及び手法を適宜用いる。

次に、図9(D)に示すように、第1の絶縁層601及び半導体領域701上に第3の導電層711を形成する。次に第2の導電層711上に第1のマスクパターン712、713を形成する。第2の導電層711及び第1のマスクパターン712、713はそれぞれ、実施の形態6に示される第2の導電層602及び第1のマスクパターン603、604を適宜用いることができる。第1のマスクパターンは、後に形成されるソース電極及びドレイン電極を形成するためのマスクとして機能する。

次に、図9(E)に示すように、第1のマスクパターン712、713を用いて第2の導電層711をエッチングして、ソース電極及びドレイン電極721、722を形成する。本実施形態で作製される半導体素子は、半導体領域701が、ゲート絶縁膜として機能する第1の絶縁層601と、ソース電極及びドレイン電極721、722の一方とで挟まれている領域がある。

以上の工程により、短チャネル構造の有機薄膜トランジスタを形成することができる。

(実施の形態8)

本実施形態では、上記実施形態におけるマスクパターン形成に用いることができる液滴吐出装置について説明する。図10では、基板1900上において、1つのパネル1930が形成される領域を点線で示す。

図10には、配線等のパターンの形成に用いる液滴吐出装置の一態様を示す。液滴吐出手段1905は、ヘッドを有し、ヘッドは複数のノズルを有する。本実施の形態では、十個のノズルが設けられたヘッドを三つ(1903a、1903b、1903c)有する場合で説明するが、ノズルの数や、ヘッドの数は処理面積や工程等により設定することができる。

ヘッドは、制御手段1907に接続され、制御手段がコンピュータ1910により制御することにより、予め設定されたパターンを描画することができる。描画するタイミングは、例えば、ステージ1931上に固定された基板1900等に形成されたマーカー1911を基準点として行えばよい。また、基板1900の縁を基準点として行ってもよい。これら基準点をCCDなどの撮像手段1904で検出し、画像処理手段1909にてデジタル信号に変換させる。デジタル変換された信号をコンピュータ1910で認識して、制御信号を発生させて制御手段1907に送る。このようにパターンを描画するとき、パターン形成面と、ノズルの先端との間隔は、0.1cm〜5cm、好ましくは0.1cm〜2cm、さらに好ましくは0.1cm前後とするとよい。このように間隔を短くすることにより、液滴の着弾精度が向上する。

このとき、基板1900上に形成されるパターンの情報は記憶媒体1908に格納されており、この情報を基にして制御手段1907に制御信号を送り、各ヘッド1903a〜1903cを個別に制御することができる。すなわち、ヘッド1903a〜1903cが有する各ノズルから異なる組成物の液滴を吐出することができる。例えばヘッド1903a、1903bが有するノズルは絶縁膜を形成する組成物の液滴を吐出し、ヘッド1903cが有するノズルは導電膜を形成する組成物の液滴を吐出することができる。

さらに、ヘッドが有する各ノズルを個別に制御することもできる。ノズルを個別に制御することができるため、特定のノズルから異なる組成物の液滴を吐出することができる。例えば同一ヘッド1903aに、導電膜を形成する組成物の液滴を吐出するノズルと、絶縁膜を形成する組成物の液滴を吐出するノズルとを設けることができる。

なお、ノズルは組成物が充填されたタンクと接続されている。

また、層間絶縁膜の形成工程のように大面積に対して液滴吐出処理を行う場合、層間絶縁膜を形成する組成物の液滴を全ノズルから吐出させるとよい。さらに、複数のヘッドが有する全ノズルから、層間絶縁膜を形成する組成物の液滴を吐出するとよい。その結果、スループットを向上させることができる。もちろん、層間絶縁膜形成工程において、一つのノズルから層間絶縁膜を形成する組成物の液滴を吐出し、複数走査することにより大面積に対して液滴吐出処理を行ってもよい。

そしてヘッドをジグザグ又は往復させ、大型マザーガラスに対するパターン形成を行うことができる。このとき、ヘッドと基板を相対的に複数回走査させればよい。ヘッドを基板に対して走査するとき、進行方向に対してヘッドを斜めに傾けるとよい。

ヘッドの幅は、大型マザーガラスから複数のパネルを形成する場合、ヘッドの幅は1つのパネルの幅と同程度とすると好ましい。1つのパネル1930が形成される領域に対して一回の走査でパターン形成することができ、高いスループットが期待できるからである。

また、ヘッドの幅は、パネルの幅より小さくしてもよい。このとき、複数の幅の小さなヘッドを直列に配置し、1つのパネルの幅と同程度としてもよい。複数の幅の小さなヘッドを直列に配置することにより、ヘッドの幅が大きくなるにつれて懸念されるヘッドのたわみの発生を防止することができる。もちろん、幅の小さなヘッドを複数回走査することにより、パターン形成を行ってもよい。

また、液滴吐出法として、ピエゾ方式を用いることができる。ピエゾ方式は、液滴の制御性に優れインク選択の自由度の高いことからインクジェットプリンターでも利用されている。なお、ピエゾ方式には、ベンダー型、(代表的にはMLP(Multi Layer Piezo)タイプ)と、ピストン型(代表的にはMLChip(Multi Layer Ceramic Hyper Integrated Piezo Segments)タイプ)、サイドウォール型、ルーフウォール型がある。また溶液の溶媒によっては、発熱体を発熱させ気泡を生じさせ溶液を押し出す、いわゆるサーマル方式を用いた液滴吐出法でもよい。

本実施例では、Agペーストを用いてパターンを形成し、該パターンを仮焼成した試料と、Agペーストを用いてパターンを形成し、該パターンにレーザ光を照射してAg粒子を焼成した試料の抵抗値について図32を用いて説明する。

ガラス基板上にAgペーストを液滴吐出法によって滴下し、条件1によって仮焼成した試料の抵抗値と、条件2によって焼成した試料の抵抗値の比較結果を表1に示すと共に、そのグラフを図32に示す。このとき抵抗値を測定した各試料の形状は、図32(B)に示すような、長軸の幅D1が1000μm、短軸の幅D2が200μmの楕円状である。なお、条件1は、100度で30分加熱する条件である。また、条件2は、連続発振のYVO4レーザから発振されるレーザ光(レーザパワー2W、レーザビームの直径80μm、レーザ光の波長532nm)を照射する。このときのスキャン速度は50cm/secである。

表1及び図32から分かるように、条件2の処理により試料の抵抗値が低下している。すなわち、金属粒子を含むペーストにレーザ光を照射することにより、金属粒子が焼成され、抵抗値を低下させることが可能である。

次に、アクティブマトリクス基板及びそれを有する表示パネルの作製方法について図12〜図16を用いて説明する。本実施例では、表示パネルとして液晶表示パネルを用いて説明する。図16は、アクティブマトリクス基板の上面図であり、接続端子部のA−B及び画素部のC−Dに対応する縦断面構造を図12〜15に模式的に示す。

図12(A)に示すように、基板800表面を400度で酸化して膜厚100nmの絶縁膜801を形成する。次に、絶縁膜801上に第1の導電層802を形成する。第1の導電層802の代表例としては、透光性を有する導電膜、又は反射性を有する導電膜がある。透光性を有する導電膜の材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)、酸化珪素を含む酸化インジウムスズ等が挙げられる。また、反射性を有する導電膜の材料としては、アルミニウム(Al)、チタン(Ti)、銀(Ag)、タンタル(Ta)などの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料、若しくは該金属の窒化物である窒化チタン(TiN)、窒化タンタル(TaN)、若しくは1〜20%のニッケルを含むアルミニウムなどが挙げられる。また、第1の導電層802の形成方法としては、スパッタリング法、蒸着法、CVD法、塗布法等を適宜用いる。ここでは、基板800として、旭硝子社製AN100ガラス基板を用い、第1の導電層802として、スパッタリング法により膜厚110nmの酸化珪素を含むインジウム錫酸化物(ITO)を成膜する。

次に、液滴吐出法により第1の導電層802上に第1のマスクパターン803を形成する。第1のマスクパターンは、後に形成する第2のマスクパターン(導電層をエッチングするためマスクとして機能する膜)を形成するためのマスクとして機能する。このため、塗れ性が低いことが好ましい。即ち、表面において、後に形成する第2のマスクパターンを弾きやすいことが好ましい。ここでは、フッ素系シランカップリング剤をアルコール溶媒に溶解した溶液を用いて第1のマスクパターンを形成する。

次に、液滴吐出法により第2のマスクパターン804を形成する。第2のマスクパターン804は、塗れ性の高い材料を液滴吐出法によって吐出する。第2のマスクパターン804は、ポリイミドを液滴吐出法により吐出し、200度で30分加熱して焼成して形成する。

ここで、図30を用いて塗れ性の低い領域と塗れ性の高い領域の関係について示す。塗れ性の低い領域(ここでは、第1のマスクパターン803)とは、図30に示すように、表面において液体の接触角θ1が大きい領域である。この表面上では液体は、半球状にはじかれる。一方、塗れ性の高い領域(ここでは、第2のマスクパターン804)は、表面において液体の接触角θ2が小さい領域である。この表面上では、液体は塗れ広がる。

このため、接触角の異なる二つの領域が接している場合、相対的に接触角の小さい領域が塗れ性の高い領域となり、接触角の大きい方の領域が塗れ性の低い領域となる。この二つの領域上に溶液を塗布又は吐出した場合、溶液は、塗れ性が低い領域表面に塗れ広がり、塗れ性が高い領域との界面で半球状にはじかれる。

塗れ性の低い領域の接触角θ1と塗れ性の高い領域の接触角θ2の差は、30度、望ましくは40度以上であることが好ましい。この結果、塗れ性の低い領域の表面で塗れ性の高い領域の材料が半球状にはじかれ、自己整合的に各マスクパターン803、804を形成することが可能である。

次に、図12(B)に示すように、第1のマスクパターン803を、酸素を用いたアッシングにより除去した後、第2のマスクパターン804に覆われていない第1の導電層802をエッチングして除去する。次に、第2のマスクパターン804を除去して、第2の導電層805を形成する。第2の導電層805は、画素電極として機能する。

次に、図12(C)に示すように、第1のパターン811、812を形成する。第3の導電層は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属粒子と有機樹脂で形成される組成物を液滴吐出法により吐出して形成する。ここでは、第2の導電層805と接して酸化物を形成しにくい導電材料を用いることが好ましい。

次に、第1のパターン811、812それぞれ一部にレーザ光813、814を照射して、図13(A)に示すような金属粒子が焼成された第3の導電層815、816を形成する。このとき、第1のパターン811、812においてレーザ光が照射されなかった領域は、金属粒子が分散された有機樹脂層817、818である。第3の導電層815は後のゲート配線として機能し、第3の導電層816は後のゲート電極として機能する。

次に、スパッタリング法によりゲート絶縁膜821を成膜する。ゲート絶縁膜821としては、膜厚110nmの窒化酸化珪素膜(SiNO(N>O))を成膜する。

次に、第1の半導体膜822及びn型を呈する第2の半導体膜823を成膜する。第1の半導体膜822としては、スパッタリング法により膜厚150nmのアモルファスシリコン膜を成膜する。次に、アモルファスシリコン膜の表面の酸化膜を除去した後、第2の半導体膜823として、同様の手法により膜厚50nmのセミアモルファスシリコン膜を成膜する。ここでは、スパッタリング法で第1の半導体膜及び第2の半導体膜を成膜するため、室温で成膜が可能である。

次に、第2の半導体膜上に第3のマスクパターン824、825を形成する。第3のマスクパターンは、ポリイミドを液滴吐出法により第2の半導体膜上に吐出し、200度で30分加熱して形成する。第3のマスクパターン824、825は、後の第1の半導体領域が形成される領域上に吐出する。

次に、図13(B)に示すように、第3のマスクパターンを用いて第2の半導体膜823をエッチングして第2の半導体領域(ソース領域及びドレイン領域、コンタクト層)826を形成する。第2の半導体膜を、流量比がCF4:O2=10:9の混合ガスを用いてエッチングする。この後、第3のマスクパターン824、825を剥離液を用いて剥離する。

次に、第2の半導体領域826及びその間に形成されている第1の半導体膜822を覆う第4のマスクパターン831を形成する。第4のマスクパターンは、第3のマスクパターンと同様の材料及び手法により形成する。第4のマスクパターンを用いて、第1の半導体膜822をエッチングして、図13(C)に示すような第1の半導体領域832を形成すると共にゲート絶縁膜821の一部を露出する。第1の半導体膜を、流量比がCF4:O2=10:9の混合ガスを用いてエッチングした後、酸素を用いたアッシングを行う。この後、第4のマスクパターン831を剥離液を用いて剥離する。

次に、図14(A)に示すように、第5のマスクパターン841、842を形成する。第5のマスクパターンは、液滴吐出法によりゲート絶縁膜821と第2の導電層805とが重畳する領域及び接続端子部に、塗れ性の低い溶液を吐出する。ここでは、塗れ性の低い溶液として、フッ素系シランカップリング剤をアルコール溶媒に溶解した溶液を用いる。第5のマスクパターン841、842は、後のドレイン電極と第2の導電層805とが接続する領域にコンタクトホールを形成するために用いる第6のマスクパターンを形成するための保護膜である。また、第6のマスクパターンは接続端子部の導電層を露出するための保護膜でもある。

次に、第6のマスクパターン843を形成する。第6のマスクパターンは、コンタクトホールを形成するためのマスクであり、ポリイミドを液滴吐出法により吐出し、200度で30分加熱して形成する。このとき、第5のマスクパターン841は塗れ性が低い材料で形成されており、第6のマスクパターン843は塗れ性の高い材料で形成されているため、第5のマスクパターンが形成される領域には、第6のマスクパターン843は形成されない。

次に、酸素アッシングにより第5のマスクパターン841、842を除去してゲート絶縁膜821の一部を露出する。次に、第6のマスクパターン843を用いて、露出されたゲート絶縁膜の一部をエッチングしてコンタクトホール844を形成する。ゲート絶縁膜は、CHF3を用いてエッチングする。この後、酸素アッシング及び剥離液を用いたエッチングにより第6のマスクパターンを剥離する。

次に、図14(C)に示すように、第4の導電層851、852を液滴吐出法で形成する。第4の導電層は、後のソース配線層及びドレイン配線層となる。ここでは、第4の導電層851、852は、Ag(銀)粒子が分散された組成物を吐出し、100度で30分加熱して乾燥した後、レーザ光を照射して金属粒子を焼成して形成する。

以上の工程により、アクティブマトリクス基板を形成することができる。なお、図14(C)の縦断面構造A−B及びC−Dに対応する平面構造を図16に示すので同時に参照する。

次に、図15(A)に示すように、保護膜861を成膜する。保護膜は、シリコンターゲット、及びスパッタリングガスとしてアルゴン並びに窒素(流量比Ar:N2=1:1)を用いたスパッタリング法により、膜厚100nmの窒化珪素膜を成膜する。

次に、保護膜861を覆うように印刷法やスピンコート法により、絶縁膜を成膜し、ラビングを行って配向膜862を形成する。なお、配向膜862は、斜方蒸着法により形成することもできる。

次に、配向膜883及び第2の画素電極(対向電極)882が設けられた対向基板881において、画素部の周辺の領域に液滴吐出法により閉ループ状のシール材871を形成する。ディスペンサ式(滴下式)により、シール材871で形成された閉ループ内側に、液晶材料を滴下する。

シール材871には、フィラーが混入されていてもよく、さらに、対向基板881にはカラーフィルタや遮蔽膜(ブラックマトリクス)などが形成されていても良い。

ここで、図17を用いて、液晶材料を滴下する工程を示す。図17(A)は、ディスペンサ2701によって液晶材料を滴下する工程の斜視図であり、図17(B)は、図17(A)のA―Bにおける断面図である。

シール材2702で囲まれた領域2703を覆うように液晶材料2704をディスペンサ2701から滴下、または、吐出させている。ディスペンサ2701を移動させてもよいし、ディスペンサ2701を固定し、基板2700を移動させることによって液晶層を形成することができる。また、複数のディスペンサ2701を設置して、同時に複数の領域に液晶材料を滴下してもよい。この結果、図17(B)に示すように、シール材2702で囲まれた領域のみに選択的に液晶材料2704を滴下、または吐出させることができる。

また、ここでは画素部に液晶材料を滴下したが、対向基板側に液晶材料を滴下した後、画素部を有する基板を貼り合わせても良い。

次に、図15(A)に示すように、真空中で、配向膜883及び第2の画素電極(対向電極)882が設けられた対向基板881とアクティブマトリクス基板とを貼り合わせ、紫外線硬化を行って、液晶材料が充填された液晶層884を形成する。なお、液晶層884を形成する方法として、ディスペンサ式(滴下式)の代わりに、対向基板を貼り合わせてから毛細管現象を用いて液晶材料を注入するディップ式(汲み上げ式)を用いることができる。

次に、図15(B)に示すように、第3の導電層815、ソース配線層(図示しない)それぞれの端部上に絶縁膜が形成されている場合、該絶縁膜を除去した後、接続導電層885を介して接続端子(第3の導電層に接続される接続端子886、ソース配線層に接続される接続端子は図示せず。)を貼り付ける。さらに、各配線層と接続端子との接続部を封止樹脂で封止することが好ましい。この構造により、断面部からの水分が画素部に侵入し、劣化することを防ぐことができる。以上の工程により、液晶表示パネルを形成することができる。

以上の工程により液晶表示パネルを作製することができる。なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とソース配線(ゲート配線)の間または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部のゲート配線層とダイオードのドレイン又はソース配線層とを接続することにより、静電破壊を防止することができる。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。

本実施例では、表示パネルとして発光表示パネルの作製方法について図19〜図22を用いて説明する。画素部の平面構造を図22に示し、図19〜図21は、図22の画素部のA−B、及びC−Dに対応する縦断面構造を模式的に示したものである。

図19(A)に示すように、基板2001上に第1の絶縁層2002を膜厚100〜1000nmで形成する。ここでは、第1の絶縁層として、プラズマCVD法を用いた膜厚100nmの酸化シリコン膜と減圧熱CVD法を用いた膜厚480nmの酸化シリコン膜を積層させて形成する。

次に、非晶質半導体膜を膜厚10〜100nmで形成する。ここでは減圧熱CVD法を用いて膜厚50nmの非晶質シリコン膜を形成する。次に、この非晶質半導体膜を結晶化させる。本実施例では、非晶質シリコン膜にレーザ光を照射して結晶性シリコン膜を形成する。次に、結晶性シリコン膜の不要な部分を除去して半導体領域2003、2004を形成する。次に、ゲート絶縁膜として機能する第2の絶縁層2005を形成する。ここでは、CVD法により第2の絶縁層2005として酸化珪素膜を成膜する。

次いで、TFTのチャネル領域となる領域にp型またはn型の不純物元素を低濃度に添加するチャネルドープ工程を全面または選択的に行う。このチャネルドープ工程は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加する。なお、質量分離を行うイオンインプランテーション法を用いてもよい。

次に、第1のパターン2006〜2009を形成したのち、レーザ光2010〜2013を照射して、図19(B)に示すような、ゲート電極として機能する第1の導電層2014〜2016、および容量配線として機能する第1の導電層2017を形成する。また、この工程と同時にレーザ光2010〜2013が照射されなかった領域には、金属粒子が分散された有機樹脂層2018〜2021が形成される。ここでは、液滴吐出法によりAgペーストを吐出し、レーザ光を照射する。

次いで、図20(A)に示すように、第1の導電層2014〜2017及び金属粒子が分散された有機樹脂層2018〜2021をマスクとして、自己整合的にリンを半導体領域に添加して、高濃度不純物領域2030〜2034を形成する。高濃度不純物領域のリンの濃度が1×1020〜1×1021atoms/cm3(代表的には2×1020〜5×1020atoms/cm3)となるように調整する。なお、半導体領域2003、2004のうち、第1の導電層2014〜2017及び金属粒子が分散された有機樹脂層2018〜2021と重なる領域はチャネル形成領域となる。

次いで、第1の導電層2014〜2017を覆う第3の絶縁層2035を形成する。ここでは、水素を含む絶縁膜を成膜する。この後、半導体領域に添加された不純物元素の活性化および半導体領域の水素化を行う。水素を含む絶縁膜は、スパッタリング法により得られる窒化酸化珪素膜(SiNO膜)を用いる。

次いで、半導体領域に達する開口部を形成した後、第2の導電層2041〜2044を形成する。第2の導電層2041はソース配線として機能し、第2の導電層2042は第1の接続配線として機能し、第2の導電層2043は電源線として機能し、第2の導電層2044は第2の接続配線として機能する。本実施例ではTi膜と、アルミニウムーシリコン合金膜と、Ti膜とをスパッタ法で連続して形成した3層構造の積層膜を成膜した後、所望の形状にエッチングして第3の導電層を形成する。

次に、図20(B)に示すように、第4の絶縁層2051を形成する。第4の絶縁層としては、平坦化が可能な絶縁層が好ましい。平坦化が可能な絶縁層としては、実施の形態5で示される第3の絶縁層544と同様の材料及び手法を適宜用いることができる。ここではアクリル樹脂を成膜する。なお、第4の絶縁層として、黒色顔料、色素などの可視光を吸収する材料を溶解又は分散させてなる有機材料を用いることで、後に形成される発光素子の迷光の吸収が第4の絶縁層に吸収され、各画素のコントラスト向上が可能である。

次に、第4の絶縁層に公知のフォトリソグラフィー及びエッチングにより第4の絶縁層に開口部を設けると共に、第2の導電層(第2の接続配線)2044の一部を露出する。次に、第3の導電層2052を形成する。第3の導電層2052としては、反射導電膜と透明導電膜を積層して成膜する。ここでは、1〜20%のニッケルを含むアルミニウム膜と酸化珪素を有するITOをスパッタリング法で積層する。なお、1〜20%のニッケルを含むアルミニウムは、酸化物であるITOと接しても電食しないため好ましい。

次に、液滴吐出法により第1のマスクパターン2053を形成する。次に、液滴吐出法により第2のマスクパターン2054を形成する。第1のマスクパターン2053は、塗れ性の低い材料、ここではフッ素系シランカップリング剤をアルコール溶媒に溶解した溶液を液滴吐出法によって吐出する。第2のマスクパターン2054は、ポリイミドを液滴吐出法により吐出し、200度で30分加熱して焼成して形成する。

次に、図21(A)に示すように、第1のマスクパターン2053を酸素を用いたアッシングにより除去した後、第2のマスクパターン2054で覆われていない第3の導電層2052をエッチングして除去する。次に、第2のマスクパターン2054を除去して、第4の導電層2055を形成する。第5の導電層は、第1の画素電極として機能する。なお、図21(A)の縦断面構造A−B及びC−Dに対応する平面構造を図22に示すので同時に参照する。

次に、第4の導電層2055の端部を覆って、隔壁(バンク、障壁、土手などとも呼ばれる)となる第5の絶縁層2061を形成する。第5の絶縁層は、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、またはベンゾシクロブテン)、またはSOG膜(例えば、アルキル基を含むSiOx膜)を膜厚0.8μm〜1μmの範囲で用いる。第5の絶縁層として、感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに形成されるため好ましい。

また、第5の絶縁層2061として、上記有機材料に、色素、黒色顔料等の可視光を吸収する材料を溶解又は分散、遮光性を有する絶縁物としてもよい。例えば、富士フィルムオーリン社製COLOR MOSAIC CK(商品名)のような材料を用いる。この場合、第5の絶縁層は、ブラックマトリックスとして機能するため、後に形成される発光素子からの迷光を吸収することができる。この結果、各画素のコントラストが向上する。さらには、第4の絶縁層2051も遮光性を有する絶縁物で設けることによって、第5の絶縁層2061とのトータルで遮光の効果を得ることができる。

次に、蒸着法、塗布法、液滴吐出法などにより、第4の導電層2055表面及び第5の絶縁層2061の端部上に発光物質を含む層2062を形成する。この後、発光物質を含む層2062上に、第2の画素電極として機能する第5の導電層2063を形成する。ここでは、酸化珪素を含むITOをスパッタリング法により成膜する。この結果、第4の導電層2055、発光物質を含む層2062、及び第5の導電層2063により発光素子を形成することができる。発光素子を構成する導電層及び、発光物質を含む層の各材料は適宜選択し、各膜厚も調整する。

なお、発光物質を含む層2062を形成する前に、大気圧中で200℃の熱処理を行い第5の絶縁層2061中若しくはその表面に吸着している水分を除去する。また、減圧下で200〜400℃、好ましくは250〜350℃に熱処理を行い、そのまま大気に晒さずに発光物質を含む層2062を真空蒸着法や、減圧下の液滴吐出法で形成することが好ましい。

発光物質を含む層2062は、有機化合物又は無機化合物を含む電荷注入輸送物質及び発光材料で形成し、その分子数から低分子系有機化合物、デンドリマー、オリゴマー等に代表される中分子系有機化合物、高分子系有機化合物から選ばれた一種又は複数種の層を含み、電子注入輸送性又は正孔注入輸送性の無機化合物と組み合わせても良い。

電荷注入輸送物質のうち、特に電子輸送性の高い物質としては、例えばトリス(8−キノリノラト)アルミニウム(略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Almq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:BeBq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニウム(略称:BAlq)など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等が挙げられる。

また、正孔輸送性の高い物質としては、例えば4,4’−ビス[N−(1−ナフチル)−N−フェニル−アミノ]−ビフェニル(略称:α−NPD)や4,4’−ビス[N−(3−メチルフェニル)−N−フェニル−アミノ]−ビフェニル(略称:TPD)や4,4’,4’’−トリス(N,N−ジフェニル−アミノ)−トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニル−アミノ]−トリフェニルアミン(略称:MTDATA)などの芳香族アミン系(即ち、ベンゼン環−窒素の結合を有する)の化合物が挙げられる。

また、電荷注入輸送物質のうち、特に電子注入性の高い物質としては、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaF2)等のようなアルカリ金属又はアルカリ土類金属の化合物が挙げられる。また、この他、Alq3のような電子輸送性の高い物質とマグネシウム(Mg)やアルカリ土類金属との混合物であってもよい。

電荷注入輸送物質のうち、正孔注入性の高い物質としては、例えば、モリブデン酸化物(MoOx)やバナジウム酸化物(VOx)、ルテニウム酸化物(RuOx)、タングステン酸化物(WOx)、マンガン酸化物(MnOx)等の金属酸化物が挙げられる。また、この他、フタロシアニン(略称:H2Pc)や銅フタロシアニン(CuPc)等のフタロシアニン系の化合物が挙げられる。

発光層は、発光波長帯の異なる発光層を画素毎に形成して、カラー表示を行う構成としても良い。典型的には、R(赤)、G(緑)、B(青)の各色に対応した発光層を形成する。この場合にも、画素の光放射側にその発光波長帯の光を透過するフィルター(着色層)を設けた構成とすることで、色純度の向上や、画素部の鏡面化(映り込み)の防止を図ることができる。画素の光放射側にフィルター(着色層)を設けることで、従来必要であるとされていた円偏光版などを省略することが可能となり、発光層から放射される光の損失を無くすことができる。さらに、斜方から画素部(表示画面)を見た場合に起こる色調の変化を低減することができる。

発光層を形成する発光材料には様々な材料がある。低分子系有機発光材料では、4−(ジシアノメチレン)2−メチル−6−[2−(1,1,7,7−テトラメチルジュロリジン−9−イル)エテニル]−4H−ピラン(略称:DCJT)、4−(ジシアノメチレン)−2−tert−ブチル−6−[2−(1,1,7,7−テトラメチルジュロリジン−9−イル)エテニル]−4H−ピラン(略称:DCJTB)、ペリフランテン、2,5−ジシアノ−1,4−ビス[2−(10−メトキシ−1,1,7,7−テトラメチルジュロリジン−9−イル)エテニル]ベンゼン、N,N’−ジメチルキナクリドン(略称:DMQd)、クマリン6、クマリン545T、トリス(8−キノリノラト)アルミニウム(略称:Alq3)、9,9’−ビアントリル、9,10−ジフェニルアントラセン(略称:DPA)や9,10−ジ(2−ナフチル)アントラセン(略称:DNA)等を用いることができる。また、この他の物質でもよい。

一方、高分子系有機発光材料は低分子系に比べて物理的強度が高く、素子の耐久性が高い。また塗布により成膜することが可能であるので、素子の作製が比較的容易である。高分子系有機発光材料を用いた発光素子の構造は、低分子系有機発光材料を用いたときと基本的には同じであり、陰極/発光物質を含む層/陽極となる。しかし、高分子系有機発光材料を用いた発光物質を含む層を形成する際には、低分子系有機発光材料を用いたときのような積層構造を形成させることは難しく、多くの場合2層構造となる。具体的には、陰極/発光層/正孔輸送層/陽極という構造である。

発光色は、発光層を形成する材料で決まるため、これらを選択することで所望の発光を示す発光素子を形成することができる。発光層の形成に用いることができる高分子系の発光材料は、ポリパラフェニレンビニレン系、ポリパラフェニレン系、ポリチオフェン系、ポリフルオレン系が挙げられる。

ポリパラフェニレンビニレン系発光材料には、ポリ(パラフェニレンビニレン) [PPV] の誘導体、ポリ(2,5−ジアルコキシ−1,4−フェニレンビニレン) [RO−PPV]、ポリ(2−(2’−エチル−ヘキソキシ)−5−メトキシ−1,4−フェニレンビニレン)[MEH−PPV]、ポリ(2−(ジアルコキシフェニル)−1,4−フェニレンビニレン)[ROPh−PPV]等が挙げられる。ポリパラフェニレン系発光材料には、ポリパラフェニレン[PPP]の誘導体、ポリ(2,5−ジアルコキシ−1,4−フェニレン)[RO−PPP]、ポリ(2,5−ジヘキソキシ−1,4−フェニレン)等が挙げられる。ポリチオフェン系発光材料には、ポリチオフェン[PT]の誘導体、ポリ(3−アルキルチオフェン)[PAT]、ポリ(3−ヘキシルチオフェン)[PHT]、ポリ(3−シクロヘキシルチオフェン)[PCHT]、ポリ(3−シクロヘキシル−4−メチルチオフェン)[PCHMT]、ポリ(3,4−ジシクロヘキシルチオフェン)[PDCHT]、ポリ[3−(4−オクチルフェニル)−チオフェン][POPT]、ポリ[3−(4−オクチルフェニル)−2,2ビチオフェン][PTOPT]等が挙げられる。ポリフルオレン系発光材料には、ポリフルオレン[PF]の誘導体、ポリ(9,9−ジアルキルフルオレン)[PDAF]、ポリ(9,9−ジオクチルフルオレン)[PDOF]等が挙げられる。

また、発光層は単色又は白色の発光を呈する構成とすることができる。白色発光材料を用いる場合には、画素の光放射側に特定の波長の光を透過するフィルター(着色層)を設けた構成としてカラー表示を可能にすることができる。

白色に発光する発光層を形成するには、例えば、Alq3、部分的に赤色発光色素であるナイルレッドをドープしたAlq3、p−EtTAZ、TPD(芳香族ジアミン)を蒸着法により順次積層することで白色を得ることができる。また、スピンコートを用いた塗布法により発光層を形成する場合には、塗布した後、真空加熱で焼成することが好ましい。例えば、正孔注入層として作用する層としてポリ(エチレンジオキシチオフェン)、ポリ(スチレンスルホン酸)水溶液(PEDOT、PSS)を全面に塗布、焼成し、その後、発光層として作用する層として発光中心色素(1,1,4,4−テトラフェニル−1,3−ブタジエン(TPB)、4−ジシアノメチレン−2−メチル−6−(p−ジメチルアミノ−スチリル)−4H−ピラン(DCM1)、ナイルレッド、クマリン6など)をドープしたポリビニルカルバゾール(PVK)溶液を全面に塗布、焼成すればよい。

発光層は単層で形成することもでき、ホール輸送性のポリビニルカルバゾール(PVK)に電子輸送性の1,3,4−オキサジアゾール誘導体(PBD)を分散させてもよい。また、30wt%のPBDを電子輸送剤として分散し、4種類の色素(TPB、クマリン6、DCM1、ナイルレッド)を適当量分散することで白色発光が得られる。ここで示した白色発光が得られる発光素子の他にも、発光層の材料を適宜選択することによって、赤色発光、緑色発光、または青色発光が得られる発光素子を作製することができる。

なお、正孔輸送性の高分子系有機発光材料を、陽極と発光性の高分子系有機発光材料の間に挟んで形成すると、陽極からの正孔注入性を向上させることができる。一般にアクセプター材料と共に水に溶解させたものをスピンコート法などで塗布する。また、有機溶媒には不溶であるため、上述した発光性の有機発光材料との積層が可能である。正孔輸送性の高分子系有機発光材料としては、PEDOTとアクセプター材料としてのショウノウスルホン酸(CSA)の混合物、ポリアニリン[PANI]とアクセプター材料としてのポリスチレンスルホン酸[PSS]の混合物等が挙げられる。

さらに、発光層は、一重項励起発光材料の他、金属錯体などを含む三重項励起材料を用いても良い。例えば、赤色の発光性の画素、緑色の発光性の画素及び青色の発光性の画素のうち、輝度半減時間が比較的短い赤色の発光性の画素を三重項励起発光材料で形成し、他の発光性の画素を一重項励起発光材料で形成する。三重項励起発光材料は発光効率が良いので、同じ輝度を得るのに消費電力が少なくて済むという特徴がある。すなわち、赤色画素に三重項励起材料を適用した場合、発光素子に流す電流量が少なくて済むので、信頼性を向上させることができる。低消費電力化として、赤色の発光性の画素と緑色の発光性の画素とを三重項励起発光材料で形成し、青色の発光性の画素を一重項励起発光材料で形成しても良い。人間の視感度が高い緑色の発光素子も三重項励起発光材料で形成することで、より低消費電力化を図ることができる。

三重項励起発光材料の一例としては、金属錯体をドーパントとして用いたものがあり、第3遷移系列元素である白金を中心金属とする金属錯体、イリジウムを中心金属とする金属錯体などが知られている。三重項励起発光材料としては、これらの化合物に限られることはなく、上記構造を有し、且つ中心金属に周期表の8〜10属に属する元素を有する化合物を用いることも可能である。

以上に掲げる発光物質を含む層を形成する物質は一例であり、正孔注入輸送層、正孔輸送層、電子注入輸送層、電子輸送層、発光層、電子ブロック層、正孔ブロック層などの機能性の各層を適宜積層することで発光素子を形成することができる。また、これらの各層を合わせた混合層又は混合接合を形成しても良い。発光層の層構造は変化しうるものであり、特定の電子注入領域や発光領域を備えていない代わりに、もっぱらこの目的用の電極を備えたり、発光性の材料を分散させて備えたりする変形は、本発明の趣旨を逸脱しない範囲において許容されうるものである。

上記のような材料で形成した発光素子は、順方向にバイアスすることで発光する。発光素子を用いて形成する表示装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。いずれにしても、個々の画素は、ある特定のタイミングで順方向バイアスを印加して発光させることとなるが、ある一定期間は非発光状態となっている。この非発光時間に逆方向のバイアスを印加することで発光素子の信頼性を向上させることができる。発光素子では、一定駆動条件下で発光強度が低下する劣化や、画素内で非発光領域が拡大して見かけ上輝度が低下する劣化モードがあるが、順方向及び逆方向にバイアスを印加する交流的な駆動を行うことで、劣化の進行を遅くすることができ、発光装置の信頼性を向上させることができる。

次に、発光素子を覆って、水分の侵入を防ぐ透明保護層2064を形成する。透明保護層2064としては、スパッタ法またはCVD法により得られる窒化珪素膜、酸化珪素膜、酸化窒化珪素膜(SiNO膜(組成比N>O)またはSiON膜(組成比N<O))、炭素を主成分とする薄膜(例えばDLC膜、CN膜)などを用いることができる。

以上の工程により、発光表示パネルを作製することができる。なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とソース配線層(ゲート配線層)の間または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部のゲート配線層とダイオードのドレイン配線層又はソース配線層とを接続することにより、静電破壊を防止することができる。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。また、表示パネルとして実施例2及び実施例3において、液晶表示パネル及び発光表示パネルを例に挙げて説明したが、これに限られるものではなく、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等のアクティブ型表示パネルに、本発明を適宜適用することができる。

上記実施例において適用可能な発光素子の形態を、図23を用いて説明する。

図23(A)は第1の画素電極11を透光性の酸化物導電性材料で形成した例であり、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成している。その上に正孔注入層若しくは正孔輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層した発光物質を含む層16を設けている。第2の画素電極17は、LiFやMgAgなどアルカリ金属又はアルカリ土類金属を含む第1の電極層33とアルミニウムなどの金属材料で形成する第2の電極層34で形成している。この構造の画素は、図中に矢印で示したように第1の画素電極11側から光を放射することが可能となる。

図23(B)は第2の画素電極17から光を放射する例を示し、第1の画素電極11はアルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する第1の電極層35と、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成する第2の電極層32で形成している。その上に正孔注入層若しくは正孔輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層した発光物質を含む層16を設けている。第2の画素電極17は、LiFやCaFなどのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成するが、いずれの層も100nm以下の厚さとして光を透過可能な状態としておくことで、第2の画素電極17から光を放射することが可能となる。

図23(E)は、両方向、即ち第1の電極及び第2の電極から光を放射する例を示し、第1の画素電極11に、透光性を有し且つ仕事関数の大きい導電膜を用い、第2の画素電極17に、透光性を有し且つ仕事関数の小さい導電膜を用いる。代表的には、第1の画素電極11を、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成し、第2の画素電極17を、それぞれ100nm以下の厚さのLiFやCaFなどのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成すればよい。

図23(C)は第1の画素電極11から光を放射する例を示し、かつ、発光物質を含む層16を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層41の順に積層した構成を示している。第2の画素電極17は、発光物質を含む層16側から酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成する第2の電極層32、アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する第1の電極層35で形成している。第1の画素電極11は、LiFやCaFなどのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成するが、いずれの層も100nm以下の厚さとして光を透過可能な状態としておくことで、第1の画素電極11から光を放射することが可能となる。

図23(D)は第2の画素電極17から光を放射する例を示し、かつ、第1の画素電極11上に発光物質を含む層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層41の順に積層した構成を示している。第1の画素電極11は図23(A)と同様な構成とし、膜厚は発光物質を含む層で発光した光を反射可能な程度に厚く形成している。第2の画素電極17は、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で構成している。この構造において、正孔注入層若しくは正孔輸送層41を無機物である金属酸化物(代表的には酸化モリブデン若しくは酸化バナジウム)で形成することにより、第2の画素電極17を形成する際に導入される酸素が供給されて正孔注入性が向上し、駆動電圧を低下させることができる。

図23(F)は、両方向、即ち第1の画素電極及び第2の画素電極から光を放射する例を示し、第1の画素電極11に、透光性を有し且つ仕事関数の小さい導電膜を用い、第2の画素電極17に、透光性を有し且つ仕事関数の大きい導電膜を用いる。代表的には、第1の画素電極11を、それぞれ100nm以下の厚さのLiFやCaFなどのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成し、第2の画素電極17を、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成すればよい。

上記実施例で示す発光表示パネルの画素回路、及びその動作構成について、図24を用いて説明する。発光表示パネルの動作構成は、ビデオ信号がデジタルの表示装置において、画素に入力されるビデオ信号が電圧で規定されるのものと、電流で規定されるものとがある。ビデオ信号が電圧によって規定されるものには、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加される電流が一定のもの(CVCC)とがある。また、ビデオ信号が電流によって規定されるものには、発光素子に印加される電圧が一定のもの(CCCV)と、発光素子に印加される電流が一定のもの(CCCC)とがある。本実施例では、CVCV動作をする画素を図24(A)及び(B)を用いて説明する。また、CVCC動作をする画素を図24(C)〜(F)を用いて説明する。

図24(A)及び(B)に示す画素は、列方向に信号線3710及び電源線3711、行方向に走査線3714が配置される。また、スイッチング用TFT3701、駆動用TFT3703、容量素子3702及び発光素子3705を有する。

なお、スイッチング用TFT3701及び駆動用TFT3703は、オンしているときは線形領域で動作する。また駆動用TFT3703は発光素子3705に電圧を印加するか否かを制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましく、本実施例ではpチャネル型TFTとして形成する。また駆動用TFT3703には、エンハンスメント型だけでなく、ディプリーション型のTFTを用いてもよい。また、駆動用TFT3703のチャネル幅Wとチャネル長Lとの比(W/L)は、TFTの移動度にもよるが1〜1000であることが好ましい。W/Lが大きいほど、TFTの電気特性が向上する。

図24(A)、(B)に示す画素において、スイッチング用TFT3701は、画素に対するビデオ信号の入力を制御するものであり、スイッチング用TFT3701がオンとなると、画素内にビデオ信号が入力される。すると、容量素子3702にそのビデオ信号の電圧が保持される。

図24(A)において、電源線3711がVssで発光素子3705の対向電極がVddの場合、即ち図23(C)、(D)、及び(F)の場合(逆積みの構造)、発光素子の対向電極は陽極であり、駆動用TFT3703に接続される電極は陰極である。この場合、駆動用TFT3703の特性バラツキによる輝度ムラを抑制することが可能である。

図24(A)において、電源線3711がVddで発光素子3705の対向電極がVssの場合、即ち図23(A)、(B)及び(E)の場合(順積み構造)、発光素子の対向電極は陰極であり、駆動用TFT3703に接続される電極は陽極である。この場合、Vddより電圧の高いビデオ信号を信号線3710に入力することにより、容量素子3702にそのビデオ信号の電圧が保持され、駆動用TFT3703が線形領域で動作するので、TFTのバラツキによる輝度ムラを改善することが可能である。

図24(B)に示す画素は、TFT3706と走査線3715を追加している以外は、図24(A)に示す画素構成と同じである。

TFT3706は、新たに配置された走査線3715によりオン又はオフが制御される。TFT3706がオンとなると、容量素子3702に保持された電荷は放電し、TFT3703がオフとなる。つまり、TFT3706の配置により、強制的に発光素子3705に電流が流れない状態を作ることができる。そのためTFT3706を消去用TFTと呼ぶことができる。従って、図24(B)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時又は直後に点灯期間を開始することができるため、発光のデューティ比を向上することが可能となる。

上記動作構成を有する画素において、発光素子3705の電流値は、線形領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性のバラツキを抑制することが可能であり、TFT特性のバラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

次に、CVCC動作をする画素を図24(C)〜(F)を用いて説明する。図24(C)に示す画素は、図24(A)に示す画素構成に、電源線3712、電流制御用TFT3704が設けられている。

図24(E)に示す画素は、駆動用TFT3703のゲート電極が、行方向に配置された電源線3712に接続される点が異なっており、それ以外は図24(C)に示す画素と同じ構成である。つまり、図24(C)、(E)に示す両画素は、同じ等価回路図を示す。しかしながら、列方向に電源線3712が配置される場合(図24(C))と、行方向に電源線3712が配置される場合(図24(E))とでは、各電源線は異なるレイヤーの導電膜で形成される。ここでは、駆動用TFT3703のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図24(C)、(E)として分けて記載する。

なお、スイッチング用TFT3701は線形領域で動作し、駆動用TFT3703は飽和領域で動作する。また駆動用TFT3703は発光素子3705に流れる電流値を制御する役目を有し、電流制御用TFT3704は飽和領域で動作し発光素子3705に対する電流の供給を制御する役目を有する。

図24(D)及び(F)に示す画素はそれぞれ、図24(C)及び(E)に示す画素に、消去用のTFT3706と走査線3715を追加している以外は、図24(C)及び(E)に示す画素構成と同じである。

なお、図24(A)及び(B)に示される画素でも、CVCC動作をすることは可能である。また、図24(C)〜(F)に示される動作構成を有する画素は、図24(A)及び(B)と同様に、発光素子の電流の流れる方向によって、Vdd及びVssを適宜変えることが可能である。

上記構成を有する画素は、電流制御用TFT3704が線形領域で動作するために、電流制御用TFT3704のVgsの僅かな変動は、発光素子3705の電流値に影響を及ぼさない。つまり、発光素子3705の電流値は、飽和領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

特に、非晶質半導体等を有する薄膜トランジスタを形成する場合、駆動用TFTの半導体膜の面積を大きくすると、TFTのバラツキの低減が可能であるため好ましい。このため、図24(A)及び図24(B)に示す画素は、TFTの数が少ないため開口率を増加させることが可能である。

なお、容量素子3702を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などで、まかなうことが可能な場合には、容量素子3702を設けなくてもよい。

また、薄膜トランジスタの半導体領域が非晶質半導体膜で形成される場合は、しきい値がシフトしやすいため、しきい値を補正する回路を画素内又は画素周辺に設けることが好ましい。

このようなアクティブマトリクス型の発光装置は、画素密度が増えた場合、各画素にTFTが設けられているため低電圧駆動でき、有利であると考えられている。一方、一列毎にTFTが設けられるパッシブマトリクス型の発光装置を形成することもできる。パッシブマトリクス型の発光装置は、各画素にTFTが設けられていないため、高開口率となる。

また、本発明の表示装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、表示装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

以上のように、多様な画素回路を採用することができる。

本実施例では、上記実施例に示した表示パネルへの駆動回路の実装について、図26を用いて説明する。

図26(A)に示すように、画素部1401の周辺に信号線駆動回路1402、及び走査線駆動回路1403a、1403bを実装する。図26(A)では、信号線駆動回路1402、及び走査線駆動回路1403a、1403b等として、公知の異方性導電接着剤、及び異方性導電フィルムを用いた実装方法、COG方式、ワイヤボンディング方法、並びに半田バンプを用いたリフロー処理等により、基板1400上にICチップ1405を実装する。ここでは、COG方式を用いる。そして、FPC(フレキシブルプリントサーキット)1406を介して、ICチップと外部回路とを接続する。

また、図26(B)に示すように、SASや結晶性半導体でTFTを形成する場合、画素部1401と走査線駆動回路1403a、1403b等を基板上に一体形成し、信号線駆動回路1402等を別途ICチップとして実装する場合がある。図26(B)において、信号線駆動回路1402として、COG方式により、基板1400上にICチップ1405を実装する。そして、FPC1406を介して、ICチップと外部回路とを接続する。

さらに、図26(C)に示すように、COG方式に代えて、TAB方式により信号線駆動回路1402等を実装する場合がある。そして、FPC1406を介して、ICチップと外部回路とを接続する。図26(C)において、信号線駆動回路をTAB方式により実装しているが、走査線駆動回路をTAB方式により実装してもよい。

ICチップをTAB方式により実装すると、基板に対して画素部を大きく設けることができ、狭額縁化を達成することができる。

ICチップは、シリコンウェハを用いて形成するが、ICチップの代わりにガラス基板上にICを形成したIC(以下、ドライバICと表記する)を設けてもよい。ICチップは、円形のシリコンウェハからICチップを取り出すため、母体基板形状に制約がある。一方ドライバICは、母体基板がガラスであり、形状に制約がないため、生産性を高めることができる。そのため、ドライバICの形状寸法は自由に設定することができる。例えば、ドライバICの長辺の長さを15〜80mmとして形成すると、ICチップを実装する場合と比較し、必要な数を減らすことができる。その結果、接続端子数を低減することができ、製造上の歩留まりを向上させることができる。

ドライバICは、基板上に形成された結晶質半導体を用いて形成することができ、結晶質半導体は連続発振型のレーザ光を照射することで形成するとよい。連続発振型のレーザ光を照射して得られる半導体膜は、結晶欠陥が少なく、大粒径の結晶粒を有する。その結果、このような半導体膜を有するトランジスタは、移動度や応答速度が良好となり、高速駆動が可能となり、ドライバICに好適である。

本実施例では、表示モジュールについて説明する。ここでは、表示モジュールの一例として、液晶モジュールを、図18を用いて示す。

アクティブマトリクス基板1601と対向基板1602とが、シール材1600により固着され、それらの間には画素部1603と液晶層1604とが設けられ表示領域を形成している。

着色層1605は、カラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。アクティブマトリクス基板1601と対向基板1602との外側には、偏光板1606、1607が配設されている。また、偏光板1606の表面には、保護膜1616が形成されており、外部からの衝撃を緩和している。

アクティブマトリクス基板1601に設けられた接続端子1608には、FPC1609を介して配線基板1610が接続されている。FPC又は接続配線には画素駆動回路(ICチップ、ドライバIC等)1611が設けられ、配線基板1610には、コントロール回路や電源回路などの外部回路1612が組み込まれている。

冷陰極管1613、反射板1614、及び光学フィルム1615はバックライトユニットであり、これらが光源となって液晶表示パネルへ光を投射する。液晶パネル、光源、配線基板、FPC等は、ベゼル1617で保持及び保護されている。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。

本実施例では、表示モジュールの一例として、発光表示モジュールの外観について、図25を用いて説明する。図25(A)は、第1の基板と、第2の基板との間を第1のシール材1205及び第2のシール材によって封止されたパネルの上面図であり、図25(B)は、図25(A)のA−A’における断面図に相当する。

図25(A)において、点線で示された1201は信号線(ソース線)駆動回路、1202は画素部、1203は走査線(ゲート線)駆動回路である。本実施例において、信号線駆動回路1201、画素部1202、及び走査線駆動回路1203は第1のシール材1205及び第2のシール材で封止されている領域内にある。第1のシール材1205としては、フィラーを含む粘性の高いエポキシ系樹脂を用いるのが好ましい。また、第2のシール材としては、粘性の低いエポキシ系樹脂を用いるのが好ましい。また、第1のシール材1205及び第2のシール材はできるだけ水分や酸素を透過しない材料であることが望ましい。

また、画素部1202と第1のシール材1205との間に、乾燥剤を設けてもよい。さらには、画素部において、走査線又は信号線上に乾燥剤を設けてもよい。乾燥剤としては、酸化カルシウム(CaO)や酸化バリウム(BaO)等のようなアルカリ土類金属の酸化物のような化学吸着によって水(H2O)を吸着する物質を用いるのが好ましい。但し、これに限らずゼオライトやシリカゲル等の物理吸着によって水を吸着する物質を用いても構わない。

また、透湿性の高い樹脂に乾燥剤の粒状の物質を含ませた状態で第2の基板1204に固定することができる。ここで、透湿性の高い樹脂としては、例えば、エステルアクリレート、エーテルアクリレート、エステルウレタンアクリレート、エーテルウレタンアクリレート、ブタジエンウレタンアクリレート、特殊ウレタンアクリレート、エポキシアクリレート、アミノ樹脂アクリレート、アクリル樹脂アクリレート等のアクリル樹脂を用いることができる。この他、ビスフェノールA型液状樹脂、ビスフェノールA型固形樹脂、含ブロムエポキシ樹脂、ビスフェノールF型樹脂、ビスフェノールAD型樹脂、フェノール型樹脂、クレゾール型樹脂、ノボラック型樹脂、環状脂肪族エポキシ樹脂、エピビス型エポキシ樹脂、グリシジルエステル樹脂、グリシジルアミン系樹脂、複素環式エポキシ樹脂、変性エポキシ樹脂等のエポキシ樹脂を用いることができる。また、この他の物質を用いても構わない。また、例えばシロキサンポリマー、ポリイミド、PSG(リンガラス)、BPSG(リンボロンガラス)、等の無機物等を用いてもよい。

乾燥剤を走査線と重畳する領域に設けることで、また、透湿性の高い樹脂に乾燥剤の粒状の物質を含ませた状態で第2の基板に固定することで、開口率を低下せずに表示素子への水分の侵入及びそれに起因する劣化を抑制することができる。

なお、1210は、信号線駆動回路1201及び走査線駆動回路1203に入力される信号を伝送するための接続配線であり、外部入力端子となるFPC(フレキシブルプリント配線)1209から、接続配線1208を介してビデオ信号やクロック信号を受け取る。

次に、断面構造について図25(B)を用いて説明する。第1の基板1200上には駆動回路及び画素部が形成されており、TFTを代表とする半導体素子を複数有している。駆動回路として信号線駆動回路1201と画素部1202とを示す。なお、信号線駆動回路1201はnチャネル型TFT1221とpチャネル型TFT1222とを組み合わせたCMOS回路が形成される。

本実施例においては、同一基板上に信号線駆動回路、走査線駆動回路、及び画素部のTFTが形成されている。このため、発光表示装置の容積を縮小することができる。

また、画素部1202はスイッチング用のTFT1211と、駆動用TFT1212とそのドレインに電気的に接続された反射性を有する導電膜からなる第1の画素電極(陽極)1213を含む複数の画素により形成される。

また、これらのTFT1211、1212、1221、1222の層間絶縁膜1220としては、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、有機材料(ポリイミド、ポリアミド、ポリイミドアミド、ベンゾシクロブテン、またはシロキサンポリマー)を主成分とする材料を用いて形成することができる。また、層間絶縁膜の原料としてシロキサンポリマーを用いると、シリコンと酸素を骨格構造に有し、側鎖に水素又は/及びアルキル基を有する構造の絶縁膜となる。

また、第1の画素電極(陽極)1213の両端には絶縁物(バンク、隔壁、障壁、土手などと呼ばれる)1214が形成される。絶縁物1214に形成する膜の被覆率(カバレッジ)を良好なものとするため、絶縁物1214の上端部または下端部に曲率を有する曲面が形成されるようにする。絶縁物1214の材料としては、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、有機材料(ポリイミド、ポリアミド、ポリイミドアミド、ベンゾシクロブテン、またはシロキサンポリマー)を主成分とする材料を用いて形成することができる。また、絶縁物1214を窒化アルミニウム膜、窒化酸化アルミニウム膜、炭素を主成分とする薄膜、または窒化珪素膜からなる保護膜(平坦化層)で覆ってもよい。また、絶縁物1214として、黒色顔料、色素などの可視光を吸収する材料を溶解又は分散させてなる有機材料を用いることで、後に形成される発光素子からの迷光を吸収することができる。この結果、各画素のコントラストが向上する。また、層間絶縁膜1220も遮光性を有する絶縁物で設けることによって、絶縁物1214とのトータルで遮光の効果を得ることができる。

また、第1の画素電極(陽極)1213上には、有機化合物材料の蒸着を行い、発光物質を含む層1215を選択的に形成する。

こうして、第1の画素電極(陽極)1213、発光物質を含む層1215、及び第2の画素電極(陰極)1216からなる発光素子1217が形成される。発光素子1217は、第2の基板1204側に発光する。

発光素子1217は、実施例5に示される構造を適宜用いることができる。

また、発光素子1217を封止するために保護積層1218を形成する。保護積層は、第1の無機絶縁膜と、応力緩和膜と、第2の無機絶縁膜との積層からなっている。次に、保護積層1218と第2の基板1204とを、第1のシール材1205及び第2のシール材1206で接着する。なお、第2のシール材を実施例3の図15に示す液晶を滴下する装置のように、シール材を滴下する装置を用いて滴下することが好ましい。シール材をディスペンサから滴下、又は吐出させてシール材をアクティブマトリクス基板上に塗布した後、真空中で、第2の基板とアクティブマトリクス基板とを貼り合わせ、紫外線硬化を行って封止することができる。

なお、第2の基板1204表面には、偏光板1225が固定され、偏光板1225表面には、1/2λ又は1/4λの位相差板1229及び反射防止膜1226が設けられている。また、第2の基板1204から順に、1/4λ板の位相差板及び1/2λ板の位相差板1229、偏光板1225を順次設けてもよい。位相差板または偏光板を設けることにより、外光が画素電極で反射することを防止することが可能である。なお、第1の画素電極1213及び第2の画素電極1216を透光性又は半透光性を有する導電膜で形成し、層間絶縁膜1223を可視光を吸収する材料、又は可視光を吸収する材料を溶解又は分散させてなる有機材料を用いて形成すると、各画素電極で外光が反射しないため、位相差板及び偏光板を用いなくとも良い。

接続配線1208とFPC1209とは、異方性導電膜又は異方性導電樹脂1227で電気的に接続されている。さらに、各配線層と接続端子との接続部を封止樹脂で封止することが好ましい。この構造により、断面部からの水分が発光素子に侵入し、劣化することを防ぐことができる。

なお、第2の基板1204と、保護積層1218との間には、不活性ガス、例えば窒素ガスを充填した空間を有してもよい。水分や酸素の侵入の防止を高めることができる。

画素部1202と偏光板1225の間に着色層を設けることができる。この場合、画素部に白色発光が可能な発光素子を設け、RGBを示す着色層を第2の基板1204に別途設けることでフルカラー表示することができる。また、画素部に青色発光が可能な発光素子を設け、色変換層などを別途設けることによってフルカラー表示することができる。さらには、各画素部、赤色、緑色、青色の発光を示す発光素子を形成し、且つ着色層を用いることもできる。このような表示モジュールは、各RBGの色純度が高く、高精細な表示が可能となる。

また、第1の基板1200又は第2の基板1204の一方、若しくは両方にフィルム又は樹脂等の基板を用いて発光表示モジュールを形成してもよい。このように対向基板を用いず封止すると、表示装置の軽量化、小型化、薄膜化を向上させることができる。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。また、表示モジュールとして液晶表示モジュール及び発光表示モジュールの例を示したが、これに限られるものではなく、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示モジュールに適宜適用することができる。

上記実施例に示される表示装置を筺体に組み込むことによって様々な電子機器を作製することができる。電子機器としては、テレビジョン装置、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。ここでは、これらの電子機器の代表例としてテレビジョン装置を及びそのブロック図をそれぞれ図27及び図28に、デジタルカメラを図29に示す。

図27は、アナログのテレビジョン放送を受信するテレビジョン装置の一般的な構成を示す図である。図27において、アンテナ1101で受信されたテレビ放送用の電波は、チューナ1102に入力される。チューナ1102は、アンテナ1101より入力された高周波テレビ信号を希望受信周波数に応じて制御された局部発振周波数の信号と混合することにより、中間周波数(IF)信号を生成して出力する。

チューナ1102により取り出されたIF信号は、中間周波数増幅器(IFアンプ)1103により必要な電圧まで増幅された後、映像検波回路1104によって映像検波されると共に、音声検波回路1105によって音声検波される。映像検波回路1104により出力された映像信号は、映像系処理回路1106により、輝度信号と色信号とに分離され、さらに所定の映像信号処理が施されて映像信号となり、本発明の表示装置、代表的には液晶表示装置、発光表示装置、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の映像系出力部1108に出力される。なお、表示装置に液晶表示装置を用いたものは、液晶テレビジョンとなり、発光表示装置を用いたものはEL(Electro Luminescence)テレビジョンとなる。また、他の表示装置を用いた場合も同様である。

また、音声検波回路1105により出力された信号は、音声系処理回路1107により、FM復調などの処理が施されて音声信号となり、適宜増幅されてスピーカ等の音声系出力部1109に出力される。

なお、本発明を用いたテレビジョン装置は、VHF帯やUHF帯などの地上波放送、ケーブル放送、又はBS放送などのアナログ放送に対応するものに限らず、地上波デジタル放送、ケーブルデジタル放送、又はBSデジタル放送に対応するものであっても良い。

図28はテレビジョン装置を前面方向から見た斜視図であり、筐体1151、表示部1152、スピーカ部1153、操作部1154、ビデオ入力端子1155等を含む。また、図27に示すような構成となっている。

表示部1152は、図27の映像系出力部1108の一例であり、ここで映像を表示する。

スピーカ部1153は、図27の音声系出力部の一例であり、ここで音声を出力する。

操作部1154は、電源スイッチ、ボリュームスイッチ、選局スイッチ、チューナースイッチ、選択スイッチ等が設けられており、該ボタンの押下によりテレビジョン装置の電源のON/OFF、映像の選択、音声の調整、及びチューナの選択等を行う。なお、図示していないが、リモートコントローラ型操作部によって、上記の選択を行うことも可能である。

ビデオ入力端子1155は、VTR、DVD、ゲーム機等の外部からの映像信号をテレビジョン装置に入力する端子である。

本実施例で示されるテレビジョン装置を壁掛け用テレビジョン装置の場合、本体背面に壁掛け用の部位が設けられている。

テレビジョン装置の表示部に本発明の半導体装置の一例である表示装置を用いることにより、低コストで、スループットや歩留まり高くテレビジョン装置を作製することができる。また、テレビジョン装置の映像検波回路、映像処理回路、音声検波回路、音声処理回路を制御するCPUに本発明の半導体装置を用いることにより、低コストで、スループットや歩留まり高くテレビジョン装置を作製することができる。このため、壁掛けテレビジョン装置、鉄道の駅や空港などにおける情報表示板や、街頭における広告表示板など特に大面積の表示媒体として様々な用途に適用することができる。

図29(A)及び図29(B)は、デジタルカメラの一例を示す図である。図29(A)は、デジタルカメラの前面方向から見た斜視図、図29(B)は、後面方向から見た斜視図である。図29(A)において、デジタルカメラには、リリースボタン1301、メインスイッチ1302、ファインダー窓1303、フラッシュ1304、レンズ1305、鏡胴1306、筺体1307が備えられている。

また、図29(B)において、ファインダー接眼窓1311、モニター1312、操作ボタン1313が備えられている。

リリースボタン1301は、半分の位置まで押下されると、焦点調整機構および露出調整機構が作動し、最下部まで押下されるとシャッターが開く。

メインスイッチ1302は、押下又は回転によりデジタルカメラの電源のON/OFFを切り替える。

ファインダー窓1303は、デジタルカメラの前面のレンズ1305の上部に配置されており、図29(B)に示すファインダー接眼窓1311から撮影する範囲やピントの位置を確認するための装置である。

フラッシュ1304は、デジタルカメラの前面上部に配置され、被写体輝度が低いときに、リリースボタンが押下されてシャッターが開くと同時に補助光を照射する。

レンズ1305は、デジタルカメラの正面に配置されている。レンズは、フォーカシングレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光学系を構成する。また、レンズの後方には、CCD(Charge Coupled Device)等の撮像素子が設けられている。

鏡胴1306は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレンズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ1305を手前に移動させる。また、携帯時は、レンズ1305を沈胴させてコンパクトにする。なお、本実施例においては、鏡胴を繰り出すことにより被写体をズーム撮影することができる構造としているが、この構造に限定されるものではなく、筺体1307内での撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでもよい。

ファインダー接眼窓1311は、デジタルカメラの後面上部に設けられており、撮影する範囲やピントの位置を確認する際に接眼するために設けられた窓である。

操作ボタン1313は、デジタルカメラの後面に設けられた各種機能ボタンであり、セットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等により構成されている。

本発明の半導体装置の一実施例である表示装置をモニターに用いることにより、低コストで、スループットや歩留まり高くデジタルカメラを作製することが可能である。また、各種機能ボタン、メインスイッチ、リリースボタン等の操作入力を受けて関連した処理を行うCPU、自動焦点動作及び自動焦点調整動作を行う回路、ストロボ発光の駆動制御回路、CCDの駆動を制御するタイミング制御回路、CCD等の撮像素子によって光電変換された信号から画像信号を生成する撮像回路、撮像回路で生成された画像信号をデジタル信号に変換するA/D変換回路、メモリへの画像データの書き込み及び画像データの読み出しを行うメモリインターフェース等の各回路を制御するCPU等に本発明の半導体装置を用いることにより、低コストで、スループットや歩留まり高くデジタルカメラを作製することが可能である。

本発明に係る配線の作製工程を説明する斜視図。

本発明に係る配線の作製工程を説明する上面図。

本発明に係る配線を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に適用可能な液滴吐出装置を説明する図。

本発明に適用可能なレーザビーム直接描画装置を説明する図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する上面図。

本発明に適用することのできる液晶滴下方法を説明する図。

本発明に係る液晶表示モジュールの構成を説明する図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する上面図。

本発明に適用可能な発光素子の形態を説明する図。

本発明に適用可能な発光素子の等価回路を説明する図。

本発明に係る発光表示パネルの構成を説明する図。

本発明に係る表示装置の駆動回路の実装方法を説明する上面図。

電子機器の一例を説明するブロック図。

電子機器の一例を説明する図。

電子機器の一例を説明する図。

塗れ性の低い領域及び塗れ性の高い領域の接触角を説明する図。

本発明に係る配線を説明する断面図。

本発明に係る配線の抵抗値を説明する図。