JP4754848B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4754848B2 JP4754848B2 JP2005057344A JP2005057344A JP4754848B2 JP 4754848 B2 JP4754848 B2 JP 4754848B2 JP 2005057344 A JP2005057344 A JP 2005057344A JP 2005057344 A JP2005057344 A JP 2005057344A JP 4754848 B2 JP4754848 B2 JP 4754848B2

- Authority

- JP

- Japan

- Prior art keywords

- light

- layer

- pattern

- film

- absorption layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 205

- 238000000034 method Methods 0.000 title claims description 192

- 238000004519 manufacturing process Methods 0.000 title claims description 71

- 239000000758 substrate Substances 0.000 claims description 167

- 239000000463 material Substances 0.000 claims description 136

- 230000031700 light absorption Effects 0.000 claims description 134

- 229920005989 resin Polymers 0.000 claims description 49

- 239000011347 resin Substances 0.000 claims description 49

- 239000004020 conductor Substances 0.000 claims description 42

- 230000003287 optical effect Effects 0.000 claims description 31

- 238000007599 discharging Methods 0.000 claims description 25

- 238000005530 etching Methods 0.000 claims description 23

- 238000010438 heat treatment Methods 0.000 claims description 23

- 229920001187 thermosetting polymer Polymers 0.000 claims description 22

- 239000012815 thermoplastic material Substances 0.000 claims description 18

- 230000001678 irradiating effect Effects 0.000 claims description 11

- 238000010521 absorption reaction Methods 0.000 claims description 6

- 239000010410 layer Substances 0.000 description 415

- 239000010408 film Substances 0.000 description 307

- 239000000243 solution Substances 0.000 description 154

- 239000007788 liquid Substances 0.000 description 41

- 239000004973 liquid crystal related substance Substances 0.000 description 35

- -1 and the like Inorganic materials 0.000 description 34

- 239000000126 substance Substances 0.000 description 31

- 239000011159 matrix material Substances 0.000 description 30

- 230000008569 process Effects 0.000 description 30

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 29

- 230000002940 repellent Effects 0.000 description 29

- 239000005871 repellent Substances 0.000 description 29

- 230000001681 protective effect Effects 0.000 description 28

- 230000006870 function Effects 0.000 description 25

- 229910052710 silicon Inorganic materials 0.000 description 25

- 229910052814 silicon oxide Inorganic materials 0.000 description 25

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 24

- 239000007789 gas Substances 0.000 description 24

- 239000010703 silicon Substances 0.000 description 24

- 239000002904 solvent Substances 0.000 description 24

- 239000011521 glass Substances 0.000 description 22

- 230000002829 reductive effect Effects 0.000 description 22

- 239000002245 particle Substances 0.000 description 21

- 229920001721 polyimide Polymers 0.000 description 20

- 239000004642 Polyimide Substances 0.000 description 19

- 229910052760 oxygen Inorganic materials 0.000 description 19

- 229910052782 aluminium Inorganic materials 0.000 description 18

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 18

- 239000001301 oxygen Substances 0.000 description 18

- 229910052709 silver Inorganic materials 0.000 description 18

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 16

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 16

- 239000010949 copper Substances 0.000 description 16

- 239000011229 interlayer Substances 0.000 description 16

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 16

- 239000004332 silver Substances 0.000 description 16

- 229910052581 Si3N4 Inorganic materials 0.000 description 15

- 239000010931 gold Substances 0.000 description 15

- 238000002347 injection Methods 0.000 description 15

- 239000007924 injection Substances 0.000 description 15

- 238000012545 processing Methods 0.000 description 15

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 15

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 14

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 12

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 229910052802 copper Inorganic materials 0.000 description 12

- 239000002274 desiccant Substances 0.000 description 12

- 230000007246 mechanism Effects 0.000 description 12

- 238000000576 coating method Methods 0.000 description 11

- 239000013078 crystal Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 11

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 11

- 239000010936 titanium Substances 0.000 description 11

- 229910052721 tungsten Inorganic materials 0.000 description 11

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 11

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 10

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 10

- 239000003822 epoxy resin Substances 0.000 description 10

- 229910052737 gold Inorganic materials 0.000 description 10

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 10

- 239000004417 polycarbonate Substances 0.000 description 10

- 229920000647 polyepoxide Polymers 0.000 description 10

- 239000000565 sealant Substances 0.000 description 10

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical compound C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 9

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 9

- 239000010419 fine particle Substances 0.000 description 9

- 239000012212 insulator Substances 0.000 description 9

- 238000004544 sputter deposition Methods 0.000 description 9

- 229910052719 titanium Inorganic materials 0.000 description 9

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 9

- 239000010937 tungsten Substances 0.000 description 9

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 8

- 239000000853 adhesive Substances 0.000 description 8

- 230000001070 adhesive effect Effects 0.000 description 8

- 238000004380 ashing Methods 0.000 description 8

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 8

- 229910052697 platinum Inorganic materials 0.000 description 8

- 229920000642 polymer Polymers 0.000 description 8

- 238000004528 spin coating Methods 0.000 description 8

- 239000010409 thin film Substances 0.000 description 8

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 7

- 239000004952 Polyamide Substances 0.000 description 7

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 7

- 150000001342 alkaline earth metals Chemical class 0.000 description 7

- 239000011651 chromium Substances 0.000 description 7

- 229910052731 fluorine Inorganic materials 0.000 description 7

- 239000011737 fluorine Substances 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 239000007769 metal material Substances 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- 229910052763 palladium Inorganic materials 0.000 description 7

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 7

- 229920002647 polyamide Polymers 0.000 description 7

- YMWUJEATGCHHMB-UHFFFAOYSA-N Dichloromethane Chemical compound ClCCl YMWUJEATGCHHMB-UHFFFAOYSA-N 0.000 description 6

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- 239000006087 Silane Coupling Agent Substances 0.000 description 6

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 6

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 6

- 229910052783 alkali metal Inorganic materials 0.000 description 6

- 150000001340 alkali metals Chemical class 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 6

- 239000011248 coating agent Substances 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 238000001514 detection method Methods 0.000 description 6

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 6

- 238000009826 distribution Methods 0.000 description 6

- 235000019441 ethanol Nutrition 0.000 description 6

- 229910052739 hydrogen Inorganic materials 0.000 description 6

- 239000001257 hydrogen Substances 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 229920000123 polythiophene Polymers 0.000 description 6

- 239000010948 rhodium Substances 0.000 description 6

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- 229920000265 Polyparaphenylene Polymers 0.000 description 5

- 239000004372 Polyvinyl alcohol Substances 0.000 description 5

- 239000012298 atmosphere Substances 0.000 description 5

- IISBACLAFKSPIT-UHFFFAOYSA-N bisphenol A Chemical compound C=1C=C(O)C=CC=1C(C)(C)C1=CC=C(O)C=C1 IISBACLAFKSPIT-UHFFFAOYSA-N 0.000 description 5

- 239000000872 buffer Substances 0.000 description 5

- 229910052733 gallium Inorganic materials 0.000 description 5

- 229910052741 iridium Inorganic materials 0.000 description 5

- 239000013081 microcrystal Substances 0.000 description 5

- 239000002105 nanoparticle Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 239000002861 polymer material Substances 0.000 description 5

- 229920002451 polyvinyl alcohol Polymers 0.000 description 5

- 229910021332 silicide Inorganic materials 0.000 description 5

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 5

- 229910052715 tantalum Inorganic materials 0.000 description 5

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 4

- 239000004925 Acrylic resin Substances 0.000 description 4

- HEDRZPFGACZZDS-UHFFFAOYSA-N Chloroform Chemical compound ClC(Cl)Cl HEDRZPFGACZZDS-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 229910052788 barium Inorganic materials 0.000 description 4

- 239000005380 borophosphosilicate glass Substances 0.000 description 4

- 229910052793 cadmium Inorganic materials 0.000 description 4

- XJHCXCQVJFPJIK-UHFFFAOYSA-M caesium fluoride Chemical compound [F-].[Cs+] XJHCXCQVJFPJIK-UHFFFAOYSA-M 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 238000001723 curing Methods 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000001035 drying Methods 0.000 description 4

- 239000000975 dye Substances 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 4

- 229910052734 helium Inorganic materials 0.000 description 4

- 230000005525 hole transport Effects 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 239000005011 phenolic resin Substances 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 4

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 4

- 229920002098 polyfluorene Polymers 0.000 description 4

- 229920001709 polysilazane Polymers 0.000 description 4

- 229960002796 polystyrene sulfonate Drugs 0.000 description 4

- 239000011970 polystyrene sulfonate Substances 0.000 description 4

- 238000007639 printing Methods 0.000 description 4

- 229910052703 rhodium Inorganic materials 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- YLYPIBBGWLKELC-UHFFFAOYSA-N 4-(dicyanomethylene)-2-methyl-6-(4-(dimethylamino)styryl)-4H-pyran Chemical compound C1=CC(N(C)C)=CC=C1C=CC1=CC(=C(C#N)C#N)C=C(C)O1 YLYPIBBGWLKELC-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 3

- 229920000178 Acrylic resin Polymers 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 239000004641 Diallyl-phthalate Substances 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 229920000877 Melamine resin Polymers 0.000 description 3

- 239000004640 Melamine resin Substances 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- IMNFDUFMRHMDMM-UHFFFAOYSA-N N-Heptane Chemical compound CCCCCCC IMNFDUFMRHMDMM-UHFFFAOYSA-N 0.000 description 3

- 239000004677 Nylon Substances 0.000 description 3

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 3

- WYURNTSHIVDZCO-UHFFFAOYSA-N Tetrahydrofuran Chemical compound C1CCOC1 WYURNTSHIVDZCO-UHFFFAOYSA-N 0.000 description 3

- 230000002776 aggregation Effects 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 3

- QUDWYFHPNIMBFC-UHFFFAOYSA-N bis(prop-2-enyl) benzene-1,2-dicarboxylate Chemical compound C=CCOC(=O)C1=CC=CC=C1C(=O)OCC=C QUDWYFHPNIMBFC-UHFFFAOYSA-N 0.000 description 3

- UHESRSKEBRADOO-UHFFFAOYSA-N ethyl carbamate;prop-2-enoic acid Chemical compound OC(=O)C=C.CCOC(N)=O UHESRSKEBRADOO-UHFFFAOYSA-N 0.000 description 3

- 229920000840 ethylene tetrafluoroethylene copolymer Polymers 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 238000010304 firing Methods 0.000 description 3

- 239000007849 furan resin Substances 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 3

- 239000003550 marker Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- 229920003986 novolac Polymers 0.000 description 3

- 229920001778 nylon Polymers 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 239000003960 organic solvent Substances 0.000 description 3

- 238000009832 plasma treatment Methods 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920001197 polyacetylene Polymers 0.000 description 3

- 229920000767 polyaniline Polymers 0.000 description 3

- 229920000515 polycarbonate Polymers 0.000 description 3

- 229920000728 polyester Polymers 0.000 description 3

- 239000002243 precursor Substances 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 150000004756 silanes Chemical class 0.000 description 3

- 238000001179 sorption measurement Methods 0.000 description 3

- TVIVIEFSHFOWTE-UHFFFAOYSA-K tri(quinolin-8-yloxy)alumane Chemical compound [Al+3].C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1 TVIVIEFSHFOWTE-UHFFFAOYSA-K 0.000 description 3

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 3

- MIOPJNTWMNEORI-GMSGAONNSA-N (S)-camphorsulfonic acid Chemical compound C1C[C@@]2(CS(O)(=O)=O)C(=O)C[C@@H]1C2(C)C MIOPJNTWMNEORI-GMSGAONNSA-N 0.000 description 2

- 150000005072 1,3,4-oxadiazoles Chemical class 0.000 description 2

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 2

- YBYIRNPNPLQARY-UHFFFAOYSA-N 1H-indene Chemical compound C1=CC=C2CC=CC2=C1 YBYIRNPNPLQARY-UHFFFAOYSA-N 0.000 description 2

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- KAKZBPTYRLMSJV-UHFFFAOYSA-N Butadiene Chemical compound C=CC=C KAKZBPTYRLMSJV-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 229910052684 Cerium Inorganic materials 0.000 description 2

- IAZDPXIOMUYVGZ-UHFFFAOYSA-N Dimethylsulphoxide Chemical compound CS(C)=O IAZDPXIOMUYVGZ-UHFFFAOYSA-N 0.000 description 2

- 229920001780 ECTFE Polymers 0.000 description 2

- 229910052691 Erbium Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 229910052689 Holmium Inorganic materials 0.000 description 2

- UFWIBTONFRDIAS-UHFFFAOYSA-N Naphthalene Chemical compound C1=CC=CC2=CC=CC=C21 UFWIBTONFRDIAS-UHFFFAOYSA-N 0.000 description 2

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 2

- 239000002033 PVDF binder Substances 0.000 description 2

- OFBQJSOFQDEBGM-UHFFFAOYSA-N Pentane Chemical compound CCCCC OFBQJSOFQDEBGM-UHFFFAOYSA-N 0.000 description 2

- 239000004813 Perfluoroalkoxy alkane Substances 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 229920000282 Poly(3-cyclohexylthiophene) Polymers 0.000 description 2

- 229920000291 Poly(9,9-dioctylfluorene) Polymers 0.000 description 2

- 239000004693 Polybenzimidazole Substances 0.000 description 2

- 239000004698 Polyethylene Substances 0.000 description 2

- 239000004743 Polypropylene Substances 0.000 description 2

- 239000004793 Polystyrene Substances 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- 229910003902 SiCl 4 Inorganic materials 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910002808 Si–O–Si Inorganic materials 0.000 description 2

- 239000004809 Teflon Substances 0.000 description 2

- 229920006362 Teflon® Polymers 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 239000007983 Tris buffer Substances 0.000 description 2

- XTXRWKRVRITETP-UHFFFAOYSA-N Vinyl acetate Chemical compound CC(=O)OC=C XTXRWKRVRITETP-UHFFFAOYSA-N 0.000 description 2

- BZHJMEDXRYGGRV-UHFFFAOYSA-N Vinyl chloride Chemical compound ClC=C BZHJMEDXRYGGRV-UHFFFAOYSA-N 0.000 description 2

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 2

- 230000004931 aggregating effect Effects 0.000 description 2

- 238000004220 aggregation Methods 0.000 description 2

- RDOXTESZEPMUJZ-UHFFFAOYSA-N anisole Chemical compound COC1=CC=CC=C1 RDOXTESZEPMUJZ-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- WZJYKHNJTSNBHV-UHFFFAOYSA-N benzo[h]quinoline Chemical compound C1=CN=C2C3=CC=CC=C3C=CC2=C1 WZJYKHNJTSNBHV-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- PXKLMJQFEQBVLD-UHFFFAOYSA-N bisphenol F Chemical compound C1=CC(O)=CC=C1CC1=CC=C(O)C=C1 PXKLMJQFEQBVLD-UHFFFAOYSA-N 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 150000001722 carbon compounds Chemical class 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- MVPPADPHJFYWMZ-UHFFFAOYSA-N chlorobenzene Chemical compound ClC1=CC=CC=C1 MVPPADPHJFYWMZ-UHFFFAOYSA-N 0.000 description 2

- 229920006026 co-polymeric resin Polymers 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 150000004696 coordination complex Chemical class 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- VBVAVBCYMYWNOU-UHFFFAOYSA-N coumarin 6 Chemical compound C1=CC=C2SC(C3=CC4=CC=C(C=C4OC3=O)N(CC)CC)=NC2=C1 VBVAVBCYMYWNOU-UHFFFAOYSA-N 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- DIOQZVSQGTUSAI-UHFFFAOYSA-N decane Chemical compound CCCCCCCCCC DIOQZVSQGTUSAI-UHFFFAOYSA-N 0.000 description 2

- 238000000354 decomposition reaction Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 230000002542 deteriorative effect Effects 0.000 description 2

- SQNZJJAZBFDUTD-UHFFFAOYSA-N durene Chemical compound CC1=CC(C)=C(C)C=C1C SQNZJJAZBFDUTD-UHFFFAOYSA-N 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 125000005678 ethenylene group Chemical group [H]C([*:1])=C([H])[*:2] 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002366 halogen compounds Chemical class 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 125000000623 heterocyclic group Chemical group 0.000 description 2

- AMWRITDGCCNYAT-UHFFFAOYSA-L hydroxy(oxo)manganese;manganese Chemical compound [Mn].O[Mn]=O.O[Mn]=O AMWRITDGCCNYAT-UHFFFAOYSA-L 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 229910052809 inorganic oxide Inorganic materials 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 229910001507 metal halide Inorganic materials 0.000 description 2

- 150000005309 metal halides Chemical class 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000000113 methacrylic resin Substances 0.000 description 2

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 2

- VLKZOEOYAKHREP-UHFFFAOYSA-N n-Hexane Chemical compound CCCCCC VLKZOEOYAKHREP-UHFFFAOYSA-N 0.000 description 2

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical group C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- VOFUROIFQGPCGE-UHFFFAOYSA-N nile red Chemical compound C1=CC=C2C3=NC4=CC=C(N(CC)CC)C=C4OC3=CC(=O)C2=C1 VOFUROIFQGPCGE-UHFFFAOYSA-N 0.000 description 2

- 229910017464 nitrogen compound Inorganic materials 0.000 description 2

- 150000002830 nitrogen compounds Chemical class 0.000 description 2

- TVMXDCGIABBOFY-UHFFFAOYSA-N octane Chemical compound CCCCCCCC TVMXDCGIABBOFY-UHFFFAOYSA-N 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 229910052762 osmium Inorganic materials 0.000 description 2

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 229920011301 perfluoro alkoxyl alkane Polymers 0.000 description 2

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 2

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical class N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229920000301 poly(3-hexylthiophene-2,5-diyl) polymer Polymers 0.000 description 2

- 229920002493 poly(chlorotrifluoroethylene) Polymers 0.000 description 2

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 2

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 2

- 229920002480 polybenzimidazole Polymers 0.000 description 2

- 239000005023 polychlorotrifluoroethylene (PCTFE) polymer Substances 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920013716 polyethylene resin Polymers 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920001155 polypropylene Polymers 0.000 description 2

- 229920002223 polystyrene Polymers 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000007261 regionalization Effects 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 239000010944 silver (metal) Substances 0.000 description 2

- PRAKJMSDJKAYCZ-UHFFFAOYSA-N squalane Chemical compound CC(C)CCCC(C)CCCC(C)CCCCC(C)CCCC(C)CCCC(C)C PRAKJMSDJKAYCZ-UHFFFAOYSA-N 0.000 description 2

- 239000007858 starting material Substances 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- BFKJFAAPBSQJPD-UHFFFAOYSA-N tetrafluoroethene Chemical group FC(F)=C(F)F BFKJFAAPBSQJPD-UHFFFAOYSA-N 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 229910001935 vanadium oxide Inorganic materials 0.000 description 2

- 239000008096 xylene Substances 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- DTZWGKCFKSJGPK-VOTSOKGWSA-N (e)-2-(2-methyl-6-(2-(1,1,7,7-tetramethyl-1,2,3,5,6,7-hexahydropyrido[3,2,1-ij]quinolin-9-yl)vinyl)-4h-pyran-4-ylidene)malononitrile Chemical compound O1C(C)=CC(=C(C#N)C#N)C=C1\C=C\C1=CC(C(CCN2CCC3(C)C)(C)C)=C2C3=C1 DTZWGKCFKSJGPK-VOTSOKGWSA-N 0.000 description 1

- BQCIDUSAKPWEOX-UHFFFAOYSA-N 1,1-Difluoroethene Chemical compound FC(F)=C BQCIDUSAKPWEOX-UHFFFAOYSA-N 0.000 description 1

- YMRMDGSNYHCUCL-UHFFFAOYSA-N 1,2-dichloro-1,1,2-trifluoroethane Chemical compound FC(Cl)C(F)(F)Cl YMRMDGSNYHCUCL-UHFFFAOYSA-N 0.000 description 1

- QZJJMHGIQXXGSA-UHFFFAOYSA-N 1,2-dichloro-1,1,2-trifluoroethane;ethene Chemical group C=C.FC(Cl)C(F)(F)Cl QZJJMHGIQXXGSA-UHFFFAOYSA-N 0.000 description 1

- KLCLIOISYBHYDZ-UHFFFAOYSA-N 1,4,4-triphenylbuta-1,3-dienylbenzene Chemical compound C=1C=CC=CC=1C(C=1C=CC=CC=1)=CC=C(C=1C=CC=CC=1)C1=CC=CC=C1 KLCLIOISYBHYDZ-UHFFFAOYSA-N 0.000 description 1

- RYHBNJHYFVUHQT-UHFFFAOYSA-N 1,4-Dioxane Chemical compound C1COCCO1 RYHBNJHYFVUHQT-UHFFFAOYSA-N 0.000 description 1

- OCJBOOLMMGQPQU-UHFFFAOYSA-N 1,4-dichlorobenzene Chemical compound ClC1=CC=C(Cl)C=C1 OCJBOOLMMGQPQU-UHFFFAOYSA-N 0.000 description 1

- KMQPLEYEXDZOJF-UHFFFAOYSA-N 1-naphthalen-2-ylanthracene Chemical compound C1=CC=C2C=C3C(C4=CC5=CC=CC=C5C=C4)=CC=CC3=CC2=C1 KMQPLEYEXDZOJF-UHFFFAOYSA-N 0.000 description 1

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 1

- POAOYUHQDCAZBD-UHFFFAOYSA-N 2-butoxyethanol Chemical compound CCCCOCCO POAOYUHQDCAZBD-UHFFFAOYSA-N 0.000 description 1

- POXIZPBFFUKMEQ-UHFFFAOYSA-N 2-cyanoethenylideneazanide Chemical group [N-]=C=[C+]C#N POXIZPBFFUKMEQ-UHFFFAOYSA-N 0.000 description 1

- QTWJRLJHJPIABL-UHFFFAOYSA-N 2-methylphenol;3-methylphenol;4-methylphenol Chemical compound CC1=CC=C(O)C=C1.CC1=CC=CC(O)=C1.CC1=CC=CC=C1O QTWJRLJHJPIABL-UHFFFAOYSA-N 0.000 description 1

- HONWGFNQCPRRFM-UHFFFAOYSA-N 2-n-(3-methylphenyl)-1-n,1-n,2-n-triphenylbenzene-1,2-diamine Chemical compound CC1=CC=CC(N(C=2C=CC=CC=2)C=2C(=CC=CC=2)N(C=2C=CC=CC=2)C=2C=CC=CC=2)=C1 HONWGFNQCPRRFM-UHFFFAOYSA-N 0.000 description 1

- LNILPZLJSRHNPD-UHFFFAOYSA-N 3,4-dicyclohexylthiophene Chemical compound C1CCCCC1C1=CSC=C1C1CCCCC1 LNILPZLJSRHNPD-UHFFFAOYSA-N 0.000 description 1

- YEWTUGLUENRXFN-UHFFFAOYSA-N 3-(4-octylphenyl)-2-thiophen-2-ylthiophene Chemical compound C1=CC(CCCCCCCC)=CC=C1C1=C(C=2SC=CC=2)SC=C1 YEWTUGLUENRXFN-UHFFFAOYSA-N 0.000 description 1

- CHMILGIDWWDNMF-UHFFFAOYSA-N 3-(4-octylphenyl)thiophene Chemical compound C1=CC(CCCCCCCC)=CC=C1C1=CSC=C1 CHMILGIDWWDNMF-UHFFFAOYSA-N 0.000 description 1

- UBNBPEQRHOIIMO-UHFFFAOYSA-N 3-cyclohexyl-4-methylthiophene Chemical compound CC1=CSC=C1C1CCCCC1 UBNBPEQRHOIIMO-UHFFFAOYSA-N 0.000 description 1

- OGGKVJMNFFSDEV-UHFFFAOYSA-N 3-methyl-n-[4-[4-(n-(3-methylphenyl)anilino)phenyl]phenyl]-n-phenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 OGGKVJMNFFSDEV-UHFFFAOYSA-N 0.000 description 1

- SCZWJXTUYYSKGF-UHFFFAOYSA-N 5,12-dimethylquinolino[2,3-b]acridine-7,14-dione Chemical compound CN1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3N(C)C1=C2 SCZWJXTUYYSKGF-UHFFFAOYSA-N 0.000 description 1

- FCNCGHJSNVOIKE-UHFFFAOYSA-N 9,10-diphenylanthracene Chemical compound C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 FCNCGHJSNVOIKE-UHFFFAOYSA-N 0.000 description 1

- SXGIRTCIFPJUEQ-UHFFFAOYSA-N 9-anthracen-9-ylanthracene Chemical group C1=CC=CC2=CC3=CC=CC=C3C(C=3C4=CC=CC=C4C=C4C=CC=CC4=3)=C21 SXGIRTCIFPJUEQ-UHFFFAOYSA-N 0.000 description 1

- 229930185605 Bisphenol Natural products 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- MSDMPJCOOXURQD-UHFFFAOYSA-N C545T Chemical compound C1=CC=C2SC(C3=CC=4C=C5C6=C(C=4OC3=O)C(C)(C)CCN6CCC5(C)C)=NC2=C1 MSDMPJCOOXURQD-UHFFFAOYSA-N 0.000 description 1

- ODINCKMPIJJUCX-UHFFFAOYSA-N Calcium oxide Chemical compound [Ca]=O ODINCKMPIJJUCX-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-N Methacrylic acid Chemical compound CC(=C)C(O)=O CERQOIWHTDAKMF-UHFFFAOYSA-N 0.000 description 1

- FXHOOIRPVKKKFG-UHFFFAOYSA-N N,N-Dimethylacetamide Chemical compound CN(C)C(C)=O FXHOOIRPVKKKFG-UHFFFAOYSA-N 0.000 description 1

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N Phenol Chemical compound OC1=CC=CC=C1 ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229930182556 Polyacetal Natural products 0.000 description 1

- 239000004721 Polyphenylene oxide Substances 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910000831 Steel Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- QYKIQEUNHZKYBP-UHFFFAOYSA-N Vinyl ether Chemical compound C=COC=C QYKIQEUNHZKYBP-UHFFFAOYSA-N 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 229910021536 Zeolite Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 239000011358 absorbing material Substances 0.000 description 1

- 125000003668 acetyloxy group Chemical group [H]C([H])([H])C(=O)O[*] 0.000 description 1

- 239000004840 adhesive resin Substances 0.000 description 1

- 229920006223 adhesive resin Polymers 0.000 description 1

- 238000005054 agglomeration Methods 0.000 description 1

- 239000003570 air Substances 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 239000004844 aliphatic epoxy resin Substances 0.000 description 1

- 125000001931 aliphatic group Chemical group 0.000 description 1

- 229920000109 alkoxy-substituted poly(p-phenylene vinylene) Polymers 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229920003180 amino resin Polymers 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 150000004984 aromatic diamines Chemical class 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- GQVWHWAWLPCBHB-UHFFFAOYSA-L beryllium;benzo[h]quinolin-10-olate Chemical compound [Be+2].C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21.C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21 GQVWHWAWLPCBHB-UHFFFAOYSA-L 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- UFVXQDWNSAGPHN-UHFFFAOYSA-K bis[(2-methylquinolin-8-yl)oxy]-(4-phenylphenoxy)alumane Chemical compound [Al+3].C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC([O-])=CC=C1C1=CC=CC=C1 UFVXQDWNSAGPHN-UHFFFAOYSA-K 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- 229910052794 bromium Inorganic materials 0.000 description 1

- WUKWITHWXAAZEY-UHFFFAOYSA-L calcium difluoride Chemical compound [F-].[F-].[Ca+2] WUKWITHWXAAZEY-UHFFFAOYSA-L 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000007809 chemical reaction catalyst Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 229930003836 cresol Natural products 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000000412 dendrimer Substances 0.000 description 1

- 229920000736 dendritic polymer Polymers 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 229940117389 dichlorobenzene Drugs 0.000 description 1

- BKMIWBZIQAAZBD-UHFFFAOYSA-N diindenoperylene Chemical compound C12=C3C4=CC=C2C2=CC=CC=C2C1=CC=C3C1=CC=C2C3=CC=CC=C3C3=CC=C4C1=C32 BKMIWBZIQAAZBD-UHFFFAOYSA-N 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- HNPSIPDUKPIQMN-UHFFFAOYSA-N dioxosilane;oxo(oxoalumanyloxy)alumane Chemical compound O=[Si]=O.O=[Al]O[Al]=O HNPSIPDUKPIQMN-UHFFFAOYSA-N 0.000 description 1

- 239000002270 dispersing agent Substances 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 125000001301 ethoxy group Chemical group [H]C([H])([H])C([H])([H])O* 0.000 description 1

- 229920001038 ethylene copolymer Polymers 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 125000003709 fluoroalkyl group Chemical group 0.000 description 1

- XUCNUKMRBVNAPB-UHFFFAOYSA-N fluoroethene Chemical compound FC=C XUCNUKMRBVNAPB-UHFFFAOYSA-N 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical group FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- 229920002313 fluoropolymer Polymers 0.000 description 1

- 239000004811 fluoropolymer Substances 0.000 description 1

- 230000004927 fusion Effects 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- GNOIPBMMFNIUFM-UHFFFAOYSA-N hexamethylphosphoric triamide Chemical compound CN(C)P(=O)(N(C)C)N(C)C GNOIPBMMFNIUFM-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 1

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 1

- 150000002483 hydrogen compounds Chemical class 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- 239000002346 layers by function Substances 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 125000000956 methoxy group Chemical group [H]C([H])([H])O* 0.000 description 1

- UZKWTJUDCOPSNM-UHFFFAOYSA-N methoxybenzene Substances CCCCOC=C UZKWTJUDCOPSNM-UHFFFAOYSA-N 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- JXTPJDDICSTXJX-UHFFFAOYSA-N n-Triacontane Natural products CCCCCCCCCCCCCCCCCCCCCCCCCCCCCC JXTPJDDICSTXJX-UHFFFAOYSA-N 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 1

- JFNLZVQOOSMTJK-KNVOCYPGSA-N norbornene Chemical compound C1[C@@H]2CC[C@H]1C=C2 JFNLZVQOOSMTJK-KNVOCYPGSA-N 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- AFEQENGXSMURHA-UHFFFAOYSA-N oxiran-2-ylmethanamine Chemical compound NCC1CO1 AFEQENGXSMURHA-UHFFFAOYSA-N 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- 125000005010 perfluoroalkyl group Chemical group 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 239000002798 polar solvent Substances 0.000 description 1

- 229920000412 polyarylene Polymers 0.000 description 1

- 229920005668 polycarbonate resin Polymers 0.000 description 1

- 239000004431 polycarbonate resin Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 229920000570 polyether Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920006324 polyoxymethylene Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229940005642 polystyrene sulfonic acid Drugs 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- KCTAWXVAICEBSD-UHFFFAOYSA-N prop-2-enoyloxy prop-2-eneperoxoate Chemical compound C=CC(=O)OOOC(=O)C=C KCTAWXVAICEBSD-UHFFFAOYSA-N 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 125000002943 quinolinyl group Chemical group N1=C(C=CC2=CC=CC=C12)* 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 1

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910002027 silica gel Inorganic materials 0.000 description 1

- 239000000741 silica gel Substances 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 238000005245 sintering Methods 0.000 description 1

- 230000005476 size effect Effects 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000005236 sound signal Effects 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 229940032094 squalane Drugs 0.000 description 1

- 239000010959 steel Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 150000003457 sulfones Chemical class 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- YLQBMQCUIZJEEH-UHFFFAOYSA-N tetrahydrofuran Natural products C=1C=COC=1 YLQBMQCUIZJEEH-UHFFFAOYSA-N 0.000 description 1

- CXWXQJXEFPUFDZ-UHFFFAOYSA-N tetralin Chemical compound C1=CC=C2CCCCC2=C1 CXWXQJXEFPUFDZ-UHFFFAOYSA-N 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- JLGNHOJUQFHYEZ-UHFFFAOYSA-N trimethoxy(3,3,3-trifluoropropyl)silane Chemical compound CO[Si](OC)(OC)CCC(F)(F)F JLGNHOJUQFHYEZ-UHFFFAOYSA-N 0.000 description 1

- 229910001930 tungsten oxide Inorganic materials 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000010457 zeolite Substances 0.000 description 1

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

- Lasers (AREA)

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

Description

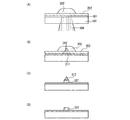

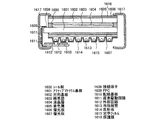

本実施の形態においては、レーザ光の光エネルギーが光吸収層に吸収されて生じた熱エネルギーを用いて膜パターンを形成する工程を図1及び図8を用いて説明する。

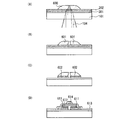

本実施の形態では、実施の形態1において、光吸収層102が導電材料で形成され、且つ、溶液103として導電体を溶媒に溶解又は分散させた溶液を用いたときの膜パターンの形成方法について、図2を用いて説明する。

本実施の形態においては、レーザ光を用いてマスクパターンを形成し、該マスクパターンを用いて膜パターンを形成する工程を、図3を用いて説明する。

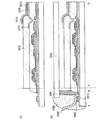

本実施の形態では、幅の狭いゲート電極層を有するTFTの作製工程について、図4を用いて説明する。なお、本実施の形態では、TFTとしてチャネルエッチ型TFTを用いて説明する。なお、実施の形態1を用いてゲート電極層を形成するがこれに限定されず、適宜実施の形態2又は実施の形態3を用いることができる。

本実施の形態では、幅の狭いゲート電極層を有するTFTの作製工程について、図5を用いて説明する。なお、本実施の形態では、TFTとしてチャネル保護型TFTを用いて説明する。本実施の形態では、実施の形態1を用いてゲート電極層を形成するがこれに限定されず、適宜実施の形態2又は実施の形態3を用いることができる。

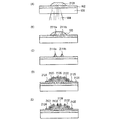

本実施の形態においては、チャネル長の小さい順スタガ型TFTの作製工程について図6を用いて説明する。本実施の形態においては、ソース領域及びドレイン領域の形成方法として実施の形態3を用いて説明するが、この工程に限らず、第1又は実施の形態2を適宜適用することができる。

本実施の形態では、TFTのコンタクトホールの形成方法を図7を用いて説明する。

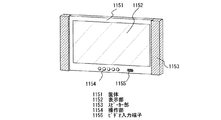

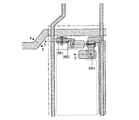

本実施の形態では、上記実施の形態におけるパターン形成に用いることができる液滴吐出装置について説明する。図24において、基板1900上において、1つのパネルが形成される領域1930を点線で示す。

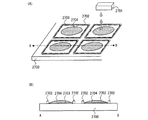

本実施の形態においては、マルチゲート構造のTFTにおいて、ゲート電極の作製工程について、図40乃至図42を用いて説明する。なお、図40及び図41は作製工程の断面図であり、図42はマルチゲート電極の上面図である。

Claims (17)

- 基板上に光吸収層を形成し、

溶液を液滴吐出法によって吐出することにより、前記光吸収層上の一部の領域にパターンを形成し、

前記光吸収層にレーザ光を照射して前記光吸収層に熱を生じさせ、前記熱により前記領域を加熱して前記パターンより小さな膜パターンを形成することを特徴とする半導体装置の作製方法。 - 基板上に光吸収層を形成し、

溶液を液滴吐出法によって吐出することにより、前記光吸収層上の一部の領域にパターンを形成し、

前記光吸収層にレーザ光の焦点を合わせて照射して前記光吸収層に熱を生じさせ、前記熱により前記溶液を加熱して前記パターンより小さな膜パターンを形成することを特徴とする半導体装置の作製方法。 - 基板上に光吸収層を形成し、

溶液を液滴吐出法によって吐出することにより、前記光吸収層上の一部の領域にパターンを形成し、

前記光吸収層にレーザ光の焦点をあわせて照射して、前記光吸収層において前記レーザ光の光エネルギーを熱エネルギーに変換し、前記熱エネルギーを用いて前記溶液を改質して前記パターンより小さな膜パターンを形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか一項において、前記基板表面と平行な面における前記膜パターンの断面形状は、前記光吸収層における前記レーザ光のビームスポット形状より小さいことを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項4のいずれか一項において、前記基板は透光性を有し、前記レーザ光を前記基板裏面側から前記光吸収層に照射することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項4のいずれか一項において、前記溶液は透光性を有し、前記レーザ光を前記溶液側から前記光吸収層に照射することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項6のいずれか一項において、前記光吸収層は、絶縁性を有する層であることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項6のいずれか一項において、前記光吸収層は、導電性を有する層であることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項8のいずれか一項において、前記膜パターンをマスクとして前記光吸収層をエッチングすることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項9のいずれか一項において、前記膜パターンは導電性を有する膜であることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項9のいずれか一項において、前記膜パターンは導電体が凝集されてなることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項9のいずれか一項において、前記溶液は熱硬化性材料又は熱可塑性材料を有し、前記膜パターンは有機樹脂で形成されることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項12のいずれか一項において、前記光吸収層は、遮光性を有することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項13のいずれか一項において、前記光吸収層は、紫外光、可視光、又は赤外光の波長を有する光を吸収することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項13のいずれか一項において、前記光吸収層は、400nm乃至700nmの波長の光を吸収することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項15のいずれか一項において、前記膜パターンの幅は、0.1μm乃至10μmであることを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項16のいずれか一項において、前記基板表面に対して垂直な面における前記膜パターンの断面の形状はガウス型曲線状又は台形状であることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005057344A JP4754848B2 (ja) | 2004-03-03 | 2005-03-02 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004059819 | 2004-03-03 | ||

| JP2004059819 | 2004-03-03 | ||

| JP2005057344A JP4754848B2 (ja) | 2004-03-03 | 2005-03-02 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005286317A JP2005286317A (ja) | 2005-10-13 |

| JP2005286317A5 JP2005286317A5 (ja) | 2008-02-28 |

| JP4754848B2 true JP4754848B2 (ja) | 2011-08-24 |

Family

ID=35184301

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005057344A Expired - Fee Related JP4754848B2 (ja) | 2004-03-03 | 2005-03-02 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4754848B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5037808B2 (ja) * | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| TWI427702B (zh) * | 2006-07-28 | 2014-02-21 | Semiconductor Energy Lab | 顯示裝置的製造方法 |

| US7943287B2 (en) | 2006-07-28 | 2011-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing display device |

| KR101346246B1 (ko) * | 2006-08-24 | 2013-12-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 제작방법 |

| US7749907B2 (en) * | 2006-08-25 | 2010-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP5276811B2 (ja) * | 2006-08-25 | 2013-08-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5227563B2 (ja) * | 2006-10-26 | 2013-07-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR101563237B1 (ko) * | 2007-06-01 | 2015-10-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 제조장치 및 발광장치 제작방법 |

| WO2010058581A1 (ja) * | 2008-11-20 | 2010-05-27 | シャープ株式会社 | シフトレジスタ |

| JP5686014B2 (ja) * | 2011-03-25 | 2015-03-18 | 凸版印刷株式会社 | 光学素子及びその製造方法 |

| US8716708B2 (en) | 2011-09-29 | 2014-05-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| EP2736076A1 (en) * | 2012-11-23 | 2014-05-28 | Nederlandse Organisatie voor toegepast -natuurwetenschappelijk onderzoek TNO | Apparatus and method for manufacturing a layered product |

| WO2014112554A1 (ja) * | 2013-01-16 | 2014-07-24 | コニカミノルタ株式会社 | 薄膜形成方法及び薄膜形成装置 |

| KR101960267B1 (ko) * | 2017-05-12 | 2019-03-21 | (주)제이스텍 | 플렉시블 디스플레이 벤딩을 위한 필름 박리방법 |

| JP6941538B2 (ja) * | 2017-11-10 | 2021-09-29 | 日本放送協会 | 塗布型金属酸化物膜の製造方法、それを用いて製造された塗布型金属酸化物膜および電子デバイス |

| EP3633658B1 (en) * | 2018-02-28 | 2022-10-05 | Kyocera Corporation | Display device, glass substrate, and method for manufacturing glass substrate |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000258921A (ja) * | 1999-03-10 | 2000-09-22 | Canon Inc | パターン形成方法およびその形成パターン |

| CN1292496C (zh) * | 2001-05-23 | 2006-12-27 | 造型逻辑有限公司 | 器件的图案形成 |

| JP2005244204A (ja) * | 2004-01-26 | 2005-09-08 | Semiconductor Energy Lab Co Ltd | 電子機器、半導体装置およびその作製方法 |

-

2005

- 2005-03-02 JP JP2005057344A patent/JP4754848B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005286317A (ja) | 2005-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4754848B2 (ja) | 半導体装置の作製方法 | |

| US7462514B2 (en) | Semiconductor device and method for manufacturing the same, liquid crystal television, and EL television | |

| US7223641B2 (en) | Semiconductor device, method for manufacturing the same, liquid crystal television and EL television | |

| JP4939756B2 (ja) | 半導体装置の作製方法 | |

| US7371625B2 (en) | Semiconductor device and manufacturing method thereof, liquid crystal television system, and EL television system | |

| US7531294B2 (en) | Method for forming film pattern, method for manufacturing semiconductor device, liquid crystal television, and EL television | |

| JP4536601B2 (ja) | 半導体装置の作製方法 | |

| JP5364779B2 (ja) | 半導体装置の作製方法 | |

| US7494923B2 (en) | Manufacturing method of wiring substrate and semiconductor device | |

| JP5292224B2 (ja) | 膜パターンの作製方法 | |

| KR101114897B1 (ko) | 반도체 장치, 텔레비전 세트 및 상기 제조 방법 | |

| US7416977B2 (en) | Method for manufacturing display device, liquid crystal television, and EL television | |

| JP5093985B2 (ja) | 膜パターンの形成方法 | |

| JP4932173B2 (ja) | 膜パターンの形成方法 | |

| JP5025107B2 (ja) | 半導体装置の作製方法 | |

| JP4754841B2 (ja) | 半導体装置の作製方法 | |

| JP4877871B2 (ja) | 表示装置の作製方法、液晶テレビジョン、及びelテレビジョン | |

| JP4785396B2 (ja) | 半導体装置の作製方法 | |

| JP4713192B2 (ja) | 薄膜トランジスタの作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080115 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110222 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110224 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110419 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110517 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110526 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140603 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140603 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |