JP4477705B2 - 差動増幅回路 - Google Patents

差動増幅回路 Download PDFInfo

- Publication number

- JP4477705B2 JP4477705B2 JP36037198A JP36037198A JP4477705B2 JP 4477705 B2 JP4477705 B2 JP 4477705B2 JP 36037198 A JP36037198 A JP 36037198A JP 36037198 A JP36037198 A JP 36037198A JP 4477705 B2 JP4477705 B2 JP 4477705B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- timing

- timing information

- circuit

- input signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45479—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection

- H03F3/45632—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit

- H03F3/45744—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit by offset reduction

- H03F3/45766—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit by offset reduction by using balancing means

- H03F3/45771—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection in differential amplifiers with FET transistors as the active amplifying circuit by offset reduction by using balancing means using switching means

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45479—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/22—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral

- H03K5/24—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral the characteristic being amplitude

- H03K5/2472—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral the characteristic being amplitude using field effect transistors

- H03K5/2481—Circuits having more than one input and one output for comparing pulses or pulse trains with each other according to input signal characteristics, e.g. slope, integral the characteristic being amplitude using field effect transistors with at least one differential stage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45624—Indexing scheme relating to differential amplifiers the LC comprising balancing means, e.g. trimming means

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45646—Indexing scheme relating to differential amplifiers the LC comprising an extra current source

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45702—Indexing scheme relating to differential amplifiers the LC comprising two resistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Amplifiers (AREA)

- Logic Circuits (AREA)

- Pulse Circuits (AREA)

Description

【発明の属する技術分野】

本発明は一般にデジタル差動増幅回路及びそのタイミング挙動に関するものである。

【0002】

【従来の技術】

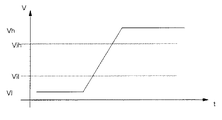

デジタル回路は通常2レベル、すなわちバイナリ・モードで動作する。すなわち、定常状態において各入力及び出力は2つの条件の一方にある。これらの条件(状態)はそれぞれ、真または偽状態、高(Vh)または低(Vl)レベル、もしくは、「1」または「0」状態と呼ばれる場合も多い。回路出力は、一般に電圧であるため、これら2つの状態は、高電圧Vihと低電圧Vilに基づく2つの電圧範囲を特徴とする。ここで、Vih>Vil。電圧Vih及びVilは、高論理しきい値及び低論理しきい値とも呼ばれる。図1に示すように、ノード電圧Vが不等式V>Vihを満たす場合、ノードは高状態にあり、V<Vilの場合、ノードは低状態にあるのは明らかである。

【0003】

用途によっては、2レベル・モードでは不十分な場合もあることが立証されており、代わりに、差動論理が用いられる。差動論理を用いるデジタル回路(今後は、デジタル差動増幅回路、あるいはただ単に差動増幅回路とも呼ばれる)において、信号電圧は、2つのノード電圧の差V=Vp−Vnと定義される。定常状態において、差動論理の2つのノード電圧Vp及びVnは必ず逆の状態である、すなわち、Vp>Vnの場合には、Vn<Vilとなり、逆も同じである。とりわけ有利なのは、差動論理を適用する回路は一般に電源電流が一定しており、同程度に低い電圧の揺れを示すので、高速で、ノイズに影響されにくく、発生するノイズが同程度に低いという点である。

【0004】

デジタル差動増幅回路を含む差動増幅回路は、正式にはECL(エミッタ結合論理)回路のようなバイポーラ・テクノロジで実施されてきた。ECLは、高速度を必要とするコンピュータにおいて用いられる場合が多い。こうした高速度を実現するため、ECLは、大量の電力を消費するので、コストのかかる冷却手段を必要とする。現在、電子産業では集積度を高くし、システムを小型化しようとする傾向にあるため、MOS(金属酸化物半導体)テクノロジによる差動増幅回路の適用が押し進められている。差動増幅回路の実施に利用されるバイポーラ・トランジスタとMOSトランジスタの主たる相違点は、下記の通りである。ECLの場合、MOSトランジスタの場合と同じ数のトランジスタを単一ICチップにパックすることができない。ECLチップに実装するトランジスタが多すぎると、過度の熱によって損傷を被ることになる。信号が極めて高い周波数で変化しなければ、MOSチップの消費電力は極めて少ない。従って、MOSの場合は単一チップに多数のトランジスタをパックすることが可能である。さらに、MOSトランジスタは、同程度の速度及び電源電流で、しきい値電圧がより高くなり、相互コンダクタンスがより低くなる。

【0005】

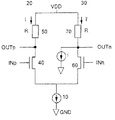

図2には、一例として、デジタル差動増幅回路のためのインバータ回路が示されている。電流源10は、第1の電流路20及び第2の電流路30に給電する。第1の電流路20には、第1の電流スイッチ40及び第1の負荷50が含まれており、第2の電流路30には、第2の電流スイッチ60及び第2の負荷70が含まれている。第1の電流スイッチ40と第2の電流スイッチ60は、通常、バイポーラ・トランジスタまたはMOSトランジスタのようなトランジスタ素子によって実施され、それぞれ、その制御電極において差動入力信号INp及びINnを受信する。第1の負荷50及び第2の負荷70は、MOSトランジスタのようなトランジスタ素子によって、あるいは、当該技術において既知の他の抵抗手段によって実施することも可能である。電流路20及び30は、それぞれ、電流スイッチと負荷の間のノードにおいて、それぞれ、差動出力信号OUTp及びOUTnを送り出す。

【0006】

動作時、差動入力信号INp及びINnの高いほうの信号によって、電流スイッチ40と60のいずれか一方がオンになり、該電流路における出力信号(OUTpまたはOUTn)の電位が高電位から低電位に引き下げられる。従って、差動信号INp及びINnの低いほうの信号によって、電流スイッチ40及び60のもう一方がオフになり、該電流路における出力信号の電位が低電位から高電位に引き上げられる。こうして、図2の回路によって、差動入力信号INp及びINnが反転される。

【0007】

入力信号または出力信号を交換することによって、非反転バッファが得られるように、図2の回路の機能に修正を加えることができるのは明らかである。

【0008】

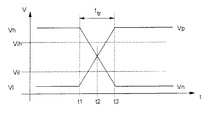

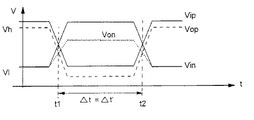

一般に、状態遷移は、ノード電圧の第1の状態から第2の状態への変化であり、デジタル回路の場合、状態遷移は、通常、2つの規定の状態の間で生じる。図3には、こうした状態遷移の一例が示されている。電圧がしきい値電圧VihとVilの範囲内にある時間は、遷移時間ttrと呼ばれる。物理的理由のため、遷移時間は、非ゼロ、ttr>0でなければならない。

【0009】

電圧がV=(Vih+Vil)/2に達する時点は、一般に、遷移のタイミング・マーク(timing mark)と呼ばれる。差動信号の場合、タイミング・マークは差動信号が等しくなる時点である。図3において、遷移は、時間t1に開始されて、時間t3に終了し、時間t2において、2つの差動信号が等しくなり、電圧(Vih+Vil)/2に達する。遷移時間は、ttr=t3−t1と定義される。該遷移のタイミング・マークはt2になる。

【0010】

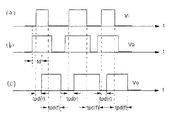

タイミング情報は、信号がある状態から別の状態に変化する際に、送り出されるか、または処理され、一般に、タイミング・マークに関する情報を含んでいる。タイミング情報を処理するか、または、送り出しているデジタル回路は、一連の入力状態遷移の結果として、一連の出力状態遷移を発生する。出力状態遷移は、図4aに示すように、時間ti(1)、ti(2)..ti(N)に生じる入力状態遷移によってto(1)、to(2)..to(N)に生じる。

【0011】

入力遷移のタイミング情報間の関係は、システムの出力において反映されなければならない。さらに、入力状態の変化間において経過する時間が、それぞれの入力状態の変化によって生じる出力状態の変化間においても経過するのが望ましい。さもなければ、システムは、タイミング情報を変化させてしまうことになるが、これは、ほとんどの用途において回避すべきことである。従って、遷移時間に関する下記の方程式が満たされる場合には、デジタル回路によって、正確なタイミング情報が生じる。

【0012】

【数1】

ここで、kは整数。

【0013】

システムまたは装置の入力における遷移のタイミング・マークti(k)とそれに対応する出力遷移のタイミング・マークto(k)との間の時間差は、伝搬遅延tpd(k)と呼ばれる、すなわち、tpd(k)=to(k)−ti(k)である。理想のデジタル回路の場合、伝搬遅延は、一定の値、tpd(k)=tpd(k+n)である(ここで、nは整数)。しかし、実際のデジタル回路では、伝搬遅延tpd(k)は、実際の入力状態、入力における状態変化の頻度等によって異なる可能性がある。

【0014】

とりわけ、デジタル電子回路が、例えば、集積回路(IC)または他の電子装置をテストするためのテスト用途において、例えば、時間測定に利用される場合、その回路によって正確なタイミングが得られることは、動作にとって重大である。すなわち、伝搬遅延tpd(k)の変動は、測定されるか、送信されるか、または、別様に処理される信号の遷移時間に対して小さいことが望ましい。

【0015】

差動増幅回路の伝搬遅延tpd(k)は、図4bに示すように、一般に、対応する時間マーク間、すなわち、Vi=0またはVip=Vinの時点とVo=0またはVop=Vonの時点の間の経過時間と定義される。これは、上述の遷移タイミング間における経過時間に一致する。

【0016】

小型化によって、回路の集積度を高めることができるだけでなく、特徴サイズが小さくなるため、より高い周波数を用いることも可能になるので、電気的回路の小型化がもくろまれている。しかし、集積度が増し、差動増幅回路が小型化されると、伝搬遅延tpd(k)のようなタイミング挙動が、同一の差動増幅回路間においてさえ大きく変動し始めることが明らかになった。さらに、例えば、伝搬遅延tpd(k)が、結局相違を生じ、特定の回路について一定の値ではなくなり、タイミング情報が回路によって変わってくることが分かった。この結果、ほとんどの用途にとって、とりわけ、テスト用途のようなタイミングに影響されやすい用途にとって全く許容できない、タイミングの欠陥を生じることになる。

【0017】

すなわち、差動増幅回路は、主として高精度な用途に用いられるので、予測不能なタイミング挙動の影響は、該テクノロジにとって非常な欠点になることが分かった。しかし、当該技術において、そのタイミング挙動の変動理由を十分に明らかにすることができなかったので、回路設計者は、ある程度の集積化及び小型化だけしか許容しないようにするか、あるいは、別のテクノロジを用いるようにしなければならなかった。

【0018】

【発明が解決しようとする課題】

本発明の目的は、集積化及び小型化のさらなる強化を可能にする差動増幅回路を提供することにある。

【0019】

【課題を解決するための手段】

差動増幅回路を小型化した場合に変動するタイミング挙動の問題を分析することによって、差動増幅回路の動作、つまりタイミング挙動は、差動増幅回路の対称性によって大きく左右されるので、差動増幅回路内の個別デバイスのパラメータが変動すると、回路全体の挙動に変動を生じることが分かった。集積度の低い回路の場合、製造プロセス時における構成要素の統計的ばらつきは、一般に、構成要素の通常の公差間内に含まれるので、対称性はほぼ均衡がとれるが、集積度が高くなると、構成要素の統計的ばらつきによって、差動増幅回路の大幅な非対称性を生じることになり、これが、統計的に、集積化及び小型化の進展と共に増大するということが明らかになった。例えば、集積度の高い回路におけるゲート長が1.2μmから0.6μmに短縮され、製造プロセスによって生じる典型的なばらつきが20nmの場合、相対的な公差は、1.5%から3.0%に増大する。しかし、所定の用途に必要な速度を得るには、特徴サイズ(ゲート長のような)を縮小しなければならない。

【0020】

図2のインバータのようなMOS適用例の場合、MOSトランジスタのしきい値電圧の変動によって、入力オフセット電圧が生じ、一方、MOSトランジスタの相互コンダクタンスの変動によって出力オフセット電圧が生じる。ある程度単純化すると、第1の電流路20と第2の電流路30の間の非対称性の影響は、第1の電流路20と第2の電流路30の間における対応する構成要素の非対称性を相殺するオフセット電圧Voffsによって表すことが可能である。図5には、第1の電流路20と第2の電流路30との非対称性に起因するオフセット電圧Voffsを有する図2のインバータが示されており、それによれば、オフセット電圧Voffsは、例えば、入力オフセット電圧、出力オフセット電圧、または、その組み合わせから生じる可能性がある。

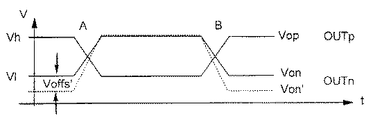

【0021】

図6には、回路におけるタイミング情報に対するオフセット電圧Voffsの影響が示されている。2つの入力信号の一方が、例えば、トランジスタのしきい値電圧の変動に起因するオフセット電圧Voffsだけシフトされる(点線で示すように)。第1の遷移Aのタイミング・マーク(Vonに関する立ち上がりエッジ)が、タイミングマークt1(オフセット電圧Voffsを生じない)からタイミングマークt1'(オフセット電圧Voffsを生じる)にシフトされる。従って、第1の遷移Aに対して逆方向の第2の遷移B(Voffsに関する立ち下がりエッジ)が、タイミングマークt2(オフセット電圧Voffsを生じない)からタイミングマークt2'(オフセット電圧Voffsを生じる)にシフトされる。しかし、図6から明らかなように、タイミング・マークt1'は、タイミング・マークt2'として逆方向にシフトされたので(その「もとの信号」に対して)、時間差△t=t2−t1が、時間差△t’=t2'−t1'に変化したことになる。以上から、立ち上がりエッジと立ち下がりエッジのタイミング・マークが逆方向にシフトされるので、オフセット電圧Voffsによって、それぞれの電流経路における電圧レベルの相対的シフト、従って、タイミング情報の変化が生じることが明らかになる。

【0022】

図7には、タイミング情報に対するオフセット電圧Voffsの影響が示されている。(a)には、初期タイミング情報が示されている。(b)には、一方の電流路においてオフセット電圧Voffsが生じる差動増幅回路に通された後の、ただし、伝搬遅延のない理想化されたタイミング図による、タイミング情報が示されている。(c)には、最終的に、伝搬遅延を伴うオフセット電圧Voffsの影響が示されている。各立ち上がりエッジは、ほぼ一定した伝搬遅延tpd(r)だけ遅延し、一方、各立ち下がりエッジは、ほぼ一定した伝搬遅延tpd(f)だけ遅延する。(c)におけるタイミング情報は、一定の遅延時間tdだけ遅延するが、伝搬遅延tpd(r)とtpd(f)が等しくないのは明らかである。

【0023】

さらに、ほぼ一定したオフセット電圧Voffsを生じることのない他の影響によって、やはり、入力情報のタイミング情報に変化を生じる可能性のあることも分かった。例えば、出力ノードOUTp及びOUTnにおける出力容量が異なると、やはり、異なるタイミング・エッジに関して伝搬遅延の変動を生じる可能性がある。

【0024】

本発明によれば、例えば、オフセット電圧Voffsに起因するタイミング情報の変化の影響は、少なくとも一方の電流路における電圧レベル、例えば、Vip及び/またはVinのレベルを修正することによって補償される。電圧レベルは、出力信号のタイミング情報が少なくとも入力信号のタイミング情報とほぼ同等になるまで修正される。これによって、製造プロセス時における装置の公差に起因する差動増幅回路の非対称性の影響を補償することが可能になるので、差動増幅回路は、印加される信号のタイミング情報を変えることなく、より集積密度の高い回路にも適用可能になる。

【0025】

補償は、原則として、補償すべき回路の入力において既知のタイミング特性を備えた規定の入力信号を加えることによって実行可能である。結果生じる出力信号のタイミング特性は、入力信号のタイミング特性と比較され、電流路の少なくとも一方における少なくとも1つの電圧レベルが、出力信号と入力信号のタイミング特性が一致するまで修正される。タイミング特性は、立ち上がりエッジと立ち下がりエッジの伝搬遅延を比較することによって調整するのが望ましい。望ましい実施態様の場合、加えられる入力信号は、デューティ・サイクルが約50%の信号である、すなわち、立ち上がりエッジと立ち下がりエッジとの間の時間がほぼ等しい。出力信号のデューティ・サイクルが測定されて、入力信号と比較される。次に、電流路の少なくとも一方における少なくとも1つの電圧レベルが、出力信号のデューティ・サイクルが約50%になるまで修正される。

【0026】

より精密な補償の場合には、各電流路毎に、所定の程度まで修正を施すことになる可能性がある。すなわち、少なくとも対をなす一方のコンポーネントに修正を加えることによって、各対をなす対応するコンポーネント毎に補償を行うことになる可能性がある。

【0027】

タイミング情報の変化は、トリミング回路に関する2つの原理に基づく方法で補償することが可能である。オームの法則に従って、第1の原理に基づく方法として、インピーダンスRを変化させるか、あるいは、第2の原理に基づく方法として、それぞれの電流Iを変化させることによって電圧レベルVを修正することが可能である。

【0028】

トリミング回路に関する第1の原理に基づく方法の後、電流路の少なくとも一方における少なくとも1つのインピーダンスRが修正される。インピーダンスR(例えば、抵抗器または負荷デバイス)の修正は、例えば、必要に応じて、並列または直列をなす多くのデバイスをスイッチして、タイミング・エラーを調整するか、トランジスタの制御電圧を調整して、インピーダンスを修正するか、並列をなす少なくとも1つの(例えば、FET)トランジスタをスイッチして、その制御電圧を調整し、インピーダンスを修正するか、あるは、当該技術において既知の他の手段によって実施することが可能である。

【0029】

図8aには、図2のインバータ回路の例における一方の電流路において少なくとも1つのインピーダンスR’に調整を加えるための原理が示されており、その効果が図8bに示されている。図8bにおける出力電圧OUTnの点線(Von')から明らかなように、インピーダンスR’が変動すると、Vlにオフセット電圧Voffs'が生じ(Vhは影響を受けない状態を保ち)、連続線Vonで示されたR’=Rである対称な状況と比べて、遷移中の立ち上がりエッジと立ち下がりエッジに異なる角度が生じる。従って、遷移のタイム・マークは、インピーダンスR’を変化させると変動するというわけである。従って、インピーダンスR’の値を変化させることによって、立ち上がりエッジと立ち下がりエッジに関する伝搬遅延がほぼ等しくなるように調整を加え、その結果、出力信号のタイミング情報が入力信号のタイミング情報と同等になるようにすることが可能である。

【0030】

インピーダンスの調整には、基本的に、補償される回路内における追加電力が不要という利点がある。電力消費は、いずれにしても、セルを駆動する差動電流によって決まる。

【0031】

トリミング回路に関する第2の原理に基づく方法の後、電流路の少なくとも1つの電流Iが修正される、すなわち、少なくとも1つの調整電流iが、電流路の少なくとも一方に追加される。電流の修正は、例えば、一方の電流路とアースのような低電位との間の少なくとも1つの(例えば、FET)トランジスタをスイッチし、その制御電圧に調整を加えて、電流iの値を調整するか、または、当該技術において既知の他の電流手段によって実施可能である。一定の(調整)電流の非対称な追加は、ノードOUTp及びOUTnから大地電位にトランジスタをスイッチすることによって実施するのが望ましい。

【0032】

図9には、図2のインバータ回路の例における、1つの調整電流を追加することによって、電流路の一方における少なくとも1つの電流I’に調整を加えるための原理が示されており、その効果が図9bに示されている。図9bにおける出力電圧OUTnの点線(Von'')から明らかなように、電流I’が変動すると、(連続した)線Vonで示されたR’=Rである対称状況に対するオフセット電圧Voffs''が生じる。しかし、図8bにおけるオフセット電圧Voffs'と比較すると、オフセット電圧Voffs''は、出力電圧OUTnの全範囲にわたって重畳されている。従って、立ち上がりエッジ及び立ち下がりエッジに関する伝搬遅延がほぼ等しくなるように調整可能である。

【0033】

本発明による電流修正は、追加電流やインピーダンス修正に関する電力を必要とするが、負荷キャパシタンスが低くなる。もう1つの利点は、電流源としてNFETを用いることができるということである。NFETはこの場合、より小さくすることが可能であり、そのドーパント濃度のため、出力ノードに追加される容量負荷も少ない。

【0034】

本発明の望ましい実施態様の場合、電流路の調整は、電流路の一方における出力信号の電圧レベルをより低いレベルに引き下げることによって実施される。従って、回路は各電流路毎に調整手段を含んでおり、出力信号のうち電圧レベルが高いほうの電流路だけがより低いレベルに引き下げられる。もう1つの実施態様の場合、両方の出力信号の電圧レベルがより低いレベルに引き下げられる。従って、「アップ・サイド・ダウン構成」の場合、例えば、PFETをスイッチとして利用し、NFETを負荷として利用すると、電圧レベルをより高いレベルに引き上げることが可能になる。例えば、各側から引き出される電流の量は、調整がつくまで、各電流路においてそれぞれある数のトランジスタをオンにすることによって調整可能である。両方の実施態様とも、能動素子を必要としないので、より調整しやすい実施態様が可能になる。

【0035】

インピーダンス及び電流の調整を同時に施すことが可能であること、あるいは、一方の電流路において、インピーダンス調整を実施し、もう一方の電流路において、電流の調整を施すことも可能であるのは明白である。

【0036】

図9cには、本発明によるタイミング調整に関する原理の一例が示されている。入力信号Vip及びVinが実線で示されている。(調整済みの)出力信号Vop及びVonのタイミング挙動が点線で示されている。言うまでもなく、単純化のため、入力信号Vip及びVinに対する出力信号Vop及びVonの内部遅延が省略されているので、入力信号と出力信号のタイミング・マークt1及びt2は一致する。すなわち、入力信号と出力信号が、同じタイミング情報、従って、立ち上がりエッジと立ち下がりエッジに関する同じ伝搬遅延を示す。

【0037】

図8a、8b、及び、9a、9bと組み合わせることによって図9cから明らかなように、電流路20における出力ノードOUTpの電圧レベルVopは、電流I(図9a)を変化させることによって、例えば、出力ノードOUTpと大地電位の間に電流源iを加えることによって調整された。それとは対照的に、電流路30における出力ノードOUTnの電圧レベルは、インピーダンス70(図9a)の値を変化させることによって、例えば、さらに1つ以上のインピーダンスを並列に接続することによって調整された。電流路20及び30の調整は、出力信号のタイミング情報が、入力信号のタイミング情報と同等になるまで、すなわち、換言すれば、タイミング・マーク間における対応する時間差△t=△t’(=t2−t1)が、入力情報と出力情報の両方について同じになるまで実行される(図6と比較されたい)。しかし、図9cから明らかなように、補償結果として、調整された出力信号VopとVonは、必ずしも対称になる必要はない。

【0038】

一般に、補償効果は、下記のように実行することが可能である。例えば、信号VopをVop'=Vop+Vomodpに変化させると、タイミングについて関連したVop'=Vonの時点も変化する。VonをVon'=Von+Vomodnに変化させると、Vop=Von'の時点も変化する。従って、同様に信号VopをVop'=Vop+Vomodpに変化させ、VonをVon'=Von+Vomodnに変化させると、Vop'=Von'の時点が修正される。

【0039】

線形立ち上がり遷移中における信号電圧は、次のように表すことができる。

【0040】

【数2】

【0041】

電圧Vは、レベルVlから開始して、その定常状態の高レベルVhに達するまで、時間の経過とともに線形に上昇する(図6と比較されたい)。立ち下がり遷移は、次のように表すことができる。

【0042】

【数3】

【0043】

非修正信号VopとVonの交差点がタイミング・マークt1で、Vop'が式2に従い、Von'が式3に従う場合、交差点としてのタイミング・マークt1'(ここで、Vop'=Von')は、次のように計算することができる。

【0044】

【数4】

【0045】

t1は、遷移Aの結果生じるタイミング・マークであり(図6と比較されたい)、t2は、遷移Bの初期タイミング・マークである場合、遷移Bの結果生じるタイミング・マークt2'は、下記のように計算することができる。

【0046】

【数5】

【0047】

差動増幅回路における出力レベルの変化は、オームの法則を用いることによって実施可能である。

【0048】

【数6】

【0049】

Vを修正すべき場合には、IまたはRを変化させることが可能である。この結果、上述のようなトリミング回路を実施する、下記による2つの方法が得られる。

1.図8a及び8bに示す負荷デバイスの非対称的修正すなわち上述の式におけるR’=R+dR

2.図9a及び9bにおける調整電流のような定電流dIの非対称的追加。

【0050】

もちろん、本発明は、例えば図5に示すオフセット電圧Voffsを補償するだけではなく、差動増幅回路によって、加えられる入力信号のタイミング情報が変化しないようにするため、差動増幅回路のタイミング挙動を調整するためのツールも提供する。本発明による補償の結果、既存のオフセット電圧Voffsが上昇することさえあるし、あるいは、以前は存在しなかったオフセット電圧Voffsが生じることになる場合さえある(図9c参照)。しかし、本発明の補償によれば、入力信号のタイミング情報の変化に起因するタイミングの欠陥が軽減されるか、あるいは、解消されさえする。

【0051】

従って、本発明によれば、さらに集積化及び小型化を押し進めたとしても、改善されたタイミング挙動、あるいは、理想に近いタイミング挙動さえ示す差動増幅回路を提供することが可能になる。この結果、速度及びタイミング精度に対する妥協を強いられることなく、高集積度の回路を用いることが可能になる。

【0052】

もちろん、本発明による補償は、XOR、フリップ・フロップ等のような任意の種類の差動増幅回路または論理ゲートに適用することが可能であり、分かりやすくするためだけに用いられた図2に示すインバータ回路に制限されるわけではない。

【0053】

【実施例】

以下では、本発明による差動増幅回路を調整するための実施態様が、図2のインバータ回路の例に関して示される。調整には、差動増幅回路の動作点を修正し、伝搬遅延の差を取り除くことができるようにする必要がある。実施態様は、MOSテクノロジに関して示されるが、もちろん、本発明はそれに制限されるものではなく、任意のテクノロジで実施される任意の差動増幅回路をそれ相応に調整することが可能である。

【0054】

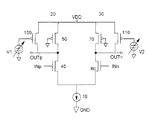

図10aには、電流路の少なくとも一方における少なくとも1つのインピーダンスが修正される、トリミング回路に関する第1の原理に基づく方法に従った、図2のインバータ回路を調整するための一例が示されている。第1の電流路20の第1の負荷50及び第2の電流路30の第2の負荷70はトランジスタとして実施され、そのインピーダンスはそれぞれ、ゲート電極に印加される制御電圧によって設定される。インピーダンス手段100(及び110)は、第1の負荷50と第2の負荷70の少なくとも一方(できれば、両方)に対して並列に接続される。インピーダンス手段100及び110は、トランジスタとして実施するのが望ましく、そのインピーダンスは、それぞれ、その制御(ゲート)電極に印加される制御電圧V1及びV2によって設定することが可能である。制御電圧V1及びV2は、アナログ電圧源または当該技術において既知の他の電圧供給手段によって実施することが可能である。

【0055】

図10bには、インピーダンス手段100及び110の実施例が示されている。インピーダンス手段100及び110はそれぞれ、並列接続をなすように構成された複数のトランジスタ100.1,...,100.n及び110.1,...,110nとして実施される。ある実施態様の場合、大地電位(0V)または高電位の(VDD)の電圧(レール電圧)は、制御電極に関する制御電圧として印加される。

【0056】

望ましい実施態様の場合、インピーダンス手段100及び110は、複数の並列トランジスタ100.1,...,100.n及び110.1,...,110nとして実施されるので、インピーダンス手段100及び110のデジタル制御が可能になる。複数のトランジスタ100.1,...,100.nの制御(ゲート)電極は制御バス120に結合され、複数のトランジスタ110.1,...,110nの制御(ゲート)電極は制御バス130に結合される。制御バス120及び130によってデジタル信号が複数のトランジスタ100.1,...,100.n及び110.1,...,110nに供給され、これによって、次にトランジスタがオンまたはオフになり、その結果、インピーダンス手段100及び110のインピーダンスが修正される。

【0057】

図11aには、電流路の少なくとも一方における少なくとも1つの電流Iが修正される、トリミング回路に関する第2の原理に基づく方法に従った、図2のインバータ回路を調整するための一例が示されている。第1の電流源150は、出力ノードOUTpとOUTnの一方に結合される。第2の電流源160は、出力ノードOUTpとOUTnのもう一方に結合するのが望ましい。第1の電流源150及び第2の電流源160は、トランジスタとして実施されるのが望ましく、それぞれの出力ノードOUTpまたはOUTnに加えられる電流値は、それぞれ、その制御(ゲート)電極に印加される制御電圧V1及びV2によって設定することが可能である。制御電圧V1及びV2は、アナログ電圧源によって、または、当該技術において既知の他の電圧供給手段によって実施することが可能である。

【0058】

図11bには、それぞれ、並列接続をなすように構成された複数のトランジスタ150.1,...,150n及び160.1,...,160nとして実施された、第1の電流源150及び第2の電流源160の実施例が示されている。第1の電流源150及び第2の電流源160によって供給される電流値は、複数のトランジスタ150.1,...,150n及び160.1,...,160nの制御(ゲート)電極に制御電圧を印加することによって設定可能である。

【0059】

望ましい実施態様の場合、第1の電流源150及び第2の電流源160は、可制御電流出力デジタル・アナログ変換器(CCO−DAC)150及び160として実施され、複数のトランジスタ150.1,...,150nの制御(ゲート)電極は、制御バス170に結合され、複数のトランジスタ160.1,...,160nの制御(ゲート)電極は、制御バス180に結合される。制御バス170及び180によって、デジタル信号が複数のトランジスタ150.1,...,150.n及び160.1,...,160nに供給され、これによって、次に、トランジスタがオンまたはオフになり、その結果、第1の電流源150及び第2の電流源160によって供給される電流値が修正される。

【0060】

第1の電流源150及び第2の電流源160は、出力ノードOUTpまたはOUTnと大地電位のような低電位との間に接続するのが望ましい。その場合、電流iは、差動増幅回路のそれぞれの電流路から「引き出される」だけであるため、より容易に実施することが可能になる。

【0061】

CCD−DAC150及び160は、k(例えば6)の2値重み付けを施された電流源によって実施するのが望ましい。個別にオン/オフして、電流の量を調整することが可能なこれらの電流源は、これらのFETのソース・コネクタが低(大地)電位に接続される場合、NMOS FETとして実施するのが望ましい。一方、これらのトランジスタのドレイン・コネクタが高電位に接続される場合、電流源はPMOS FETとして実施するのが望ましい。ゲート・コネクタは、トランジスタを通る電流を制御するk(例えば6)のデジタル信号によって駆動するのが望ましい。デジタル信号によって、電流をオン/オフすることが可能である。出力ノードOUTpまたはOUTnに供給される電流負荷は、kの個別電流の和である。

【0062】

インピーダンス手段100及び110と第1の電流源150及び第2の電流源160は、それに従って構成することが可能であり、その接点の1つが、出力ノードOUTpまたはOUTnに結合されるのが望ましい。差動増幅回路による伝搬遅延を変化させるため、2つの出力ノードOUTpまたはOUTnは、別様に負荷を加えるのが望ましい。プログラム可能なインピーダンス手段100.1,...,100nまたは110.1,...,110nまたはCCD−DAC150及び160は、それぞれの側におけるデジタル入力信号が反転されるようにプログラム可能であることが望ましい。

【0063】

〔実施態様〕

なお、本発明の実施態様の例を以下に示す。

【0064】

〔実施態様1〕 ほぼ対称をなすように形成された2つの電流路(20、30)において、差動入力信号を受信し、出力信号を送り出すための回路であって、2つの電流路(20、30)の少なくとも一方に、入力信号のタイミング情報と出力信号のタイミング情報とを合わせるように調整するための調整手段が含まれていることを特徴とする回路。

【0065】

〔実施態様2〕 前記調整手段(R’、I’)に、出力信号のタイミング情報が、少なくともほぼ入力信号のタイミング情報を表すようになるまで、それぞれの電流路における電圧レベルに修正を加えるための手段が含まれていることを特徴とする、実施態様1に記載の回路。

【0066】

〔実施態様3〕 前記調整手段(R’、I’)に、それぞれの電流路におけるインピーダンス(R’)に修正を加えるための手段が含まれていることを特徴とする、実施態様1または実施態様2に記載の回路。

【0067】

〔実施態様4〕 前記調整手段(R’、I’)に、それぞれの電流路における電流(I’)に修正を加えるための手段が含まれていることを特徴とする、実施態様1または実施態様2のいずれか一項に記載の回路。

【0068】

〔実施態様5〕 前記調整手段(R’、I’)に、それぞれの電流路におけるインピーダンス(R’)に修正を加えるための手段と、電流(I’)に修正を加えるための手段が含まれていることを特徴とする、実施態様1または実施態様2に記載の回路。

【0069】

〔実施態様6〕 前記インピーダンス(R’)に修正を加えるための手段に、並列及び/または直列に接続されたトランジスタ素子が望ましい、複数のインピーダンス素子が含まれることを特徴とする、実施態様3に記載の回路。

【0070】

〔実施態様7〕 前記電流(I’)に修正を加えるための手段に、少なくとも1つのトランジスタ素子が望ましい、少なくとも1つの調整電流源(i)を追加するための手段が含まれることを特徴とする、実施態様4に記載の回路。

【0071】

〔実施態様8〕 前記少なくとも1つの調整電流源(i)が、それぞれの電流路と低または高電位の間に接続されることを特徴とする、実施態様7に記載の回路。

【0072】

〔実施態様9〕 実施態様1または実施態様2に記載の回路を利用して、出力信号のタイミング情報と入力信号のタイミング情報とを合わせるように調整する方法。

【0073】

〔実施態様10〕 ほぼ対称をなすように形成された2つの電流路(20、30)を備える差動増幅回路からの出力信号のタイミング情報と、差動増幅回路に加えられた入力信号のタイミング情報とを合わせるように調整するための方法であって、

(a)既知のタイミング情報を備えた規定の入力信号を加えるステップと、

(b)結果生じる出力信号のタイミング情報と入力信号のタイミング情報を比較するステップと、

(c)出力信号と入力信号のタイミング情報が、少なくともほぼ一致するまで、電流路の少なくとも一方における少なくとも1つの電圧レベルに修正を加えるステップと

を設けて成る方法。

【0074】

〔実施態様11〕 前記ステップ(a)において、加えられる入力信号が、好ましくは約50%で規定されたデューティ・サイクル信号を備えることと、

前記ステップ(b)において、出力信号のデューティ・サイクルが測定され、入力信号のデューティ・サイクルと比較されることと、

前記ステップ(c)において、入力信号と出力信号のデューティ・サイクルが少なくともほぼ一致するまで、電流路の少なくとも一方における少なくとも1つの電圧レベルが修正されること

を特徴とする、実施態様10に記載の方法。

【図面の簡単な説明】

【図1】高論理しきい値と低論理しきい値の間における遷移を示す図である。

【図2】当該技術において既知のインバータ回路を示す図である。

【図3】差動増幅回路における状態遷移の一例を示す図である。

【図4a】差動入力及び出力の状態遷移を示す図である。

【図4b】差動入力及び出力の状態遷移を示す図である。

【図5】非対称性に起因するオフセット電圧Voffsを生じる図2のインバータを示す図である。

【図6】タイミング情報に対するオフセット電圧Voffの影響を示す図である。

【図7】タイミング情報に対するオフセット電圧Voffの影響を示す図である。

【図8a】本発明に従って、図2のインバータ回路の電流路の一方における少なくとも1つのインピーダンスR’を調整する機能を有する回路を示す図である

【図8b】本発明に従って、図2のインバータ回路の電流路の一方における少なくとも1つのインピーダンスR’を調整するための原理及び効果を示した図である。

【図9a】本発明に従って、図2のインバータ回路の電流路の一方における少なくとも1つの電流I’を調整する機能を有する回路を示す図である。

【図9b】本発明に従って、図2のインバータ回路の電流路の一方における少なくとも1つの電流I’を調整するための原理及び効果を示す図である。

【図9c】本発明によるタイミング調整の原理の一例を示す図である。

【図10a】本発明の実施態様によるトリミング回路の一例を示す図である。

【図10b】本発明の実施態様によるトリミング回路の一例を示す図である。

【図11a】本発明の実施態様によるトリミング回路の一例を示す図である。

【図11b】本発明の実施態様によるトリミング回路の一例を示す図である。

【符号の説明】

10 電流源

20 第1の電流路

30 第2の電流路

40 第1の電流スイッチ

50 第1の負荷

60 第2の電流スイッチ

70 第2の負荷

100 インピーダンス手段

110 インピーダンス手段

120 制御バス

130 制御バス

150 第1の電流源

160 第2の電流源

170 制御バス

180 制御バス

Claims (3)

- ほぼ対称をなすように形成された2つの電流路を有するデジタル差動増幅回路からの出力信号のタイミング情報を該デジタル差動増幅回路に印加される入力信号のタイミング情報に合わせて調整する方法であって、

(a)既知のタイミング情報を有する所定の入力信号を印加するステップと、

(b)結果得られた出力信号のタイミング信号を入力信号のタイミング情報と比較するステップと、

(c)前記出力信号のタイミング情報と前記入力信号のタイミング情報が少なくともほぼ一致するまで、前記電流路のうちの少なくとも一方の電圧レベルを変更するステップ

を含む方法。 - 前記ステップ(a)において、印加される入力信号の前記既知のタイミング情報が所定のデューティ・サイクル、好ましくは約50%のデューティ・サイクルであり、

前記ステップ(b)において、前記出力信号のデューティ・サイクルが前記入力信号のデューティ・サイクルと比較され、

前記ステップ(c)において、前記入力信号のデューティ・サイクルと前記出力信号のデューティ・サイクルが少なくともほぼ一致するまで、前記電流路のうちの前記少なくとも一方の電圧レベルを変更する、請求項1に記載の方法。 - 前記ステップ(c)における前記電流路のうちの少なくとも一方の電圧レベルを変更することが、一方の前記電流路のインピーダンスと、他方の前記電流路に流れる電流量の両方を調整することである、請求項1または2に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US995,886 | 1997-12-22 | ||

| US08/995,886 US5999028A (en) | 1997-12-22 | 1997-12-22 | Differential circuits with adjustable propagation timing |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11261350A JPH11261350A (ja) | 1999-09-24 |

| JP4477705B2 true JP4477705B2 (ja) | 2010-06-09 |

Family

ID=25542318

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP36037198A Expired - Lifetime JP4477705B2 (ja) | 1997-12-22 | 1998-12-18 | 差動増幅回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US5999028A (ja) |

| JP (1) | JP4477705B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6392448B1 (en) | 2000-02-03 | 2002-05-21 | Teradyne, Inc. | Common-mode detection circuit with cross-coupled compensation |

| US6300804B1 (en) | 2000-02-09 | 2001-10-09 | Teradyne, Inc. | Differential comparator with dispersion reduction circuitry |

| US6384637B1 (en) * | 2000-06-06 | 2002-05-07 | Rambus | Differential amplifier with selectable hysteresis and buffered filter |

| US6683498B2 (en) * | 2000-07-03 | 2004-01-27 | Broadcom Corporation | Protection circuit for extending headroom with off-chip inductors |

| DE10145656A1 (de) * | 2001-09-15 | 2003-04-03 | Philips Corp Intellectual Pty | Komparator |

| JP4235433B2 (ja) * | 2002-10-31 | 2009-03-11 | ザインエレクトロニクス株式会社 | 受信回路及びそれを備えた差動回路 |

| US6937054B2 (en) * | 2003-05-30 | 2005-08-30 | International Business Machines Corporation | Programmable peaking receiver and method |

| JP2006109105A (ja) * | 2004-10-05 | 2006-04-20 | Nec Electronics Corp | 半導体集積回路及びその制御方法 |

| US7358809B2 (en) * | 2004-11-08 | 2008-04-15 | Elder J Scott | Method for forming elements with reduced variation |

| KR100744069B1 (ko) * | 2005-09-28 | 2007-07-30 | 주식회사 하이닉스반도체 | 디지털과 아날로그 제어를 이용한 전압제어지연라인의딜레이 셀 |

| JP5264401B2 (ja) * | 2008-10-10 | 2013-08-14 | キヤノン株式会社 | Pll回路 |

| WO2014024263A1 (ja) * | 2012-08-07 | 2014-02-13 | 富士通株式会社 | クロック分配回路 |

| KR102178865B1 (ko) * | 2015-02-25 | 2020-11-18 | 한국전자통신연구원 | 고속 스위칭 성능을 갖는 캐스코드 타입의 스위치 회로 |

| KR20220057159A (ko) * | 2020-10-29 | 2022-05-09 | 에스케이하이닉스 주식회사 | 차동 입력 회로를 포함하는 반도체 장치 및 그의 캘리브레이션 방법 |

| US11881969B2 (en) * | 2022-04-22 | 2024-01-23 | Samsung Display Co., Ltd. | Real-time DC-balance aware AFE offset cancellation |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4464631A (en) * | 1981-12-01 | 1984-08-07 | Harris Corporation | Circuit for trimming FET differential pair offset voltage without increasing the offset voltage temperature coefficient |

| US4717888A (en) * | 1986-05-22 | 1988-01-05 | Raytheon Company | Integrated circuit offset voltage adjustment |

| US4827222A (en) * | 1987-12-11 | 1989-05-02 | Vtc Incorporated | Input offset voltage trimming network and method |

| US5045806A (en) * | 1988-04-17 | 1991-09-03 | Teledyne Industries | Offset compensated amplifier |

| US4987327A (en) * | 1989-05-30 | 1991-01-22 | Motorola, Inc. | Apparatus for adjusting DC offset voltage |

| US5132559A (en) * | 1991-05-03 | 1992-07-21 | Motorola, Inc. | Circuit for trimming input offset voltage utilizing variable resistors |

| US5812005A (en) * | 1996-07-30 | 1998-09-22 | Dallas Semiconductor Corp. | Auto zero circuitry and associated method |

-

1997

- 1997-12-22 US US08/995,886 patent/US5999028A/en not_active Expired - Fee Related

-

1998

- 1998-12-18 JP JP36037198A patent/JP4477705B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11261350A (ja) | 1999-09-24 |

| US5999028A (en) | 1999-12-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4477705B2 (ja) | 差動増幅回路 | |

| US6593795B2 (en) | Level adjustment circuit and data output circuit thereof | |

| US8274331B2 (en) | Differential receiver | |

| US7075339B2 (en) | Semiconductor output circuit device | |

| US10063232B1 (en) | Digitally controlled impedance calibration for a driver using an on-die reference resistor | |

| US7391825B2 (en) | Comparator circuit having reduced pulse width distortion | |

| CN113691249A (zh) | 工作周期校正电路及其方法 | |

| US7518424B2 (en) | Slew rate controlled output circuit | |

| US20070046337A1 (en) | Comparator circuit and semiconductor apparatus | |

| KR20030002305A (ko) | 반도체 집적 회로 | |

| JP4923442B2 (ja) | 差動信号伝送回路および差動信号伝送装置 | |

| US7218169B2 (en) | Reference compensation circuit | |

| US6377095B1 (en) | Digital-edge-rate control LVDS driver | |

| US8504320B2 (en) | Differential SR flip-flop | |

| US20060164144A1 (en) | Flip-flop circuit and semiconductor device | |

| US10447246B1 (en) | Low voltage differential signaling circuit | |

| US6545503B1 (en) | Output buffer for digital signals | |

| JP3158000B2 (ja) | バイアス回路 | |

| KR20030028486A (ko) | 차동 입력 신호를 위한 대칭 클럭 수신기 | |

| US20100148854A1 (en) | Comparator with reduced power consumption | |

| US20100073037A1 (en) | Output impedance control circuit | |

| US20080238517A1 (en) | Oscillator Circuit and Semiconductor Device | |

| TWI672002B (zh) | 比較器電路系統 | |

| JP3688072B2 (ja) | 可変遅延回路 | |

| EP0924854B1 (en) | Differential circuits for higher integration |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20050909 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051216 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20071025 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20071025 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080603 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080610 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080910 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080916 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090519 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090807 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100309 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100312 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130319 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130319 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130319 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130319 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140319 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |