JP4418713B2 - 乱数発生方法及び乱数発生装置 - Google Patents

乱数発生方法及び乱数発生装置 Download PDFInfo

- Publication number

- JP4418713B2 JP4418713B2 JP2004174607A JP2004174607A JP4418713B2 JP 4418713 B2 JP4418713 B2 JP 4418713B2 JP 2004174607 A JP2004174607 A JP 2004174607A JP 2004174607 A JP2004174607 A JP 2004174607A JP 4418713 B2 JP4418713 B2 JP 4418713B2

- Authority

- JP

- Japan

- Prior art keywords

- bit

- bit string

- random number

- bits

- register

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/58—Random or pseudo-random number generators

- G06F7/582—Pseudo-random number generators

- G06F7/584—Pseudo-random number generators using finite field arithmetic, e.g. using a linear feedback shift register

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/58—Indexing scheme relating to groups G06F7/58 - G06F7/588

- G06F2207/583—Serial finite field implementation, i.e. serial implementation of finite field arithmetic, generating one new bit or trit per step, e.g. using an LFSR or several independent LFSRs; also includes PRNGs with parallel operation between LFSR and outputs

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Image Processing (AREA)

Description

マスクパターンを表すビットパターンを生成して設定する設定工程と、

メモリに保持されているKビットのビット列を前記ビットパターンでマスクするマスク工程と、

前記マスク工程でマスクしたビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記メモリに保持されているKビットのビット列を予め定められた方向にシフトした結果に含める演算工程と、

予め設定されたビットパターン中の指示されたビット値に応じて、前記演算工程によるビット列中の各ビット値の反転/非反転を制御する第1の反転制御工程と、

前記第1の反転制御工程による処理結果のビット列を、Kビットで表現される乱数として出力する出力工程と

を備えることを特徴とする。

図1は、本実施形態に係る乱数発生器の基本構成を示すブロック図である。本実施形態では、画像を構成する全ての画素に対する乱数を生成する場合について説明する。

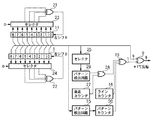

図2は、本実施形態に係る乱数発生器の基本構成を示す図である。なお、同図において図1と同じ部分については同じ番号を付けており、その説明は省略する。図2において11はシフトレジスタ、12はマスク回路、13はEXOR回路、14はパターンテーブル、15はパターン検出回路、16はラインカウンタ、17はセレクタ、18は画素カウンタ、19はEXOR回路、20はパターンカウンタである。

図3は、本実施形態に係る乱数発生器の基本構成を示す図である。同図において図1,2と同じ部分については同じ番後を付けており、その説明は省略する。同図において、21,22はEXOR回路、23,24,25はセレクタ、26はパターン検出回路、27は画素カウンタ、28はEXOR回路である。

図4は、本実施形態に係る乱数発生器の構成を示す図である。同図において図2,3と同じ部分については同じ番号を付けており、その説明は省略する。同図において、31,34はシフトレジスタ、32,35はマスク回路、33,36はEXOR回路、29はMSBテーブル、30はラインカウンタである。

第1乃至4の実施形態で説明した乱数発生方法は、図1乃至4に示す如く構成を備えるハードウェアでもって実行していたが、メモリとして機能する部分をコンピュータのRAM内に設け、メモリとして機能する部分以外のそれぞれの部分を、それぞれの部分の機能をコンピュータのCPUに実行させるためのプログラムの形態でもって実装するようにしても良い。すなわち、第1乃至4の実施形態で説明した乱数発生方法をソフトウェアの形態でもって実装し、これをコンピュータに実行させることで、このコンピュータが上記各実施形態で説明した乱数発生方法を実現させるようにしても良い。その場合、このコンピュータの構成としては周知のPC(パーソナルコンピュータ)やWS(ワークステーション)等が適用可能であり、これらのコンピュータは周知の通り、CPUやRAMを備える、また、これ以外の構成については特に限定するものではない。

本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体(または記憶媒体)を、カメラやプリンタ等の機器のCPUやMPUが記録媒体に格納されたプログラムコードを読み出し実行することによっても、達成されることは言うまでもない。この場合、記録媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記録した記録媒体は本発明を構成することになる。

Claims (11)

- Kビットで表現される乱数を発生する乱数発生方法であって、

マスクパターンを表すビットパターンを生成して設定する設定工程と、

メモリに保持されているKビットのビット列を前記ビットパターンでマスクするマスク工程と、

前記マスク工程でマスクしたビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記メモリに保持されているKビットのビット列を予め定められた方向にシフトした結果に含める演算工程と、

予め設定されたビットパターン中の指示されたビット値に応じて、前記演算工程によるビット列中の各ビット値の反転/非反転を制御する第1の反転制御工程と、

前記第1の反転制御工程による処理結果のビット列を、Kビットで表現される乱数として出力する出力工程と

を備えることを特徴とする乱数発生方法。 - 更に、前記演算工程で演算されたビット列が、ある特定のパターンのビット列であるか否かに応じて、前記予め設定されたビットパターンの反転/非反転を制御する第2の反転制御工程を備えることを特徴とする請求項1に記載の乱数発生方法。

- Kビットで表現される乱数を発生する乱数発生方法であって、

マスクパターンを表すビットパターンを生成して設定する設定工程と、

メモリに保持されている(K−1)ビットのビット列を前記ビットパターンでマスクするマスク工程と、

前記マスク工程でマスクしたビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記メモリに保持されている(K−1)ビットのビット列を予め定められた方向にシフトした結果に含める第1の演算工程と、

処理する画素の画像上の位置に応じて、前記予め設定されたビットパターン中のビット値を選択する選択工程と、

処理する画素の画像上の位置に応じて、前記選択工程で選択されたビット値を反転させる処理を制御する反転制御工程と、

前記第1の演算工程によるビット列の先頭に前記反転制御工程での処理結果のビットを付加したことにより得られるビット列を、Kビットで表現される乱数として出力する出力工程と

を備えることを特徴とする乱数発生方法。 - Kビットで表現される乱数を発生する乱数発生装置であって、

Kビットのビット列を保持するレジスタと、

マスクパターンを表すビットパターンを生成して設定する設定手段と、

前記レジスタが保持するビット列を前記ビットパターンでマスクするマスク手段と、

前記レジスタが保持するビット列を予め定められた方向にシフトするシフト手段と、

前記マスク手段がマスクしたビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記シフト手段がシフトした前記レジスタ内のビット列に含める演算手段と、

予め設定されたビットパターン中の指示されたビット値に応じて、前記演算手段によるビット列中の各ビット値を反転させる処理を制御する第1の反転制御手段と、

前記第1の反転制御手段による処理結果のビット列を、Kビットで表現される乱数として出力する出力手段と

を備えることを特徴とする乱数発生装置。 - Kビットで表現される乱数を発生する乱数発生装置であって、

(K−1)ビットのビット列を保持するレジスタと、

マスクパターンを表すビットパターンを生成して設定する設定手段と、

前記レジスタが保持するビット列を前記ビットパターンでマスクするマスク手段と、

前記レジスタが保持するビット列を予め定められた方向にシフトするシフト手段と、

前記マスク手段がマスクしたビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記シフト手段がシフトした前記レジスタ内のビット列に含める第1の演算手段と、

前記第1の演算手段によるビット列中の予め定められたビット数分のビット列がある特定のビット列であるか否かに応じて決まるビット値と、予め設定されたビットパターン中の指示されたビット値とに応じて決まるビット値を演算する第2の演算手段と、

前記第1の演算手段で演算されたビット列の先頭に前記第2の演算手段によるビットを付加したことにより得られるビット列を、Kビットで表現される乱数として出力する出力手段と

を備えることを特徴とする乱数発生装置。 - コンピュータに請求項1乃至3の何れか1項に記載の乱数発生方法を実行させることを特徴とするプログラム。

- 請求項6に記載のプログラムを格納したことを特徴とする、コンピュータ読み取り可能な記憶媒体。

- Kビットで表現される乱数を発生する乱数発生装置であって、

Kビットのビット列を保持する第1のレジスタと、

前記レジスタが保持するビット列から予め定められたビット列を選択する第1の選択手段と、

前記レジスタが保持するビット列を予め定められた方向にシフトする第1のシフト手段と、

前記第1の選択手段が選択したビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記第1のシフト手段がシフトした前記第1のレジスタ内のビット列に含める第1の演算手段と、

前記第1の演算手段によるビット列中の予め定められたビット数分のビット列が、ある特定のビット列であるか否かに応じて決まるビット値と、処理する画素の画像上の位置に応じて、前記第1の演算手段によるビット列中の各ビットの値を反転させる処理を制御する反転制御手段と、

前記反転制御手段による処理結果のビット列を、Kビットで表現される乱数として出力する出力手段と

を備えることを特徴とする乱数発生装置。 - Kビットのビット列を保持する第2のレジスタと、

前記第2のレジスタが保持するビット列から予め定められたビット列を選択する第2の選択手段と、

前記第2のレジスタが保持するビット列を予め定められた方向にシフトする第2のシフト手段と、

前記第2の選択手段が選択したビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記第2のシフト手段がシフトした前記第2のレジスタ内のビット列に含める第2の演算手段とを備え、

処理する画像上のライン終端またはライン先頭にて、前記第1のレジスタに前記第2のレジスタの値をロードすることを特徴とする請求項8に記載の乱数発生装置。 - Kビットで表現される乱数を発生する乱数発生方法であって、

メモリに保持されているKビットのビット列から予め定められたビット列を選択する第1の選択工程と、

前記メモリが保持するビット列を予め定められた方向にシフトする第1のシフト工程と、

前記第1の選択工程で選択したビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記第1のシフト工程でシフトした前記メモリ内のビット列に含める第1の演算工程と、

前記第1の演算工程によるビット列中の予め定められたビット数分のビット列が、ある特定のビット列であるか否かに応じて決まるビット値と、処理する画素の画像上の位置に応じて、前記第1の演算工程によるビット列中の各ビットの値を反転させる処理を制御する反転制御工程と、

前記反転制御工程による処理結果のビット列を、Kビットで表現される乱数として出力する出力工程と

を備えることを特徴とする乱数発生方法。 - メモリが保持するKビットのビット列から予め定められたビット列を選択する第2の選択工程と、

当該メモリが保持するビット列を予め定められた方向にシフトする第2のシフト工程と、

前記第2の選択工程で選択したビット列に対する排他的論理和演算を行い、当該排他的論理和演算結果を示すビット値を、前記第2のシフト工程でシフトした当該メモリ内のビット列に含める第2の演算工程とを備え、

処理する画像上のライン終端またはライン先頭にて、前記第1のレジスタに前記第2のレジスタの値をロードすることを特徴とする請求項10に記載の乱数発生方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004174607A JP4418713B2 (ja) | 2004-06-11 | 2004-06-11 | 乱数発生方法及び乱数発生装置 |

| US11/149,133 US7895251B2 (en) | 2004-06-11 | 2005-06-10 | Random number generating method and random number generating apparatus |

| US13/013,770 US8782108B2 (en) | 2004-06-11 | 2011-01-25 | Random number generating method and random number generating apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004174607A JP4418713B2 (ja) | 2004-06-11 | 2004-06-11 | 乱数発生方法及び乱数発生装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005352904A JP2005352904A (ja) | 2005-12-22 |

| JP2005352904A5 JP2005352904A5 (ja) | 2007-07-19 |

| JP4418713B2 true JP4418713B2 (ja) | 2010-02-24 |

Family

ID=35461790

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004174607A Expired - Fee Related JP4418713B2 (ja) | 2004-06-11 | 2004-06-11 | 乱数発生方法及び乱数発生装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7895251B2 (ja) |

| JP (1) | JP4418713B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4418713B2 (ja) * | 2004-06-11 | 2010-02-24 | キヤノン株式会社 | 乱数発生方法及び乱数発生装置 |

| FR2899702A1 (fr) * | 2006-04-10 | 2007-10-12 | France Telecom | Procede et dispositif pour engendrer une suite pseudo-aleatoire |

| US8788552B2 (en) * | 2008-01-25 | 2014-07-22 | Tata Consultancy Services Ltd. | Deterministic random number generator for cryptography and digital watermarking |

| US8645775B2 (en) * | 2008-05-21 | 2014-02-04 | Advantest (Singapore) Pte Ltd | Method and apparatus for the determination of a repetitive bit value pattern |

| US9747105B2 (en) * | 2009-12-17 | 2017-08-29 | Intel Corporation | Method and apparatus for performing a shift and exclusive or operation in a single instruction |

| JP5836585B2 (ja) * | 2010-02-09 | 2015-12-24 | キヤノン株式会社 | データ処理装置及びその制御方法、プログラム |

| US8918442B2 (en) * | 2012-08-22 | 2014-12-23 | International Business Machines Corporation | Reducing bias in hardware generated random numbers |

| JP2014222394A (ja) | 2013-05-13 | 2014-11-27 | 株式会社東芝 | 半導体記憶装置および乱数発生器 |

| JP6542171B2 (ja) * | 2016-09-15 | 2019-07-10 | 東芝メモリ株式会社 | ランダマイザおよび半導体記憶装置 |

| CN112955955B (zh) | 2018-10-24 | 2023-01-31 | 宁波飞芯电子科技有限公司 | 计数方法、计数装置以及应用其的计数系统和像素阵列 |

| GB2580160B (en) * | 2018-12-21 | 2021-01-06 | Graphcore Ltd | Hardware module for converting numbers |

| KR102199808B1 (ko) * | 2019-03-26 | 2021-01-07 | 한양대학교 에리카산학협력단 | 드론 센서 기반 진난수 생성 방법 및 장치 |

| US20230289473A1 (en) * | 2020-06-17 | 2023-09-14 | The Trustees Of Princeton University | System and method for secure and robust distributed deep learning |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3568551B2 (ja) | 1993-03-18 | 2004-09-22 | アンリツ株式会社 | 擬似ランダム信号発生装置 |

| JP3461247B2 (ja) | 1996-07-19 | 2003-10-27 | キヤノン株式会社 | 画像処理装置及び画像処理方法 |

| US5805738A (en) | 1995-12-21 | 1998-09-08 | Canon Kabushiki Kaisha | Image processing apparatus and method |

| JPH11339016A (ja) * | 1998-05-28 | 1999-12-10 | Canon Inc | 画像処理装置及び画像処理方法並びにメモリ媒体 |

| JPH11340799A (ja) * | 1998-05-28 | 1999-12-10 | Oki Electric Ind Co Ltd | M系列発生回路、m系列の発生方法及びpn系列発生回路 |

| JP3613396B2 (ja) * | 2001-06-25 | 2005-01-26 | 日本電気株式会社 | 機能ブロック |

| DE10216240A1 (de) * | 2002-04-12 | 2003-10-30 | Infineon Technologies Ag | Verfahren und Vorrichtung zur Berechnung eines iterierten Zustands einer rückgekoppelten Schieberegisteranordnung |

| US7028059B2 (en) * | 2002-06-24 | 2006-04-11 | Sun Microsystems, Inc. | Apparatus and method for random number generation |

| US20040078401A1 (en) * | 2002-10-22 | 2004-04-22 | Hilton Howard E. | Bias-free rounding in digital signal processing |

| JP4418713B2 (ja) * | 2004-06-11 | 2010-02-24 | キヤノン株式会社 | 乱数発生方法及び乱数発生装置 |

-

2004

- 2004-06-11 JP JP2004174607A patent/JP4418713B2/ja not_active Expired - Fee Related

-

2005

- 2005-06-10 US US11/149,133 patent/US7895251B2/en not_active Expired - Fee Related

-

2011

- 2011-01-25 US US13/013,770 patent/US8782108B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005352904A (ja) | 2005-12-22 |

| US20110119321A1 (en) | 2011-05-19 |

| US20050278402A1 (en) | 2005-12-15 |

| US7895251B2 (en) | 2011-02-22 |

| US8782108B2 (en) | 2014-07-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7895251B2 (en) | Random number generating method and random number generating apparatus | |

| JP2937919B2 (ja) | 疑似乱数発生回路 | |

| JP3022439B2 (ja) | 擬似乱数発生方法および装置 | |

| JP2008145791A5 (ja) | ||

| CN103098018B (zh) | 比特序列生成器 | |

| JP2004007337A5 (ja) | ||

| JP2002040933A (ja) | データ暗号化標準アルゴリズムを利用した暗号化装置 | |

| JP2006072891A (ja) | セルオートマトンに基づく、制御可能な周期を有する擬似乱数シーケンスの生成方法および装置 | |

| KR100478974B1 (ko) | 직렬 유한체 승산기 | |

| JP2005352904A5 (ja) | ||

| US9389834B2 (en) | Pseudorandom number generating circuit and method | |

| KR20050065976A (ko) | Sha-1 해쉬값 연산 장치 및 방법 | |

| JP3626105B2 (ja) | 疑似ランダム信号発生回路 | |

| JP4709685B2 (ja) | 擬似乱数生成装置、擬似乱数生成方法および擬似乱数生成プログラム並びに暗号化装置および復号化装置 | |

| JP2004166274A (ja) | 有限体での基底変換方法及び基底変換装置 | |

| US20070047622A1 (en) | Data generator having linear feedback shift registers for generating data pattern in forward and reverse orders | |

| JP2010160248A (ja) | Gold系列擬似乱数生成回路 | |

| JP2022103663A (ja) | 画像処理装置、画像処理装置の画像処理方法およびプログラム | |

| JPH07134647A (ja) | 乱数発生装置 | |

| JP2009301265A (ja) | 倍数判定方法、倍数判定装置および倍数判定プログラム | |

| RU2761766C1 (ru) | Устройство для генерации псевдослучайных чисел | |

| JP3157741B2 (ja) | 2進10進変換回路 | |

| JP4341889B2 (ja) | 楕円積和演算計算方法、楕円積和演算計算装置、プログラム及び記録媒体 | |

| JP3610564B2 (ja) | 情報処理装置 | |

| JP3618554B2 (ja) | 符号発生方法および符号発生装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070531 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070531 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090724 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090924 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091124 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091130 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121204 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131204 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |