JP4387397B2 - 3値メモリ回路 - Google Patents

3値メモリ回路 Download PDFInfo

- Publication number

- JP4387397B2 JP4387397B2 JP2006298466A JP2006298466A JP4387397B2 JP 4387397 B2 JP4387397 B2 JP 4387397B2 JP 2006298466 A JP2006298466 A JP 2006298466A JP 2006298466 A JP2006298466 A JP 2006298466A JP 4387397 B2 JP4387397 B2 JP 4387397B2

- Authority

- JP

- Japan

- Prior art keywords

- potential

- level

- circuit

- bit line

- reset

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Dram (AREA)

Description

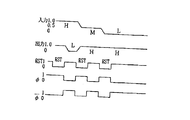

図1は、本発明にかかるセンスアンプの動作原理を説明する為の回路図であり、図2はその動作原理を説明する為のタイミングチャート図である。本明細書では、Pチャネル型MOSトランジスタについてはPを引用符号として使用し、Nチャネル型MOSトランジスタについてはQを引用符号として使用する。

に上昇する。その上昇分の約0.05Vが、増幅トランジスタP1により増幅され、ノードnampの電位はより低くなる。そして、期間t2において、サンプルパルスφ2のLレベルによりトランジスタP3を介してその電位がキャパシタC2にサンプルされる。

図3は、上記のセンスアンプ回路を3値DRAMに適用した時の回路図である。また、図4はその動作を説明するタイミングチャート図である。この例でも、電源電圧は1V、NMOSトランジスタの閾値は0.6V、PMOSトランジスタの閾値は−0.6Vとする。

先ず、リセット期間では、リセット信号φRST1が立ち上がり、ビット線BLをVRL(0.48V)にリセットし、その時のセンスアンプSA2内のノードnamp2がサンプルパルスφ1の立ち下がりによりキャパシタC12にサンプルされる。次にリセット信号φRST2が立ち上がり、ビット線BLをVRH(0.52V)にリセットし、その時のセンスアンプSA1内のノードnamp1がサンプルパルスφ2の立ち下がりによりキャパシタC11にサンプルされる。そして最後に、リセット信号φRST3が立ち上がり、ビット線BLはVRM(0.5V)にリセットされる。

リセット期間は、上記と同様である。そして、ワード線WLMが2.0Vまで立ち上がると、メモリセルMCM内には0.5Vが記憶されているので、ビット線BLの電位は変化なくリセット電位VRM(0.5V)を維持する。その時のノードnamp1,2の電位がキャパシタC21,C22にそれぞれサンプリングされる。従って、n11<n21,n12>n22の状態が、ラッチパルスφLATCH の立ち下がりによりラッチされる。従って、ノードn21はHレベル、n22はLレベルとなる。

リセット期間は、上記と同様である。そして、ワード線WLLが2.0Vまで立ち上がると、メモリセルMCL内には0Vが記憶されているので、ビット線BLの電位はCc/(CBL+Cc)×0.5V(約0.05V)の電位低下が発生する。それに従って増幅トランジスタP11,P12によって増加したノードnamp1,2の電位がサンプルパルスφ3でキャパシタC21,C22にサンプリングされる。従って、センスアンプSA2では十分な電位差ΔVをもってn12<n22となり、ラッチパルスφLATCH の立ち下がりにより、ノードn22はHレベルとなる。その時、センスアンプSA1側のノードn21もHレベルになる。従って、ノードn21とn22はいずれもHレベルとなる。

上記した様に、再書き込み回路RWの出力には、Hレベル(1V),Mレベル(0.5V),Lレベル(0V)がそれぞれ読みだされる。従って、その出力を図示しない出力回路に供給する必要がある。或いは図示しない入力回路から書き込み回路まで3値信号を供給する必要がある。メモリセルアレイが複数のブロックに分割されている場合などは、その中間で増幅する必要がある。また、出力回路内等で必要に応じて、Hレベルを検出したり、Lレベルを検出したりする回路も適宜利用することが必要になる。そこで、以下に3値インバータ、Hレベル検出回路、Lレベル検出回路の例について説明する。

3値DRAMを構成するためには、その入力段でシステム側の2進数の信号を内部記憶用の3進に変換することが必要である。一方、出力段ではその逆の変換も必要になる。

図15は、3進数2ビット信号を2進数3ビット信号に変換する回路である。また図16はその動作波形図である。この変換は、前述の変換回路の逆変換となる。この回路の場合も、電源電圧が1Vで、NチャネルMOSの閾値が0.6V、PチャネルMOSの閾値が−0.6Vである。

SA センスアンプ回路

BL ビット線

MC メモリセル

RW 再書き込み回路

MPX マルチプレクサ

Claims (4)

- メモリセルに接続されたビット線の電位を増幅する増幅部と、

該ビット線がリセット電位にされた時に該増幅部で増幅された電位を第一のサンプリングパルスにより第一のキャパシタに蓄積する第一のサンプリング保持部と、

該メモリセルによりビット線が読出し電位にされた時に該増幅部で増幅された電位を第二のサンプリングパルスにより第二のキャパシタに蓄積する第二のサンプリング保持部と、

該第一及び第二のキャパシタに保持されている電位差を検出してラッチするラッチ回路とを有することを特徴とするセンスアンプ回路。 - H,M,Lレベルの3値の電位を記憶するメモリセルと、

該メモリセルに接続されるビット線と、

前記HレベルとMレベルのメモリセルが読みだされた時のビット線の電位の中間の第1のリセット電位にビット線をリセットする第一のリセット回路と、

該ビット線を前記Mレベル近傍の第2のリセット電位にリセットする第二のリセット回路と、

前記LレベルとMレベルのメモリセルが読みだされた時のビット線の電位の中間の第3のリセット電位に該ビット線をリセットする第三のリセット回路と、

前記Hレベルのメモリセルが読みだされた時を検出する第一のセンスアンプ回路と、

前記Lレベルのメモリセルが読みだされた時を検出する第二のセンスアンプ回路と、

該第一、第二のセンスアンプ回路の出力に従って再書込み電位を前記ビット線にフィードバックする再書込み回路とを有し、

前記第一のセンスアンプ回路は、

ビット線の電位を増幅する第一の増幅部と、

該ビット線が第1のリセット電位にされた時に該第一の増幅部で増幅された電位を第一のサンプリングパルスにより第一のキャパシタに蓄積する第一のサンプリング保持部と、

該メモリセルによりビット線が読出し電位にされた時に該第一の増幅部で増幅された電位を第二のサンプリングパルスにより第二のキャパシタに蓄積する第二のサンプリング保持部と、

該第一及び第二のキャパシタに保持されている電位差を検出してラッチする第一のラッチ回路とを有し

前記第二のセンスアンプ回路は、

ビット線の電位を増幅する第二の増幅部と、

該ビット線が第3のリセット電位にされた時に該第二の増幅部で増幅された電位を第三のサンプリングパルスにより第三のキャパシタに蓄積する第三のサンプリング保持部と、

該メモリセルによりビット線が読出し電位にされた時に該第二の増幅部で増幅された電位を前記第二のサンプリングパルスにより第四のキャパシタに蓄積する第四のサンプリング保持部と、

該第三及び第四のキャパシタに保持されている電位差を検出してラッチする第二のラッチ回路とを有することを特徴とする3値メモリ回路。 - 前記再書き込み回路は、前記第一のセンスアンプ回路の出力をゲートに入力する第一のPチャネルトランジスタと、前記第二のセンスアンプ回路の出力をゲートに入力する第一のNチャネルトランジスタとを有するCMOSインバータ回路で構成され、前記第一のセンスアンプ回路がメモリセルのHレベルを検出した時に前記第一のPチャネルトランジスタを導通して出力をHレベルにし、前記第二のセンスアンプ回路がメモリセルのLレベルを検出した時に前記第一のNチャネルトランジスタを導通して出力をLレベルにし、前記メモリセルがMレベルの時には、出力をMレベルにすることを特徴とする請求項2記載の3値メモリ回路。

- 前記再書き込み回路と出力バッファとの間に、

所定電位の電源に接続され、H,M,Lレベルを有する3値入力をゲートに入力する第一のPチャネルトランジスタと、接地電源に接続され、前記3値入力をゲートに入力する第一のNチャネルトランジスタと、前記第一のPチャネルトランジスタと第一のNチャネルトランジスタの間に設けられ、リセット時に非導通となりリセット時以外で導通となる第二のP,Nチャネルトランジスタと、該第二のP,Nチャネルトランジスタの接続点に接続され、リセット時に前記Mレベルの電位にリセットされる出力端子とを有する3値インバータ回路を有することを特徴とする請求項2記載の3値メモリ回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006298466A JP4387397B2 (ja) | 2006-11-02 | 2006-11-02 | 3値メモリ回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006298466A JP4387397B2 (ja) | 2006-11-02 | 2006-11-02 | 3値メモリ回路 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP8096354A Division JPH09282892A (ja) | 1996-04-18 | 1996-04-18 | 3値メモリ回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007026672A JP2007026672A (ja) | 2007-02-01 |

| JP4387397B2 true JP4387397B2 (ja) | 2009-12-16 |

Family

ID=37787216

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006298466A Expired - Lifetime JP4387397B2 (ja) | 2006-11-02 | 2006-11-02 | 3値メモリ回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4387397B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106816166B (zh) * | 2016-12-07 | 2018-10-23 | 宁波大学 | 一种三值灵敏放大器及其实现的sram阵列 |

-

2006

- 2006-11-02 JP JP2006298466A patent/JP4387397B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007026672A (ja) | 2007-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10475491B2 (en) | Random code generator with antifuse differential cell and associated sensing method | |

| KR0164199B1 (ko) | 반도체 기억장치 | |

| CN1774766B (zh) | 具有传感放大器和自定时锁存器的存储装置及其操作方法 | |

| US11862233B2 (en) | System and method for detecting mismatch of sense amplifier | |

| US10482931B1 (en) | Reversed bias compensation for sense amplifier operation | |

| JP2009211733A (ja) | 磁気記憶装置 | |

| JPWO2009034603A1 (ja) | 半導体メモリ | |

| CN102265396A (zh) | 电容隔离的失配补偿型读出放大器 | |

| JP2002157876A (ja) | 半導体装置 | |

| US20040017717A1 (en) | Differential amplifier circuit with high amplification factor and semiconductor memory device using the differential amplifier circuit | |

| KR890003373B1 (ko) | 씨모오스 반도체 메모리 장치의 입출력 회로 | |

| JPS61110396A (ja) | 半導体記憶装置 | |

| US5452254A (en) | Semiconductor memory device | |

| JP6576510B1 (ja) | メモリデバイス及びそのテスト読書き方法 | |

| US5420869A (en) | Semiconductor integrated circuit device | |

| JP4387397B2 (ja) | 3値メモリ回路 | |

| JP6444668B2 (ja) | データ保持制御回路、データ書込方法、データ読出方法、強誘電体記憶部の特性テスト方法、半導体チップ | |

| JP5941577B1 (ja) | 半導体記憶装置 | |

| US6768678B1 (en) | Data sensing method used in a memory cell circuit | |

| JPH09282892A (ja) | 3値メモリ回路 | |

| CN110619903A (zh) | 存储装置及其测试读写方法 | |

| JP2011222091A (ja) | 半導体装置及び情報処理システム | |

| US12237009B2 (en) | Sense amplifier circuit, memory circuit, and sensing method thereof | |

| TWI409817B (zh) | 快閃記憶體的資料感測模組與感測電路 | |

| KR100474733B1 (ko) | 반도체메모리장치용데이터출력회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061102 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080731 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090914 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090929 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090930 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121009 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121009 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121009 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121009 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131009 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |