JP4385268B2 - Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method - Google Patents

Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method Download PDFInfo

- Publication number

- JP4385268B2 JP4385268B2 JP2000011070A JP2000011070A JP4385268B2 JP 4385268 B2 JP4385268 B2 JP 4385268B2 JP 2000011070 A JP2000011070 A JP 2000011070A JP 2000011070 A JP2000011070 A JP 2000011070A JP 4385268 B2 JP4385268 B2 JP 4385268B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- flip

- flop

- signal

- count value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Transmission And Conversion Of Sensor Element Output (AREA)

Description

【0001】

【産業上の利用分野】

本発明は、回転体例えばモータの速度・位置の検出に使われるエンコーダの信号処理回路において、モータの反転時に生じるパルスのヒステレシスを補償するジッタ除去手段を改良するジッタ除去回路のパルスヒステレシス補償方法とその装置ならびにその手順をコンピュータプログラムとして記録した媒体に関する。

【0002】

【従来の技術】

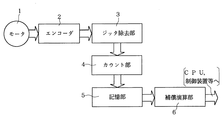

図3は、従来例としてのジッタ除去回路を用いたエンコーダの位置検出方法を示す装置のブロック図である。全ての図面において、同一符号は同一若しくは相当部材を示す。

また、図4はそのジッタ除去回路の回路構成を示す論理回路図である。

モータ1の回転により、エンコーダ2で出力された90度位相の異なる2相パルスは、ジッタ除去回路3でジッタを除去されたパルスとしてカウント部4に入力され、カウント部4ではパルスのエッジをカウントし出力する。その出力された値は中央演算装置(CPU)や記憶装置へ入力され、モータの制御に利用されていた。

【0003】

ところが、このような従来例の方法では、モータ反転時にパルスヒステレシスが発生するという問題があった。

図5は、このパルスヒステレシスを示す電圧波形のタイムチャートである。

モータ反転時のエンコーダ2相出力パルスは一般に図5 (イ) のようになり、パルスの立ち上がり立ち下がりの部分にジッタがある波形となる。

そこで、ジッタ除去回路が挿入されるのだが、ジッタを取り除くことが目的であるから、ジッタ除去回路から出力される2組のパルスは図5 (ロ) のように成るべきである。

【0004】

【発明が解決しようとする課題】

しかしながら、先の図4のジッタ除去回路を用いると出力される2相出力パルスは図5 (ハ) のようになる。

これらの図5 (ロ), (ハ) で明らかなように、従来例のジッタ除去回路を用いたエンコーダ信号処理では、図5 (ロ) に示すモータ反転後最初のB相立ち上がりで[図5の51参照]、2相出力パルス図5 (ハ) に示すの出力もB相が立ち上がるべきところを、図5 (ロ) に示すA相の立ち上がりで図5 (ハ) に示すの出力のB相が立ち上がっている[図5の52参照]。

つまり、モータ反転後最初の2カウント目で初めて1カウント目が制御装置等へ出力されており、ここにヒステレシスがあることがわかる。

そこで、本発明はこのヒステレシスを補償することをことを目的とする。

【0005】

【課題を解決するための手段】

上記目的を達成するために本発明の請求項1の発明は、モータの回転によりエンコーダが出力する90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力することを特徴とするエンコーダ信号処理回路のヒステレシス補償方法である。

このように本発明の請求項1の発明によれば、モータの反転時に生じるパルスヒステレシスを補償することができ、モータの回転を反転し、繰り返し運転を行う場合などに、オフセットすることなく正確な位置に停止することができるという特段の効果を奏する。

【0006】

本発明の請求項2の発明は、請求項1のジッタ除去回路のパルスヒステレシス補償方法において、今回のカウント値と前回カウント値の差分をとるとその差分がゼロか否かを判断し、ゼロであれば今回のカウント値を記憶して補正は行わず、次回のカウント値との差分をとる操作を繰り返し、前記差分がゼロでなければ、前回の差分と符号が違うか否かを判断し、前記符号が違えば差分の符号に応じて、+1または−1を補正量として前記今回のカウント値に加えて出力することを特徴とする請求項1記載のエンコーダ信号処理回路のヒステレシス補償方法である。

【0007】

本発明の請求項3の発明は、モータの回転によりエンコーダが出力する90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力する補償演算部を備えたことを特徴とするエンコーダ信号処理回路である。

【0008】

本発明の請求項4の発明は、モータの回転によりエンコーダが出力する90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力する手順を記録したことを特徴とするコンピュータプログラム用記録媒体である。

【0009】

【発明の実施の形態】

本発明の実施の形態について図面を参照して説明する。

図1は、本発明の実施の形態における回路構成を示すブロック図である。

この図1は、従来例の図3にカウント記憶部5とヒステレシス補償部6が追加して配置された構成である。

【0010】

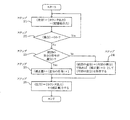

図2は、本発明に係る演算部における補償方法の操作手順を示すフローチャートである。

手順に従って図1,図2を説明する。

[1] モータ1が回転し、その変位に対応して90度位相の異なる2相のパルスがエンコーダ2より出力され、ジッタ除去部3においてパルスの立ち上がり、立ち下がりの部分が排除される。

[2] カウント部4では、ジッタの除去されたパルスの立ち上がり、立ち下がりを検出し、併せて2相パルスの方向も検出し、カウントの増減を行う。

ここまでは、従来例と同じである。そして、

[3] 記憶部5では、カウント部4より前回出力された値を保持しておく。この記憶部5の値が更新されるのは、一定時間が経過した後、若しくはカウント部4の出力が更新されたときである。

【0011】

[4] 補償演算部6では、

ステップ21として、カウント部4より現在出力されている値から、記憶部5より出力されるカウント出力の前回値を引いて差分を取る。

ステップ22では、前記差分がゼロであれば(Yes) ステップ21に戻り、ゼロでなければ(No)次のステップ23へ進む。

ステップ23として、前記差分の符号が前回のものと異なっていれば、すなわちモータ1が反転していれば(Yes) ステップ25へ、前回の差分の符号と同じであれば(No)つまりモータ1の回転方向が変わっていなければ、ステップ24へ進む。

ステップ24では、今回の差分値を前回の差分値として保存する。さらに補正値はゼロにしてステップ26へ移る。

ステップ25として、モータ1が反転しているので、今回の差分値が正であれば+1、負であれば−1を補正量として、ステップ26へ進む。さらに今回の差分値を前回の差分値として保存する[図示のように、差分符号に1を乗じたものを補正量としている]。

ステップ26では、補正出力として、カウンタ部4の出力に補正量を加えた値を出力する。

【0012】

このようにして、モータ1の反転後2つ目のエッジ[図5の51参照]が、カウンタ部4に入力されたときに、補正を加えて出力され、制御等に用いられる。

また、本発明の操作手順をコンピュータプログラムとして記述し、それを読み取ったコンピュータがヒステリシス補償部6として機能するようにしてもよいことは勿論である。

【0013】

【発明の効果】

以上述べたように本発明によれば、モータの反転時に生じるパルスヒステレシスを補償することができ、モータの回転を反転し、繰り返し運転を行う場合などに、オフセットすることなく正確な位置に停止することができるという特段の効果を奏する。

【図面の簡単な説明】

【図1】本発明の実施の形態における回路構成を示すブロック図

【図2】本発明に係る演算部における補償方法の操作手順を示すフローチャート

【図3】従来例としてのジッタ除去回路を用いたエンコーダの位置検出方法を示す装置のブロック図

【図4】図4は図3のジッタ除去回路の回路構成を示す論理回路図

【図5】従来例のパルスヒステレシスを示す電圧波形のタイムチャート

【符号の説明】

1 モータ

2 エンコーダ

3 ジッタ除去部

4 カウント部

5 記憶部

6 補償演算部[0001]

[Industrial application fields]

The present invention relates to a pulse hysteresis compensation method for a jitter removal circuit for improving a jitter removal means for compensating for the hysteresis of a pulse generated at the time of inversion of a motor in a signal processing circuit of an encoder used for detecting the speed and position of a rotating body such as a motor. The present invention relates to a device and a medium recording the procedure as a computer program.

[0002]

[Prior art]

FIG. 3 is a block diagram of an apparatus showing an encoder position detection method using a jitter removal circuit as a conventional example. In all the drawings, the same reference numerals indicate the same or corresponding members.

FIG. 4 is a logic circuit diagram showing the circuit configuration of the jitter removal circuit.

Due to the rotation of the

[0003]

However, such a conventional method has a problem that pulse hysteresis occurs when the motor is reversed.

FIG. 5 is a time chart of a voltage waveform showing this pulse hysteresis.

The encoder two-phase output pulse at the time of motor reversal is generally as shown in FIG. 5 (a), and has a jitter waveform at the rising and falling portions of the pulse.

Therefore, a jitter removal circuit is inserted. Since the purpose is to remove jitter, the two sets of pulses output from the jitter removal circuit should be as shown in FIG.

[0004]

[Problems to be solved by the invention]

However, the two-phase output pulse that is output when the jitter removal circuit of FIG. 4 is used is as shown in FIG.

As apparent from FIGS. 5 (b) and 5 (c), in the encoder signal processing using the conventional jitter removal circuit, the first B phase rising after the motor reversal shown in FIG. 51]] Two-phase output pulse In the output shown in FIG. 5 (c), the output of B shown in FIG. 5 (c) is shown at the rise of phase A shown in FIG. The phase is up [see 52 in FIG. 5].

That is, the first count is output to the control device or the like for the first time after the motor inversion, and it can be seen that there is hysteresis.

Therefore, an object of the present invention is to compensate for this hysteresis.

[0005]

[Means for Solving the Problems]

The invention of

As described above, according to the first aspect of the present invention, it is possible to compensate for the pulse hysteresis that occurs during the reversal of the motor, and when the motor rotation is reversed and repeated operation is performed, an accurate operation without offset is possible. There is a special effect of being able to stop at the position.

[0006]

The invention of

[0007]

The invention of

[0008]

In the invention of claim 4 of the present invention, a two-phase rectangular wave signal having a phase difference of 90 degrees outputted from the encoder by the rotation of the motor and an inverted signal of the rectangular wave signal are input signals of four sets of RS flip-flops, The logical product signal of the output of two sets of RS flip-flops is obtained from the output of the four sets of RS flip-flops, and the logical product signal of outputs of two other sets of RS flip-flops different from the two sets of RS flip-flops by taking, comprising a jitter removing circuit for outputting a rectangular wave signal of the jitter-free 90 degree phase different 2-phase, a counter for counting the square wave signal of the edge of which is the output two-phase of the jitter removing circuit in an encoder signal processing circuit, when the sign of the difference of the count value with the stored previous times count value of the counter is determined to have changed by the inverse of the motor A recording medium for a computer program, characterized by recording the steps of outputting by adding +1 or -1 depending on the sign of the difference in the count value.

[0009]

DETAILED DESCRIPTION OF THE INVENTION

Embodiments of the present invention will be described with reference to the drawings.

FIG. 1 is a block diagram showing a circuit configuration according to an embodiment of the present invention.

FIG. 1 shows a configuration in which a count storage unit 5 and a

[0010]

FIG. 2 is a flowchart showing the operation procedure of the compensation method in the arithmetic unit according to the present invention.

1 and 2 will be described in accordance with the procedure.

[1] The

[2] The counting unit 4 detects the rise and fall of the pulse from which jitter is removed, and also detects the direction of the two-phase pulse, and increases or decreases the count.

So far, it is the same as the conventional example. And

[3] The storage unit 5 holds the value output from the count unit 4 last time. The value of the storage unit 5 is updated after a certain time has elapsed or when the output of the count unit 4 is updated.

[0011]

[4] In the

In

In

In

In

In

In

[0012]

In this way, when the second edge after reversal of the motor 1 [see 51 in FIG. 5] is input to the counter unit 4, it is output with correction and used for control and the like.

Of course, the operation procedure of the present invention may be described as a computer program, and the computer that has read the program may function as the

[0013]

【The invention's effect】

As described above, according to the present invention, it is possible to compensate for the pulse hysteresis that occurs at the time of reversal of the motor, and when the rotation of the motor is reversed and repeated operation is performed, it stops at an accurate position without offset. There is a special effect of being able to.

[Brief description of the drawings]

FIG. 1 is a block diagram showing a circuit configuration in an embodiment of the present invention. FIG. 2 is a flowchart showing an operation procedure of a compensation method in an arithmetic unit according to the present invention. FIG. 4 is a logic circuit diagram showing the circuit configuration of the jitter removal circuit of FIG. 3. FIG. 5 is a time chart of voltage waveforms showing the pulse hysteresis of the conventional example. Explanation of]

1

Claims (4)

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力することを特徴とするエンコーダ信号処理回路のヒステレシス補償方法。And the rectangular wave signal of two different phases of 90 degrees phase encoder output by the rotation of the motor, an inverted signal of the rectangular wave signal four pairs of an input signal of the RS flip-flop, the output of the four sets of the RS flip-flop of the two sets of ANDed signal of the output of the RS flip-flop, by taking the logical product signal of the output of the two sets of separate two pairs different from the RS flip-flop of the RS flip-flop, a jitter-free 90 ° In an encoder signal processing circuit comprising a jitter removal circuit that outputs a two-phase rectangular wave signal having different phases, and a counter that counts edges of the two-phase rectangular wave signal that is the output of the jitter removal circuit ,

When the sign of the difference of the count value with the stored previous times count value of the counter is determined to have changed by the inverse of the motor, the output adding +1 or -1 depending on the sign of the difference in the count value A hysteresis compensation method for an encoder signal processing circuit.

ゼロであれば今回のカウント値を記憶して補正は行わず、次回のカウント値との差分をとる操作を繰り返し、

前記差分がゼロでなければ、前回の差分と符号が違うか否かを判断し、

前記符号が違えば差分の符号に応じて、+1または−1を補正量として前記今回のカウント値に加えて出力する

ことを特徴とする請求項1記載のエンコーダ信号処理回路のヒステレシス補償方法。 Taking the difference of the current count value and the previous count value and determines whether the difference is zero or,

Correction and stores the current count value if the zero is not performed, repeat the operation Ru bet the difference between the next count value,

If the difference is not zero, determine whether the sign is different from the previous difference,

Depending on the code differential Different symbols, +1 or -1 hysteresis compensation method of an encoder signal processing circuit according to claim 1, characterized in that the pressure forte outputs the to the current count value as the correction amount.

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力する補償演算部を備えたことを特徴とするエンコーダ信号処理回路。And the rectangular wave signal of two different phases of 90 degrees phase encoder output by the rotation of the motor, an inverted signal of the rectangular wave signal four pairs of an input signal of the RS flip-flop, the output of the four sets of the RS flip-flop of the two sets of ANDed signal of the output of the RS flip-flop, by taking the logical product signal of the output of the two sets of separate two pairs different from the RS flip-flop of the RS flip-flop, a jitter-free 90 ° In an encoder signal processing circuit comprising a jitter removal circuit that outputs a two-phase rectangular wave signal having different phases, and a counter that counts edges of the two-phase rectangular wave signal that is the output of the jitter removal circuit ,

When the sign of the difference of the count value with the stored previous times count value of the counter is determined to have changed by the inverse of the motor, the output adding +1 or -1 depending on the sign of the difference in the count value An encoder signal processing circuit comprising a compensation calculation unit .

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは−1を加えて出力する手順を記録したことを特徴とするコンピュータプログラム用記録媒体。And the rectangular wave signal of two different phases of 90 degrees phase encoder output by the rotation of the motor, an inverted signal of the rectangular wave signal four pairs of an input signal of the RS flip-flop, the output of the four sets of the RS flip-flop of the two sets of ANDed signal of the output of the RS flip-flop, by taking the logical product signal of the output of the two sets of separate two pairs different from the RS flip-flop of the RS flip-flop, a jitter-free 90 ° In an encoder signal processing circuit comprising a jitter removal circuit that outputs a two-phase rectangular wave signal having different phases, and a counter that counts edges of the two-phase rectangular wave signal that is the output of the jitter removal circuit ,

When the sign of the difference of the count value with the stored previous times count value of the counter is determined to have changed by the inverse of the motor, the output adding +1 or -1 depending on the sign of the difference in the count value A recording medium for a computer program in which a procedure is recorded.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000011070A JP4385268B2 (en) | 2000-01-19 | 2000-01-19 | Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000011070A JP4385268B2 (en) | 2000-01-19 | 2000-01-19 | Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001201367A JP2001201367A (en) | 2001-07-27 |

| JP2001201367A5 JP2001201367A5 (en) | 2006-12-28 |

| JP4385268B2 true JP4385268B2 (en) | 2009-12-16 |

Family

ID=18538987

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000011070A Expired - Lifetime JP4385268B2 (en) | 2000-01-19 | 2000-01-19 | Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4385268B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100368777C (en) * | 2004-10-15 | 2008-02-13 | 中国科学院长春光学精密机械与物理研究所 | Electronic zeroing method for photoelectric rotary encoder |

-

2000

- 2000-01-19 JP JP2000011070A patent/JP4385268B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001201367A (en) | 2001-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4859903B2 (en) | Moving direction detection device | |

| JP4385268B2 (en) | Encoder signal processing circuit, hysteresis compensation method thereof, and recording medium for computer recording the method | |

| US5198750A (en) | Extremely wide range frequency measurement method | |

| JPH06118090A (en) | Speed detector | |

| US5394102A (en) | Non-repeatable run-out measuring instrument using encoder signals based upon the back EMF of a motor as trigger signals | |

| JP3050027B2 (en) | Encoder pulse count circuit | |

| JP2000078892A (en) | Driving apparatus of stepping motor | |

| JPH04346069A (en) | Speed signal generating circuit | |

| JPH04285815A (en) | Position counter circuit of rotary encoder | |

| JP3248143B2 (en) | Digital AC servo device | |

| JP4035751B2 (en) | Encoder signal processing circuit and signal processing method thereof | |

| JP3302864B2 (en) | Motor rotation speed detection circuit | |

| JP3509775B2 (en) | Incremental signal processing method and apparatus | |

| JP3195801B2 (en) | Digital counter device | |

| JP2968418B2 (en) | Speed detector | |

| JPH05223594A (en) | Transfer information detector using encoder | |

| JP2000213925A (en) | Position detector | |

| JPS62171480A (en) | Speed controller | |

| JP2523207Y2 (en) | Speed detector | |

| JP2874797B2 (en) | Control device for vibration actuator | |

| KR940022059A (en) | Encoder Output Error Compensation Method | |

| JPH09145734A (en) | Speed detection device | |

| JP3487697B2 (en) | Interpolation processing circuit | |

| JPS61262315A (en) | Signal processing circuit of two-phase pulse signal | |

| JP2725463B2 (en) | Servo motor speed detector |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061113 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061113 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090814 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090903 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090916 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121009 Year of fee payment: 3 |