JP4366731B2 - Method for manufacturing electro-optical device and method for manufacturing drive substrate for electro-optical device - Google Patents

Method for manufacturing electro-optical device and method for manufacturing drive substrate for electro-optical device Download PDFInfo

- Publication number

- JP4366731B2 JP4366731B2 JP25637698A JP25637698A JP4366731B2 JP 4366731 B2 JP4366731 B2 JP 4366731B2 JP 25637698 A JP25637698 A JP 25637698A JP 25637698 A JP25637698 A JP 25637698A JP 4366731 B2 JP4366731 B2 JP 4366731B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- single crystal

- tft

- gate

- crystal silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【0001】

【発明の属する技術分野】

本発明は、電気光学装置の製造方法及び電気光学装置用の駆動基板の製造方法に関し、特に絶縁基板上にグラフォエピタキシャル成長させた単結晶シリコン層を能動領域に用いるトップゲート型の薄膜絶縁ゲート型電界効果トランジスタ(以降、トップゲート型MOSTFTと呼ぶ。尚、トップゲート型にはスタガー型又はコプラナー型が含まれる。)と受動領域を有する液晶表示装置などに好適な方法に関するものである。

【0002】

【従来の技術】

アクティブマトリクス型の液晶表示装置として、アモルファスシリコンをTFTに用いた表示部と外付け駆動回路用ICとを有するものや、固相成長法による多結晶シリコンをTFTに用いた表示部と駆動回路との一体型(特開平6−242433号公報)、エキシマレーザーアニールを行った多結晶シリコンをTFTに用いた表示部と駆動回路との一体型(特開平7−131030号公報)などが知られている。

【0003】

【発明が解決しようとする課題】

しかし、上記した従来のアモルファスシリコンTFTは、生産性は良いが、電子移動度は0.5〜1.0cm2 /v・sec前後と低いために、pチャンネルのMOSTFT(以降、pMOSTFTと呼ぶ。)を作ることができない。従って、pMOSTFTを用いた周辺駆動部を表示部と同じガラス基板上に形成できないため、ドライバICは外付けとなり、TAB方式等により実装されるので、コストダウンが難しい。また、このために、高精細化には限界がある。更に、電子移動度は0.5〜1.0cm2 /v・sec前後と低いので、十分なオン電流がとれず、表示部に用いた場合、トランジスタサイズが必然的に大きくなり、画素の高開口率に不利である。

【0004】

また、上記した従来の多結晶シリコンTFTの電子移動度は70〜100cm2 /v・secで高精細化にも対応できるので、最近は駆動回路一体型の多結晶シリコンTFTを用いたLCD(液晶表示装置)が注目されている。しかし、15インチ以上の大型LCDの場合は、多結晶シリコンの電子移動度は70〜100cm2 /v・secであるため、駆動能力が不足し、結局、外付けの駆動回路用ICが必要となっている。

【0005】

また、固相成長法により成膜された多結晶シリコンを用いるTFTでは、600℃以上で十数時間のアニールと、約1000℃の熱酸化によるゲートSiO2 の形成が必要なために、半導体製造装置を採用せざるを得ない。そのために、ウエーハサイズ8〜12インチφが限界であり、高耐熱性で高価な石英ガラスの採用が余儀なくされ、コストダウンが難しい。従って、EVFやデータ/AVプロジェクタ用途に限定されている。

【0006】

更に、上記した従来のエキシマレーザーアニールによる多結晶シリコンTFTでは、エキシマレーザー出力の安定性、生産性、大型化による装置価格の上昇、歩留/品質低下等の問題が山積している。

【0007】

特に、1m角等の大型ガラス基板になると、前記の問題が拡大し、ますます性能/品質向上とコストダウンが難しくなる。

【0008】

本発明の目的は、特に周辺駆動回路部において、高い電子/正孔移動度の単結晶シリコン薄膜を比較的低温でかつ均一に成膜して、高性能ドライバ内蔵のアクティブマトリクス基板と、これを用いた表示用薄膜半導体装置等の電気光学装置の製造を可能とし、高いスイッチング特性と低リーク電流を有するLDD構造(Lightly doped drain 構造)のnチャンネルのMOSTFT(以降、nMOSTFTと呼ぶ。)又はpMOSTFT又は高い駆動能力の相補型薄膜絶縁ゲート電界効果トランジスタ(以降、cMOSTFTと呼ぶ。)の表示部と、cMOSTFT又はnMOSTFT又はpMOSTFT、或いはこれらの混在からなる周辺駆動回路とを一体化した構成を可能とし、高画質、高精細、狭額縁、高効率、大画面の表示パネルを実現することができ、しかも歪点が比較的低い大型のガラス基板であっても使用でき、生産性が高く、高価な製造設備が不要であってコストダウンが可能となり、更に、しきい値調整が容易であって低抵抗化による高速動作と大画面化を可能にすることにある。

【0009】

【課題を解決するための手段】

即ち、本発明は、画素電極(例えばマトリクス状に配列された複数の画素電極:以下、同様)が配された表示部と、この表示部の周辺に配された周辺駆動回路部とを第1の基板(即ち、駆動用の基板:以下、同様)上に有し、この第1の基板と第2の基板(即ち、対向基板:以下、同様)との間に液晶などの所定の光学材料を介在させてなる電気光学装置、及びこの電気光学装置用の駆動基板のそれぞれの製造方法において、

前記第1の基板の一方の面に段差を形成する工程と、

前記段差による凹部を含む前記第1の基板上に、シリコンを含有する後述の低融点金

属の溶融液層を塗布によって形成する工程と、

次いで冷却処理(望ましくは徐冷処理)によって前記溶融液層の前記シリコンを前記

段差をシードとしてグラフォエピタキシャル成長させ、単結晶シリコン層を析出させる

工程と、

この単結晶シリコン層に所定の処理を施して能動素子及び受動素子のうちの少なくと

も能動素子を形成する工程(例えば、前記単結晶シリコン層をチャンネル領域、ソース

領域及びドレイン領域とし、前記チャンネル領域の上部にゲート絶縁膜及びゲート電極

からなるゲート部、更にはソース及びドレイン電極を有するトップゲート型の薄膜トラ

ンジスタ(特にMOSTFT:以下、同様)を能動素子として形成する工程)と

を有することを特徴とする電気光学装置、及びこの電気光学装置用の駆動基板のそれぞれの製造方法に係るものである。なお、本発明において、上記能動素子は薄膜トランジスタやその他のダイオード等の素子を含む概念であり、上記受動素子は抵抗などを含む概念である(以下、同様)。その代表例としての薄膜トランジスタとは、電界効果トランジスタ(FET)(これにはMOS型と接合型があるが、いずれでもよい。)とバイポーラトランジスタとがあるが、本発明はいずれのトランジスタにも適用できる(以下、同様)。また、上記受動素子は抵抗、インダクタンス、キャパシタンス等を含む概念であり、例えばシリコンナイトライド(以後、SiNと呼ぶ。)等の高誘電体膜を低抵抗化した前記単結晶シリコン層(電極)で挟み込んで形成したキャパシタンスがある。

【0010】

本発明によれば、シリコンなどを溶解したインジウムなどの低融点金属の溶融液を塗布し、この溶融液から、基板に形成した上記段差をシードにしたグラフォエピタキシャル成長により単結晶シリコン薄膜などの単結晶半導体薄膜を形成し、これをアクティブマトリクス基板などの駆動基板の周辺駆動回路のトップゲート型MOSTFTや表示部−周辺駆動回路一体型のLCDなどの電気光学装置の周辺駆動回路のトップゲート型MOSTFTなどの能動素子や、抵抗、インダクタンス、キャパシタンス等の受動素子のうちの少なくとも能動素子に用いているので、次の(A)〜(F)に示す顕著な作用効果を得ることができる。

【0011】

(A)所定形状/寸法の段差を基板上に形成し、その段差の底辺の角(底角)をシードとしてグラフォエピタキシャル成長させることにより、540cm2 /v・sec以上の高い電子移動度の単結晶シリコン薄膜などの単結晶半導体層が得られるので、高性能ドライバ内蔵の表示用薄膜半導体装置などの電気光学装置の製造が可能となる。この場合、断面において底面に対し側面が直角状若しくは下端側へ望ましくは90°以下の底角をなすように傾斜状となるような凹部として前記段差が形成されるのがよい。

【0012】

(B)特にこの単結晶シリコン薄膜は、従来のアモルファスシリコン薄膜や多結晶シリコン薄膜に比べて、単結晶シリコン基板並の高い電子及び正孔移動度を示すので、これによる単結晶シリコントップゲート型MOSTFTは、高いスイッチング特性〔望ましくは更に、電界強度を緩和して低リーク電流化するLDD(Lightly doped drain) 構造〕を有するnMOS又はpMOSTFT又はcMOSTFTからなる表示部と、高い駆動能力のcMOS、又はnMOS、pMOSTFT又はこれらの混在からなる周辺駆動回路部とを一体化した構成が可能となり、高画質、高精細、狭額縁、高効率、大画面の表示パネルが実現する。特に、多結晶シリコンではLCD用TFTとして、高い正孔移動度のpMOSTFTは形成し難いが、本発明による単結晶シリコン薄膜は正孔でも十分に高い移動度を示すため、電子と正孔をそれぞれ単独でも、或いは双方を組み合せて駆動する周辺駆動回路を作製でき、これをnMOS又はpMOS又はcMOSのLDD構造の表示部用TFTと一体化したパネルを実現できる。また、小型〜中型パネルの場合には、周辺の一対の垂直駆動回路の一方を省略できる可能性がある。

【0013】

(C)そして、上記した低融点金属の溶融液は低温(例えば350℃)で調製し、それより少し高いだけの温度に加熱した基板上に塗布で形成できるから、比較的低温(例えば350〜400℃)でシリコン単結晶膜を均一に形成することができる。従って、歪点の比較的低いガラス基板や耐熱性有機基板などの入手し易く、低コストで物性も良好な基板を用いることができ、また基板の大型化も可能となる。

【0014】

(D)固相成長法の場合のような中温で長時間(約600℃、十数時間)のアニールや、エキシマレーザーアニールが不要となるから、生産性が高く、高価な製造設備が不要でコストダウンが可能となる。

【0015】

(E)このグラフォエピタキシャル成長では、基板の加熱温度、溶融液の組成比、溶融液温度、冷却速度等の調整により、広範囲のP型不純物濃度と高移動度の単結晶シリコン薄膜が容易に得られるので、Vth(しきい値)調整が容易であり、低抵抗化による高速動作と大画面化が可能である。

【0016】

(F)また、シリコン含有低融点金属溶融液層の成膜時に、3族又は5族の不純物元素(ボロン、リン、アンチモン、ひ素、ビスマス、アルミニウムなど)を別途適量ドープしておけば、成長する単結晶シリコンエピタキシャル成長層の不純物種及び/又はその濃度、即ちP型/N型の導電型及び/又はキャリア濃度を任意に制御することができる。

【0017】

【発明の実施の形態】

本発明においては、前記段差が、断面において底面に対し側面が直角状若しくは下端側へ望ましくは90°以下の底角をなすように傾斜状となるような凹部として、絶縁基板又はその上の拡散バリア、例えばSiNなどの膜(或いはこれらの双方)に形成され、この段差が前記単結晶シリコン層のグラフォエピタキシャル成長時のシードとなっているのがよい。この段差は、前記能動素子、例えば薄膜トランジスタの前記チャンネル領域、前記ソース領域及び前記ドレイン領域で形成される素子領域の少なくとも一辺に沿って形成されているのがよい。また、前記受動素子、例えば抵抗が形成される素子領域の少なくとも一辺に沿って形成されているのがよい。

【0018】

この場合、前記MOSTFTの如き第1の薄膜トランジスタを前記段差による基板凹部内に設けてよいが、凹部外、或いはこれらの双方において基板上に設けてもよい。

【0019】

前記段差をリアクティブイオンエッチングなどのドライエッチングによって形成し、シリコンを例えば2.0重量%〜0.005重量%、例えば1重量%含有する低融点金属の溶融液を加熱された絶縁基板に塗布し、所定時間(数分〜数10分)保持した後、前記冷却処理を行うのがよい。これによって、厚さ数μm〜0.005μm、例えば1μmの単結晶シリコン膜を得ることができる。

【0020】

また、前記基板として絶縁基板、例えばガラス基板、耐熱性有機基板を使用し、前記低融点金属としてインジウム、ガリウム、スズ、ビスマス、鉛、亜鉛、アンチモン及びアルミニウムからなる群より選ばれた少なくとも1種を使用することができる。

【0021】

この場合、前記低融点金属としてインジウムを使用するときには前記溶融液を850〜1100℃、望ましくは900〜950℃に加熱された前記絶縁基板に塗布し、前記低融点金属としてインジウム・ガリウム又はガリウムを使用するときには前記溶融液を300〜1100℃、望ましくは350〜600℃又は400〜1100℃、望ましくは420〜600℃に加熱された前記絶縁基板に塗布することができる。基板の加熱は、電気炉やランプ等を用いて基板全体を均一に加熱する方法の他、光レーザー、電子ビーム等によって、所定の場所のみを局部的に加熱する方法も可能である。

【0022】

このようにシリコンを含有する低融点金属は、図10に示す状態図から明らかなように、低融点金属の割合に応じて融点が低下する。インジウムを用いるときには、シリコンを含有(例えば1重量%含有)するインジウム溶融液層を850〜1100℃の基板温度で形成するのは、1100℃程度までは基板として石英板ガラスを使用でき、1100℃〜850℃まではそれよりも耐熱性が低いガラス、例えば結晶化ガラスでも使用できることになる。ガリウムを用いるときにも、上記と同様の理由から、シリコンを含有(例えば1重量%含有)するガリウム溶融液層を400〜1100℃の基板温度で形成することができる。

【0023】

後者の場合(インジウム・ガリウム・シリコン又はガリウム・シリコンの場合)、基板として、比較的歪点の低いガラス基板や耐熱性有機基板を用い得るので、大型ガラス基板(例えば1m2 以上)上に半導体結晶層を作成することが可能であるが、このような基板は、安価で、薄板化が容易であり、長尺ロール化されたガラス板や耐熱性有機基板を作製できる。これを用いて、長尺ロール化ガラス板や耐熱性有機基板上に、上記手法により、グラフォエピタキシャル成長による単結晶シリコン薄膜を連続して又は非連続に作製することができる。

【0024】

上記の溶融液塗布式では一定時間(数分〜数十分)保持した後に徐冷するが、この他にも、ガラス基板を上記溶液に浸して、一定時間(数分〜数十分)保持した後、徐々に引き上げるディッピング方式や、溶融液中又は表面を適切な速度で移動させて徐冷するフローティング方式でもよい。溶融液の組成、温度、引き上げ速度によって、エピタキシャル成長層の厚さやキャリア不純物濃度を制御することができる。塗布式、ディッピング方式、フローティング方式等は、基板を連続又は断続送りして処理できるため、量産性も向上する。

【0025】

上記のように、歪点が低いガラスの上層へは、このガラス内部から、その構成元素 が拡散し易いので、これを抑える目的で、拡散バリア層の薄膜(例えばシリコンナイトライド:厚さ50〜200nm程度)を形成するのがよい。

【0026】

上記したシリコンを溶かした低融点金属から、徐冷によって、上記段差をシードとしてグラフォエピタキシャル成長により前記単結晶シリコン層を析出させた後に、この上の前記低融点金属の層を塩酸などで溶解除去し、しかる後に前記単結晶シリコン層に所定の処理を施して能動素子と受動素子を作製することができる。

【0027】

このように、冷却後に単結晶シリコン層の上に析出したインジウムなどの低融点金属薄膜は塩酸等を用いて溶解除去するが、インジウム等はシリコン層中に微量(1016atoms/cc程度)しか残留しないよう作成できるので、作成直後はP型の単結晶シリコン薄膜の半導体が作成される。従って、これはnMOSTFTの作製にとって都合が良い。しかし、適量のリン原子などのN型不純物を全面又は選択的にイオン注入することによって、全面又は選択的にN型の単結晶シリコン薄膜を作成することができるので、pMOSTFTも作成することができる。このため、cMOSTFTも作成できることになる。シリコン含有低融点金属の溶融液層の形成時に、溶解度が大きい3族又は5族の不純物元素(ボロン、リン、アンチモン、ひ素、ガリウム、ビスマスなど)を別途適量ドープしておけば、成長するシリコンエピタキシャル成長層の不純物種及び/又はその濃度、即ちP型/N型及び/又はキャリア濃度を任意に制御することができる。

【0028】

このように、基板上にグラフォエピタキシャル成長した前記単結晶シリコン層を周辺駆動回路の少なくとも一部を構成するトップゲート型MOSTFTのチャンネル領域、ソース領域及びドレイン領域に適用し、これら各領域の不純物種及び/又はその濃度を制御することができる。

【0029】

前記周辺駆動回路部及び前記表示部の薄膜トランジスタがnチャンネル型、pチャンネル型又は相補型の絶縁ゲート電界効果トランジスタを構成し、例えば相補型とnチャンネル型との組、相補型とpチャンネル型との組、又は相補型とnチャンネル型とpチャンネル型との組からなっていてよい。また、前記周辺駆動回路部及び/又は前記表示部の薄膜トランジスタの少なくとも一部がLDD(Lightly doped drain)構造を有しているのがよい。なお、LDD構造は、ゲート−ドレイン間のみならず、ゲート−ソース間にも、又はゲート−ソース間及びゲート−ドレイン間の両方に設けてもよい(これをダブルLDDと呼ぶ)。

【0030】

特に、前記MOSTFTは表示部では、nMOS又はpMOS又はcMOSのLDD型TFTを構成し、また周辺駆動回路部では、cMOS又はnMOS又はpMOSTFT又はこれらの混在を構成しているのがよい。

【0031】

そして、前記MOSTFTが前記段差による基板凹部内及び/又は基板凹部外の凹部付近に設けられてよい。

【0032】

この場合、前記第1の基板の一方の面上に段差が形成され、この段差を含む前記基板上に単結晶、多結晶又はアモルファスシリコン層が形成され、前記第2の薄膜トランジスタが、前記単結晶、多結晶又はアモルファスシリコン層をチャンネル領域、ソース領域及びドレイン領域とし、前記チャンネル領域の上部及び/又は下部にゲート部を有するトップゲート型、ボトムゲート型又はデュアルゲート型であってよい。この場合も、断面において底面に対し側面が直角状若しくは下端側へ望ましくは90°以下の底角をなすように傾斜状となるような凹部として上記と同様の前記段差が形成され、この段差が前記単結晶シリコン層のグラフォエピタキシャル成長時のシードとなる。

【0033】

前記第2の薄膜トランジスタは、前記第1の基板及び/又はその上の膜に形成された前記段差による基板凹部内及び/又は外に設けられ、前記第1の薄膜トランジスタと同様にグラフォエピタキシャル成長による単結晶シリコン層を用いて、そのソース、ドレイン、チャンネルの各領域が形成されてよい。

【0034】

この第2の薄膜トランジスタでも、上記したと同様、前記単結晶、多結晶又はアモルファスシリコン層の3族又は5族の不純物種及び/又はその濃度が制御されていたり、前記段差が、前記第2の薄膜トランジスタの前記チャンネル領域、前記ソース領域及び前記ドレイン領域で形成される素子領域の少なくとも一辺に沿って形成されていてよい。また、前記単結晶、多結晶又はアモルファスシリコン層下のゲート電極がその側端部にて台形状になっているのがよい。前記第1の基板と前記単結晶、多結晶又はアモルファスシリコン層との間に拡散バリア層が設けられていてよい。

【0035】

前記第1及び/又は第2の薄膜トランジスタのソース又はドレイン電極が前記段差を含む領域上に形成されているのがよい。

【0036】

前記第1の薄膜トランジスタが、チャンネル領域の上部及び/又は下部にゲート部を有するトップゲート型、ボトムゲート型又はデュアルゲート型の中から選ばれた少なくともトップゲート型からなり、かつ、表示部において画素電極をスイッチングするスイッチング素子が、前記トップゲート型、前記ボトムゲート型又は前記デュアルゲート型の第2の薄膜トランジスタであってよい。

【0037】

この場合、チャンネル領域の下部に設けられたゲート電極は耐熱性材料で形成されていたり、前記第2の薄膜トランジスタの上部ゲート電極と前記第1の薄膜トランジスタのゲート電極とが共通の材料で形成されていてよい。

【0038】

前記周辺駆動回路部において、前記第1の薄膜トランジスタ以外に、多結晶又はアモルファスシリコン層をチャンネル領域とし、このチャンネル領域の上部及び/又は下部にゲート部を有するトップゲート型、ボトムゲート型又はデュアルゲート型の薄膜トランジスタ、或いは前記単結晶シリコン層又は多結晶シリコン層又はアモルファスシリコン層を用いたダイオード、抵抗、キャパシタンス、インダクタンス素子などが設けられていてよい。

【0039】

前記周辺駆動回路部及び/又は前記表示部の薄膜トランジスタが、シングルゲート又はマルチゲートに構成されていてよい。

【0040】

前記周辺駆動回路部及び/又は前記表示部のn又はpチャンネル型の薄膜トランジスタがデュアルゲート型であるときには、上部又は下部ゲート電極が電気的にオープンとされるか或いは任意の負電圧(nチャンネル型の場合)又は正電圧(pチャンネル型の場合)が印加され、ボトムゲート型又はトップゲート型の薄膜トランジスタとして動作されるのがよい。

【0041】

前記周辺駆動回路部の薄膜トランジスタがnチャンネル型、pチャンネル型又は相補型の前記第1の薄膜トランジスタであり、前記表示部の薄膜トランジスタが、単結晶シリコン層をチャンネル領域とするときはnチャンネル型、pチャンネル型又は相補型であり、多結晶シリコン層をチャンネル領域とするときにはnチャンネル型、pチャンネル型又は相補型であり、アモルファスシリコン層をチャンネル領域とするときにはnチャンネル型、pチャンネル型又は相補型であってよい。

【0042】

本発明において、前記単結晶シリコン層の析出後、この単結晶シリコン層上にゲート絶縁膜とゲート電極とからなる上部ゲート部を形成し、この上部ゲート部をマスクとして前記単結晶シリコン層に3族又は5族の不純物元素を導入して前記チャンネル領域、前記ソース領域及び前記ドレイン領域を形成してよい。

【0043】

また、前記第2の薄膜トランジスタがボトムゲート型又はデュアルゲート型であるときは、前記チャンネル領域の下部に耐熱性材料からなる下部ゲート電極を設け、このゲート電極上にゲート絶縁膜を形成して下部ゲート部を形成した後、前記段差の形成工程を含めて前記第1の薄膜トランジスタと共通の工程を経て前記第2の薄膜トランジスタを形成することができる。この場合、前記第2の薄膜トランジスタの上部ゲート電極と前記第1の薄膜トランジスタのゲート電極とを共通の材料で形成することができる。

【0044】

また、前記下部ゲート部上に前記単結晶シリコン層を形成した後、この単結晶シリコン層に3族又は5族の不純物元素を導入し、ソース及びドレイン領域を形成した後に、活性化処理を行うことができる。

【0045】

また、前記単結晶シリコン層の形成後にレジストをマスクとして前記第1及び第2の薄膜トランジスタの各ソース及びドレイン領域を前記不純物元素のイオン注入で形成し、このイオン注入後に前記活性化処理を行い、ゲート絶縁膜の形成後に、前記第1の薄膜トランジスタのゲート電極と、必要あれば前記第2の薄膜トランジスタの上部ゲート電極とを形成してよい。

【0046】

前記薄膜トランジスタがトップゲート型のとき、前記単結晶シリコン層の形成後にレジストをマスクとして前記第1及び第2の薄膜トランジスタの各ソース及びドレイン領域を前記不純物元素のイオン注入で形成し、このイオン注入後に活性化処理を行い、しかる後に前記第1及び第2の薄膜トランジスタのゲート絶縁膜とゲート電極とからなる各ゲート部を形成することができる。

【0047】

或いは、前記薄膜トランジスタがトップゲート型のとき、前記単結晶シリコン層の形成後に前記第1及び第2の薄膜トランジスタの各ゲート絶縁膜と耐熱性材料からなる各ゲート電極とを形成して各ゲート部を形成し、これらのゲート部をマスクとして各ソース及びドレイン領域を前記不純物元素のイオン注入で形成し、このイオン注入後に活性化処理を行ってもよい。

【0048】

また、前記LDD構造を形成する際に用いたレジストマスクを残して、これを覆うレジストマスクを用いてソース領域及びドレイン領域形成用のイオン注入を行うことができる。

【0049】

また、前記基板が光学的に不透明又は透明であり、反射型、又は透過型の表示部用画素電極が設けられてよい。

【0050】

前記表示部が前記画素電極とカラーフィルタ層との積層構造を有していると、表示アレイ部上にカラーフィルタを作り込むことにより、表示パネルの開口率、輝度等の改善をはじめ、カラーフィルタ基板の省略、生産性改善等によるコストダウンが実現する。

【0051】

この場合、前記画素電極が反射電極であるときは、樹脂膜に最適な反射特性と視野角特性を得るための凹凸が形成され、この上に画素電極が設けられ、また前記画素電極が透明電極であるときは、透明平坦化膜によって表面が平坦化され、この平坦化面上に画素電極が設けられているのがよい。

【0052】

前記表示部は、前記MOSTFTによる駆動で発光又は調光を行うように構成され、例えば液晶表示装置(LCD)、エレクトロルミネセンス表示装置(EL)、電界放出型表示装置(FED)、発光ポリマー表示装置(LEPD)、発光ダイオード表示装置(LED)などとして構成されてよい。この場合、前記表示部に複数の前記画素電極がマトリクス状に配列され、これらの画素電極のそれぞれに前記スイッチング素子が接続されてよい。

【0053】

次に、本発明を好ましい実施の形態について更に詳細に説明する。

【0054】

<第1の実施の形態>

図1〜図13は、本発明の第1の実施の形態を示すものである。

【0055】

本実施の形態は、耐熱性基板に設けた上述した段差(凹部)をシードとしてインジウム・シリコン溶融液から単結晶シリコン層を高温グラフォエピタキシャル成長させ、これを用いてトップゲート型MOSTFTを構成したアクティブマトリクス反射型液晶表示装置(LCD)に関するものである。まず、この反射型LCDの全体のレイアウトを図11〜図13について説明する。

【0056】

図11に示すように、このアクティブマトリクス反射型LCDは、主基板1(これはアクティブマトリクス基板を構成する。)と対向基板32とをスペーサ(図示せず)を介して貼り合わせたフラットパネル構造からなり、両基板1−32間に液晶(ここでは図示せず)が封入されている。主基板1の表面には、マトリクス状に配列した画素電極29(又は41)と、この画素電極を駆動するスイッチング素子とからなる表示部、及びこの表示部に接続される周辺駆動回路部とが設けられている。

【0057】

表示部のスイッチング素子は、本発明に基づくnMOS又はpMOS又はcMOSでLDD構造のトップゲート型MOSTFTで構成される。また、周辺駆動回路部にも、回路要素として、本発明に基づくトップゲート型MOSTFTのcMOS又はnMOS又はpMOSTFT又はこれらの混在が形成されている。なお、一方の周辺駆動回路部はデータ信号を供給して各画素のTFTを水平ライン毎に駆動する水平駆動回路であり、また他方の周辺駆動回路部は各画素のTFTのゲートを走査ライン毎に駆動する垂直駆動回路であり、通常は表示部の両辺にそれぞれ設けられる。これらの駆動回路は、点順次アナログ方式、線順次デジタル方式のいずれも構成できる。

【0058】

図12に示すように、直交するゲートバスラインとデータバスラインの交差部に上記のTFTが配置され、このTFTを介して液晶容量(CLC)に画像情報を書き込み、次の情報がくるまで電荷を保持する。この場合、TFTのチャンネル抵抗だけで保持させるには十分ではないので、それを補うため液晶容量と並列に蓄積容量(補助容量)(CS )を付加し、リーク電流による液晶電圧の低下を補ってよい。こうしたLCD用TFTでは、画素部(表示部)に使用するTFTの特性と周辺駆動回路に使用するTFTの特性とでは要求性能が異なり、特に画素部のTFTではオフ電流の制御、オン電流の確保が重要な問題となる。このため、表示部には、後述の如きLDD構造のTFTを設けることによって、ゲート−ドレイン間に電界がかかりにくい構造としてチャンネル領域にかかる実効的な電界を低減させ、オフ電流を低減し、特性の変化も小さくできる。しかし、プロセス的には複雑になり、素子サイズも大きくなり、かつオン電流が低下するなどの問題も発生するため、それぞれの使用目的に合わせた最適設計が必要である。

【0059】

なお、使用可能な液晶としては、TN液晶(アクティブマトリクス駆動のTNモードに用いられるネマチック液晶)をはじめ、STN(スーパーツイステッドネマチック)、GH(ゲスト・ホスト)、PC(フェーズ・チェンジ)、FLC(強誘電性液晶)、AFLC(反強誘電性液晶)、PDLC(ポリマー分散型液晶)等の各種モード用の液晶を採用してよい。

【0060】

また、図13について周辺駆動回路の回路方式とその駆動方法の概略を述べる。駆動回路はゲート側駆動回路とデータ側駆動回路に分けられ、ゲート側、データ側ともにシフトレジスタを構成する必要がある。シフトレジスタは一般的に、pMOSTFTとnMOSTFTの両方を使用したもの(いわゆるCMOS回路)やいずれか一方のMOSTFTのみを使用したものがあるが、動作速度、信頼性、低消費電力の面でcMOSTFT又はCMOS回路が一般的である。

【0061】

走査側駆動回路はシフトレジスタとバッファから構成されており、水平走査期間と同期したパルスをシフトレジスタから各ラインに送る。一方、データ側駆動回路は点順次方式と線順次方式の二つの駆動方法があり、図示した点順次方式では回路の構成は比較的簡単であって、表示信号をアナログスイッチを通してシフトレジスタで制御しながら直接に各画素に書き込む。各画素に一水平走査時間内に順次書き込む(図中のR、G、Bは各色毎に画素を概略的に示している)。

【0062】

次に、図1〜図10について、本実施の形態によるアクティブマトリクス反射型LCDをその製造工程に従って説明する。但し、図1〜図6において、各図の左側は表示部の製造工程、右側は周辺駆動回路部の製造工程を示す。

【0063】

まず、図1の(1)に示すように、石英ガラス、結晶化ガラスなどの絶縁基板1の一主面において、少なくともTFT形成領域に、フォトレジスト2を所定パターンに形成し、これをマスクとして例えばCF4 プラズマのF+ イオン3を照射し、リアクティブイオンエッチング(RIE)などの汎用フォトリソグラフィ及びエッチング(フォトエッチング)によって基板1に段差4を適当な形状及び寸法で複数個形成する。この場合、絶縁基板1として石英ガラス、結晶化ガラス、セラミック等(但し、後述の透過型LCDでは、不透明のセラミック基板は使用できない。)の高耐熱性基板(8〜12インチφ、700〜800μm厚)が使用可能である。また、段差4は、後述の単結晶シリコンのグラフォエピタキシャル成長時のシードとなるものであって、深さd0.1μm、幅w5〜10μm、長さ(紙面垂直方向)10〜20μmであってよく、底辺と側面のなす角(底角)は直角とする。

【0064】

次いで、図1の(2)に示すように、フォトレジスト2の除去後に、シリコンを約1重量%含有するシリコン・インジウム溶融液6を、900〜930℃に加熱された基板1の段差4を含む全面に塗布する。或いは、溶融液中に基板1をディッピングするか、或いは、溶融液表面を徐々に移動させてフローティングさせる方法や、噴流式、超音波作用下での接触方式も可能である。

【0065】

次いで、基板1を数分〜数10分間保持した後、徐々に冷却する(ディッピングの場合は徐々に引き上げる)ことによって、インジウムに溶解していたシリコンは、段差4の底辺の角部をシード(種)として図2の(3)に示すようにグラフォエピタキシャル成長し、厚さ例えば0.1μm程度のP型単結晶シリコン層7として析出する。ディッピング法及びフローティング法では、溶融液組成、温度、引き上げ速度などの管理が容易であり、エピタキシャル成長層の厚みやP型キャリア不純物濃度を容易にコントロールできる。

【0066】

この場合、単結晶シリコン層7は(100)面が基板上にエピタキシャル成長したものであるが、これは、グラフォエピタキシャル成長と称される公知の現象によるものである。これについては、図8に示すように、非晶質基板(ガラス)1に上記の段差4の如き垂直な壁を作り、この上にエピタキシャル成長層を形成すると、図8(a)のようなランダムな面方位であったものが図8(b)のように(100)面が段差4の面に沿って結晶成長する。この単結晶粒の大きさは、温度・時間に比例して大きくなるが、温度・時間を低く、短くする時は、上記段差の間隔を短くしなければならない。また、上記段差の形状を図9(a)〜(f)のように種々に変えることによって、成長層の結晶方位を制御することができる。MOSトランジスタを作成する場合は、(100)面が最も多く採用されている。要するに、段差4の断面形状は、底辺角部の角度(底角)が直角をはじめ、上端から下端にかけて内向き又は外向きに傾斜していてもよく、結晶成長が生じ易い特定方向の面を有していればよい。段差4の底角は通常は直角又は90°以下が望ましく、その底面の角部は僅かな曲率を有しているのがよい。

【0067】

こうして、グラフォエピタキシャル成長によって基板1上に単結晶シリコン層7を析出させた後、図2の(4)のように、表面側に析出したインジウム膜6Aを塩酸、硫酸などによって溶解除去(この際、低級シリコン酸化膜が生成しないように後処理)し、単結晶シリコン層7をチャンネル領域とするトップゲート型MOSTFTの作製を行う。

【0068】

まず、上記のグラフォエピタキシャル成長による単結晶シリコン薄膜7はインジウムの含有によってP型化しているが、そのP型不純物濃度はばらついているので、pチャンネルMOSTFT部をフォトレジスト(図示せず)でマスクし、P型不純物イオン(例えばB+ )を10kVで2.7×1011atoms/cm2 のドーズ量でドーピングし、比抵抗を調整する。また、図2の(5)に示すように、pMOSTFT形成領域の不純物濃度制御のため、nMOSTFT部をフォトレジスト60でマスクし、N型不純物イオン(例えばP+ )65を10kVで1×1011atoms/cm2 のドーズ量でドーピングし、N型ウエル7Aを形成する。

【0069】

次いで、図3の(6)に示すように、単結晶シリコン薄膜層7の全面上に、プラズマCVD、高密度プラズマCVD、触媒CVD法等でシリコン酸化膜(以後SiO2 膜と呼ぶ。)(約200nm厚)とSiN膜(約100nm厚)をこの順に連続形成してゲート絶縁膜8を形成し、更に、モリブデン・タンタル(Mo・Ta)合金のスパッタ膜9(500〜600nm厚)を形成する。

【0070】

次いで、図3の(7)に示すように、汎用のフォトリソグラフィ技術により、表示領域のTFT部と、周辺駆動領域のTFT部とのそれぞれの段差領域(凹部内)にフォトレジストパターン10を形成し、連続したエッチングにより、(Mo・Ta)合金のゲート電極11とゲート絶縁膜(SiN/SiO2 )12とを形成し、単結晶シリコン薄膜層7を露出させる。(Mo・Ta)合金膜9は酸系エッチング液、SiNはCF4 ガスのプラズマエッチング、SiO2 はフッ酸系エッチング液で処理する。

【0071】

次いで、図3の(8)に示すように、周辺駆動領域のnMOS及びpMOSTFT全部と、表示領域のnMOSTFTのゲート部をフォトレジスト13でカバーし、露出したnMOSTFTのソース/ドレイン領域にリンイオン14を例えば20kVで5×1013atoms/cm2 のドーズ量でドーピング(イオン注入)して、N- 型層からなるLDD部15を自己整合的(セルフアライン)に形成する。

【0072】

次いで、図4の(9)に示すように、周辺駆動領域のpMOSTFT全部と、周辺駆動領域のnMOSTFTのゲート部と、表示領域のnMOSTFTのゲート及びLDD部とをフォトレジスト16でカバーし、露出した領域にリン又はひ素イオン17を例えば20kVで5×1015atoms/cm2 のドーズ量でドーピング(イオン注入)して、nMOSTFTのN+ 型層からなるソース部18及びドレイン部19とLDD部15とを形成する。

【0073】

次いで、図4の(10)に示すように、周辺駆動領域のnMOSTFT及び表示領域のnMOSTFTの全部とpMOSTFTのゲート部をフォトレジスト20でカバーし、露出した領域にボロンイオン21を例えば10kVで5×1015atoms/cm2 のドーズ量でドーピング(イオン注入)してpMOSTFTのP+ 層のソース部22及びドレイン部23を形成する。なお、この作業は、nMOS周辺駆動回路の場合はpMOSTFTが無いので、不要な作業である。

【0074】

次いで、図4の(11)に示すように、TFT、ダイオードなどの能動素子部や、抵抗、インダクタンスなどの受動素子部をアイランド化するため、フォトレジスト24を設け、周辺駆動領域及び表示領域のすべての能動素子部及び受動素子部以外の単結晶シリコン薄膜層を汎用フォトリソグラフィ及びエッチング技術で除去する。エッチング液はフッ酸系である。

【0075】

次いで、図5の(12)に示すように、プラズマCVD、高密度プラズマCVD、触媒CVD法等により、SiO2 膜(約200nm厚)及びリンシリケートガラス(PSG)膜(約300nm厚)をこの順に全面に連続形成して保護膜25を形成する。

【0076】

そして、この状態で単結晶シリコン層を活性化処理する。この活性化においてハロゲン等のランプアニール条件は約1000℃、約10秒程度であり、これに耐えるゲート電極材が必要であるが、高融点のMo・Ta合金は適している。このゲート電極材は従って、ゲート部のみならず配線として広範囲に亘って引き廻して設けることができる。なお、ここでは高価なエキシマレーザーアニールは使用しないが、仮に利用するとすれば、その条件はXeCl(308nm波長)で全面、又は能動素子部及び受動素子部のみの選択的な90%以上のオーバーラップスキャンニングが望ましい。

【0077】

次いで、図5の(13)に示すように、汎用フォトリソグラフィ及びエッチング技術により、周辺駆動回路の全TFTのソース/ドレイン部、及び表示用TFTのソース部のコンタクト用窓開けを行う。

【0078】

そして、全面に500〜600nm厚のアルミニウム又はアルミニウム合金、例えば1%Si入りアルミニウム又は1〜2%銅入りアルミニウム、銅等のスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、周辺駆動回路及び表示部のすべてのTFTのソース電極26と周辺駆動回路部のドレイン電極27を形成すると同時に、データライン及びゲートラインを形成する。その後に、フォーミングガス(N2 +H2 )中、約400℃/1hで、シンター処理する。

【0079】

次いで、図5の(14)に示すように、プラズマCVD、高密度プラズマCVD、触媒CVD法等により、PSG膜(約300nm厚)及びSiN膜(約300nm厚)からなる絶縁膜36を全面に形成する。次いで、表示用TFTのドレイン部のコンタクト用窓開けを行う。なお、画素部のSiO2 、PSG及びSiN膜は除去する必要はない。

【0080】

反射型液晶表示装置の基本的要件としては、液晶パネルの内部に入射光を反射させる機能と散乱させる機能を合わせ持たなければならない。これは、ディスプレイに対する観察者の方向はほぼ決まっているが、入射光の方向が一義的に決められないためである。このため、任意の方向に点光源が存在することを想定して反射板の設計を行う必要がある。そこで、図6の(15)に示すように、全面に、スピンコート等で2〜3μm厚みの感光性樹脂膜28を形成し、図6の(16)に示すように、汎用フォトリソグラフィ及びエッチング技術により、少なくとも画素部に最適な反射特性と視野角特性を得るための凹凸形状パターンを形成し、リフローさせて凹凸粗面28Aからなる反射面下部を形成する。同時に表示用TFTのドレイン部のコンタクト用の樹脂窓開けを行う。

【0081】

次いで、図6の(17)に示すように、全面に400〜500nm厚のアルミニウム又は1%Si入りアルミニウム等のスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、画素部以外のアルミニウム膜等を除去し、表示用TFTのドレイン部19と接続した凹凸形状のアルミニウム等の反射部29を形成する。これは表示用の画素電極として用いられる。その後に、フォーミングガス中、約300℃/1hでシンター処理し、コンタクトを十分にする。なお、反射率を高めるために、アルミニウム系に代えて銀又は銀合金を使用してもよい。

【0082】

以上のようにして、段差4を高温グラフォエピタキシャル成長のシードとして単結晶シリコン層7を形成し、この単結晶シリコン層7を用いた表示部及び周辺駆動回路部にそれぞれ、トップゲート型のnMOSLDD−TFT、pMOSTFT及びnMOSTFTで構成するCMOS回路を作り込んだ表示部−周辺駆動回路部一体型のアクティブマトリクス基板30を作製することができる。

【0083】

次に、このアクティブマトリクス基板(駆動基板)30を用いて、反射型液晶表示装置(LCD)を製造する方法を図7について説明する。以降では、このアクティブマトリクス基板をTFT基板と呼称する。

【0084】

このLCDの液晶セルを面面組立で作製する場合(2インチサイズ以上の中/大型液晶パネルに適している。)、まずTFT基板30と、全面ベタのITO(Indium tin oxide)電極31を設けた対向基板32の素子形成面に、ポリイミド配向膜33、34を形成する。このポリイミド配向膜はロールコート、スピンコート等により50〜100nm厚に形成し、180℃/2hで硬化キュアする。

【0085】

次いで、TFT基板30と対向基板32をラビング、又は偏光紫外線の光配向処理する。ラビングバフ材にはコットンやレーヨン等があるが、バフかす(ゴミ)やリタデーション等の面からはコットンの方が安定している。光配向は非接触の線型偏光紫外線照射による液晶分子の配向技術である。なお、配向には、ラビング以外にも、偏光又は非偏光を斜め入射させることによって高分子配向膜を形成することができる(このような高分子化合物は、例えばアゾベンゼンを有するポリメチルメタクリレート系高分子等がある)。

【0086】

次いで、洗浄後に、TFT基板30側にはコモン剤塗布、対向基板32側にはシール剤塗布する。ラビングバフかす除去のために、水、又はIPA(イソプロピルアルコール)洗浄する。コモン剤は導電性フィラーを含有したアクリル、又はエポキシアクリレート、又はエポキシ系接着剤であってよく、シール剤はアクリル、又はエポキシアクリレート、又はエポキシ系接着剤であってよい。加熱硬化、紫外線照射硬化、紫外線照射硬化+加熱硬化のいずれも使用できるが、重ね合せの精度と作業性からは紫外線照射硬化+加熱硬化タイプが良い。

【0087】

次いで、対向基板32側に所定のギャップを得るためのスペーサを散布し、TFT基板30と所定の位置で重ね合せる。対向基板32側のアライメントマークとTFT基板30側のアライメントマークとを精度よく合わせた後に、紫外線照射してシール剤を仮硬化させ、その後に一括して加熱硬化する。

【0088】

次いで、スクライブブレークして、TFT基板30と対向基板32を重ね合せた単個の液晶パネルを作成する。

【0089】

次いで、液晶35を両基板30−32間のギャップ内に注入し、注入口を紫外線接着剤で封止後に、IPA洗浄する。液晶の種類はなんでも良いが、例えばネマティック液晶を用いる高速応答のTN(ツイストネマティック)モードが一般的である。

【0090】

次いで、加熱急冷処理して、液晶35を配向させる。

【0091】

次いで、TFT基板30のパネル電極取り出し部にフレキシブル配線を異方性導電膜の熱圧着で接続し、更に対向基板32に偏光板を貼合わせる。

【0092】

また、液晶パネルの面単組立の場合(2インチサイズ以下の小型液晶パネルに適している。)、上記と同様、TFT基板30と対向基板32の素子形成面に、ポリイミド配向33、34を形成し、両基板をラビング、又は非接触の線型偏光紫外線光の配向処理する。

【0093】

次いで、TFT基板30と対向基板32をダイシング又はスクライブブレークで単個に分割し、水又はIPA洗浄する。TFT基板30にはコモン剤塗布、対向基板32にはスペーサ含有のシール剤塗布し、両基板を重ね合せる。これ以降のプロセスは上記に準ずる。

【0094】

上記した反射型LCDにおいて、対向基板32はCF(カラーフィルタ)基板であって、カラーフィルタ層46をITO電極31下に設けたものである。対向基板32側からの入射光は反射膜29で効率良く反射されて対向基板32側から出射する。

【0095】

他方、TFT基板30として、図7のような上記した基板構造以外に、TFT基板30にカラーフィルタを設けたオンチップカラーフィルタ(OCCF)構造のTFT基板とするときには、対向基板32にはITO電極がベタ付け(又はブラックマスク付きのITO電極がベタ付け)される。

【0096】

なお、図12に示した補助容量CS を画素部に組み込む場合は、上記した基板1上に設けた誘電体層(図示せず)を単結晶シリコンのドレイン領域19と接続すればよい。

【0097】

以上に説明したように、本実施の形態によれば、次の如き顕著な作用効果が得られる。

【0098】

(a)所定形状/寸法の段差4を基板1に形成し、その段差の底辺の角をシードとして高温グラフォエピタキシャル成長(但し、成長時の加熱温度は900〜930℃と比較的低温)させることにより、540cm2 /v・sec以上の高い電子移動度の単結晶シリコン薄膜7が得られるので、高性能ドライバ内蔵のLCDの製造が可能となる。

【0099】

(b)この単結晶シリコン薄膜は、従来のアモルファスシリコン薄膜や多結晶シリコン薄膜に比べて、単結晶シリコン基板並の高い電子及び正孔移動度を示すので、これによる単結晶シリコントップゲート型TFTは、高いスイッチング特性と低リーク電流のLDD構造を有するnMOS又はpMOS又はcMOSTFTの表示部と、高い駆動能力のcMOS、nMOS又はpMOSTFT又はこれらの混在からなる周辺駆動回路部とを一体化した構成が可能となり、高画質、高精細、狭額縁、大画面、高効率の表示パネルが実現する。この単結晶シリコン薄膜7は十分に高い正孔移動度を示すため、電子と正孔をそれぞれ単独でも、或いは双方を組み合せて駆動する周辺駆動回路を作製でき、これをnMOS又はpMOS又はcMOSのLDD構造の表示用TFTと一体化したパネルを実現できる。また、小型〜中型パネルの場合には、周辺の一対の垂直駆動回路の一方を省略できる可能性がある。

【0100】

(c)そして、上記したグラフォエピタキシャル成長時の加熱処理温度は930℃以下が可能であるから、絶縁基板上に比較的低温(例えば900〜930℃以下)で単結晶シリコン膜7を均一に形成することができる。なお、基板としては、石英ガラスや結晶化ガラス、セラミック基板などが使用可能である。

【0101】

(d)固相成長法の場合のような中温で長時間のアニールや、エキシマレーザーアニールが不要となるから、生産性が高く、高価な製造設備が不要でコストダウンが可能となる。

【0102】

(e)この高温グラフォエピタキシャル成長では、インジウム・シリコン組成比、基板加熱温度、溶融液温度、冷却速度等の調整により、広範囲のP型不純物濃度と高移動度の単結晶シリコン薄膜が容易に得られるので、Vth(しきい値)調整が容易であり、低抵抗化による高速動作が可能である。

【0103】

(f)表示アレイ部上にカラーフィルタを作り込めば、表示パネルの開口率、輝度等の改善をはじめ、カラーフィルタ基板の省略、生産性改善等によるコストダウンが実現する。

【0104】

<第2の実施の形態>

図14〜図16について、本発明の第2の実施の形態を説明する。

【0105】

本実施の形態は、上述の第1の実施の形態と同様のトップゲート型TFTを表示部及び周辺駆動回路部に有するが、上述の第1の実施の形態とは異なって、透過型LCDに関するものである。即ち、図1の(1)から図5の(14)に示す工程までは同様であるが、その工程後に、図14の(15)に示すように、絶縁膜25、36に表示用TFTのドレイン部コンタクト用の窓開け19を行うと同時に、透過率向上のために画素開口部の不要なSiO2 、PSG及びSiN膜を除去する。なお、不透明なセラミック基板は使用できない。

【0106】

次いで、図14の(16)に示すように、全面にスピンコート等で2〜3μm厚の感光性アクリル系透明樹脂の平坦化膜28Bを形成し、汎用フォトリソグラフィにより、表示用TFTのドレイン側の透明樹脂28Bの窓開けを行い、所定条件で硬化させる。

【0107】

次いで、図14の(17)に示すように、全面に130〜150nm厚のITOスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、表示用TFTのドレイン部19とコンタクトしたITO透明電極41を形成する。そして、熱処理(フォーミングガス中、200〜250℃/1h)により、表示用TFTのドレインとITOのコンタクト抵抗の低減化とITO透明度の向上を図る。

【0108】

そして、図15に示すように、対向基板32と組み合わせ、上述の第1の実施の形態と同様にして透過型LCDを組み立てる。但し、TFT基板側にも偏光板を貼り合わせる。この透過型LCDでは、実線のように透過光が得られるが、一点鎖線のように対向基板32側からの透過光が得られるようにもできる。

【0109】

この透過型LCDの場合、次のようにしてオンチップカラーフィルタ(OCCF)構造とオンチップブラック(OCB)構造を作製することができる。

【0110】

即ち、図1の(1)〜図5の(13)までの工程は上記の工程に準じて行うが、その後、図16の(14)に示すように、PSG/SiO2 の絶縁膜25のドレイン部も窓開けしてドレイン電極用のアルミニウム埋込み層41Aを形成した後、SiN/PSGの絶縁膜36を形成する。

【0111】

次いで、図16の(15)に示すように、R、G、Bの各色を各セグメント毎に顔料分散したフォトレジスト61を所定厚さ(1〜1.5μm)で形成した後、図16の(16)に示すように、汎用フォトリソグラフィ技術で所定位置(各画素部)のみを残すパターニングで各カラーフィルタ層61(R)、61(G)、61(B)を形成する(オンチップカラーフィルタ構造)。この際、ドレイン部の窓開けも行う。なお、不透明なセラミック基板や低透過率のガラス及び耐熱性樹脂基板は使用できない。

【0112】

次いで、図16の(16)に示すように、表示用TFTのドレインに連通するコンタクトホールに、カラーフィルタ層上にかけてブラックマスク層となる遮光層43を金属のパターニングで形成する。例えば、スパッタ法により、モリブデンを200〜250nm厚で成膜し、表示用TFTを覆って遮光する所定の形状にパターニングする(オンチップブラック構造)。

【0113】

次いで、図16の(17)に示すように、透明樹脂の平坦化膜28Bを形成し、更にこの平坦化膜に設けたスルーホールにITO透明電極41を遮光層43に接続するように形成する。

【0114】

このように、表示アレイ部上に、カラーフィルタ61やブラックマスク43を作り込むことにより、液晶表示パネルの開口率を改善し、またバックライトも含めたディスプレイモジュールの低消費電力化が実現する。

【0115】

<第3の実施の形態>

本発明の第3の実施の形態を説明する。

【0116】

本実施の形態は、歪点の低いガラス基板に上述した段差(凹部)を形成し、これをシードとしてインジウム・ガリウム・シリコン又はガリウム・シリコン溶融液から単結晶シリコン層を低温グラフォエピタキシャル成長させ、これを用いてトップゲート型MOSTFTを構成したアクティブマトリクス反射型液晶表示装置(LCD)に関するものである。

【0117】

即ち、本実施の形態では、上述の第1の実施の形態と比べて、図1の(1)に示す工程で、基板1として、歪点又は最高使用温度が例えば600℃程度と低いガラス、例えばホウケイ酸ガラスやアルミノケイ酸ガラスなどのガラス基板を用いる。これは、安価でかつ大型化が容易であり、薄板大型化(例えば500×600×0.1〜1.1mm厚)すればロール化/長尺化が可能である。もちろん、石英基板や結晶化ガラス基板も採用することができる。

【0118】

そして、上述と同様に段差4を形成した後、図1の(2)に示す工程で、シリコンを1重量%含有するシリコン・インジウム・ガリウム溶融液又はシリコン・ガリウム溶融液を段差4を含む全面に塗布する。このとき基板1は約300〜600℃又は420〜600℃に加熱しておく。

【0119】

次いで、基板1を数分〜数10分間保持した後、徐々に冷却する(ディッピングの場合は徐々に引き上げるが、フローティングの場合は溶融液面に沿って徐々に移動させる。)ことによって、インジウム・ガリウム又はガリウムに溶解していたシリコンは、段差4の底辺の角部をシード(種)として図2の(3)に示すようにグラフォエピタキシャル成長し、厚さ例えば0.1μm程度のP型単結晶シリコン層7として析出する。ディッピング法やフローティング法では、溶液組成、温度、引き上げ速度などの管理が容易であり、エピタキシャル成長層の厚みやP型不純物濃度を容易にコントロールできる。

【0120】

この場合、単結晶シリコン層7は上述したと同様に(100)面が基板上にエピタキシャル成長したものであるが、上記段差の形状を図9(a)〜(f)のように種々に変えることによって、成長層の結晶方位を制御することができる。

【0121】

こうして、低温グラフォエピタキシャル成長によって基板1上に単結晶シリコン層7を析出させた後、図2の(4)のように、表面側のインジウム・ガリウム(又はガリウム)を塩酸、硫酸などによって溶解除去する。

【0122】

しかる後、単結晶シリコン層7を用いて上述の第1の実施の形態と同様にして表示部及び周辺駆動回路部にトップゲート型のMOSTFTの作製を行う。また図7に示した構造は、本実施の形態でも同様に適用されてよい。

【0123】

本実施の形態によれば、上述した第1の実施の形態で述べた作用効果に加え、次の如き顕著な作用効果が得られる。

【0124】

(a)ガラス基板1上に、約300〜600℃又は420〜600℃と更に低温でのグラフォエピタキシャル成長により、シリコン単結晶薄膜7を均一に形成することができる。

【0125】

(b)従って、ガラス基板のみならず、有機基板などの絶縁基板上に、シリコン単結晶薄膜を形成できるため、歪点が低く、低コストで物性も良好な基板材質を任意に選択でき、また、基板の大型化も可能となる。ガラス基板や有機基板は、石英基板やセラミック基板に比べて、安価に作成することができ、さらに薄板化/長尺化/ロール化が可能であるので、シリコン単結晶薄膜を形成した薄板を長尺/ロール化した大型ガラス基板などを生産性良く、安価に作製することができる。ガラス基板として、ガラス歪点(又は最高使用温度)が低い(例えば500℃)ガラスを用いると、この上層へガラス内部からその構成元素が拡散して、トランジスタ特性に影響する場合には、これを抑制する目的で、バリア層薄膜(例えばシリコンナイトライド:厚さ50〜200nm程度)を形成すればよい。

【0126】

(c)この低温グラフォエピタキシャル成長では、インジウム・ガリウム膜のインジウム/ガリウム組成比、基板加熱温度、溶融液温度、冷却速度等の調整により、広範囲のP型不純物濃度と高移動度の単結晶シリコン薄膜が容易に得られるので、Vth調整が容易で低抵抗化での高速動作が可能である。

【0127】

<第4の実施の形態>

本発明の第4の実施の形態を説明する。

【0128】

本実施の形態は、上述の第3の実施の形態と比べて透過型LCDに関するものであってその製造工程は上述の第3の実施の形態で述べたと同様、インジウム・ガリウム溶融液を用いた低温グラフォエピタキシャル成長によって単結晶シリコン薄膜を形成することができる。

【0129】

そして、この単結晶シリコン薄膜を用い、上述した第4の実施の形態で述べたと同様、図14〜図16に示した工程によって透過型LCDを作製することができる。但し、不透明のセラミック基板や、不透明又は低透過率の有機基板は適していない。

【0130】

従って、本実施の形態では、上述した第1の実施の形態及び第3の実施の形態の双方の優れた作用効果を併せ持つことができる。即ち、上述した第1の実施の形態の有する作用効果に加え、ホウケイ酸ガラスや耐熱性のポリイミド等の有機基板などの低コストで薄板、長尺化が可能な基板1を用い得ること、インジウム/ガリウム組成比によって単結晶シリコン薄膜7の導電型やVthの調整が容易となること、表示アレイ部上にカラーフィルタ42やブラックマスク43を作りこむことにより、液晶表示パネルの開口率を改善し、またバックライトも含めたディスプレイモジュールの低消費電力化が実現することである。

【0131】

<第5の実施の形態>

図17〜図25は、本発明の第5の実施の形態を示すものである。

【0132】

本実施の形態では、周辺駆動回路部は上述した第1の実施の形態と同様のトップゲート型のpMOSTFTとnMOSTFTとからなるcMOS駆動回路で構成する。表示部は反射型ではあるが、TFTを各種ゲート構造のものとして、種々の組み合わせにしている。

【0133】

即ち、図17(A)は、上述した第1の実施の形態と同様のトップゲート型のnMOSLDD−TFTを表示部に設けているが、図17(B)に示す表示部にはボトムゲート型のnMOSLDD−TFT、図17(C)に示す表示部にはデュアルゲート型のnMOSLDD−TFTをそれぞれ設けている。これらのボトムゲート型、デュアルゲート型MOSTFTのいずれも、後述のように、周辺駆動回路部のトップゲート型MOSTFTと共通の工程で作製可能であるが、特にデュアルゲート型の場合には上下のゲート部によって駆動能力が向上し、高速スイッチングに適し、また上下のゲート部のいずれかを選択的に用いて場合に応じてトップゲート型又はボトムゲート型として動作させることもできる。

【0134】

なお、図17(B)のボトムゲート型MOSTFTにおいて、図中の71はMo・Ta等のゲート電極であり、72はSiN膜及び73はSiO2 膜であってゲート絶縁膜を形成し、このゲート絶縁膜上にはトップゲート型MOSTFTと同様の単結晶シリコン層を用いたチャンネル領域等が形成されている。また、図17(C)のデュアルゲート型MOSTFTにおいて、下部ゲート部はボトムゲート型MOSTFTと同様であるが、上部ゲート部は、ゲート絶縁膜73をSiO2 膜とSiN膜で形成し、この上に上部ゲート電極74を設けている。但し、いずれにおいても、グラフォエピタキシャル成長のシードとなる段差4の外側に各ゲート部を構成している。

【0135】

次に、上記のボトムゲート型MOSTFTの製造方法を図18〜図22で、上記のデュアルゲート型MOSTFTの製造方法を図23〜図25でそれぞれ説明する。なお、周辺駆動回路部のトップゲート型MOSTFTの製造方法は図1〜図6において述べたものと同じであるので、ここでは図示を省略している。

【0136】

表示部において、ボトムゲート型MOSTFTを製造するには、まず、図18の(1)に示すように、基板1上に、モリブデン/タンタル(Mo・Ta)合金のスパッタ膜71(500〜600nm厚)を形成する。

【0137】

次いで、図18(2)に示すように、フォトレジスト70を所定パターンに形成し、これをマスクにしてMo・Ta膜9をテーパエッチングし、側端部71aが台形状に20〜45度でなだらかに傾斜したゲート電極71を形成する。

【0138】

次いで、図18(3)に示すように、フォトレジスト71の除去後に、モリブデン・タンタル合金膜71を含む基板1上に、プラズマCVD法等により、SiN膜(約100nm厚)72とSiO2 膜(約200nm厚)73とを、この順に積層したゲート絶縁膜を形成する。

【0139】

次いで、図18の(4)に示すように、図1の(1)と同じ工程において、少なくともTFT形成領域に、フォトレジスト2を所定パターンに形成し、これをマスクとして上述したと同様に基板1上のゲート絶縁膜に(更には基板1にも)段差4を適当な形状及び寸法で複数個形成する。この段差4は、後述の単結晶シリコンのグラフォエピタキシャル成長時のシードとなるものであって、深さd=0.3〜0.4μm、幅w=2〜3μm、長さ(紙面垂直方向)=10〜20μmであってよく、底辺と側面のなす角(底角)は直角とする。

【0140】

次いで、図19(5)に示すように、フォトレジスト2の除去後に、図1の(2)と同じ工程において、上述したと同様に、シリコンを含有するインジウム(又はインジウム・ガリウム又はガリウム)溶融液6を上述したと同様の基板温度で基板1上に塗布する。以下では、インジウムを例として述べる。

【0141】

次いで、図19の(6)に示すように、図2(3)と同じ工程において、徐々に冷却することによって、インジウムに溶解していたシリコンを段差4の底辺の角部をシード(種)としてグラフォエピタキシャル成長し、厚さ例えば0.1μm程度のP型単結晶シリコン層7として析出させる。この際、下地のゲート電極71の側端部71aはなだらかな傾斜面となっているので、この面上には、段差4によるエピタキシャル成長を阻害せず、段切れなしに単結晶シリコン層7が成長することになる。

【0142】

次いで、図19(7)に示すように、表面側に付着したインジウム6Aを塩酸、硫酸などによって溶解除去した後、不純物イオンを適量ドーピングして比抵抗の調整等を行ってよい。

【0143】

次いで、図19の(8)に示すように、図3の(8)と同じ工程において、表示部のnMOSTFTのゲート部をフォトレジスト13でカバーし、露出したnMOSTFTのソース/ドレイン領域にリンイオン14をドーピング(イオン注入)して、N- 型層からなるLDD部15を自己整合的に形成する。このとき、ボトムゲート電極71の存在によって表面高低差(又はパターン)を認識し易く、フォトレジスト13の位置合わせ(マスク合わせ)を行い易く、アライメントずれが生じ難い。

【0144】

次いで、図20(9)に示すように、図4の(9)と同じ工程において、nMOSTFTのゲート部及びLDD部をフォトレジスト16でカバーし、露出した領域にリン又はひ素イオン17をドーピング(イオン注入)して、nMOSTFTのN+ 型層からなるソース部18及びドレイン部19を形成する。

【0145】

次いで、図20の(10)に示すように、図4の(10)と同じ工程において、nMOSTFTの全部をフォトレジスト20でカバーし、ボロンイオン21をドーピング(イオン注入)して周辺駆動回路部のpMOSTFTのP+ 層のソース部及びドレイン部を形成する。

【0146】

次いで、図20の(11)に示すように、図4の(11)と同じ工程において、能動素子部と受動素子部をアイランド化するため、フォトレジスト24を設け、単結晶シリコン薄膜層を汎用フォトリソグラフィ及びエッチング技術で選択的に除去する。

【0147】

次いで、図20の(12)に示すように、図4の(12)と同じ工程において、プラズマCVD、高密度プラズマCVD、触媒CVD法等により、SiO2 膜53(約300nm厚)とリンシリケートガラス(PSG)膜54(約300nm厚)をこの順に全面に形成する。なお、SiO2 膜53とPSG膜54は上述した保護膜25に相当するものである。そして、この状態で単結晶シリコン膜を上述したと同様に活性化処理する。

【0148】

次いで、図21の(13)に示すように、図5の(13)と同じ工程において、汎用フォトリソグラフィ及びエッチング技術により、ソース部のコンタクト用窓開けを行う。そして、全面に400〜500nm厚のアルミニウム等のスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、TFTのソース電極26を形成すると同時に、データライン及びゲートラインを形成する。その後に、フォーミングガス中、約400℃/1hで、シンター処理する。

【0149】

次いで、図21の(14)に示すように、図5の(14)と同じ工程において、高密度プラズマCVD、触媒CVD法等により、PSG膜(約300nm厚)及びSiN膜(約300nm厚)からなる絶縁膜36を全面に形成し、表示用のTFTのドレイン部のコンタクト用窓開けを行う。

【0150】

次いで、図21の(15)に示すように、図6の(15)と同じ工程において、スピンコート等で2〜3μm厚みの感光性樹脂膜28を形成し、図21の(16)に示すように、汎用フォトリソグラフィ及びエッチング技術により、少なくとも画素部に最適の反射特性と視野角特性とを得るような凹凸形状パターンを形成し、リフローさせて凹凸粗面28Aからなる反射面下部を形成する。同時に表示用TFTのドレイン部のコンタクト用の樹脂窓開けを行う。

【0151】

次いで、図21の(16)に示すように、図6の(16)と同じ工程において、全面に400〜500nm厚のアルミニウム等のスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、表示用TFTのドレイン部19と接続した凹凸形状のアルミニウム等の反射部29を形成する。

【0152】

以上のようにして、段差4を高温グラフォエピタキシャル成長のシードとして形成された単結晶シリコン層7を用いた表示部にボトムゲート型のnMOSLDD−TFT(周辺回路部ではpMOSTFT及びnMOSTFTからなるCMOS駆動回路)を作り込んだ表示部−周辺駆動回路部一体型のアクティブマトリクス基板30を作製することができる。

【0153】

図22は、表示部に設ける上記のボトムゲート型MOSTFTのゲート絶縁膜をMo・Taの陽極酸化法で形成した例を示す。

【0154】

即ち、図18の(2)の工程後に、図22の(3)に示すようにモリブデン・タンタル合金膜71を公知の陽極酸化処理することによって、その表面にTa2 O5 からなるゲート絶縁膜74を100〜200nm厚に形成する。

【0155】

この後の工程は、図22の(4)に示すように、図18の(4)の工程と同様にして段差4を形成し、シリコンを含有したインジウム溶融液6を塗布した後、図19の(5)〜図21の(16)の工程と同様にして図22の(5)に示すように、アクティブマトリクス基板30を作製する。

【0156】

次に、表示部において、デュアルゲート型MOSTFTを製造するには、まず、図18の(1)〜図19の(7)までの工程は、上述したと同様に行う。

【0157】

即ち、図23の(8)に示すように、絶縁膜72、73及び基板1に段差4を形成し、更に、段差4をシードとして単結晶シリコン層7をグラフォエピタキシャル成長させる。次いで、図3の(6)と同じ工程において、単結晶シリコン薄膜7上の全面に、プラズマCVD、触媒CVD等によりSiO2 膜(約200nm厚)とSiN膜(約100nm厚)をこの順に連続形成して絶縁膜80(これは上述の絶縁膜8に相当)を形成し、更にMo・Ta合金のスパッタ膜81(500〜600nm厚)(これは上述のスパッタ膜9に相当)を形成する。

【0158】

次いで、図23の(9)に示すように、図3の(7)と同じ工程において、フォトレジストパターン10を形成し、連続したエッチングによりMo・Ta合金のトップゲート電極82(これは上述のゲート電極12に相当)と、ゲート絶縁膜83(これは上述のゲート絶縁膜11に相当)を形成し、単結晶シリコン薄膜層7を露出させる。

【0159】

次いで、図23の(10)に示すように、図3の(8)と同じ工程において、nMOSTFTのトップゲート部をフォトレジスト13でカバーし、露出した表示用のnMOSTFTのソース/ドレイン領域にリンイオン14をドーピング(イオン注入)して、N- 型層のLDD部15を形成する。

【0160】

次いで、図23(11)に示すように、図4の(9)と同じ工程において、nMOSTFTのゲート部及びLDD部をフォトレジスト16でカバーし、露出した領域にリン又はひ素イオン17をドーピング(イオン注入)して、nMOSTFTのN+ 型層からなるソース部18及びドレイン部19を形成する。

【0161】

次いで、図24の(12)に示すように、図4の(10)と同じ工程において、pMOSTFTのゲート部をフォトレジスト20でカバーし、露出した領域にボロンイオン21をドーピング(イオン注入)して周辺駆動回路部のpMOSTFTのP+ 層のソース部及びドレイン部を形成する。

【0162】

次いで、図24の(13)に示すように、図4の(11)と同じ工程において、能動素子部と受動素子部をアイランド化するため、フォトレジスト24を設け、能動素子部と受動素子部以外の単結晶シリコン薄膜層を汎用フォトリソグラフィ及びエッチング技術で選択的に除去する。

【0163】

次いで、図24の(14)に示すように、図5の(12)と同じ工程において、プラズマCVD、高密度プラズマCVD、触媒CVD法等により、SiO2 膜53(約200nm厚)とリンシリケートガラス(PSG)膜54(約300nm厚)を全面に形成する。これらの膜53、54は上述の保護膜25に相当する。そして、単結晶シリコン層7を活性化処理する。

【0164】

次いで、図24の(15)に示すように、図5の(13)と同じ工程において、ソース部のコンタクト用窓開けを行う。そして、全面に400〜500nm厚のアルミニウムのスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、ソース電極26を形成すると同時に、データライン及びゲートラインを形成する。

【0165】

次いで、図25の(16)に示すように、図5の(14)と同じ工程でPSG膜(約300nm厚)及びSiN膜(約300nm厚)からなる絶縁膜36を全面に形成し、表示用のTFTのドレイン部のコンタクト用窓開けを行う。

【0166】

次いで、図25の(17)に示すように、全面に、スピンコート等で2〜3μm厚みの感光性樹脂膜28を形成し、図25の(18)に示すように、図6の(17)、(18)の工程と同様に、少なくとも画素部に凹凸粗面28Aからなる反射面下部を形成し、同時に表示用TFTのドレイン部のコンタクト用の樹脂窓開けを行い、更に表示用TFTのドレイン部19と接続した、最適な反射特性と視野角特性を得るような凹凸形状のアルミニウム反射部29を形成する。

【0167】

以上のようにして、段差4を高温グラフォエピタキシャル成長のシードとして形成された単結晶シリコン層7を用い、表示部にデュアルゲート型のnMOSLDDTFTを、周辺部にpMOSTFT及びnMOSTFTからなるCMOS駆動回路を作り込んだ表示部−周辺駆動回路部一体型のアクティブマトリクス基板30を作製することができる。

【0168】

<第6の実施の形態>

図26〜図31は、本発明の第6の実施の形態を示すものである。

【0169】

本実施の形態では、上述した実施の形態とは異なり、トップゲート部のゲート電極をアルミニウム、アルミニウム合金、例えば1%Si入りアルミニウム、1〜2%銅入りアルミニウム、銅等の比較的耐熱性の低い材料で形成している。

【0170】

まず、表示部用及び周辺駆動回路部共にトップゲート型MOSTFTを設ける場合には、上述した第1の実施の形態における図1の(1)〜図2の(5)までの工程は同様に行って、図26の(5)に示すように、周辺駆動回路部のpMOSTFT部にN型ウエル7Aを形成する。

【0171】

次いで、図26の(6)に示すように、周辺駆動領域のnMOS及びpMOSTFT全部と、表示領域のnMOSTFTのゲート部をフォトレジスト13でカバーし、露出したnMOSTFTのソース/ドレイン領域にリンイオン14を例えば20kVで5×1013atoms/cm2 のドーズ量でドーピング(イオン注入)して、N- 型層からなるLDD部15を自己整合的に形成する。

【0172】

次いで、図27の(7)に示すように、周辺駆動領域のpMOSTFT全部と、周辺駆動領域のnMOSTFTのゲート部と、表示領域のnMOSTFTのゲート及びLDD部とをフォトレジスト16でカバーし、露出した領域にリン又はひ素イオン17を例えば20kVで5×1015atoms/cm2 のドーズ量でドーピング(イオン注入)して、nMOSTFTのN+ 型層からなるソース部18及びドレイン部19とLDD部15とを形成する。この場合、仮想線のようにレジスト13を残し、これを覆うようにレジスト16を設ければ、レジスト16形成時のマスクの位置合せをレジスト13を目安にでき、マスク合せが容易となり、アライメントずれも少なくなる。

【0173】

次いで、図27の(8)に示すように、周辺駆動領域のnMOSTFT及び表示領域のnMOSTFTの全部とpMOSTFTのゲート部をフォトレジスト20でカバーし、露出した領域にボロンイオン21を例えば10kVで5×1015atoms/cm2 のドーズ量でドーピング(イオン注入)してpMOSTFTのP+ 層のソース部22及びドレイン部23を形成する。

【0174】

次いで、レジスト20の除去後に、図27の(9)に示すように、単結晶シリコン層7、7Aを上述したと同様に活性化処理し、更に表面にゲート絶縁膜12、ゲート電極材料(アルミニウム又は1%Si入りアルミニウム等)11を形成する。ゲート電極材料層11は真空蒸着法又はスパッタ法で形成可能である。

【0175】

次いで、上述したと同様に、各ゲート部をパターニングした後、能動素子部と受動素子部をアイランド化し、更に図28の(10)に示すように、SiO2 膜(約200nm厚)及びリンシリケートガラス(PSG)膜(約300nm厚)をこの順に全面に連続形成して保護膜25を形成する。

【0176】

次いで、図28の(11)に示すように、汎用フォトリソグラフィ及びエッチング技術により、周辺駆動回路の全TFTのソース/ドレイン部、及び表示用TFTのソース部のコンタクト用窓開けを行う。

【0177】

そして、全面に500〜600nm厚のアルミニウム又は1%Si入りアルミニウム等のスパッタ膜を形成し、汎用フォトリソグラフィ及びエッチング技術により、周辺駆動回路及び表示部のすべてのTFTのソース電極26と周辺駆動回路部のドレイン電極27を形成すると同時に、データライン及びゲートラインを形成する。その後に、フォーミングガス(N2 +H2 )中、約400℃/1hで、シンター処理する。

【0178】

次いで、図5の(14)〜図6の(17)と同様にして単結晶シリコン層7を用いた表示部及び周辺駆動回路部にそれぞれ、アルミニウム又は1%Si入りアルミニウム等をゲート電極とするトップゲート型のnMOSLDD−TFT、pMOSTFT及びnMOSTFTで構成するCMOS駆動回路を作り込んだ表示部−周辺駆動回路部一体型のアクティブマトリクス基板30を作製することができる。

【0179】

本実施の形態では、単結晶シリコン層7の活性化処理後にアルミニウム又は1%Si入りアルミニウム等のゲート電極11を形成しているので、その活性化処理時の熱の影響はゲート電極材料の耐熱性とは無関係となるため、ゲート電極材料として比較的耐熱性が低く、低コストのアルミニウム又は1%Si入りアルミニウム等でも使用可能となり、電極材料の選択の幅も広がる。これは、表示部がボトムゲート型MOSTFTの場合も同様である。

【0180】

次に、表示部にデュアルゲート型MOSTFT、周辺駆動回路はトップゲート型MOSTFTを設ける場合には、上述した第7の実施の形態における図18の(1)〜図19の(7)までの工程は同様に行って、図29の(7)に示すように、周辺駆動回路部のpMOSTFT部にN型ウエル7Aを形成する。

【0181】

次いで、図29の(8)に示すように、図26の(6)と同様にして、表示部のTFT部にリンイオン14をドープしてLDD部15を形成する。

【0182】

次いで、図30の(9)に示すように、図27の(7)と同様にして表示部及び周辺駆動回路部のnMOSTFT部にリンイオン17をドープしてN+ 型ソース領域18及びドレイン領域19をそれぞれ形成する。

【0183】

次いで、図30の(10)に示すように、図27の(8)と同様にして周辺駆動回路部のpMOSTFT部にボロンイオン21をドープしてP+ 型ソース領域22及びドレイン領域23をそれぞれ形成する。

【0184】

次いで、レジスト20の除去後に、図30の(11)に示すように、単結晶シリコン層7をパターニングして能動素子部と受動素子部をアイランド化した後、図31の(12)に示すように、単結晶シリコン層7、7Aを上述したと同様に活性化処理し、更に表示部では表面にゲート絶縁膜80を形成し、周辺駆動回路部では表面にゲート絶縁膜12を形成する。

【0185】

次いで、図31の(13)に示すように、全面にスパッタ法で成膜したアルミニウムをパターニングして、表示部の各上部ゲート電極83、周辺駆動回路部の各ゲート電極11を形成する。

【0186】

次いで、図31の(14)に示すように、SiO2 膜(約200nm厚)及びリンシリケートガラス(PSG)膜(約300nm厚)をこの順に全面に連続形成して保護膜25を形成する。

【0187】

次いで、上述したと同様にして、周辺駆動回路及び表示部のすべてのTFTのソース電極26と周辺駆動回路部のドレイン電極27を形成し、単結晶シリコン層7を用いた表示部及び周辺駆動回路部にそれぞれ、アルミニウムをゲート電極とするデュアルゲート型のnMOSLDD−TFT、pMOSTFT及びnMOSTFTで構成するCMOS駆動回路を作り込んだ表示部−周辺駆動回路部一体型のアクティブマトリクス基板30を作製することができる。

【0188】

本実施の形態でも、単結晶シリコン層7の活性化処理後にアルミニウム等のゲート電極11、83を形成しているので、その活性化処理時の熱の影響はゲート電極材料の耐熱性とは無関係となるため、ゲート電極材料として比較的耐熱性が低く、低コストのアルミニウム、アルミニウム合金、銅等でも使用可能となり、電極材料の選択の幅も広がる。なお、図31の(13)の工程でソース電極26を(更にはドレイン電極も)同時に形成することができるが、この場合には製法上のメリットがある。

【0189】

なお、上述したいずれの実施の形態においても、例えばボトムゲート型又はトップゲート型MOSTFTを作製するに際し、図32(A)に概略的に示すように、段差4を設けるとこの上に成長する単結晶シリコン膜7が薄いために段切れ(接続不良)や細り(抵抗の増大)を生じることがあるので、ソース電極26(又はドレイン電極)との接続を確実に行うためには、図32(B)、(C)に示すように、その電極を段差4を含む領域上に被着することが望ましい。

【0190】

なお、図26の(6)の工程又は図29の(8)の工程において、単結晶シリコン層7上にトップゲート絶縁膜の形成後に、イオン注入、活性化処理し、その後にトップゲート電極、ソース、ドレイン電極をアルミニウムで同時に形成してよい。

【0191】

また、上記した段差4は、図33(A)に示すように、上述の例では基板1に(更にはその上のSiN等の膜にも)形成したが、例えば図33(B)に示すように、基板1上のSiN膜51(これはガラス基板1からのイオンの拡散ストッパ機能がある。)に形成することもできる。このSiN膜51の代わりに、或いはこのSiN膜の上に上述したゲート絶縁膜72及び73を設け、これに段差4を形成してもよい。

【0192】

<第7の実施の形態>

図34〜図36は、本発明の第7の実施の形態を示すものである。

【0193】

本実施の形態では、上述した段差4の外側に(即ち、段差以外の基板1上に)各TFTを形成した各種の例を示す。なお、単結晶シリコン層7やゲート/ソース/ドレイン電極26、27については簡略に図示している。

【0194】

まず、図34はトップゲート型MOSTFTを示すが、(a)は段差による凹部4をソース側の一辺にソース領域に沿って形成し、この凹部以外の基板平坦面上において単結晶シリコン層7上にゲート絶縁膜12及びゲート電極11を形成している。同様に、(b)は、段差による凹部4をソース領域のみならずチャンネル長方向にドレイン領域端まで沿って2辺に亘ってL字パターンに形成した例、(c)は同様の凹部4をTFT能動領域を囲むように4辺に亘って矩形状に形成した例を示す。また、(d)は同様の凹部4を3辺に亘って形成した例、(e)は同様の凹部4を2辺に亘ってL字パターンに形成した例であるが、いずれも、隣接する凹部4−4間は連続していない。

【0195】

このように、各種パターンの凹部4を形成可能であると共に、TFTを凹部4以外の平坦面上に設けているので、TFTの作製が容易となる。

【0196】

図35は、ボトムゲート型MOSTFTの場合であるが、図34に示した各種パターンの段差(又は凹部)4を同様に形成することができる。即ち、図35(a)は図34(a)に対応した例であって、ボトムゲート型MOSTFTを段差による凹部4以外の平坦面上に形成したものである。同様に、図35(b)は図34(b)に、図35(c)は図34(c)や(d)に対応した例を示す。

【0197】

図36は、デュアルゲート型MOSTFTの場合であるが、これも図34に示した各種パターンの段差(又は凹部)4を同様に形成することができ、例えば図34(c)に示した段差4の内側領域の平坦面上にデュアルゲート型MOSTFTを作製することができる。

【0198】

<第8の実施の形態>

図37〜図39は、本発明の第8の実施の形態を示すものである。

【0199】

図37の例は、自己整合型LDD構造のTFT、例えばトップゲート型MOSLDD−TFTを複数個連ねたダブルゲート型MOSTFTに関するものである。

【0200】

これによれば、ゲート電極11を2つに分岐させ、一方を第1のゲートとして第1のLDD−TFT用、他方を第2のゲートとしての第2のLDD−TFT用として用いる(但し、単結晶シリコン層の中央部においてゲート電極間にN+ 型領域100を設け、低抵抗化を図っている)。この場合、各ゲートに異なる電圧を印加してもよいし、また何らかの原因で一方のゲートが動作不能になったとしても、残りのゲートを用いることによってソース/ドレイン間でのキャリアの移動を行え、信頼性の高いデバイスを提供できることになる。また、第1のLDD−TFTと第2のLDD−TFTとを直列に2個接続して各画素を駆動する薄膜トランジスタを形成するようにしたので、オフしているときに、各薄膜トランジスタのソース−ドレイン間に印加される電圧を大幅に減少させることができる。したがって、オフ時に流れるリーク電流を少なくすることができ、液晶ディスプレイのコントラスト及び画質を良好に改善することができる。また、上記LDDトランジスタにおける低濃度ドレイン領域と同じ半導体層のみを用いて上記2つのLDDトランジスタを接続するようにしているので、各トランジスタ間の接続距離を短くすることができ、このためLDDトランジスタを2個つなげても所要面積が大きくならないようにすることができる。なお、上記の第1、第2のゲートは互いに完全に分離し、独立して動作させることも可能である。

【0201】

図38の例は、ボトムゲート型MOSTFTをダブルゲート構造としたもの(A)と、デュアルゲート型MOSTFTをダブルゲート構造としたもの(B)である。

【0202】

これらのダブルゲート型MOSTFTも、上記のトップゲート型と同様の利点を有するが、このうちデュアルゲート型の場合は更に、上下のゲート部のいずれかが動作不能となっても一方のゲート部を使用できることも利点である。

【0203】

図39には、上記の各ダブルゲート型MOSTFTの等価回路図を示している。なお、上記においては、ゲートを2つに分岐したが、3つ又はそれ以上に分岐又は分割することもできる。これらのダブルゲート又はマルチゲート構造において、チャンネル領域内に2以上の分岐した同電位のゲート電極を有するか、又は分割された異電位又は同電位のゲート電極を有していてよい。

【0204】

<第9の実施の形態>

図40は、本発明の第9の実施の形態を示すものであって、nMOSTFTのデュアルゲート型構造のTFTにおいて、上下のゲート部のいずれか一方をトランジスタ動作させるが、他方のゲート部は次のように動作させている。

【0205】

即ち、図40(A)は、nMOSTFTにおいて、トップゲート側のゲート電極に常に任意の負電圧を印加してバックチャンネルのリーク電流を低減させるものである。トップゲート電極をオープンにする場合は、ボトムゲート型として使用するときである。また、図40(B)は、ボトムゲート側のゲート電極に常に任意の負電圧を印加してバックチャンネルのリーク電流を低減させるものである。この場合も、ボトムゲート電極をオープンにすると、トップゲート型として使用できる。なお、pMOSTFTの場合には、常に任意の正電圧をゲート電極に印加すれば、バックチャンネルのリーク電流を減らせる。

【0206】

いずれも、単結晶シリコン層7と絶縁膜との界面は結晶性が悪く、リーク電流が流れやすいが、上記のような電極の負電圧印加によってリーク電流を遮断できる。これは、LDD構造の効果と併せて、有利となる。また、ガラス基板1側から入射する光でリーク電流が流れることがあるが、ボトムゲート電極で光を遮断するので、リーク電流を低減できる。

【0207】

<第10の実施の形態>

図41〜図49は、本発明の第10の実施の形態を示すものである。

【0208】

上述したように、トップゲート型、ボトムゲート型、デュアルゲート型の各TFTはそれぞれ構造上、機能上の差異又は特長があることから、これらを表示部と周辺駆動回路部において採用する際に、これら各部間でTFTを種々に組み合わせて設けることが有利なことがある。

【0209】

例えば、図41に示すように、表示部にトップゲート型、ボトムゲート型、デュアルゲート型のいずれかのMOSTFTを採用した場合、周辺駆動回路にはトップゲート型MOSTFT、ボトムゲート型MOSTFT、デュアルゲート型MOSTFTのうち、少なくともトップゲート型を採用するか、或いはそれらが混在することも可能である。この組み合わせは12通り(No.1〜No.12)挙げられる。特に、周辺駆動回路のMOSTFTにデュアルゲート構造を用いると、このようなデュアルゲート構造は、上下のゲート部の選択によってトップゲート型にもボトムゲート型にも容易に変更することができ、また、周辺駆動回路の一部に大きな駆動能力のTFTが必要な場合は、デュアルゲート型が必要となる場合もある。例えば、LCD以外の電気光学装置として本発明を有機ELやFED等に適用する場合は必要であると考えられる。

【0210】

図42及び図43は表示部のMOSTFTがLDD構造でないとき、図44及び図45は表示部のMOSTFTがLDD構造であるとき、図46及び図47は周辺駆動回路部のMOSTFTがLDD構造のTFTを含むとき、図48及び図49は周辺駆動回路部と表示部の双方がLDD構造のMOSTFTを含むときのそれぞれにおいて、周辺駆動回路部と表示部の各MOSTFTの組み合わせをチャンネル導電型別に示した各種の例(No.1〜No.216)を示す。

【0211】

このように、図41に示したゲート構造別の組み合わせは、具体的には図42〜図49に示したようになる。これは、周辺駆動回路部がトップゲート型と他のゲート型との混在したMOSTFTからなっている場合も、同様の組み合わせが可能である。なお、図41〜図49に示したTFTの各種組合せは、TFTのチャンネル領域などを単結晶シリコンで形成する場合に限らず、多結晶シリコンや、アモルファスシリコン(但し、表示部のみ)で形成する場合も同様に適用可能である。

【0212】

<第11の実施の形態>

図50〜図51は、本発明の第11の実施の形態を示すものである。

【0213】

本実施の形態では、アクティブマトリクス駆動LCDにおいて、周辺駆動回路部は、駆動能力の向上の点から、本発明に基づいて上述の単結晶シリコン層を用いたTFTを設ける。但し、これはトップゲート型に限らず、他のゲート型が混在してよいし、チャンネル導電型も種々であってもよく、また単結晶シリコン層以外の多結晶シリコン層を用いたMOSTFTが含まれていてもよい。これに対し、表示部のMOSTFTは、単結晶シリコン層を用いるのが望ましいが、これに限らず、多結晶シリコンやアモルファスシリコン層を用いたものであってよく、或いは3種のシリコン層の少なくとも2種が混在したものであってもよい。但し、表示部をnMOSTFTで形成するときは、アモルファスシリコン層を用いても実用的なスイッチング速度は得られるが、単結晶シリコン又は多結晶シリコン層の方がTFT面積を小さくでき、画素欠陥の減少の面でもアモルファスシリコンよりは有利である。なお、既述したグラフォエピタキシャル成長時に単結晶シリコンだけでなく、多結晶シリコンも同時に生じ、いわゆるCGS(Continuous grain silicon)構造も含まれることもあるが、これも能動素子と受動素子の形成に利用できる。

【0214】

図50には、各部間でのMOSTFTの各種組み合わせ例(A)、(B)、(C)を示し、図51にはその具体例を例示した。単結晶シリコンを用いると、電流駆動能力が向上するため、素子を小さくでき、大画面化が可能となり、表示部では開口率が向上する。

【0215】

なお、周辺駆動回路部では、上記のMOSTFTだけでなく、ダイオード、キャパシタンス、抵抗、インダクタンス等を集積した電子回路が絶縁基板(ガラス基板等)に一体形成されてよいことは勿論である。

【0216】

<第12の実施の形態>

図52は、本発明の第12の実施の形態例を示すものである。

【0217】

本実施の形態は、上述した各実施の形態がアクティブマトリクス駆動の例についてのものであるのに対し、本発明をパッシブマトリクス駆動に適用したものである。

【0218】

即ち、表示部は、上述したMOSTFTの如きスイッチング素子を設けず、対向する基板に形成した一対の電極間に印加する電圧による電位差でのみ表示部の入射光又は反射光が調光される。こうした調光素子には、反射型、透過型のLCDをはじめ、有機EL(エレクトロルミネセンス表示素子)、FED(電界放出型表示素子)、LEPD(発光ポリマー表示素子)、LED(発光ダイオード表示素子)なども含まれる。

【0219】

<第13の実施の形態>

図53は、本発明の第13の実施の形態を示すものである。

【0220】

本実施の形態は、本発明をLCD以外の電気光学装置である有機又は無機EL(エレクトロルミネセンス表示素子)やFED(電界放出型表示素子)、LEPD(発生ポリマー表示素子)、LED(発光ダイオード表示素子)などに適用したものである。

【0221】

即ち、図53(A)には、アクティブマトリクス駆動のEL素子を示し、例えばアモルファス有機化合物を用いた有機EL層(又はZnS:Mnを用いた無機EL層)90を基板1上に設け、その下部に既述した透明電極(ITO)41を形成し、上部に陰極91を形成し、これら両極間の電圧印加によって所定色の発光がフィルタ61を通して得られる。

【0222】

この際、アクティブマトリクス駆動により透明電極41へデータ電圧を印加するために、基板1上の段差4をシードとしてグラフォエピタキシャル成長させた単結晶シリコン層を用いた本発明による単結晶シリコンMOSTFT(即ち、nMOSLDD−TFT)が基板1上に作り込まれている。同様のTFTは周辺駆動回路にも設けられる。このEL素子は、単結晶シリコン層を用いたMOSLDD−TFTで駆動しているので、スイッチング速度が早く、またリーク電流も少ない。なお、上記のフィルタ61は、EL層90が特定色を発光するものであれば、省略可能である。

【0223】

なお、EL素子の場合、駆動電圧が高いため、周辺駆動回路部には、上記のMOSTFT以外に、高耐圧のドライバ素子(高耐圧cMOSTFTとバイポーラ素子など)を設けるのが有利である。

【0224】

図53(B)は、パッシブマトリクス駆動のFEDを示すが、対向するガラス基板1−32間の真空部において、両電極92−93間の印加電圧によって冷陰極94から放出された電子をゲートライン95の選択によって対向する螢光体層96へ入射させ、所定色の発光を得るものである。

【0225】

ここで、エミッタライン92は、周辺駆動回路へ導かれ、データ電圧で駆動されるが、その周辺駆動回路には、本発明に基づいて単結晶シリコン層を用いたMOSTFTが設けられ、エミッタライン92の高速駆動に寄与している。なお、このFEDは、各画素に上記のMOSTFTを接続することにより、アクティブマトリクス駆動させることも可能である。

【0226】

なお、図53(A)の素子において、EL層90の代わりに公知の発光ポリマーを用いれば、パッシブマトリクス又はアクティブマトリクス駆動の発光ポリマー表示装置(LEPD)として構成することができる。その他、図53(B)の素子において、ダイアモンド薄膜をカソード側に用いたFEDと類似のデバイスも構成できる。また、発光ダイオードにおいて、発光部に本発明によりエピタキシャル成長させた単結晶シリコンのMOSTFTにより、例えばガリウム系(ガリウム・アルミニウム・ひ素など)の膜からなる発光部を駆動できる。或いは、本発明のエピタキシャル成長法で発光部の膜を単結晶成長させることも考えられる。

【0227】

以上に述べた本発明の実施の形態は、本発明の技術的思想に基いて種々変形が可能である。

【0228】

例えば、上述した低融点金属の溶融液6の塗布時に、溶解度が大きい3価又は5価元素を、例えばボロン、リン、アンチモン、ひ素、アルミニウム、ガリウム、インジウム、ビスマスなどを低融点金属の溶融液6に適量ドープしておけば、成長するシリコンエピタキシャル成長層7のP型又はN型のチャンネル導電型や、そのキャリア濃度を任意に制御することができる。

【0229】

また、ガラス基板からのイオンの拡散防止のために基板表面にSiN膜(例えば50〜200nm厚)、更には必要に応じてSiO2 膜(例えば100nm厚)を設けてよく、またこれらの膜に既述した如き段差4を形成してもよい。上述した段差はRIE以外にもイオンミリング法などによって形成することもできる。

【0230】

また、本発明は周辺駆動回路のTFTに好適なものであるが、それ以外にもダイオードなどの素子の能動領域や、抵抗、キャパシタンス、インダクタンスなどの受動領域を本発明による単結晶シリコン層で形成することも可能である。

【0231】

【発明の作用効果】

本発明によれば、基板に形成した上記段差をシードにして特にシリコンを溶解した低融点金属の溶融液を塗布し、この溶融液からの単結晶シリコンの析出によってシリコンエピタキシャル成長による単結晶シリコン薄膜層の如き単結晶半導体層を形成し、これを表示部−周辺駆動回路一体型のLCDなどの電気光学装置の周辺駆動回路部のトップゲート型MOSTFTなどの能動素子と受動素子の少なくとも能動素子に用いているので、次の(A)〜(F)に示す顕著な作用効果を得ることができる。

【0232】

(A)所定形状/寸法の段差を基板に形成し、その段差の底辺の角をシードとしてグラフォエピタキシャル成長させることにより、540cm2 /v・sec以上の高い電子移動度の単結晶シリコン薄膜などの単結晶半導体層が得られるので、高性能ドライバ内蔵の表示用薄膜半導体装置などの電気光学装置の製造が可能となる。

【0233】

(B)特にこの単結晶シリコン薄膜による単結晶シリコントップゲート型MOSTFTは、高いスイッチング特性を有し、LDD構造を有するnMOS又はpMOS又はcMOSTFTの表示部と、高い駆動能力のcMOS、又はnMOS又はpMOSTFT又はこれらの混在からなる周辺駆動回路とを一体化した構成が可能となり、高画質、高精細、狭額縁、高効率、大画面の表示パネルが実現する。

【0234】

(C)上記した低融点金属の溶融液層は低温で調製し、これより少し高いだけの温度に加熱した基板上に塗布で形成できるから、比較的低温でシリコン単結晶膜を均一に形成することができる。

【0235】

(D)固相成長法の場合のような中温で長時間のアニールや、エキシマレーザーアニールが不要となるから、生産性が高く、高価な製造設備が不要でコストダウンが可能となる。

【0236】

(E)このグラフォエピタキシャル成長では、低融点金属溶融液の組成比(特にシリコン/インジウム/ガリウム組成比、シリコン/インジウム組成比)、基板加熱温度、溶融液温度、冷却速度等の調整により、広範囲のP型不純物濃度と高移動度の単結晶シリコン薄膜が容易に得られるので、Vth調整が容易であり、低抵抗化による高速動作が可能である。

【0237】

(F)また、シリコン含有低融点金属層の成膜時に、溶解度が大きい3族又は5族の不純物元素(ボロン、リン、アンチモン、ひ素、ビスマス、アルミニウムなど)を別途適量ドープしておけば、グラフォエピタキシャル成長による単結晶シリコン薄膜の不純物種及び/又はその濃度、即ちP型/N型の導電型及び/又はキャリア濃度を任意に制御することができる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態によるLCD(液晶表示装置)の製造プロセスを工程順に示す断面図である。

【図2】同、LCDの製造プロセスを工程順に示す断面図である。

【図3】同、LCDの製造プロセスを工程順に示す断面図である。

【図4】同、LCDの製造プロセスを工程順に示す断面図である。

【図5】同、LCDの製造プロセスを工程順に示す断面図である。

【図6】同、LCDの製造プロセスを工程順に示す断面図である。

【図7】同、LCDの要部断面図である。

【図8】非晶質基板上のシリコン結晶成長の状況を説明するための概略斜視図である。

【図9】グラフォエピタキシャル成長技術における各種段差形状とシリコン成長結晶方位を示す概略断面図である。

【図10】Si−In状態図(A)及びSi−Ga状態図(B)である。

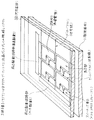

【図11】本発明の第1の実施の形態によるLCDの全体の概略レイアウトを示す斜視図である。

【図12】同、LCDの等価回路図である。

【図13】同、LCDの概略構成図である。

【図14】本発明の第2の実施の形態によるLCDの製造プロセスを工程順に示す断面図である。

【図15】同、LCDの要部断面図である。

【図16】同、LCDの製造プロセスを工程順に示す断面図である。

【図17】本発明の第5の実施の形態によるLCDの要部断面図である。

【図18】同、LCDの製造プロセスを工程順に示す断面図である。

【図19】同、LCDの製造プロセスを工程順に示す断面図である。

【図20】同、LCDの製造プロセスを工程順に示す断面図である。

【図21】同、LCDの製造プロセスを工程順に示す断面図である。

【図22】同、LCDの製造プロセスを工程順に示す断面図である。

【図23】同、LCDの製造プロセスを工程順に示す断面図である。

【図24】同、LCDの製造プロセスを工程順に示す断面図である。

【図25】同、LCDの製造プロセスを工程順に示す断面図である。

【図26】本発明の第6の実施の形態によるLCDの製造プロセスを工程順に示す断面図である。

【図27】同、LCDの製造プロセスを工程順に示す断面図である。

【図28】同、LCDの製造プロセスを工程順に示す断面図である。

【図29】同、LCDの製造プロセスを工程順に示す断面図である。

【図30】同、LCDの製造プロセスを工程順に示す断面図である。

【図31】同、LCDの製造プロセスを工程順に示す断面図である。

【図32】同、LCDの製造時の要部断面図である。

【図33】同、LCDの製造時の要部断面図である。

【図34】本発明の第7の実施の形態によるLCDの各種TFTを示す平面図又は断面図である。

【図35】同、LCDの各種TFTを示す断面図である。

【図36】同、LCDの要部断面図である。

【図37】本発明の第8の実施の形態によるLCDの要部断面図又は平面図である。

【図38】同、LCDの各種TFTの要部断面図である。

【図39】同、LCDのTFTの等価回路図である。

【図40】本発明の第9の実施の形態によるLCDのTFTの要部断面図である。

【図41】本発明の第10の実施の形態によるLCDの各部TFTの組み合わせを示す図である。

【図42】同、LCDの各部TFTの組み合わせを示す図である。

【図43】同、LCDの各部TFTの組み合わせを示す図である。

【図44】同、LCDの各部TFTの組み合わせを示す図である。

【図45】同、LCDの各部TFTの組み合わせを示す図である。

【図46】同、LCDの各部TFTの組み合わせを示す図である。

【図47】同、LCDの各部TFTの組み合わせを示す図である。

【図48】同、LCDの各部TFTの組み合わせを示す図である。

【図49】同、LCDの各部TFTの組み合わせを示す図である。

【図50】本発明の第11の実施の形態によるLCDの概略レイアウト図である。

【図51】同、LCDの各部TFTの組み合わせを示す図である。

【図52】本発明の第12の実施の形態によるデバイスの概略レイアウト図である。

【図53】本発明の第13の実施の形態によるEL及びFEDの要部断面図である。

【符号の説明】

1…ガラス(又は石英)基板、4…段差、

6…インジウム(又はインジウム・ガリウム又はガリウム)溶融液、

6A…インジウム(又はインジウム・ガリウム又はガリウム)、

7…単結晶シリコン層、9…Mo・Ta層、11…ゲート電極、

12…ゲート酸化膜、14、17…N型不純物イオン、15…LDD部、

18、19…N+ 型ソース又はドレイン領域、21…P型不純物イオン、

22、23…P+ 型ソース又はドレイン領域、25、36…絶縁膜、

26、27、31、41…電極、28…平坦化膜、28A…粗面(凹凸)、

29…反射膜(又は電極)、30…LCD(TFT)基板、

33、34…配向膜、35…液晶、37、46…カラーフィルタ層、

43…ブラックマスク層[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a method of manufacturing an electro-optical device and a method of manufacturing a driving substrate for an electro-optical device, and more particularly, a top-gate thin-film insulating gate type using a single crystal silicon layer grown on a insulating substrate as a grapho-epitaxial film as an active region. The present invention relates to a method suitable for a field effect transistor (hereinafter referred to as a top gate type MOSTFT. Note that a top gate type includes a stagger type or a coplanar type) and a liquid crystal display device having a passive region.

[0002]

[Prior art]

As an active matrix type liquid crystal display device, a display unit using amorphous silicon as a TFT and an IC for an external drive circuit, or a display unit and a drive circuit using polycrystalline silicon by a solid phase growth method as a TFT Are known (Japanese Patent Laid-Open No. 6-242433), an integrated type of a display unit and a drive circuit using polycrystalline silicon subjected to excimer laser annealing in a TFT (Japanese Patent Laid-Open No. 7-13030), and the like. Yes.

[0003]

[Problems to be solved by the invention]

However, the above-described conventional amorphous silicon TFT has good productivity, but the electron mobility is 0.5 to 1.0 cm. 2 Since it is as low as around / v · sec, a p-channel MOSTFT (hereinafter referred to as pMOSTFT) cannot be formed. Accordingly, since the peripheral driving unit using the pMOS TFT cannot be formed on the same glass substrate as the display unit, the driver IC is externally mounted and mounted by the TAB method, so that it is difficult to reduce the cost. For this reason, there is a limit to high definition. Furthermore, the electron mobility is 0.5 to 1.0 cm. 2 Since it is as low as around / v · sec, sufficient on-current cannot be obtained, and when used in a display portion, the transistor size inevitably increases, which is disadvantageous for the high aperture ratio of the pixel.

[0004]

The electron mobility of the conventional polycrystalline silicon TFT described above is 70 to 100 cm. 2 Since it can cope with high definition at / v · sec, LCD (Liquid Crystal Display) using a driver-integrated polycrystalline silicon TFT has recently attracted attention. However, in the case of a large LCD of 15 inches or more, the electron mobility of polycrystalline silicon is 70-100 cm. 2 Since / v · sec, the drive capability is insufficient, and eventually an external drive circuit IC is required.

[0005]

In a TFT using polycrystalline silicon formed by solid phase growth, a gate SiO is formed by annealing at 600 ° C. or more for several tens of hours and thermal oxidation at about 1000 ° C. 2 Therefore, it is necessary to employ a semiconductor manufacturing apparatus. Therefore, the wafer size of 8 to 12 inches φ is the limit, and it is necessary to employ high heat-resistant and expensive quartz glass, and it is difficult to reduce the cost. Therefore, it is limited to EVF and data / AV projector applications.

[0006]

Furthermore, in the conventional polycrystalline silicon TFT by excimer laser annealing described above, there are a number of problems such as excimer laser output stability, productivity, increase in device price due to increase in size, and yield / quality deterioration.

[0007]

In particular, when a large glass substrate of 1 m square or the like is used, the above-mentioned problems are expanded, and it is difficult to improve performance / quality and reduce costs.

[0008]

An object of the present invention is to form an active matrix substrate with a built-in high-performance driver by depositing a single crystal silicon thin film having a high electron / hole mobility at a relatively low temperature and uniformly, particularly in a peripheral drive circuit section. An electro-optical device such as a thin film semiconductor device for display used can be manufactured, and an n-channel MOS TFT (hereinafter referred to as an nMOS TFT) or an pMOS TFT having an LDD structure (Lightly doped drain structure) having high switching characteristics and low leakage current. Alternatively, a configuration in which a display unit of a complementary thin film insulated gate field effect transistor (hereinafter referred to as cMOSTFT) with high driving capability and a peripheral driving circuit made of cMOSTFT, nMOSTFT, pMOSTFT, or a mixture thereof is made possible. Realize high quality, high definition, narrow frame, high efficiency, large screen display panel It is possible to use even a large glass substrate with a relatively low strain point, high productivity, no need for expensive manufacturing equipment, cost reduction, and easy threshold adjustment. Therefore, it is to enable high speed operation and large screen by reducing resistance.

[0009]

[Means for Solving the Problems]

That is, according to the present invention, a display unit in which pixel electrodes (for example, a plurality of pixel electrodes arranged in a matrix: the same applies hereinafter) and a peripheral drive circuit unit disposed in the periphery of the display unit are provided in a first manner. A predetermined optical material such as a liquid crystal between the first substrate and the second substrate (i.e., the same applies hereinafter) between the first substrate and the second substrate (i.e., the same applies hereinafter). In each of the manufacturing methods of the electro-optical device and the driving substrate for the electro-optical device,

Forming a step on one surface of the first substrate;

The low melting point gold described later containing silicon on the first substrate including the recess due to the step.

Forming a melt layer of the genus by coating;

Next, the molten liquid layer is subjected to a cooling treatment (preferably a slow cooling treatment). silicon The above

Grapho-epitaxial growth using a step as a seed to deposit a single crystal silicon layer

Process,

This single crystal silicon At least one of active and passive elements by applying a predetermined treatment to the layer

Forming an active element (for example, the single crystal silicon layer is formed into a channel region, a source

A gate insulating film and a gate electrode on the channel region;

And a top gate type thin film transistor having a source and drain electrodes.

A step of forming a transistor (particularly MOSTFT: hereinafter the same) as an active element)

And an electro-optical device, and a method of manufacturing a drive substrate for the electro-optical device. In the present invention, the active element is a concept including an element such as a thin film transistor and other diodes, and the passive element is a concept including a resistor (hereinafter the same). Typical examples of the thin film transistor include a field effect transistor (FET) (which can be either a MOS type or a junction type), and a bipolar transistor, but the present invention is applicable to any transistor. Yes (hereinafter the same). The passive element is a concept including resistance, inductance, capacitance, and the like. For example, the passive element is a single crystal silicon layer (electrode) in which a high dielectric film such as silicon nitride (hereinafter referred to as SiN) is reduced in resistance. There is a capacitance formed by sandwiching.

[0010]

According to the present invention, silicon Such Dissolved Such as indium Low melting point metal melt Apply this melt Then, a single crystal semiconductor thin film such as a single crystal silicon thin film is formed by graphoepitaxial growth using the step formed on the substrate as a seed, and this is formed into a top gate type MOS TFT or a display of a peripheral drive circuit of a drive substrate such as an active matrix substrate. Since it is used for at least an active element such as an active element such as a top gate type MOSTFT of a peripheral driving circuit of an electro-optical device such as a part-peripheral driving circuit integrated type LCD, or a passive element such as resistance, inductance, capacitance, etc. The remarkable effects shown in the following (A) to (F) can be obtained.

[0011]

(A) A step having a predetermined shape / dimension is formed on the substrate, and the bottom corner of the step (bottom angle) is used as a seed for graphoepitaxy growth to be 540 cm. 2 Since a single crystal semiconductor layer such as a single crystal silicon thin film having a high electron mobility of / v · sec or more can be obtained, an electro-optical device such as a display thin film semiconductor device with a built-in high performance driver can be manufactured. In this case, it is preferable that the step is formed as a concave portion whose side surface is perpendicular to the bottom surface in the cross section or is inclined so as to form a base angle of preferably 90 ° or less toward the lower end side.

[0012]

(B) In particular, this single crystal silicon thin film exhibits high electron and hole mobility comparable to that of a single crystal silicon substrate as compared with the conventional amorphous silicon thin film and polycrystalline silicon thin film. The MOSTFT has a display portion composed of an nMOS, pMOSTFT, or cMOSTFT having high switching characteristics (preferably, an LDD (Lightly doped drain) structure that reduces the electric field strength and reduces the leakage current), and a cMOS with high driving capability, or A configuration in which an nMOS, a pMOS TFT, or a peripheral driving circuit unit made of a mixture of these is integrated is possible, and a display panel with high image quality, high definition, narrow frame, high efficiency, and a large screen is realized. In particular, it is difficult to form a pMOS TFT with high hole mobility as a TFT for LCD with polycrystalline silicon, but the single crystal silicon thin film according to the present invention exhibits sufficiently high mobility even with holes. A peripheral drive circuit that can be driven alone or in combination with each other can be manufactured, and a panel in which this is integrated with an nMOS, pMOS, or cMOS LDD structure TFT for display can be realized. In the case of a small to medium panel, there is a possibility that one of a pair of peripheral vertical drive circuits can be omitted.

[0013]

(C) Since the low-melting-point metal melt is prepared at a low temperature (for example, 350 ° C.) and can be formed by coating on a substrate heated to a temperature slightly higher than that, it can be formed at a relatively low temperature (for example, 350 to 400 ° C.), a silicon single crystal film can be formed uniformly. Therefore, a glass substrate or a heat-resistant organic substrate having a relatively low strain point can be easily obtained, and a substrate having good physical properties at a low cost can be used, and the size of the substrate can be increased.

[0014]

(D) Since there is no need for long-term annealing (about 600 ° C., several tens of hours) or excimer laser annealing as in the case of the solid phase growth method, productivity is high and expensive manufacturing equipment is not required. Cost reduction is possible.

[0015]

(E) In this grapho epitaxial growth, a single crystal silicon thin film having a wide range of P-type impurity concentration and high mobility can be easily obtained by adjusting the heating temperature of the substrate, the composition ratio of the melt, the melt temperature, the cooling rate, etc. Therefore, Vth (threshold) adjustment is easy, and high-speed operation and a large screen can be achieved by reducing resistance.

[0016]

(F) When a silicon-containing low-melting-point metal melt layer is formed, growth can be achieved by doping a suitable amount of a

[0017]

DETAILED DESCRIPTION OF THE INVENTION

In the present invention, the step is formed as a concave portion such that the side surface is perpendicular to the bottom surface in the cross section or is inclined so as to form a base angle of preferably 90 ° or less toward the lower end side. It is preferable that the barrier is formed on a film such as SiN (or both of them), and this step serves as a seed for grapho epitaxial growth of the single crystal silicon layer. The step is preferably formed along at least one side of an element region formed by the channel region, the source region, and the drain region of the active element, for example, a thin film transistor. Further, it is preferable that the passive element, for example, it is formed along at least one side of an element region where a resistor is formed.

[0018]

In this case, the first thin film transistor such as the MOSTFT may be provided in the concave portion of the substrate due to the step, but may be provided on the substrate outside the concave portion or both of them.

[0019]

The step is formed by dry etching such as reactive ion etching, and a low-melting-point metal melt containing 2.0% to 0.005%, for example, 1% by weight of silicon is applied to a heated insulating substrate. Then, after holding for a predetermined time (several minutes to several tens of minutes), the cooling process is preferably performed. Thereby, a single crystal silicon film having a thickness of several μm to 0.005 μm, for example, 1 μm can be obtained.

[0020]

Further, an insulating substrate such as a glass substrate or a heat-resistant organic substrate is used as the substrate, and at least one selected from the group consisting of indium, gallium, tin, bismuth, lead, zinc, antimony and aluminum as the low melting point metal. Can be used.

[0021]

In this case, when using indium as the low melting point metal, the melt is applied to the insulating substrate heated to 850 to 1100 ° C., preferably 900 to 950 ° C., and indium gallium or gallium is used as the low melting point metal. When used, the melt can be applied to the insulating substrate heated to 300 to 1100 ° C., desirably 350 to 600 ° C. or 400 to 1100 ° C., desirably 420 to 600 ° C. In addition to a method of heating the entire substrate uniformly using an electric furnace, a lamp, or the like, the substrate can be heated by a method of locally heating only a predetermined place with an optical laser, an electron beam, or the like.

[0022]

As is apparent from the state diagram shown in FIG. 10, the melting point of the low melting point metal containing silicon is lowered according to the proportion of the low melting point metal. When indium is used, an indium melt layer containing silicon (for example, containing 1% by weight) is formed at a substrate temperature of 850 to 1100 ° C. Quartz plate glass can be used as the substrate up to about 1100 ° C. Up to 850 ° C., glass having lower heat resistance than that, for example, crystallized glass can be used. Even when gallium is used, a gallium melt layer containing silicon (for example, containing 1% by weight) can be formed at a substrate temperature of 400 to 1100 ° C. for the same reason as described above.

[0023]

In the latter case (indium gallium silicon or gallium silicon), a glass substrate or a heat-resistant organic substrate having a relatively low strain point can be used as the substrate. 2 Although a semiconductor crystal layer can be formed on the above, such a substrate is inexpensive, can be easily thinned, and can produce a long rolled glass plate or a heat-resistant organic substrate. By using this, it is possible to continuously or discontinuously produce a single crystal silicon thin film by graphoepitaxial growth on a long rolled glass plate or a heat-resistant organic substrate by the above method.

[0024]

In the above-mentioned melt application method, the glass substrate is gradually cooled after being held for a certain time (several minutes to several tens of minutes). In addition, the glass substrate is immersed in the above solution and held for a certain time (several minutes to several tens of minutes). Then, a dipping method of gradually pulling up, or a floating method of slowly cooling by moving the molten liquid or the surface at an appropriate speed may be used. The thickness of the epitaxial growth layer and the carrier impurity concentration can be controlled by the composition, temperature, and pulling speed of the melt. The coating method, dipping method, floating method, etc. can process the substrate continuously or intermittently, so that mass productivity is improved.

[0025]

As described above, since the constituent elements easily diffuse into the upper layer of the glass having a low strain point from the inside of the glass, for the purpose of suppressing this, a thin film of the diffusion barrier layer (for example, silicon nitride:

[0026]

After the single crystal silicon layer is deposited by graphoepitaxial growth using the step as a seed from the low melting point metal in which silicon is dissolved, the low melting point metal layer is dissolved and removed with hydrochloric acid or the like. After that, the single crystal silicon layer can be subjected to a predetermined treatment to produce an active element and a passive element.

[0027]

As described above, the low melting point metal thin film such as indium deposited on the single crystal silicon layer after cooling is dissolved and removed using hydrochloric acid or the like. 16 A semiconductor of a P-type single crystal silicon thin film is formed immediately after the production. This is therefore convenient for the fabrication of nMOS TFTs. However, since an N-type single crystal silicon thin film can be formed on the entire surface or selectively by ion-implanting an appropriate amount of N-type impurities such as phosphorus atoms, the pMOS TFT can also be formed. . For this reason, a cMOS TFT can also be produced. When forming a molten layer of a silicon-containing low-melting-point metal, if a suitable amount of a highly

[0028]

In this way, the single crystal silicon layer that is grapho epitaxially grown on the substrate is applied to the channel region, the source region, and the drain region of the top gate type MOS TFT constituting at least a part of the peripheral drive circuit, and the impurity species in each of these regions And / or its concentration can be controlled.

[0029]

The thin film transistors in the peripheral driver circuit portion and the display portion constitute an n-channel type, p-channel type or complementary type insulated gate field effect transistor. For example, a complementary type and an n-channel type, a complementary type and a p-channel type Or a pair of complementary type, n-channel type and p-channel type. Further, it is preferable that at least a part of the thin film transistor in the peripheral driver circuit portion and / or the display portion has an LDD (Lightly doped drain) structure. Note that the LDD structure may be provided not only between the gate and the drain but also between the gate and the source or between the gate and the source and between the gate and the drain (this is referred to as a double LDD).

[0030]

In particular, the MOSTFT preferably constitutes an nMOS, pMOS or cMOS LDD type TFT in the display section, and a cMOS, nMOS or pMOSTFT or a mixture thereof in the peripheral drive circuit section.

[0031]

The MOS TFT may be provided in the substrate recess due to the step and / or in the vicinity of the recess outside the substrate recess.

[0032]

In this case, a step is formed on one surface of the first substrate, a single crystal, polycrystalline, or amorphous silicon layer is formed on the substrate including the step, and the second thin film transistor is formed of the single crystal. Alternatively, a polycrystalline or amorphous silicon layer may be used as a channel region, a source region, and a drain region, and a top gate type, a bottom gate type, or a dual gate type having a gate portion above and / or below the channel region may be used. Also in this case, the step similar to the above is formed as a concave portion such that the side surface is perpendicular to the bottom surface in the cross section or is inclined so as to form a base angle of preferably 90 ° or less toward the lower end side. It becomes a seed for grapho epitaxial growth of the single crystal silicon layer.

[0033]

The second thin film transistor is provided in and / or outside the substrate recess due to the step formed on the first substrate and / or a film thereon. Similarly to the first thin film transistor, the second thin film transistor is simply formed by grapho epitaxial growth. The source, drain, and channel regions may be formed using a crystalline silicon layer.

[0034]

In the second thin film transistor, as described above, the

[0035]

The source or drain electrode of the first and / or second thin film transistor may be formed on a region including the step.

[0036]

The first thin film transistor is at least a top gate type selected from a top gate type, a bottom gate type, and a dual gate type having a gate portion above and / or below a channel region, and a pixel in the display portion The switching element for switching the electrode may be the top gate type, the bottom gate type, or the dual gate type second thin film transistor.

[0037]

In this case, the gate electrode provided under the channel region is formed of a heat-resistant material, or the upper gate electrode of the second thin film transistor and the gate electrode of the first thin film transistor are formed of a common material. It's okay.

[0038]

In the peripheral driver circuit portion, in addition to the first thin film transistor, a polycrystalline or amorphous silicon layer is used as a channel region, and a top gate type, a bottom gate type or a dual gate having a gate portion above and / or below the channel region. A thin film transistor, or a diode, a resistor, a capacitance, an inductance element, or the like using the single crystal silicon layer, the polycrystalline silicon layer, or the amorphous silicon layer may be provided.

[0039]

The thin film transistors of the peripheral driver circuit unit and / or the display unit may be configured as a single gate or a multi gate.

[0040]

When the n or p channel type thin film transistor of the peripheral driving circuit unit and / or the display unit is a dual gate type, the upper or lower gate electrode is electrically opened or an arbitrary negative voltage (n channel type) Or a positive voltage (in the case of a p-channel type) is applied to operate as a bottom-gate or top-gate thin film transistor.

[0041]

The thin film transistor in the peripheral driver circuit portion is the first thin film transistor of n-channel type, p-channel type or complementary type, and the thin film transistor of the display portion is n-channel type, p. Channel type or complementary type, n channel type, p channel type or complementary type when the polycrystalline silicon layer is used as a channel region, n channel type, p channel type or complementary type when the amorphous silicon layer is used as a channel region It may be.

[0042]

In the present invention, after the single crystal silicon layer is deposited, an upper gate portion composed of a gate insulating film and a gate electrode is formed on the single crystal silicon layer, and the upper gate portion is used as a mask to form 3 The channel region, the source region, and the drain region may be formed by introducing a Group or

[0043]

Further, when the second thin film transistor is a bottom gate type or a dual gate type, a lower gate electrode made of a heat-resistant material is provided below the channel region, and a gate insulating film is formed on the gate electrode to form a lower portion. After the gate portion is formed, the second thin film transistor can be formed through a process common to the first thin film transistor including the step of forming the step. In this case, the upper gate electrode of the second thin film transistor and the gate electrode of the first thin film transistor can be formed of a common material.

[0044]

In addition, after the single crystal silicon layer is formed on the lower gate portion, a

[0045]

Further, after the formation of the single crystal silicon layer, the source and drain regions of the first and second thin film transistors are formed by ion implantation of the impurity element using a resist as a mask, and the activation treatment is performed after the ion implantation, After forming the gate insulating film, a gate electrode of the first thin film transistor and, if necessary, an upper gate electrode of the second thin film transistor may be formed.

[0046]

When the thin film transistor is a top gate type, the source and drain regions of the first and second thin film transistors are formed by ion implantation of the impurity element using a resist as a mask after the formation of the single crystal silicon layer. An activation process is performed, and then each gate portion including the gate insulating film and the gate electrode of the first and second thin film transistors can be formed.

[0047]

Alternatively, when the thin film transistor is a top gate type, each gate insulating film of each of the first and second thin film transistors and each gate electrode made of a heat resistant material are formed after forming the single crystal silicon layer, and each gate portion is formed. The source and drain regions may be formed by ion implantation of the impurity element using these gate portions as a mask, and an activation process may be performed after the ion implantation.

[0048]

Further, the resist mask used when forming the LDD structure is left, and the ion implantation for forming the source region and the drain region can be performed using the resist mask covering the resist mask.

[0049]

Further, the substrate may be optically opaque or transparent, and a reflective or transmissive display unit pixel electrode may be provided.

[0050]

When the display unit has a laminated structure of the pixel electrode and the color filter layer, the color filter is formed on the display array unit, thereby improving the aperture ratio, luminance, and the like of the display panel. Cost reduction is realized by omitting substrates and improving productivity.

[0051]

In this case, when the pixel electrode is a reflective electrode, the resin film is provided with irregularities for obtaining optimum reflection characteristics and viewing angle characteristics, the pixel electrode is provided thereon, and the pixel electrode is a transparent electrode. In this case, the surface is flattened by the transparent flattening film, and the pixel electrode is preferably provided on the flattened surface.

[0052]

The display unit is configured to perform light emission or dimming by being driven by the MOSTFT. For example, a liquid crystal display (LCD), an electroluminescence display (EL), a field emission display (FED), a light emitting polymer display It may be configured as a device (LEPD), a light emitting diode display (LED) or the like. In this case, a plurality of the pixel electrodes may be arranged in a matrix on the display unit, and the switching element may be connected to each of the pixel electrodes.

[0053]

Next, the present invention will be described in more detail with respect to preferred embodiments.

[0054]

<First Embodiment>

1 to 13 show a first embodiment of the present invention.

[0055]

In the present embodiment, a single-crystal silicon layer is grown at a high temperature by graphoepitaxial growth from an indium-silicon melt using the step (concave portion) provided on the heat-resistant substrate as a seed, and a top gate type MOSTFT is formed using this. The present invention relates to a matrix reflection type liquid crystal display (LCD). First, the overall layout of the reflective LCD will be described with reference to FIGS.

[0056]

As shown in FIG. 11, this active matrix reflective LCD has a flat panel structure in which a main substrate 1 (which constitutes an active matrix substrate) and a

[0057]

The switching element of the display unit is an nMOS, pMOS or cMOS according to the present invention, and is composed of a top gate type MOS TFT having an LDD structure. Also, in the peripheral drive circuit section, cMOS, nMOS, pMOSTFT, or a mixture of these is formed as a circuit element of the top gate MOSTFT according to the present invention. One peripheral driving circuit unit is a horizontal driving circuit that supplies a data signal to drive the TFT of each pixel for each horizontal line, and the other peripheral driving circuit unit sets the gate of the TFT of each pixel for each scanning line. The vertical driving circuit is normally provided on both sides of the display portion. These drive circuits can be configured in either a dot sequential analog system or a line sequential digital system.

[0058]

As shown in FIG. 12, the above TFT is arranged at the intersection of the orthogonal gate bus line and the data bus line, and the liquid crystal capacitance (C LC The image information is written in () and the electric charge is held until the next information comes. In this case, since it is not sufficient to hold only the channel resistance of the TFT, a storage capacitor (auxiliary capacitor) (C S ) May be added to compensate for the decrease in the liquid crystal voltage due to the leakage current. Such LCD TFTs require different performance depending on the characteristics of TFTs used in the pixel portion (display portion) and TFTs used in the peripheral drive circuit. In particular, the TFTs in the pixel portion control off current and ensure on current. Is an important issue. For this reason, the display portion is provided with a TFT having an LDD structure as will be described later, thereby reducing the effective electric field applied to the channel region as a structure in which an electric field is unlikely to be applied between the gate and the drain, thereby reducing the off-current. The change of can be made small. However, since the process is complicated, the element size is increased, and problems such as a decrease in on-current occur, an optimum design that matches each purpose of use is required.

[0059]

As usable liquid crystal, TN liquid crystal (nematic liquid crystal used for TN mode of active matrix driving), STN (super twisted nematic), GH (guest / host), PC (phase change), FLC ( Liquid crystals for various modes such as ferroelectric liquid crystal), AFLC (antiferroelectric liquid crystal), and PDLC (polymer dispersed liquid crystal) may be used.

[0060]