JP4359657B2 - 薄膜基板を処理するための方法 - Google Patents

薄膜基板を処理するための方法 Download PDFInfo

- Publication number

- JP4359657B2 JP4359657B2 JP2006508027A JP2006508027A JP4359657B2 JP 4359657 B2 JP4359657 B2 JP 4359657B2 JP 2006508027 A JP2006508027 A JP 2006508027A JP 2006508027 A JP2006508027 A JP 2006508027A JP 4359657 B2 JP4359657 B2 JP 4359657B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- film substrate

- vias

- real

- nanotracks

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/0041—Etching of the substrate by chemical or physical means by plasma etching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y30/00—Nanotechnology for materials or surface science, e.g. nanocomposites

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01K—MEASURING TEMPERATURE; MEASURING QUANTITY OF HEAT; THERMALLY-SENSITIVE ELEMENTS NOT OTHERWISE PROVIDED FOR

- G01K2211/00—Thermometers based on nanotechnology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09609—Via grid, i.e. two-dimensional array of vias or holes in a single plane

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/0979—Redundant conductors or connections, i.e. more than one current path between two points

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/09—Treatments involving charged particles

- H05K2203/092—Particle beam, e.g. using an electron beam or an ion beam

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/002—Etching of the substrate by chemical or physical means by liquid chemical etching

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Plasma & Fusion (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Spectrometry And Color Measurement (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

- Superconductors And Manufacturing Methods Therefor (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Manufacturing Of Printed Wiring (AREA)

- Investigating Or Analyzing Materials By The Use Of Electric Means (AREA)

- Measuring Temperature Or Quantity Of Heat (AREA)

Description

プリント回路カードという表現は主に又は第1には、以下に説明される態様で処理される単一の薄膜基板を意図しているが、第2には、複数のそのように処理された薄膜基板を結合し、それにより、多層プリント回路カードを設けることができるようにすることも妨げられず、その場合には、本発明によって与えられる記載又は助言に従って処理されるプリント回路カードは、そのような層構造に関連する表面の最も外側に被着できることが好都合である。

このようにして製造される上記フレキシブルプリント回路カードはそれぞれ、薄膜基板の中に延在するか、又は薄膜基板を貫通する複数のバイアを含み、或る回路を経由して、向かい合っていない表面に沿って電気的に接続され、そうすることで、1つ又は複数の電気回路を形成できるようにするであろう。

a;バルク材料としての上記薄膜基板の全体又は少なくとも或る特定の選択された表面部分がたとえばイオンの形をとる加速された粒子で処理されるようにすること、

b;薄膜基板の表面上で選択される上記表面部分に衝突するときの上記粒子の速度と、それらの粒子の相互に関連する質量とを選択して、それらの粒子に関連する、又は割り当てられる運動エネルギーが、少なくともいくつかの粒子が十分な確実度で、上記薄膜基板を通り抜けて、貫通することになるほど十分に高く選択されるようにし、それにより、いわゆるナノワイヤを後に形成し、且つ上記薄膜基板を横断する、潜在ナノトラックと見なされるトラックを形成できるようにすること、

c;既知の態様と同じように、上記ナノワイヤ又は選択された潜在横断ナノトラックを処理できるようにし、それにより、実在し、適当に組み合わせられたナノトラックを形成し、それらの多くが薄膜基板を完全に横断するようにすること、

d;薄膜基板を横断するか、又は薄膜基板の中に延在(又は薄膜基板を貫通)するバイアを形成するために、良好又は或る程度良好な導電性を有する材料で示唆されるような材料で、それ自体が知られている態様で、少なくとも選択された実在ナノトラックを満たすことができるようにすること、及び

e;良好又は或る程度良好な導電性を有する、薄膜基板の向かい合っていない表面に被着される、1つ又は好ましくは2つの材料列によって、表面に延伸する電気回路を経由して、複数の上記貫通バイアを電気的に相互接続できるようにすることを含む。

潜在ナノトラック又はナノワイヤは、バルク材料として用いられる薄膜基板を貫通し、それにより基板の中に延在するか、又は基板を貫通する概ね垂直で、たとえば異方性のナノワイヤを形成する、加速された粒子、好ましくはイオンによって引き起こされる細いワイヤ状の材料の改質を示すことを意図しており、そのナノワイヤの材料構造は、薄膜基板の材料構造の残りの部分よりも高いエネルギーを有する材料構造に変化しており、変化した材料構造は結果として、薄膜基板の中を粒子又はイオンが移動する方向において、エッチング、たとえば化学エッチングされやすくなっている。

前置きとして触れておくと、絶縁性材料の中を貫通するか、又は貫通した加速された粒子又はイオンが、ナノトラック又はナノワイヤを形成することについての理解は1960年代には既に得られており、利用されていたが、それは、これらが地質学及び宇宙学において重要であると見なされていたからであり、宇宙粒子が地球の大気を通って到達すると、多くの絶縁性材料内に永久トラックが形成され、それと同じ技術が本発明においても用いられるということに言及することができる。

本発明に関連し、好都合な応用形態を期待することができる技術分野が、特許文献1に図示され、開示される。

数ある中でも、気体セル(2)の中を通り抜ける、赤外線光線のような電磁波を検出できるように意図される、気体センサに関連する検出器を製造できるようにするための方法が提供され、上記気体セルは、測定又は評価の対象となる気体(G)の量を収容することができるように構成される空洞(21)を形成し、上記電磁波に対して高い反射率を有する表面を形成できるようにするために、上記気体セル(2)又は空洞(21)内の壁部(21C、21D、21E)を形成する表面又は表面の一部が、1つ又は複数の異なる金属層(M1、M2)でコーティングされる。

上記基層(B)は、検出器に関連する回路構成(1b)を形成するように構成される1つ又は複数の付加的な部分も有するべきである。

技術分野に適用することができる。

アが、指定された表面に関連する回路を介して適当に組み合わせられるようにすることの重要性とそれに関連する利点を理解できるようにすることに技術的課題がある。

される材料によって形成される電気回路によって、複数の第1のマイクロバイア及び複数の第2のマイクロバイアが電気的に相互接続されるようにすることの重要性とそれに関連する利点を理解できるようにすることに技術的課題があり、その場合、同様に、電気的熱電対以外の電気的接続のために、電気回路を介して上記材料を利用し、形成することができる。

さらに、上記薄膜基板は芳香族ポリマー材料から構成され、その場合、開放ナノトラック又は実在ナノトラックを形成するために化学試薬を利用している最中に、アルカリ性及び/又は酸化する湿潤環境内でエッチングを実行することができ、選択された粒子又はイオン、並びに薄膜基板内の選択された材料及びその割り当てられた厚みに応じて、運動エネルギーはイオン当たり200〜7000MeVになるように選択されるべきであることが教示及び示唆される。

[利点]

第一に本発明の特徴及びそれにより提供される特別な意味のある特徴と見なすことができる利点は、このようにして、電気的熱電対及び/又は1つ又は複数の回路構成のような、処理された薄膜基板によって、そのような熱電対が、スペクトル分析用に構成される検出器内に、1つ又は複数の信号受信機のような1つ又は複数の回路構成として収容されるようになる状況を作り出すことができるようにするために、複数の状況が作り出されたことである。

本明細書で、単に本発明の実施形態を例示するにすぎないが、現在提案されている実施形態とともに、本発明に適合するように薄膜基板を処理できるようにするために、本発明に関連付けられる意味のある特徴を有する従来の既知の方法が、より詳しく説明されることになり、その際、添付の図面が参照される。

、電気回路構成を形成できるようにするための提案される一連のステップが図1に示される。

図1bは、薄膜基板1の上側1' 及び下側1''がそれぞれ1つの銅層12及び13をコーティングされており、上側銅層12が開口部12aを設けられていることを示す

。

図1cでは、実在ナノトラック1eが形成されるように、ナノワイヤ1dが処理される。

小孔又は実在ナノトラック1eは、下側層1''に向かって、薄膜基板1の全厚を貫通して延在するので、この層は支持部分を構成することができ、別法では、粘着テープが用いられる。

図1eでは、電着による材料が上側銅層に達する前に、上側銅層1' が除去されていることが示される。

その後、電着は続く。

図1fは、本明細書で、上記スルーホールに関連付けられるバイア「V1」のうちの1つが、薄膜基板の向かい合っていない表面に回路として被着され、且つ導電性を有する1つ又は2つの材料によって相互接続されることができることも示す。

本明細書で、上側(及び下側)の上に必要な回路を等方性ウエットエッチングによって形成することができる。

[現時点で提案される実施形態の説明]

さらに前置きとして、本発明に関連付けられる意味のある特徴を有し、且つ添付の図面に示される図4〜図10によって明らかにされる、現時点で提案される実施形態に関する以下の説明では、主に本発明の根本的な概念を明らかにできるように、用語及び特定の術語が選択されていることを強調しておきたい。

したがって、本発明は、既知の実験から、所望の材料間の所望の熱電気特性を決定できるようになることに基づいている。

直列に接続される複数のそのような個々の熱電対100を並列に接続することも妨げられない。

参照符号10a' のように、薄膜基板10上で電気的熱電対100の表面部分10aを繰り返すことができること、及びそれにより1つの同じ薄膜基板10上で2つの電気的熱電対100及び100' を提供でき、当該熱電対100及び100' はそれぞれ、スペクトル分析中に異なる光線又は波を検出するために用いることができ、熱電対100は本来の測定のために用いることができ、熱電対100' は基準測定として用いることができ、いずれの信号も、上記接続ワイヤを介して、それ自体が知られているタイプの電子値計算回路に供給されることは当業者には明らかである。

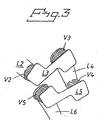

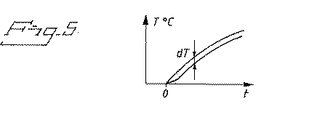

図5を参照すると、スペクトル分析用の検出器のために提案される熱電対において、ホットジョイントに割り当てられる温度及びコールドジョイントに割り当てられる温度のための温度−時間グラフが示されており、指定される温度差「dT」は、少なくとも以下の要因によるものと見なすことができる。

a)上側表面10aに対して入射する光波の光強度。

b)2つの連続するパルス間の光強度の周波数。

c)光強度の上昇勾配特性。

d)薄膜基板10を横断するマイクロバイアの長さ「d」。

e)薄膜基板10を横断するマイクロバイアの計算された太さ「t」。

f)隣接するマイクロバイア間の距離。ただし、距離「a」(図3)はバイア「V2」と「V3」との間の距離に相当し、一方、距離「a1」はバイア「V2」と「V4」との間の距離に相当する。

g)マイクロバイアとバルク材料との間に生じる熱伝達。

h)バルク材料又は薄膜基板10において選択される材料。

i)下側表面10bから基層103への選択された熱伝導。

j)個々のマイクロバイアを形成する際に並列に接続される実在ナノトラックの数。

k)上記実在ナノトラックの計算された太さ。

表面10a上で発生する熱が増加すると、熱伝導によって表面10bまで長い距離を通

るので、マイクロバイア「V10」及び他のマイクロバイアの長さ「d」が長くなると、明らかに大きな信号「V」を与えることができるようになるだけでなく、発生する温度差の遅延が大きくなるのがごく自然である。

いくつかのより細いマイクロバイアは、同じ断面積を有する太いマイクロバイアよりも、バルク材料への熱伝導が大きい。単一の太いマイクロバイアは、いくつかの細いマイクロバイアよりも低い温度勾配を与える。

指定されたように直列に相互接続されるマイクロバイアの数が増えると、マイクロバイアが少ない場合よりも出力信号が高くなる。

しかしながら、パルスによってランプが制御され、それによりランプが、放射される光パルスの選択された周波数を割り当てられる場合には、この周波数は、100μmの厚み「d」を有する薄膜基板において0.1秒の間に現われるように選択されるべきであることがわかっている。

図7には、薄膜基板の高さ寸法又は厚み「d」が電気的熱電対からの出力信号に如何に関連付けられ、また用いられる光源又はランプの繰返し周波数に如何に関連付けられるかに関するグラフが示される。

当然、本発明の範囲内には、マイクロバイアにおいて、及び/又は表面部分10a及び10bのために、それぞれ十分に導電性の材料又は半導電性の材料を利用できるようにし、それにより、少なくとも2つの異なる材料を利用しながら、種々の回路構成を構成できるようにすることが含まれる。

図8では、薄膜として構造化されるバルク材料によって、少なくとも2つ、本明細書で

は金属材料M1、M2及びM3によって示される3つの異なる材料を利用して、熱電対又は別の回路構成を形成できるようにするために、図1に示される方法に類似の、いくつかの工程ステップ「A」、「B」〜「G」に分割される方法の一連のステップが示される。

図8Bは、実在ナノトラック80dを配設するために、図8Aにおいて形成されたナノワイヤ80bが工程ステップ内のエッチング工程にかけられることを示す。

図8Cでは、図8Bに従って処理される材料80が、さらに別の工程ステップにおいて金属層80eを設けられることが示される。

図8Dは、マスキング又は保護薄膜としての役割を果たすレジスト80iが金属層80eに被着されていることも示す。

図8Fは、薄膜80f' が1つの工程ステップにおいて除去されており、それに続く工程ステップにおいて、露出した、満たされたナノトラック80h及び80h' をそれぞれマイクロバイアとして覆うために、開口部80kを備えるマスキングを有する新たなフォトレジスト80j、すなわち乾燥塗膜が上側表面80cに被着され、電気めっきによって、「L10」によって示されるような、必要とされる回路を形成する金属材料M3が被着されることを示すことを意図している。

ることを示す。

図9Bは、選択された実在ナノトラック80dを配設するために、図9Aにおいて形成されたナノワイヤ80bがフォトレジスト80fによって覆われ、マスキング及びその開口部80gによって、それらのナノワイヤが、図9Cによる1つの工程ステップ内のエッチング工程にかけられることを示す。

図9B及び図9Cでは、さらに別の工程ステップにおいて、材料80が金属層80eを設けられることが示される。

図9Eは、後続の工程ステップにおいて、乾燥塗膜80fが除去され、露出した3つの図示される他の実在ナノトラック80h' を覆うために、開口部80g' を有するフォトレジスト、乾燥塗膜80f''が上側表面80cに被着されることを示す。

図8F及び図8Gに従って先に示された工程ステップによって図9Fが達成されるので、これ以上は図示されない。

当然、本発明は例として先に与えられた実施形態には限定されず、添付の特許請求の範囲に示される、本発明による包括的な概念の範囲内で変更することができる。

Claims (26)

- プリント回路カード又はプリント回路基板を形成するための芳香族ポリマー材料からなる薄膜基板において、前記薄膜基板には、前記薄膜基板を貫通するとともに、電気回路を形成すべく互いに対向する表面に沿って電気接続されている複数のマイクロバイアを設けるために、

a)前記薄膜基板を貫通している潜在ナノトラックを形成するために、前記薄膜基板の少なくとも選択された表面部分に加速されたイオンを照射する処理であって、前記イオンの少なくとも80%を確実に前記薄膜基板に貫通させる運動エネルギーを前記イオンが有するように、前記運動エネルギーが、イオン当たり200〜7000MeVになるように前記選択された表面部分に衝突するときの前記イオンの速度、及び質量が選択されている、加速されたイオンの照射処理と、

b)前記薄膜基板を貫通する実在ナノトラックを形成するために、前記潜在ナノトラックのうちの選択されたものに対して、アルカリ性試薬及び酸化剤試薬のうちの少なくとも一方の化学試薬を利用するウェットエッチングを行う処理と、

c)前記薄膜基板の前記互いに対向する表面にて、選択された導電性を有する1つ又は2つの材料によって電気接続されるとともに、スルーホールの役割を果たす、前記マイクロバイアを形成するために、選択された導電性を有する材料を前記実在ナノトラックに充填する処理であって、第1のバイア(V10、V30、V50)と呼ばれる第1の数のバイアを形成するために、第1の数の前記実在ナノトラックに、選択された電気的特性を有する第1の材料(M1)を充填し、及び、第2のバイア(V20、V40、V60)と呼ばれる第2の数のバイアを形成するために、第2の数の前記実在ナノトラックに、選択された電気的特性を有する第2の材料(M2)を充填する処理とが行われており、

前記第1のバイア(V10、V30、V50)及び第2のバイア(V20、V40、V60)にそれぞれ充填される、前記第1の材料(M1)及び前記第2の材料(M2)は互いに異なる電気的特性を有するように選択され、前記薄膜基板の表面に被着される材料は、前記第1のバイアと前記第2のバイアを電気接続するために設けられ、直列接続に含まれる最初のバイア(V10)及び最後のバイア(V60)は、熱電対及び回路構成のうちの少なくとも一方を提供するために他の素子に適切に接続される、処理された薄膜基板。 - 熱電対を備えている前記薄膜基板が、スペクトル分析用に構成される検出器内に信号受

信機として収容される、請求項1に記載の処理された薄膜基板。 - 前記「a」の処理では、前記薄膜基板全体の外側表面が、加速された重イオンで処理される、請求項1に記載の処理された薄膜基板。

- 前記「b」の処理では、マスキング工程によって、前記実在ナノトラックが形成される、請求項1に記載の処理された薄膜基板。

- 前記「c」の処理では、第1のバイアを形成するために、選択された実在ナノトラックに第1の材料を充填する、請求項1に記載の処理された薄膜基板。

- 前記「c」の処理では、第2のバイアを形成するために、第2の選択された実在ナノトラックに第2の材料を充填する、請求項1に記載の処理された薄膜基板。

- 前記「c」の処理では、複数の第1のバイア及び複数の第2のバイアが、マスキング工程によって前記薄膜基板の前記2つの表面のうちの一方に被着される材料によって電気接続される、請求項1に記載の処理された薄膜基板。

- 前記「c」の処理では、複数の第1のバイア及び複数の第2のバイアが、マスキング工程によって前記薄膜基板の前記2つの表面のうちの第2の表面に被着される材料によって電気的に相互接続される、請求項1に記載の処理された薄膜基板。

- 前記「a」の処理では、画定された潜在ナノトラックが、異方性材料から成るナノワイヤとして前記薄膜基板のバルク材料内に形成され、前記異方性材料は実在ナノトラックを形成するために化学エッチングされやすいものである、請求項1に記載の処理された薄膜基板。

- 前記薄膜基板は200〜30μmの厚みを有する、請求項1に記載の処理された薄膜基板。

- 前記「a」の処理では、前記ナノワイヤは、「クーロン」爆発及び熱過渡現象のうちの少なくとも一方によって設けられる、請求項1に記載の処理された薄膜基板。

- 前記「b」の処理では、次亜塩素酸ナトリウム含有溶液又は酸化カリウム含有溶液が用いられる、請求項1に記載の処理された薄膜基板。

- 前記実在ナノトラックは、内側トラック表面を濡らすために、前記導電性を有する材料を充填する処理の前にエタノールにさらされる、請求項1に記載の処理された薄膜基板。

- プリント回路カード又はプリント回路基板を形成するための芳香族ポリマー材料からなる薄膜基板において、前記薄膜基板を貫通するとともに、互いに対向する表面に沿って電気接続される複数のマイクロバイアを設けることによって、電気回路を形成するための、前記薄膜基板の製造方法において、

a)前記薄膜基板を貫通している潜在ナノトラックを形成するために、前記薄膜基板の少なくとも選択された表面部分に加速されたイオンを照射するステップであって、前記イオンの少なくとも80%を確実に前記薄膜基板に貫通させる運動エネルギーを前記イオンが有するように、前記運動エネルギーが、イオンあたり200〜7000MeVになるように前記選択された表面部分に衝突するときの前記イオンの速度、及び質量を選択されている、加速されたイオンの照射ステップと、

b)前記薄膜基板を貫通する実在ナノトラックを形成するために、前記潜在ナノトラックのうちの選択されたものに対して、アルカリ性試薬及び酸化剤試薬のうちの少なくとも一方の化学試薬を利用するウェットエッチングを行うステップと、

c)前記薄膜基板の前記互いに対向する表面にて、選択された導電性を有する1つ又は2つの材料によって電気接続されるとともに、スルーホールの役割を果たす、前記マイクロバイアを形成するために、選択された導電性を有する材料を前記実在ナノトラックに充填する処理であって、第1のバイア(V10、V30、V50)と呼ばれる第1の数のバイアを形成するために、第1の数の前記実在ナノトラックに、選択された電気的特性を有する第1の材料(M1)を充填し、及び、第2のバイア(V20、V40、V60)と呼ばれる第2の数のバイアを形成するために、第2の数の前記実在ナノトラックに、選択された電気的特性を有する第2の材料(M2)を充填するステップとを備え、

前記第1のバイア(V10、V30、V50)及び第2のバイア(V20、V40、V60)にそれぞれ充填される、前記第1の材料(M1)及び前記第2の材料(M2)は互いに異なる電気的特性を有するように選択され、前記薄膜基板の表面に被着される材料は、前記第1のバイアと前記第2のバイアを電気接続するために設けられ、直列接続に含まれる最初のバイア(V10)及び最後のバイア(V60)は、熱電対及び回路構成のうちの少なくとも一方を提供するために他の素子に適切に接続される、薄膜基板の製造方法。 - 熱電対を備えている薄膜基板が、スペクトル分析用に構成される検出器内に信号受信機として収容される、請求項14に記載の薄膜基板の製造方法。

- 前記「a」のステップにおいて、前記薄膜基板全体の外側表面が、加速された重イオンで処理される、請求項14に記載の薄膜基板の製造方法。

- 前記「b」のステップにおいて、マスキング工程によって前記実在ナノトラックが形成される、請求項14に記載の薄膜基板の製造方法。

- 前記「c」のステップにおいて、第1のバイアを形成するために、選択された実在ナノトラックに第1の材料を充填する、請求項14に記載の薄膜基板の製造方法。

- 前記「c」のステップにおいて、第2のバイアを形成するために、第2の選択された実在ナノトラックに第2の材料を充填する、請求項14に記載の薄膜基板の製造方法。

- 前記「c」のステップにおいて、複数の第1のバイア及び複数の第2のバイアが、マスキング工程によって前記薄膜基板の前記2つの表面のうちの一方に被着される材料によって電気接続される、請求項14に記載の薄膜基板の製造方法。

- 前記「c」のステップにおいて、複数の第1のバイア及び複数の第2のバイアが、マスキング工程によって前記薄膜基板の前記2つの表面のうちの第2の表面に被着される材料によって電気接続される、請求項14に記載の薄膜基板の製造方法。

- 前記「a」のステップにおいて、画定された潜在ナノトラックが異方性材料からなるナノワイヤとして前記薄膜基板のバルク材料内に形成され、前記異方性材料は、実在ナノトラックを形成するために化学エッチングされやすいものである、請求項14に記載の薄膜基板の製造方法。

- 前記薄膜基板は200〜30μmの厚みを有する、請求項14に記載の薄膜基板の製造方法。

- 前記「a」のステップにおいて、前記ナノワイヤは、「クーロン」爆発及び熱過渡現象のうちの少なくとも一方によって設けられる、請求項14に記載の薄膜基板の製造方法。

- 前記「b」のステップにおいて、次亜塩素酸ナトリウム含有溶液又は酸化カリウム含有溶液が用いられる、請求項14に記載の薄膜基板の製造方法。

- 前記実在ナノトラックは、内側トラック表面を濡らすために、前記導電性を有する材料を充填する処理の前にエタノールにさらされる、請求項14に記載の薄膜基板の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| SE0301238A SE526006C2 (sv) | 2003-04-29 | 2003-04-29 | Behandlat tunnfilmssubstrat |

| PCT/SE2004/000606 WO2004098256A1 (en) | 2003-04-29 | 2004-04-21 | A method for processing a thin film substrate |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007529101A JP2007529101A (ja) | 2007-10-18 |

| JP4359657B2 true JP4359657B2 (ja) | 2009-11-04 |

Family

ID=20291147

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006508027A Expired - Fee Related JP4359657B2 (ja) | 2003-04-29 | 2004-04-21 | 薄膜基板を処理するための方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US7176578B2 (ja) |

| EP (1) | EP1621054B1 (ja) |

| JP (1) | JP4359657B2 (ja) |

| KR (1) | KR101055600B1 (ja) |

| CN (1) | CN100521876C (ja) |

| AT (1) | ATE524956T1 (ja) |

| AU (1) | AU2004234763B2 (ja) |

| CA (1) | CA2523971A1 (ja) |

| SE (1) | SE526006C2 (ja) |

| WO (1) | WO2004098256A1 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1832146A1 (de) * | 2004-12-28 | 2007-09-12 | Siemens Home and Office Communication Devices GmbH & Co. KG | Halbzeug sowie trägerkomponente auf der basis dieses halbzeugs |

| JP4344954B2 (ja) | 2006-10-03 | 2009-10-14 | セイコーエプソン株式会社 | 素子基板の製造方法 |

| WO2008063125A1 (en) * | 2006-11-20 | 2008-05-29 | Senseair Ab | A process for treating a flexible thin film substrate, in the form of a dielectric plastic foil, and a thin film substrate thus formed |

| US20090162666A1 (en) * | 2007-12-20 | 2009-06-25 | Palo Alto Research Center Incorporated | Curable flexible material |

| US20090223700A1 (en) * | 2008-03-05 | 2009-09-10 | Honeywell International Inc. | Thin flexible circuits |

| US7884488B2 (en) * | 2008-05-01 | 2011-02-08 | Qimonda Ag | Semiconductor component with improved contact pad and method for forming the same |

| US8026567B2 (en) * | 2008-12-22 | 2011-09-27 | Taiwan Semiconductor Manufactuirng Co., Ltd. | Thermoelectric cooler for semiconductor devices with TSV |

| JP2011233714A (ja) * | 2010-04-27 | 2011-11-17 | Canon Inc | 半導体素子 |

| US20150035162A1 (en) * | 2013-08-02 | 2015-02-05 | Qualcomm Incorporated | Inductive device that includes conductive via and metal layer |

| SE541450C2 (en) | 2018-02-19 | 2019-10-08 | Jondetech Sensors Ab Publ | Overheating alarm device for cell phone charger or similar device |

| SE543173C2 (en) | 2018-07-02 | 2020-10-20 | Jondetech Sensors Ab Publ | Adapter device with infrared sensor and heat protection switch |

| US20200361782A1 (en) * | 2019-05-16 | 2020-11-19 | Sciosense B.V. | Photo-annealing in Metal Oxide Sensors |

| US11662109B2 (en) | 2019-06-05 | 2023-05-30 | Carrier Corporation | Enclosure for gas detector |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE521415C2 (sv) * | 1998-02-17 | 2003-10-28 | Hans Goeran Evald Martin | Metod för att framställa en gassensortillhörig detektor, samt en detektor framställd enligt metoden |

| JP3655242B2 (ja) * | 2002-01-04 | 2005-06-02 | 株式会社東芝 | 半導体パッケージ及び半導体実装装置 |

| US6891266B2 (en) * | 2002-02-14 | 2005-05-10 | Mia-Com | RF transition for an area array package |

| TWI256719B (en) * | 2002-03-06 | 2006-06-11 | Via Tech Inc | Semiconductor device package module and manufacturing method thereof |

-

2003

- 2003-04-29 SE SE0301238A patent/SE526006C2/sv not_active IP Right Cessation

-

2004

- 2004-04-21 CN CNB2004800116430A patent/CN100521876C/zh not_active Expired - Lifetime

- 2004-04-21 JP JP2006508027A patent/JP4359657B2/ja not_active Expired - Fee Related

- 2004-04-21 AT AT04728728T patent/ATE524956T1/de not_active IP Right Cessation

- 2004-04-21 CA CA002523971A patent/CA2523971A1/en not_active Abandoned

- 2004-04-21 EP EP04728728A patent/EP1621054B1/en not_active Expired - Lifetime

- 2004-04-21 AU AU2004234763A patent/AU2004234763B2/en not_active Expired

- 2004-04-21 KR KR1020057020583A patent/KR101055600B1/ko active IP Right Grant

- 2004-04-21 WO PCT/SE2004/000606 patent/WO2004098256A1/en active Application Filing

-

2005

- 2005-10-26 US US11/258,763 patent/US7176578B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CA2523971A1 (en) | 2004-11-11 |

| AU2004234763A1 (en) | 2004-11-11 |

| WO2004098256A1 (en) | 2004-11-11 |

| ATE524956T1 (de) | 2011-09-15 |

| EP1621054A1 (en) | 2006-02-01 |

| KR20060016761A (ko) | 2006-02-22 |

| JP2007529101A (ja) | 2007-10-18 |

| SE0301238L (sv) | 2004-10-30 |

| EP1621054B1 (en) | 2011-09-14 |

| SE0301238D0 (sv) | 2003-04-29 |

| AU2004234763B2 (en) | 2008-07-24 |

| CN1781350A (zh) | 2006-05-31 |

| SE526006C2 (sv) | 2005-06-14 |

| US7176578B2 (en) | 2007-02-13 |

| CN100521876C (zh) | 2009-07-29 |

| KR101055600B1 (ko) | 2011-08-09 |

| US20060071323A1 (en) | 2006-04-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4359657B2 (ja) | 薄膜基板を処理するための方法 | |

| Huu et al. | Flexible thermoelectric power generator with Y-type structure using electrochemical deposition process | |

| Mersini et al. | Relic dark energy from the trans-Planckian regime | |

| JPH02123738A (ja) | 基板を貫く電気接続部の作製方法 | |

| JP2006147970A (ja) | 多層配線基板およびその製造方法 | |

| US20170262259A1 (en) | Method for generating random numbers and assoicated random number generator | |

| CN105122449A (zh) | 包括氧化层的低成本中介体 | |

| Yousef et al. | Vertical thermopiles embedded in a polyimide-based flexible printed circuit board | |

| CN107917754A (zh) | 热电式激光功率探头及其制作方法 | |

| Lindeberg et al. | A PCB-like process for vertically configured thermopiles | |

| Kim et al. | Modified shielding effectiveness equation for novel multilayered waveguide-below-cutoff array | |

| US9439295B2 (en) | Electrically insulating elements and electrically conductive elements formed from elements having different oxidation behaviors | |

| Tsukamoto et al. | Printable on-chip micro battery for disposal bio-sensing device | |

| Yousef et al. | Reliable small via interconnects made of multiple sub-micron wires in flexible PCB | |

| RU2462011C1 (ru) | Способ изготовления многослойных печатных плат | |

| RU2356194C1 (ru) | Способ изготовления гибких печатных плат | |

| Morris et al. | The'Baldwin Effect'in Wolf-Rayet stars | |

| JP5939085B2 (ja) | 温度差発電ユニット | |

| Chattopadhyay et al. | Participation in the compressed baryonic matter experiment at FAIR | |

| Frankel et al. | Search for ultradense nuclei in relativistic collisions of Ar on Ca, U, and Pb | |

| WO2008063125A1 (en) | A process for treating a flexible thin film substrate, in the form of a dielectric plastic foil, and a thin film substrate thus formed | |

| JP2024029824A (ja) | 電磁波吸収構造体および熱電変換素子 | |

| JP2002368383A (ja) | 複合部材の製造方法、複合部材製造用マスク基板、複合部材、および配線基板 | |

| Yousef et al. | Ion track enabled multiple wire microvia interconnects in printed circuit boards | |

| Fang | Suspended Trace Air-Gap Resonators for Low Loss Superconducting Circuits |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080819 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081119 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090219 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090616 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090625 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20090715 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090715 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4359657 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120821 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130821 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |