JP4344088B2 - 基板の一次側と二次側における同一の接続点レイアウトのためのルーティングトポロジー - Google Patents

基板の一次側と二次側における同一の接続点レイアウトのためのルーティングトポロジー Download PDFInfo

- Publication number

- JP4344088B2 JP4344088B2 JP2000531862A JP2000531862A JP4344088B2 JP 4344088 B2 JP4344088 B2 JP 4344088B2 JP 2000531862 A JP2000531862 A JP 2000531862A JP 2000531862 A JP2000531862 A JP 2000531862A JP 4344088 B2 JP4344088 B2 JP 4344088B2

- Authority

- JP

- Japan

- Prior art keywords

- connection point

- layout

- connection points

- chip

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

- G11C5/063—Voltage and signal distribution in integrated semi-conductor memory access lines, e.g. word-line, bit-line, cross-over resistance, propagation delay

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/181—Printed circuits structurally associated with non-printed electric components associated with surface mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10159—Memory

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10545—Related components mounted on both sides of the PCB

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Combinations Of Printed Boards (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

(技術分野)

本発明はトレース・ルーティング・トポロジーに関し、より厳密には基板の一次側と二次側上で同一の接続点レイアウトを可能にするトポロジーに関する。

【0002】

(背景技術)

マイクロプロセッサのようないくつかのプロセッサはそのプロセッサのプロセッサチップが使用するデータを記憶するために、外部キャッシュチップ(L2キャッシュと呼ばれることもある)を使用する。キャッシュチップはプリント基板などの基板に取り付けられ、高速バスを通してプロセッサコアチップに接続される。

【0003】

例えばインテルコーポレーションが製造するペンティアム(登録商標)IIプロセッサはプロセッサチップとキャッシュチップが各々接続される基板を含む。プロセッサチップとキャッシュチップを基板に接続するためにプロセッサチップの接続点とキャッシュチップの接続点とのそれぞれが一致する接続点を基板に設けている。基板は複数の層を含む。1つのチップの様々な接続点を別のチップの様々な接続点に連結するためにトレースが基板の接続点に接続される。トレースがそれぞれ一緒にコネクタに入ってくるのを避けるために、トレースは特定の形状に経路が決められる。トレースをお互いに接触させないように、バイアを通って接続されている様々な層を通るようにトレースの経路を決めることができる。基板はマザーボードに取り付けることができるコネクタに、1つのエッジコネクタのゴールドフィンガーを通じて接続される。

【0004】

1つのチップ上の接続点は、中間接続点から実質的に等距離にあるものを含む複数の分岐トレースを通って、基板の同じ側で同じ相対的なレイアウト位置にある1個より多いチップ上の接続点に連結されてきた。

ペンティアム(登録商標)IIプロセッサに使われているような基板は複数の層を有する。各層は複雑さと費用を追加する。更にバイアの追加は複雑さ(例えばトレースのルーティングチャンネルをブロックすることにより)と費用を追加する。

【0005】

(発明の開示)

本発明の一態様では、本発明は多層基板を有する。基板は、第1の接続点を含むような第1の接続点グループを持ち、第1のチップを接合する第1のレイアウトを持つような一次側を有する。基板はまた、第2の接続点を含むような第2の接続点グループを持ち、第2のチップを接合するために第1のレイアウトと同一のレイアウトを持つような二次側を有する。基板はまた、各々が実質的に同じ電気的長さを持つ第1と第2の分岐トレースを通って第1と第2の接続点に連結されている中間接続点を有する。

【0006】

本発明は以下に述べる詳細な説明と添付の本発明の実施形態の図面によってより十分に理解されるであろう。しかし、それらは本発明をその特定の説明されている実施形態に限定すると解釈されるべきではなく、単に説明と理解のためである。

【0007】

(好ましい実施形態の詳細な説明)

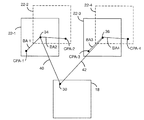

図1および図2において、プリント基板である基板10は一次側12と二次側14を有する。基板10は5つの接続点グループを有する、即ち、接続点18のグループ、接続点22−1、22−2、22−3および22−4のグループである。単に例として挙げると、その接続点はバイア上のパッドでよく、また他の導体でもよい。

【0008】

1つの例として、基板10は接続点18のグループに接続されるプロセッサチップを有するプロセッサの一部であることができる。そのプロセッサは、それぞれが接続点22−1、22−2、22−3および22−4の4つのグループのうちのどれか1つに接続される4つのキャッシュチップを有する。接続点のそれぞれのグループはレイアウトを有する。チップもまた接続点のレイアウトを持つ。チップの接続点はピン、パッド、または他の導体である。接続点22−1、22−2、22−3および22−4のグループのレイアウトを同一にすることにより、同じキャッシュチップを基板10の一次側および二次側の両方に使うことができる。従ってキャッシュチップは1つのタイプのみ製造されればよい(すなわち、キャッシュチップのたった1つの導体ポイント・レイアウトのみが必要である)。ここに規定するように、もし2つの接続点グループの接続点レイアウトが同一であれば、同一のチップが接続点グループのどちらにも同じように働く。

【0009】

特に以下の接続点を具体的に説明する。即ち接続点18のグループの接続点30、接続点22−1のグループの接続点CPA−1とCPB−1、接続点22−2のグループの接続点CPA−2とCPB−2、接続点22−3のグループの接続点CPA−3とCPB−3、接続点22−4のグループの接続点CPA−4とCPB−4、および接続点32である。

【0010】

基板10は例えばゴールドフィンガー接続の6つのグループを有する。即ち、16A、16B、16C、16D、16E、および16Fである。1つの例として、接続点32はゴールドフィンガー接続の1つであるか、または1つ或いはそれ以上のゴールドフィンガー接続に接続される。

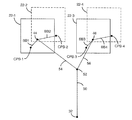

基板10はバイア34、36、44、および46を有する。図示の実施形態において、バイアは基板10の各層を通り抜ける。他の実施形態では、バイアは各層を通るようには延びていない。バイア34、36、44、および46は中間接続点と見ることができる。しかしながら図示の実施形態では、バイア34、36、44、および46はチップと直接接合することがないのに対し、接続点CPA−1、CPA−2などは直接接合する。

【0011】

図1,図2,および図3において、基本トレース40は接続点30とバイア34の間で連結されている。基本トレース42は接続点30とバイア36の間で連結されている。基本トレース40と42は実質上同じ電気的長さを持つべきである。電気的長さはフライト時間である。等しい物理的長さは等しい電気的長さを与えるであろう。実質的に等しい電気的長さを持つ目的はチップ間信号のためのタイミング許容値を小さくすることである。電気的長さが実質的に同じでなければならないその程度は、少なくとも部分的には実装によって変わる許容値に依存する。その程度はまた、他のトレース(以下に述べる)がいかに近似した実質的に同一の電気的長さを持っているかにもよる。接続点30がバイア36よりバイア34に近いので、基本トレース42の電気的長さと合致させるためにトレース40に余分の物理的長さを加える目的で基本トレース40に曲がり(図3には示していないが、例えば曲がりくねった形状)を持たせてもよい。基本トレース42もまた曲がりを持つことができる。ここに述べる様々なトレースは、必ずしも一定の幅を持つ必要はない。

【0012】

分岐トレースBA1は接続点CPA−1とバイア34の間で連結されている。分岐トレースBA2は接続点CPA−2とバイア34の間に連結されている。分岐トレースBA1とBA2は実質的に同一の電気的長さを持つ。分岐トレースBA3は接続点CPA−3とバイア36の間で連結され、分岐トレースBA4は接続点CPA−4とバイア36の間で連結される。分岐トレースBA3とBA4は実質的に同一の電気的長さを持つ。言及したように、バイアはすべての層を通って完全に延びている必要はない。1つ或いはそれ以上のトレースは直線でない形状(例えば曲がりくねった形状)を持つことができる。また、トレースの幅は均一である必要はない。

【0013】

図4において、基板10はNの層(すべてが図示されていない)を持つ。図4は基本トレース40が内部層を通過して内部層内のバイア34に接続されていることを示す。代わりの実施形態においては、基本トレース40を異なる層を通過して異なるバイアに接続する複数の基本トレースまたは基本/分岐トレースで置き換えることができる。接続点CPA−1とCPA−2は図1、図2、および図3に示すように移動される(すなわち、1つがもう一方の上にないように)。接続点CPA−1とCPA−2は全ての層を通って拡がるバイア(バイア34と同様)に接続されるパッドであってもよい。

【0014】

図5に図4に示すものとは異なるもう一つのタイプのトレース・ルーティング・トポロジーを示す。図5においてトレース・ルーティング・トポロジーは基本トレース50とそれに接続された基本/分岐トレース54、56を有する。基本トレース50は、接続点の一形態であるバイア52を通って基本/分岐トレース54と56に接続されている。分岐BB1とBB2はバイア44に接続され、各々接続点CPB−1とCPB−2に接続される。分岐BB3とBB4はバイア46に接続され、接続点CPB−3とCPB−4に接続される。分岐BB1とBB2は実質的に等しい電気的長さを持つ。分岐BB3とBB4は実質的に等しい電気的長さを持つ。

【0015】

図4のトレース・ルーティング・トポロジーはVトポロジーを有するのに対して、図5のトレース・ルーティング・トポロジーはYトポロジーを有する。

基本トレースは2より大きい分岐トレースまたは基本/分岐トレースに接続することもできる。

【0016】

図6はチップ70の底面図を示し、また接続点CPA−1とCPB−1、またはCPA−2とCPB−2、またはCPA−3とCPB−3、またはCPA−4、またはCPB−4に接続することができる2つの接続点74と76を示す。図7はチップ70の側面図を示す。トレーストポロジーのため、1つのタイプのチップ70のみが必要である。

チップを接合する接続点(例えばCPA−1)は駆動点でもよく、また受信点でもよい。

【0017】

もし鏡像チップが各々の側に使われたとしたら、基板は基板10よりもはるかに簡単であろう。確かに図3、図4、および図5に示す基板10の内部層、トレース、および中間接続(34、36、44、および46)は基板10に複雑さと費用を追加する。従って本発明は反直観的である。

基板10は、よく知られた材料及び回路を有することができ、且つよく知られていない材料及び回路を有することができる。基板10は、よく知られた技術及び工程に従って構築され、またよく知られていない技術及び工程に従っても構築することができる。

【0018】

商品化においてはここに図示されていない他の接続点や接続点グループがあるであろう、なぜならそれらは本発明の理解にとってさらになにも付加せず、図を乱雑にし、本発明を分かりにくくする傾向があるため図示されていないからである。本発明はプロセッサに使用することに限定するものではなく、他の様々な基板、回路基板、そしてチップと関連して使用することが可能である。

【0019】

当業者にとっては明らかであろうが、基板上の様々なコンポーネントの相対的な大きさ(例えばバイアや接続点)が説明の目的のために誇張されている。接続点は円形または球形である必要はない。図中のボックスの境界線は説明の目的のためであり、コンポーネントの境界を限定するものではなく重なり合うことも可能である。説明のためのコンポーネントの相対的な大きさは実際の相対的な大きさを示唆するものではない。「導体」という用語は広く解釈されるように意図しており、幾分か絶縁特性をも有する導電装置を含む。説明にあげたコンポーネント間、及び導体間には中間的なコンポーネントあるいは導体が存在することが可能である。

【0020】

もし本明細書があるコンポーネントあるいは特徴が含まれること、またはある特徴を持つことに関して「可能である」、「できる」、「できるであろう」、または「可能であろう」と述べている場合には、その特定のコンポーネントあるいは特徴が含まれる、または特徴を持つことを要求しない。「応答性がある」という用語は完全に、または部分的に応答性があるという意味である。

本発明の開示により利便を得る当業者には前述の説明と図面からの他の多くの変形を本発明の範囲内で作ることが可能であることがわかるであろう。従って、本発明の範囲を規定するのはいかなる修正条項をもさらに含んでいる以下の特許請求範囲である。

【図面の簡単な説明】

【図1】 接続点を有する多層基板の正面側の図である。

【図2】 図1に示す多層基板の背面側に位置する図である。

【図3】 図1に示す基板の接続点間のトレース接続の略図である。

【図4】 図1に示す基板の側面簡略図である。

【図5】 図1に示す基板の接続点間のトレース接続の略図である。

【図6】 図1または図に示す接続点に接続されるチップの底面図である。

【図7】 図6に示すチップの側面図である。

Claims (3)

- 第1のチップを接合するための第1のレイアウトを持ち、第1の接続点を含む第1の接続点グループを有する多層基板における正面側に位置する一次側、

第2のチップを接合するための、上記第1のレイアウトと同一のレイアウトを持ち、第2の接続点を含む第2の接続点グループを有する多層基板における背面側に位置する二次側、及び

各々が実質的に同じ電気的長さを有する第1と第2の分岐トレースを通して上記第1と第2の接続点に連結される中間接続点

を有し、上記中間接続点が基本トレースに連結、接続され、上記基本トレースが、第3のチップを接合するための接続点グループの該当する接続点に連結されることを特徴とする多層基板。 - 第1と第3の接続点を各々含む第1と第3の接続点グループを有し、それぞれが第1と第3のチップの各々を接合する第1のレイアウトを持つ多層基板における正面側に位置する一次側、

第2と第4の接続点を各々含む第2と第4の接続点グループを有し、それぞれが第2と第4のチップの各々を接合する上記第1のレイアウトと同一のレイアウトを持つ多層基板における背面側に位置する二次側、及び、

各々が実質的に同一の電気的長さを持つ第1と第2の分岐トレースを通って上記第1と第2の接続点に連結される第1の中間接続点と、各々が実質的に同一の電気的長さを有する第3と第4の分岐トレースを通って上記第3と第4の接続点に連結される第2の中間接続点

とを有し、上記中間接続点が基本トレースに連結、接続され、上記基本トレースが、第5のチップを接合するための接続点グループの該当する接続点に連結されることを特徴とする多層基板。 - 第1の接続点を含む第1の接続点グループを有し、レイアウトされた接続点を持つ第1のチップを接合するための第1のレイアウトを持つ多層基板における正面側に位置する一次側、

第2の接続点を含む第2の接続点グループを有し、上記第1のチップの上記レイアウトと同一のレイアウトを持つ第2のチップを接合するための上記第1のレイアウトと同一のレイアウトを持つ多層基板における背面側に位置する二次側、及び、

各々が実質的に同じ電気的長さを持つ第1と第2の分岐トレースを通って上記第1と第2の接続点に連結される中間接続点

とを有し、上記中間接続点が基本トレースに連結、接続され、上記基本トレースが、第3のチップを接合するための接続点グループの該当する接続点に連結されることを特徴とする多層基板。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/023,388 | 1998-02-13 | ||

| US09/023,388 US6118669A (en) | 1998-02-13 | 1998-02-13 | Routing topology for identical connector point layouts on primary and secondary sides of a substrate |

| PCT/US1999/001555 WO1999041770A2 (en) | 1998-02-13 | 1999-01-25 | Routing topology for identical connector point layouts on primary and secondary sides of a substrate |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002517080A JP2002517080A (ja) | 2002-06-11 |

| JP2002517080A5 JP2002517080A5 (ja) | 2006-03-09 |

| JP4344088B2 true JP4344088B2 (ja) | 2009-10-14 |

Family

ID=21814799

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000531862A Expired - Fee Related JP4344088B2 (ja) | 1998-02-13 | 1999-01-25 | 基板の一次側と二次側における同一の接続点レイアウトのためのルーティングトポロジー |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6118669A (ja) |

| JP (1) | JP4344088B2 (ja) |

| KR (1) | KR100347444B1 (ja) |

| AU (1) | AU2342199A (ja) |

| TW (1) | TW418420B (ja) |

| WO (1) | WO1999041770A2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6347041B1 (en) * | 2000-01-21 | 2002-02-12 | Dell Usa, L.P. | Incremental phase correcting mechanisms for differential signals to decrease electromagnetic emissions |

| CN1211723C (zh) * | 2000-04-04 | 2005-07-20 | 胜开科技股份有限公司 | 计算机卡制作方法 |

| US6875930B2 (en) * | 2002-04-18 | 2005-04-05 | Hewlett-Packard Development Company, L.P. | Optimized conductor routing for multiple components on a printed circuit board |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0249463A (ja) * | 1988-05-27 | 1990-02-19 | Matsushita Electron Corp | 半導体装置 |

| JP2793378B2 (ja) * | 1991-03-28 | 1998-09-03 | 株式会社東芝 | セミカスタム半導体集積回路マクロセル設計法 |

| US5604710A (en) * | 1994-05-20 | 1997-02-18 | Mitsubishi Denki Kabushiki Kaisha | Arrangement of power supply and data input/output pads in semiconductor memory device |

| US5841686A (en) * | 1996-11-22 | 1998-11-24 | Ma Laboratories, Inc. | Dual-bank memory module with shared capacitors and R-C elements integrated into the module substrate |

| US5831890A (en) * | 1996-12-16 | 1998-11-03 | Sun Microsystems, Inc. | Single in-line memory module having on-board regulation circuits |

-

1998

- 1998-02-13 US US09/023,388 patent/US6118669A/en not_active Expired - Lifetime

-

1999

- 1999-01-25 KR KR1020007008853A patent/KR100347444B1/ko not_active IP Right Cessation

- 1999-01-25 WO PCT/US1999/001555 patent/WO1999041770A2/en active Application Filing

- 1999-01-25 JP JP2000531862A patent/JP4344088B2/ja not_active Expired - Fee Related

- 1999-01-25 AU AU23421/99A patent/AU2342199A/en not_active Abandoned

- 1999-04-03 TW TW088102277A patent/TW418420B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| AU2342199A (en) | 1999-08-30 |

| WO1999041770A3 (en) | 1999-09-23 |

| JP2002517080A (ja) | 2002-06-11 |

| US6118669A (en) | 2000-09-12 |

| KR20010096460A (ko) | 2001-11-07 |

| KR100347444B1 (ko) | 2002-08-03 |

| TW418420B (en) | 2001-01-11 |

| WO1999041770A2 (en) | 1999-08-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4628714B2 (ja) | 回路相互接続構造 | |

| US5508938A (en) | Special interconnect layer employing offset trace layout for advanced multi-chip module packages | |

| US5426566A (en) | Multichip integrated circuit packages and systems | |

| JP2009038112A (ja) | プリント配線板構造および電子機器 | |

| US6392162B1 (en) | Double-sided flexible jumper assembly and method of manufacture | |

| US6561410B2 (en) | Low cost and high speed 3 load printed wiring board bus topology | |

| US6382986B1 (en) | Socket for mounting memory module boards on a printed circuit board | |

| US6670558B2 (en) | Inline and “Y” input-output bus topology | |

| JP4344088B2 (ja) | 基板の一次側と二次側における同一の接続点レイアウトのためのルーティングトポロジー | |

| TW200306140A (en) | Optimized conductor routing for multiple components on a printed circuit board | |

| US6477060B1 (en) | Dual channel bus routing using asymmetric striplines | |

| US6743985B1 (en) | Method and apparatus for increased routing density on printed circuit boards with differential pairs | |

| JP2531500B2 (ja) | 並列プロセッサとパッケ―ジ | |

| US6662250B1 (en) | Optimized routing strategy for multiple synchronous bus groups | |

| US6417688B1 (en) | Method and apparatus for implementing a highly robust, fast, and economical five load bus topology based on bit mirroring and a well terminated transmission environment | |

| JP2006216956A (ja) | 配線構造を有するメモリモジュール | |

| TW202130243A (zh) | 印刷電路板過渡之封裝 | |

| JP7439719B2 (ja) | マルチチップモジュールおよび電子制御装置 | |

| JP3166722B2 (ja) | 積層型半導体装置のスタック構造 | |

| JP2563189Y2 (ja) | メモリicカード | |

| JP2004318451A (ja) | 方向性結合素子を使用したメモリバスシステム | |

| JPH10302899A (ja) | コネクタ及びマザーボード | |

| JPH11163531A (ja) | 多層配線板 | |

| US8125087B2 (en) | High-density flip-chip interconnect | |

| JPH0215700A (ja) | 印刷配線板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080401 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080701 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090317 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090616 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090710 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120717 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120717 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130717 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |