JP4336477B2 - 半導体集積回路装置の製造方法 - Google Patents

半導体集積回路装置の製造方法 Download PDFInfo

- Publication number

- JP4336477B2 JP4336477B2 JP2002102026A JP2002102026A JP4336477B2 JP 4336477 B2 JP4336477 B2 JP 4336477B2 JP 2002102026 A JP2002102026 A JP 2002102026A JP 2002102026 A JP2002102026 A JP 2002102026A JP 4336477 B2 JP4336477 B2 JP 4336477B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- etching

- silicon oxide

- oxide film

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 55

- 238000004519 manufacturing process Methods 0.000 title claims description 30

- 238000005530 etching Methods 0.000 claims description 51

- 238000000034 method Methods 0.000 claims description 28

- 238000012546 transfer Methods 0.000 claims description 23

- 238000004380 ashing Methods 0.000 claims description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 56

- 229910052814 silicon oxide Inorganic materials 0.000 description 56

- 239000000758 substrate Substances 0.000 description 47

- 229910052581 Si3N4 Inorganic materials 0.000 description 42

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 42

- 238000005229 chemical vapour deposition Methods 0.000 description 19

- 238000001312 dry etching Methods 0.000 description 13

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 13

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 12

- 239000001301 oxygen Substances 0.000 description 12

- 229910052760 oxygen Inorganic materials 0.000 description 12

- 239000003990 capacitor Substances 0.000 description 8

- 238000000151 deposition Methods 0.000 description 8

- 239000012535 impurity Substances 0.000 description 8

- 238000003860 storage Methods 0.000 description 8

- 238000004140 cleaning Methods 0.000 description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 6

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 4

- 238000002955 isolation Methods 0.000 description 4

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229910001936 tantalum oxide Inorganic materials 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000011835 investigation Methods 0.000 description 2

- 239000010410 layer Substances 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000012827 research and development Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Drying Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、半導体集積回路装置の製造技術に関し、特に、DRAM(Dynamic Random Access Memory)等の製造中に行われる微細な孔の形成工程に適用して有効な技術に関するものである。

【0002】

【従来の技術】

DRAMは、情報転送用MISFET(Metal Insulator Semiconductor Field Effect Transistor)と、このMISFETに直列に接続された情報蓄積用容量素子を有している。

【0003】

例えば、情報転送用MISFETと情報蓄積用容量素子とは、情報転送用MISFETのゲート電極間(ソース、ドレイン上)に形成されたプラグにより電気的に接続される。

【0004】

しかしながら、微細化が進みゲート電極の幅やその間隔が縮小化されると、ゲート電極間に、プラグを埋め込むためのコンタクトホールを形成することが困難となってくる。

【0005】

そこで、ゲート電極の上面と側面とに窒化シリコン膜を形成した後、その上部にゲート電極間を埋め込むように酸化シリコン膜を堆積し、これらの膜のエッチング速度差を利用することによって、ゲート電極間に自己整合的にコンタクトホールを形成するというセルフアライン・コンタクト(Self Align Contact;SAC)技術が使われている(特開平9−252098号公報)。

【0006】

【発明が解決しようとする課題】

本発明者らは、DRAM等の半導体集積回路装置に関する研究・開発に従事しており、前述のSAC技術を採用している。

【0007】

しかしながら、かかるSAC技術を採用した工程において、コンタクトホールが非開口となる不良が発生した。

【0008】

この非開口のコンタクトホール部を解析した結果、その外観から「合わせずれ」が原因ではないかとの結論に達した。即ち、本来ゲート電極間上に位置すべきレジスト膜の開口部が、合わせずれによってゲート電極上にかかることにより、ゲート電極間上がレジストで覆われてしまい、絶縁膜をエッチングし難くしてしまうのである。

【0009】

ところが、前述のコンタクトホールが非開口となった不良製品についてさらに検討を進めた結果、コンタクトホール形成時のレジスト膜の「合わせずれ量」は、許容量以下であることが判明した。

【0010】

例えば、図20に示すように、ゲート電極間のスペースが、190nmであり、その上面と側面とに形成される窒化シリコン膜の膜厚を52nmとすると、エッチングが可能なスペースは、86nmである。なお、追って詳細に説明するように、コンタクトホール形成後、その内部の側壁に形成される薄い窒化シリコン膜の膜厚15nmを考慮しても、コンタクトホールの底面の径は、計算上56(=86−30)nm確保できる。

【0011】

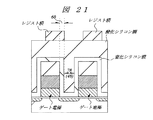

ここで、レジスト膜がゲート電極端部より60nmずれた場合でも、図21に示すように、エッチングが可能なスペースを48nm確保でき、非開口は防止できると考えられる。従って、この場合、合わせずれの許容量は例えば±60nmと規定されていた。

【0012】

しかしながら、このような許容量以下の合わせずれ量であってもコンタクトホールの非開口が生じることからその原因について、鋭意検討した結果、酸化シリコン膜をエッチングした際のテーパー成分が関与していることが判明した。

【0013】

追って詳細に説明するが、レジスト膜がゲート電極端部より例えば、50nm程度ずれた場合においても、このレジスト膜をマスクに酸化シリコン膜をエッチングすると、レジスト膜端部からテーパー状に酸化シリコン膜がエッチングされ、その裾は、ゲート電極間に残存してしまう(図5参照)。その結果、この酸化シリコン膜のテーパー状の裾が、窒化シリコン膜のエッチングの際のマスクとなり、開口領域が低減され(図6〜図8参照)、もしくは非開口が生じるのである。

【0014】

本発明の目的は、MISFETのゲート電極間(ソース、ドレイン上)に形成される接続部の接続不良を低減させることを目的とする。

【0015】

また、本発明の他の目的は、MISFETのゲート電極間(ソース、ドレイン上)上に形成される接続部を形成する際の合わせずれ量のマージンを確保することを目的とする。

【0016】

また、本発明の他の目的は、半導体集積回路装置の特性の向上を図ることができる技術を提供することにある。

【0017】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0018】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0019】

(1)本発明の半導体集積回路装置の製造方法は、情報転送用MISFETと容量素子から成るメモリセルを有する半導体集積回路装置の製造方法であって、(a)前記情報転送用MISFETを形成する工程と、(b)前記情報転送用MISFET上に第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に第2絶縁膜を形成する工程と、(d)前記第2絶縁膜上であって、前記情報転送用MISFETのソース、ドレイン領域上に開口を有するマスク膜を形成する工程と、(e)前記マスク膜をマスクに、前記第2絶縁膜を異方的にエッチングした後、等方的にエッチングすることにより前記ソース、ドレイン領域上の第1絶縁膜の表面を露出させる工程と、(f)前記露出した第1絶縁膜をエッチングすることにより、前記ソース、ドレイン領域上に孔を形成する工程と、を有する。このマスク膜の開口部の中心は、前記情報転送用MISFETのゲート電極間の中心に対しずれている。また、マスク膜の開口部の径は、例えば、200nm以下である。また、異方的なエッチングと等方的なエッチングは、双方ともドライエッチングである。また、第1絶縁膜は、例えば窒化シリコン膜、前記第2絶縁膜は、例えば酸化シリコン膜である。また、孔の形状は、孔の底部に露出したソース、ドレイン領域の中心部に対して対照的でない。また、前記半導体集積回路装置の製造方法は、さらに、(g)前記孔中に導電性膜を埋め込むことにより形成される接続部であって、前記情報転送用MISFETと前記容量素子とを電気的に接続する接続部を形成する工程を有してもよい。

【0020】

(2)本発明の半導体集積回路装置の製造方法は、情報転送用MISFETと容量素子から成るメモリセルを有する半導体集積回路装置の製造方法であって、(a)前記情報転送用MISFETを形成する工程と、(b)前記情報転送用MISFET上に第1絶縁膜を形成する工程と、(c)前記第1絶縁膜上に第2絶縁膜を形成する工程と、(d)前記第2絶縁膜上であって、前記情報転送用MISFETのソース、ドレイン領域上に開口を有するマスク膜を形成する工程と、(e)前記マスク膜の表面をアッシング(灰化)する工程と、(f)前記(e)工程の後、前記マスク膜をマスクに、前記第1絶縁膜および第2絶縁膜をエッチングすることにより前記ソース、ドレイン領域上に孔を形成する工程と、を有する。マスク膜の開口部の径は、例えば解像限界幅に対応する。

【0021】

【発明の実施の形態】

(実施の形態1)

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。

【0022】

本実施形態のDRAMの製造方法を図1〜図5および図9〜図16を用いて工程順に説明する。なお、図1〜図5および図9〜図15は、半導体基板の要部断面を示す図であり、図16は、半導体基板の要部平面を示す図である。例えば、図15は、図16のA−A断面と対応する。

【0023】

まず、図1に示すように、半導体基板(以下、単に基板という)1をエッチングして溝を形成し、熱酸化により薄い酸化膜を形成した後、この溝の内部に酸化シリコン膜5を埋め込むことにより素子分離2を形成する。この素子分離2を形成することにより、素子分離2によって周囲を囲まれた細長い島状の活性領域(L)が形成される(図16参照)。これらの活性領域(L)のそれぞれには、例えば、ソース、ドレインの一方を共有する情報転送用MISFETQtが2個ずつ形成される。

【0024】

次に、基板1にp型不純物(例えば、ホウ素(B))をイオン打ち込みした後、熱処理で不純物を拡散させることによって、基板1にp型ウエル3を形成する。

【0025】

次に、フッ酸系の洗浄液を用いて基板1(p型ウエル3)の表面をウェット洗浄した後、熱酸化によりp型ウエル3の表面に清浄なゲート絶縁膜6を形成する。

【0026】

次に、ゲート絶縁膜6の上部に低抵抗多結晶シリコン膜7aをCVD(Chemical Vapor Deposition)法で堆積する。続いて、低抵抗多結晶シリコン膜7aの上部にスパッタリング法で薄いWN膜(窒化タングステン膜、図示せず)とW(タングステン)膜7cとを堆積し、さらにその上部にCVD法で窒化シリコン膜8を堆積する。

【0027】

次に、フォトレジスト膜(図示せず、以下単に「レジスト膜」という)をマスクにして窒化シリコン膜8、W膜7c、WN膜(図示せず)および多結晶シリコン膜7aをドライエッチングすることにより、ゲート電極Gを形成する。このゲート電極Gは、ワード線WLとして機能する。ゲート電極Gの幅および間隔は、例えば約190nmである。

【0028】

次に、ゲート電極Gの両側にリン(P)イオンをイオン打ち込みすることによってn-型半導体領域9a(ソース、ドレイン領域)を形成する。

【0029】

ここまでの工程で、nチャネル型MISFETで構成される情報転送用MISFETQtが形成される。

【0030】

次に、基板1上にCVD法で窒化シリコン膜11を堆積する。この窒化シリコン膜11は、その膜厚が、52nm程度であり、n-型半導体領域9a上に微細な径(例えば56nm程度)のコンタクトホール(16、17)を形成する際のエッチングストッパー膜となる。

【0031】

次に、図2に示すように、窒化シリコン膜11の上部に、SOG(スピンオングラス:Spin On Glass)膜15aを塗布した後、基板1に熱処理を施し、SOG膜15aをデンシファイ(焼き締め)する。SOG膜15aは、CVD法で堆積した酸化シリコン膜に比べて微細な配線間のギャップフィル性に優れているので、例えば、フォトリソグラフィの解像限界で決まる最小寸法まで微細化されたゲート電極G(ワード線WL)の隙間を良好に埋め込むことができる。

【0032】

続いて、SOG膜15aの上部にCVD法で酸化シリコン膜15bを堆積した後、酸化シリコン膜15bの表面を必要に応じて化学機械研磨(Chemical Mechanical Polishing:CMP)法で研磨してその表面を平坦化する。その結果、SOG膜15aおよび酸化シリコン膜15bの積層膜よりなる層間絶縁膜が形成される。なお、層間絶縁膜は2層で構成する必要はなく、例えば、テトラエトキシシランを原料としたプラズマCVD法で酸化シリコン膜を形成する等、埋め込み特性の良い膜を用いれば単層で形成することも可能である。

【0033】

この後、図3に示すように、酸化シリコン膜15b上にゲート電極G間(n-型半導体領域9a)上に開口を有するレジスト膜Rを形成し、このレジスト膜Rをマスクに、酸化シリコン膜15bおよびSOG膜15aをエッチングした後、窒化シリコン膜11をエッチングすることによってコンタクトホール(16、17)を形成するのであるが、かかる工程について、以下に詳細に説明する。

【0034】

まず、本実施の形態の工程を説明する前に、発明者が検討した工程について図4〜図8を参照しながら説明する。

【0035】

図4に示すように、レジスト膜Rの形成の際、即ち、レジスト膜を基板全面に形成した後、コンタクトホール(16、17)の形状に対応したマスクパターンを転写する際、合わせずれが生じる。例えば、開口部間に残存ずるレジスト膜Rの中心(Rc)と、ゲート電極Gの中心(WLc)とのずれ量を、ΔLとする。なお、ここでは、レジスト膜Rの中心(Rc)が、ゲート電極Gの中心(WLc)より右にずれた場合をプラスとし、左にずれた場合をマイナスとする。

【0036】

次いで、図5(a)および(b)に示すように、このようなレジスト膜Rをマスクに、酸化シリコン膜15bおよびSOG膜15aをエッチングすると、これらの膜は、レジスト膜Rの端部からテーパー状にエッチングされ、その裾がゲート電極G間(n-型半導体領域9a)上に残存してしまう。なお、図5(b)は、図5(a)のゲート電極G間の部分拡大図である(同様に、図6〜図8について、(b)は、(a)の部分拡大図である)。

【0037】

次いで、図6(a)および(b)に示すように、前記エッチングで露出した窒化シリコン膜11をエッチングすると、ゲート電極G間(n-型半導体領域9a)上の酸化シリコン膜15bおよびSOG膜15aがマスクとなり、コンタクトホール16、17の底面の径が小さくなってしまう。

【0038】

さらに、図7(a)および(b)に示すように、コンタクトホール16、17の側壁に15nm程度の薄い窒化シリコン膜15cを形成すると、コンタクトホール16、17の底面の径は、益々小さくなる。これは、多結晶シリコン膜等の導電性膜をコンタクトホール16、17内に埋め込みプラグ18を形成する前には、基板1(n-型半導体領域9a)表面の自然酸化膜等を除去し、プラグ18と基板1との接続状態を良好にするため、フッ酸等の洗浄液を用いた洗浄を行う必要がある。この際、コンタクトホール16、17の側壁の酸化シリコン膜15bおよびSOG膜15aのエッチングを防止するため、薄い窒化シリコン膜15cを形成する。この窒化シリコン膜15cは、コンタクトホール16、17内を含む酸化シリコン膜15b上に、CVD法で窒化シリコン膜を15nm程度堆積した後、かかる膜を異方的にエッチングすることによって形成する。

【0039】

次いで、図8に示すように、コンタクトホール16、17の内部に、リン(P)などのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積し、続いてこの多結晶シリコン膜をエッチバック(またはCMP法で研磨)して、コンタクトホール16、17の内部にプラグ18を形成する。

【0040】

しかしながら、コンタクトホール16、17が非開口の場合はもとより、図5〜図7に示すように、コンタクトホール16、17の底面の径が小さい状態で、多結晶シリコン膜をコンタクトホール16、17内に埋め込むと、接触抵抗が増大し接続不良を生じさせる。

【0041】

そこで、本発明者らは、以下に示す工程で、コンタクトホール(プラグ)を形成することとした。かかる工程を、図4、図5および図9〜図13を参照しながら詳細に説明する。

【0042】

まず、図4に示すように、レジスト膜Rの形成の際、即ち、レジスト膜を基板全面に形成した後、コンタクトホール16、17の形状に対応したマスクパターンを転写する際、開口部間に残存ずるレジスト膜Rの中心(Rc)と、ゲート電極Gの中心(WLc)とが、ΔLずれた場合を考える。

【0043】

前述した通り、このようなレジスト膜Rをマスクに、酸化シリコン膜15bおよびSOG膜15aを異方的にエッチングすると、図5(a)および(b)に示すように、これらの膜は、レジスト膜Rの端部からテーパー状にエッチングされ、その裾がゲート電極G間(n-型半導体領域9a)上に残存してしまう。この際のエッチングは、ドライエッチングである。

【0044】

次いで、図9(a)および(b)に示すように、酸化シリコン膜15bおよびSOG膜15aを等方的にエッチングすることによりコンタクトホール16、17側壁のこれらの膜をエッチングする。このエッチングによって、ゲート電極G間(n-型半導体領域9a)上に残存していた、酸化シリコン膜15bおよびSOG膜15aが除去され、コンタクトホール16、17の底面の面積(窒化シリコン膜11の露出領域)を確保することができる。なお、この際のエッチングも、ドライエッチングである。

【0045】

このように、異方的なエッチングと等方的なエッチングは、双方ともドライエッチングとする。

【0046】

この異方性や等方性の制御は、例えば、プラズマエッチングにおいて、基板に印加する電位や、基板上にコリメータを設置する等して、制御することができる。

【0047】

また、これらのエッチングは、同一チャンバー(装置)内で行ってもよいし、また別チャンバー(装置)で行ってもよい。

【0048】

このように、等方的なエッチングをドライエッチングとすることで、酸化シリコン膜15bおよびSOG膜15aのエッチング量の制御性を良くすることができる。例えば、等方性のエッチングをウエットエッチングにより行うことも可能であるが、この場合、エッチング量の制御が困難となる。特に、SOG膜15aは、ウエットエッチングでエッチングされやすく、コンタクトホール16、17間を絶縁するSOG膜15aがエッチングされることで、プラグ(18)間の短絡が起こりやすくなる。これに対して、等方性のエッチングをドライエッチングで行った場合は、制御性良くエッチングを行え、プラグ(18)間の短絡を低減することができる。

【0049】

また、異方的なドライエッチングは、例えば、C5F8、Ar(アルゴン)および酸素(O2)の混合気体を用いて行うことができ、また、等方的なドライエッチングは、例えば、CF4および酸素の混合気体を用いて行うことができる。また、これらのエッチングの間に、Arおよび酸素を用いたドライエッチングを行ってもよい。このエッチングは、コンタクトホール16、17内壁に付着したレジスト残差を除去するために行う。

【0050】

この後、図10(a)および(b)に示すように、前記異方性および等方性のエッチングで露出した窒化シリコン膜11をエッチングする。このエッチングは、例えば、CHF3、Arおよび酸素を用いたドライエッチングにより行うことができる。

【0051】

このように、SOG膜15aや酸化シリコン膜15bのエッチングは、窒化シリコンに比べてエッチング速度が大きくなるような条件で行い、窒化シリコン膜11が完全には除去されないようにする。また、窒化シリコン膜11のエッチングは、シリコン(基板)や酸化シリコンに比べて窒化シリコンのエッチング速度が大きくなるような条件で行い、基板1やゲート絶縁膜6等の酸化膜が深く削れないようにする。これにより、微細な径を有するコンタクトホール16、17がゲート電極Gに対して自己整合(セルフアライン)で形成される。

【0052】

なお、本実施の形態によれば、マスクずれによって、コンタクトホール16、17側壁に、酸化シリコン膜15bおよびSOG膜15aが残存していても、その後、等方的にエッチングすることによりこれらの膜を除去することができ、窒化シリコン膜11の露出領域を確保することができる。従って、露出した窒化シリコン膜11をエッチングすることによりコンタクトホール16、17の底面積を確保することができる。

【0053】

特に、メモリセルの微細化により、ゲート電極Gの幅や間隔が、ほぼフォトリソグラフィの解像限界で決まる最小寸法(例えば200nm程度)となりつつあり、また、マスクずれをこの解像限界幅の1/4(例えば50nm程度)以下とすることは困難であるため、微細化されたメモリセルに本実施の形態を適用して効果的である。

【0054】

次いで、図11(a)および(b)に示すように、例えば、CF4および酸素を用いたエッチングにより、窒化シリコン膜11の底部の薄い酸化膜(例えば、ゲート絶縁膜6)を除去する。

【0055】

さらに、レジスト膜Rを酸素を用いてアッシング(灰化)した後、コンタクトホール16、17内を含む酸化シリコン膜15b上に、CVD法で窒化シリコン膜を15nm程度堆積した後、かかる膜を異方的にエッチングすることによって、コンタクトホール16、17の側壁に薄い窒化シリコン膜15cを形成する。

【0056】

次いで、露出した基板1(n-型半導体領域9a)の表面の自然酸化膜等を除去するため、例えばフッ酸系の洗浄液を用いて洗浄を行う。なお、前記窒化シリコン膜15cは、この洗浄の際、コンタクトホール16、17側壁の酸化シリコン膜15bおよびSOG膜15aのエッチングを防止するために形成される。

【0057】

次いで、図12(a)および(b)に示すように、コンタクトホール16、17の内部に、リン(P)などのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積し、続いてこの多結晶シリコン膜をエッチバック(またはCMP法で研磨)して、コンタクトホール16、17の内部にプラグ18を形成する。

【0058】

ここで、本実施の形態によれば、コンタクトホール16、17の底面積を確保することができるので、コンタクトホール16、17内に埋め込まれるプラグ18と基板1(n-型半導体領域9a)との接触面積を確保することができる。また、コンタクトホール16、17の側壁に薄い窒化シリコン膜15cを形成しても、接触面積を確保することができる。

【0059】

なお、図13に示すように、多結晶シリコン膜(プラグ18)中のn型不純物を基板中に拡散させることにより基板1中にn+型半導体領域9bを形成してもよい。また、このn+型半導体領域9bは、コンタクトホール16、17を介して基板中にn型不純物をイオン打ち込みすることにより形成することもできる。

【0060】

この後、コンタクトホール16内に形成されたプラグ18と電気的に接続されるビット線BLが形成され、また、コンタクトホール17内に形成されたプラグ18と電気的に接続される情報蓄積用容量素子Cが形成される。以下、これらの形成工程の一例について、図14および図15を参照しながら説明する。

【0061】

図14に示すように、酸化シリコン膜15bの上部にCVD法で酸化シリコン膜19を堆積した後、酸化シリコン膜をドライエッチングすることにより、コンタクトホール16中のプラグ18の上部に、スルーホール20を形成する。

【0062】

次に、スルーホール20の内部を含む酸化シリコン膜19の上部にCVD法で薄いTiN(窒化チタン)膜を堆積し、さらに、W膜を堆積した後、酸化シリコン膜19の上部のW膜およびTiN膜をCMP法で研磨し、これらの膜をスルーホール20の内部のみに残すことによって、プラグ23を形成する。

【0063】

次に、酸化シリコン膜19およびプラグ23の上部にスパッタリング法でW膜を堆積した後、レジスト膜をマスクにしてこのW膜をドライエッチングすることによって、ビット線BLをする。なお、図14は、図16のA−A断面に対応し、ビット線BLおよびプラグ23は、図16に示すようにA−A断面には表れないが、図14においては、プラグ18とビット線BLとの関係を明確にするため、ビット線BL等を記載してある。

【0064】

次に、酸化シリコン膜19およびビット線BLの上部に例えば、CVD法で酸化シリコン膜40を形成する。次いで、酸化シリコン膜40およびその下層の酸化シリコン膜19をドライエッチングすることによって、コンタクトホール17内のプラグ18の上部にスルーホール43を形成する。

【0065】

次に、スルーホール43の内部にプラグ44を形成する。このプラグ44は、スルーホール43の内部を含む酸化シリコン膜40の上部にn型不純物(例えば、リン)をドープした低抵抗多結晶シリコン膜をCVD法で堆積した後、この多結晶シリコン膜をCMP法で研磨してスルーホール43の内部のみに残すことによって形成する。

【0066】

この後、図15に示すように、酸化シリコン膜40およびプラグ44の上部にCVD法で窒化シリコン膜45を堆積し、続いて窒化シリコン膜45の上部にCVD法で厚い酸化シリコン膜46を堆積する。

【0067】

次に、酸化シリコン膜46の上部に、ハードマスク(図示せず)を形成し、このハードマスクをマスクにプラグ44上の酸化シリコン膜46をドライエッチングした後、露出した窒化シリコン膜45をドライエッチングすることにより、深い孔(凹部、溝)47を形成する。この窒化シリコン膜45は、エッチングストッパの役割を果たす。

【0068】

次いで、酸化シリコン膜46の上部に残ったハードマスク(図示せず)を除去し、酸化シリコン膜46の上部および孔47の内部に、n型不純物(リン)をドープしたアモルファスシリコン膜をCVD法で堆積した後、酸化シリコン膜46の上部のアモルファスシリコン膜をエッチバックすることにより、孔47の内壁に沿ってアモルファスシリコン膜を残す。次に、アモルファスシリコン膜の表面にモノシラン(SiH4)を供給し、熱処理を施すことにより、アモルファスシリコン膜を多結晶化すると共に、その表面にシリコン粒を成長させる。これにより、表面が粗面化された下部電極48が孔47の内壁に沿って形成される。

【0069】

次に、下部電極48が形成された孔47の内部および酸化シリコン膜46上に酸化タンタル膜をCVD法により堆積し、熱処理を施す。

【0070】

次いで、酸化タンタル膜の上部に、例えばCVD法によりTiN膜を堆積した後、TiN膜と酸化タンタル膜とをドライエッチングすることにより、TiN膜からなる上部電極50、酸化タンタル膜からなる容量絶縁膜49を形成する。

【0071】

ここまでの工程により、情報転送用MISFETQtとこれに直列に接続された情報蓄積用容量素子Cとで構成されるDRAMのメモリセルが略完成する。図16は、情報蓄積用容量素子C形成後の基板の要部平面図である。なお、図16に記載の各部位においては、図4を参照しながら説明したずれ量ΔLは考慮されていない。

【0072】

この後、情報蓄積用容量素子Cの上部には、酸化シリコン膜51が堆積され、その後、2層程度の配線が形成されるが、これらの図示は省略する。

【0073】

(実施の形態2)

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、情報転送用MISFETQt上部の窒化シリコン膜11、SOG膜15aおよび酸化シリコン膜15bの形成工程までは、図1〜図3を参照しながら説明した実施の形態1と同様であるためその説明を省略する。

【0074】

次いで、酸化シリコン膜15b上にレジスト膜Rを形成するのであるが、図4を参照しながら説明したように、このレジスト膜Rが、フォトリソグラフィー時のマスクずれによりその形成位置がΔLだけずれた場合を考える。

【0075】

次いで、このレジスト膜Rの表面を、10〜20nm程度、酸素を用いたアッシング(灰化)処理により除去する。その結果、図17に示すように、レジスト膜Rで覆われている領域は、小さくなり、レジスト膜Rの開口部の面積が大きくなる。

【0076】

次いで、図18に示すように、レジスト膜Rをマスクに、酸化シリコン膜15bおよびSOG膜15aを異方的にエッチングする。このエッチングは、例えば、C5F8、Arおよび酸素を用いたドライエッチングにより行うことができる。

【0077】

この際、これらの膜は、レジスト膜Rの端部からテーパー状にエッチングされるが、前述のアッシング処理によりレジスト膜Rの端部が後退しているため、その裾の部分は、ゲート電極G間(n-型半導体領域9a)上に残存しない。従って、コンタクトホール16、17の底面の面積(窒化シリコン膜11の露出領域)を確保することができる。

【0078】

次いで、図19に示すように、露出した窒化シリコン膜11をエッチングする。このエッチングは、例えば、CHF3、Arおよび酸素を用いたドライエッチングにより行うことができる。なお、窒化シリコン膜11のエッチングの前に、コンタクトホール16、17内壁に付着したレジスト残差を除去するため、Arおよび酸素を用いたドライエッチングを行ってもよい。

【0079】

次いで、実施の形態1と同様に、窒化シリコン膜11の底部の薄い酸化膜を除去し、レジスト膜Rをアッシング(灰化)した後、窒化シリコン膜15c、プラグ18を形成する(図11〜図13参照)。さらに、図14および図15を参照しながら説明した実施の形態1と同様に、ビット線BLや情報蓄積用容量素子C等を形成する。

【0080】

このように、本実施の形態によれば、レジスト膜Rの表面を除去したので、レジスト膜Rの形成時にマスクずれが生じても、かかる膜をマスクとしたコンタクトホール16、17の形成時に、その底面積を確保することができ、コンタクトホール16、17内に埋め込まれるプラグ18と基板1との接触面積を確保することができる。

【0081】

特に、メモリセルの微細化のため、ゲート電極Gの幅や間隔が、ほぼフォトリソグラフィの解像限界で決まる最小寸法となるような場合には、本実施の形態を適用して効果的である。

【0082】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0083】

特に、本実施の形態においては、DRAMを例として説明したが、この他、微細な径のコンタクトホールを有する半導体集積回路装置に広く適用可能である。

【0084】

【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

【0085】

(1)MISFET上に第1絶縁膜および第2絶縁膜の積層膜を形成し、第2絶縁膜上であって、情報転送用MISFETのソース、ドレイン領域上に開口を有するマスク膜をマスクに、第2絶縁膜を異方的にエッチングした後、等方的にエッチングすることによりソース、ドレイン領域の第1絶縁膜の表面を露出させ、この露出した第1絶縁膜をエッチングすることにより、ソース、ドレイン領域上に孔を形成したので、マスク膜の合わせずれ量のマージンを確保することができる。また、この孔内に形成される接続部とMISFETのソース、ドレインとの接続不良を低減させることができる。

【0086】

また、半導体集積回路装置の特性の向上を図ることができ、歩留まりの向上を図ることができる。

【0087】

(2)また、MISFET上の絶縁膜上に形成され、MISFETのソース、ドレイン領域上に開口を有するマスク膜を形成し、このマスク膜の表面をアッシング(灰化)した後、このマスク膜をマスクに、絶縁膜をエッチングすることによりソース、ドレイン領域上に孔を形成したので、マスク膜の合わせずれ量のマージンを確保することができる。また、この孔内に形成される接続部とMISFETのソース、ドレインとの接続不良を低減させることができる。

【0088】

また、半導体集積回路装置の特性の向上を図ることができ、歩留まりの向上を図ることができる。

【図面の簡単な説明】

【図1】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図2】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図3】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図4】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図5】(a)および(b)は、本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図6】(a)および(b)は、本発明の実施の形態1の効果を説明するための半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図7】(a)および(b)は、本発明の実施の形態1の効果を説明するための半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図8】(a)および(b)は、本発明の実施の形態1の効果を説明するための半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図9】(a)および(b)は、本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図10】(a)および(b)は、本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図11】(a)および(b)は、本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図12】(a)および(b)は、本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図13】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図14】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図15】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図16】本発明の実施の形態1である半導体集積回路装置(DRAM)の製造方法を示す基板の要部平面図である。

【図17】本発明の実施の形態2である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図18】本発明の実施の形態2である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図19】本発明の実施の形態2である半導体集積回路装置(DRAM)の製造方法を示す基板の要部断面図である。

【図20】本発明の課題を説明するための半導体集積回路装置(DRAM)を示す基板の要部断面図である。

【図21】本発明の課題を説明するための半導体集積回路装置(DRAM)を示す基板の要部断面図である。

【符号の説明】

1 基板(半導体基板)

2 素子分離

3 p型ウエル

5 酸化シリコン膜

6 ゲート絶縁膜

7a 多結晶シリコン膜

7c W膜

8 窒化シリコン膜

9a n-型半導体領域

9b n+型半導体領域

11 窒化シリコン膜

15a SOG膜

15b 酸化シリコン膜

15c 窒化シリコン膜

16 コンタクトホール

17 コンタクトホール

18 プラグ

19 酸化シリコン膜

20 スルーホール

23 プラグ

40 酸化シリコン膜

43 スルーホール

44 プラグ

45 窒化シリコン膜

46 酸化シリコン膜

47 孔

48 下部電極

49 容量絶縁膜

50 上部電極

51 酸化シリコン膜

BL ビット線

C 情報蓄積用容量素子

G ゲート電極

Qt 情報転送用MISFET

R レジスト膜

WL ワード線

ΔL ずれ量

Claims (1)

- 情報転送用MISFETと容量素子から成るメモリセルを有する半導体集積回路装置の製造方法であって、

(a)前記情報転送用MISFETを形成する工程と、

(b)前記情報転送用MISFET上に第1絶縁膜を形成する工程と、

(c)前記第1絶縁膜上に第2絶縁膜を形成する工程と、

(d)前記第2絶縁膜上であって、前記情報転送用MISFETのソース、ドレイン領域上に開口を有するマスク膜を形成する工程と、

(e)前記マスク膜の表面をアッシング(灰化)する工程と、

(f)前記(e)工程の後、前記マスク膜をマスクに、前記第1絶縁膜および第2絶縁膜をエッチングすることにより前記ソース、ドレイン領域上に孔を形成する工程と、

を有することを特徴とする半導体集積回路装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002102026A JP4336477B2 (ja) | 2002-04-04 | 2002-04-04 | 半導体集積回路装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002102026A JP4336477B2 (ja) | 2002-04-04 | 2002-04-04 | 半導体集積回路装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003297951A JP2003297951A (ja) | 2003-10-17 |

| JP2003297951A5 JP2003297951A5 (ja) | 2005-09-15 |

| JP4336477B2 true JP4336477B2 (ja) | 2009-09-30 |

Family

ID=29388821

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002102026A Expired - Fee Related JP4336477B2 (ja) | 2002-04-04 | 2002-04-04 | 半導体集積回路装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4336477B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100576463B1 (ko) * | 2003-12-24 | 2006-05-08 | 주식회사 하이닉스반도체 | 반도체소자의 콘택 형성방법 |

| JP2007149773A (ja) * | 2005-11-24 | 2007-06-14 | Mitsumi Electric Co Ltd | 半導体装置の製造方法 |

| US11973120B2 (en) | 2020-06-24 | 2024-04-30 | Etron Technology, Inc. | Miniaturized transistor structure with controlled dimensions of source/drain and contact-opening and related manufacture method |

| US11972983B2 (en) | 2020-06-24 | 2024-04-30 | Etron Technology, Inc. | Miniaturized transistor structure with controlled dimensions of source/drain and contact-opening and related manufacture method |

| US12490448B2 (en) | 2020-09-09 | 2025-12-02 | Etron Technology, Inc. | Transistor structure with metal interconnection directly connecting gate and drain/source regions |

| US11855218B2 (en) | 2020-09-09 | 2023-12-26 | Etron Technology, Inc. | Transistor structure with metal interconnection directly connecting gate and drain/source regions |

| JP7568603B2 (ja) * | 2021-12-14 | 2024-10-16 | ▲ゆ▼創科技股▲ふん▼有限公司 | ソース/ドレイン及びコンタクト開口の制御された寸法を有する小型化されたトランジスタ構造及び関連する製造方法 |

-

2002

- 2002-04-04 JP JP2002102026A patent/JP4336477B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003297951A (ja) | 2003-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6762449B2 (en) | Semiconductor integrated circuit device and the process of manufacturing the same having poly-silicon plug, wiring trenches and bit lines formed in the wiring trenches having a width finer than a predetermined size | |

| JP4167727B2 (ja) | 半導体記憶装置 | |

| US8853810B2 (en) | Integrated circuits that include deep trench capacitors and methods for their fabrication | |

| JP4964407B2 (ja) | 半導体装置及びその製造方法 | |

| JP2001203263A (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JP2924771B2 (ja) | 蓄積容量部形成方法 | |

| KR100325472B1 (ko) | 디램 메모리 셀의 제조 방법 | |

| US20050230734A1 (en) | Field effect transistors having trench-based gate electrodes and methods of forming same | |

| US5789792A (en) | Isolation trench structures protruding above a substrate surface | |

| JP2000068481A (ja) | Dram装置の製造方法 | |

| US6806195B1 (en) | Manufacturing method of semiconductor IC device | |

| JP3605493B2 (ja) | 半導体装置の製造方法 | |

| US6734479B1 (en) | Semiconductor integrated circuit device and the method of producing the same | |

| JP4336477B2 (ja) | 半導体集積回路装置の製造方法 | |

| US6674111B2 (en) | Semiconductor device having a logic transistor therein | |

| US6969649B2 (en) | Method of manufacturing semiconductor integrated circuit devices having a memory device with a reduced bit line stray capacity and such semiconductor integrated circuit devices | |

| JP5076168B2 (ja) | 半導体装置の製造方法 | |

| US6136716A (en) | Method for manufacturing a self-aligned stacked storage node DRAM cell | |

| KR100442106B1 (ko) | 도전성 콘택 구조 및 그 제조방법 | |

| JP4602818B2 (ja) | 半導体装置の製造方法 | |

| US20260068136A1 (en) | Memory device and manufacturing method thereof | |

| JP5003743B2 (ja) | 半導体装置とその製造方法 | |

| JPH10150161A (ja) | 半導体装置のキャパシタ及びその製造方法 | |

| US20030086308A1 (en) | Semiconductor memory device having a trench capacitor and a manufacturing method thereof | |

| JP2001230383A (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050330 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050330 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080221 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090317 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090407 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090513 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20090518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090602 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090629 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120703 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130703 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |