JP4286397B2 - コンデンサ構造を有する半導体素子の形成方法 - Google Patents

コンデンサ構造を有する半導体素子の形成方法 Download PDFInfo

- Publication number

- JP4286397B2 JP4286397B2 JP22910199A JP22910199A JP4286397B2 JP 4286397 B2 JP4286397 B2 JP 4286397B2 JP 22910199 A JP22910199 A JP 22910199A JP 22910199 A JP22910199 A JP 22910199A JP 4286397 B2 JP4286397 B2 JP 4286397B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- dielectric

- electrode layer

- lower electrode

- upper electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- H10W20/031—

-

- H10W20/081—

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、半導体素子の形成方法に関し、特に、集積回路においてアナログ−ディジタル変換との関連で用いるのに適した積層コンデンサ(stacked capacitor)を含む半導体素子に関するものである。

【0002】

【従来の技術】

当技術分野では既知のように、CMOSにおいてアナログおよびディジタル信号を共に用いる場合、無線周波数(RF)回路およびアナログ回路を、高速および高性能ディジタル回路と一体化する。この点において、アナログからディジタルへの変換は、通常、約1MHz以下程度の低いベースバンド周波数において行われる。しかしながら、性能向上および回路設計の簡略化を図るために、RFのようにより高い周波数においてアナログ−ディジタル変換を実行しようという試みが行われている。高周波数で変換を行うには、高い品質係数(Q)を有し、回路が用いられる印加電圧範囲および温度範囲全体にわたって線形性を呈するコンデンサ・エレメントが必要となる。

【0003】

現在のCMOS技術において利用されているコンデンサは、高周波数における変換に必要な要件を適切に満たしてはいない。例えば、かかるコンデンサの電極は、典型的に、バルクの単結晶または多結晶シリコン基板で作られる。かかる構造の容量は、2つの成分、即ち、絶縁容量およびバイアス依存シリコン表面空乏容量(bias-dependent silicon surface depletion capacitance)に左右される。シリコンを基本とする電極に伴う空乏容量の結果として、コンデンサは低い線形性を呈することになる。

【0004】

【発明が解決しようとする課題】

シリコンを基本とする電極に伴う線形性欠如の問題を解決するためには、電極を金属含有材料(例えば、Ti,W)で作ることによって、表面空乏容量を制限することが可能である。金属電極を有するコンデンサは一般に当技術分野では既知であるが、現在のプロセス・フローを用いて形成可能なコンデンサは未だ開発されていない。精度高く製造可能で、高い「Q」を有する金属電極コンデンサは、入手可能であるが、特殊化されたプロセス・フローを必要とするので、コスト効率が低い。

【0005】

【発明の実施の形態】

これより図面を参照しながら、本発明を説明するが、図示の簡略化および明確化のために、図に示すエレメントは必ずしも同じ拡縮率で描かれている訳ではないことは認められよう。例えば、エレメントによっては、明確化のために、その寸法が他のエレメントよりも誇張されている場合がある。また、適切と見なされる場合には、対応するエレメントまたは類似のエレメントを示すために図面間で参照番号を繰り返している。

【0006】

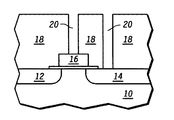

図1に移り、本発明による半導体素子の形成プロセスにおける一段階を示す。図示のように、ソース/ドレイン12,ソース/ドレイン14,およびソースをドレインから分離するゲート16を含むトランジスタ構造を有する半導体基板10が示されている。基板は、通常、ドープ単結晶シリコンで形成される。しかしながら、基板は、ポリシリコン,ゲルマニウム,絶縁物上シリコン(SOI:silicon on insulator)等でもよい。ゲート16およびソース/ドレイン12,14は、従来のプロセスで形成する。通常、ゲート16を形成する層のスタックを堆積し、リソグラフを用いて規定しエッチングし、イオン注入によって、ゲート16に自己整合するソースおよびドレインを形成する。基板上に第1層間誘電体18を堆積し、その中に開口20を形成する。層間誘電体18は、従来の技法によって形成され、その厚さは通常約0.8ないし1.0ミクロンである。層間誘電体18は二酸化シリコンで形成するが、ボロフォスフォシリケート・ガラス(BPSG)のような他の誘電体材料で形成することも可能である。開口20は、プラズマ・エッチングのような、従来の技法で形成する。

【0007】

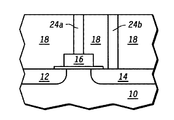

図2に移り、通常タングステン(W),チタン(Ti),および恐らくは銅(Cu)で形成する導電層22を堆積する。図3において、化学機械式研摩(CMP)によって導電層22を研磨してこの層を平面化し、開口20内にコンタクト24a,24bを規定する。コンタクト24は、第1層間誘電体18の上面と同一面となる。コンタクト24a,24bは、層間誘電体を貫通する導電性部分を形成する。

【0008】

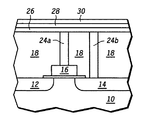

コンタクト24の形成に続いて、複数の層を一括堆積(blanket deposit)し、これらを用いて、図4に示すようなコンデンサ・エレメントを規定し形成する。即ち、第1層間誘電等18およびゲート16に接続するコンタクト24aを覆うように下側電極層26を堆積する。下側電極層は、チタン(Ti),タンタル(Ta),タングステン(W),銅(Cu),アルミニウム(Al),その窒化物およびその硅化物を含む、いずれの導電性材料で形成することも可能である。尚、ここで用いる場合、「導電層」または「導電性材料」という用語は、抵抗率が約1X10-5オーム・センチメートル未満の材料を言うことを注記しておく。通常、ドープ・ポリシリコン(doped polysilicon)の抵抗率は1X10-5オーム・センチメートルよりも大きく、ここで言う高Qコンデンサ・エレメントの電極には通常用いられない。下側電極層は、従来の技法で形成し、全体的に比較的薄く0.05ないし0.2ミクロン程度である。次に、下側電極層26を覆うように、誘電体層28を一括堆積する。誘電体層28は、窒化シリコン,酸化シリコン,または酸窒化シリコンのような窒化物または酸化物材料で形成することができ、その厚さは約0.01ないし0.06ミクロンである。しかしながら、BST(チタン化バリウム・ストロンチウム)材料,またはBZT(チタン化バリウム・ジルコニウム)材料のような、他の誘電体材料も使用可能である。その後、誘電体層28を覆うように、薄い0.02ミクロンの保護層30を一括堆積する。保護層30は導電性であり、その上に形成される上側電極層への電気コンタクトを確保し、以下で述べる第1エッチング工程の間、誘電体層28および下側電極層26を保護するために用いられる。保護層30は、窒化物または硅化物で形成することができ、例えば、一実施例では、保護層を窒化チタン(TiN)で形成する。

【0009】

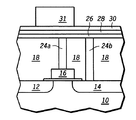

図5および図6に移り、フォトレジスト31をスピン・コートし、露光し、現像して、層26,28,30のパターニングを行う。図示のように、コンタクト24bの上に位置する層26,28,30の部分を除去して、コンタクト24bを露出させる。このパターニング工程はエッチングによって実行するが、「粗い」エッチング工程として理解することができる。第2エッチング工程によって層26,28,30のパターニングを再度行い、コンデンサ・エレメントを規定する。

【0010】

図7に移り、層26,38,30のスタックを覆い、更にコンタクト24bを含む第1層間誘電体18も覆うように、上側電極層32を一括堆積する。上側電極層32は、AlまたはCuを含有し、その公称厚さは約0.7ミクロンである。

【0011】

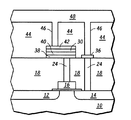

図8および図9に示すように、第2エッチング工程によって、この構造に再度パターニングを行う。具体的には、フォトレジスト層34を堆積し、コンデンサ・エレメント即ちコンデンサ構造の寸法をリソグラフによって規定する。第2エッチング工程は第1エッチング工程よりも精度が高く、これによってコンデンサ・エレメントの最終寸法が規定される。加えて、図8に示すように、コンタクト24b上に、フォトレジスト層34の一部を残しておく。図10に示すように、フォトレジスト34のエッチングおよび除去の後には、下側電極プレート38,誘電体プレート40,保護層30,および上側電極プレート42を有するコンデンサ・エレメントが規定されている。加えて、金属層32にパターニングを行い、コンタクト24b上にこれと電気的に接続する金属相互接続部36を残す。このようにして、コンデンサ・エレメントの上側電極および金属相互接続部の第1レベルを同時に形成することにより、本発明のこの特定実施例によるプロセス工程の数を削減する。即ち、コンデンサ・エレメントの上側電極および金属相互接続部36を形成する第1メタライゼーション層を形成するためには、別個のプロセス工程は不要である。尚、金属相互接続部36は断面図で示されており、実際には、これは図面を貫通する方向に延びて、他のトランジスタの他のソース/ドレインのような、他のエレメントを相互接続している導電性トレースであることを注記しておく。

【0012】

コンデンサ・エレメントおよび金属相互接続の形成に続いて、第1層間誘電体18と同様に、図11に示すように第2層間誘電体44を堆積する。第2層間誘電体44に開口46をエッチングによって形成し、金属層48を堆積し、研磨し、ビア50を規定する。その後、第2金属層の堆積およびパターニングを行い、図12に示すように、金属相互接続部52で示す、第2レベルの金属相互接続部を形成する。その後、当技術分野では公知のように、適切な誘電体層および上位メタライゼーション層を堆積し、続いてパシベーションを行うことによって、素子を完成することができる。

【0013】

以上のように、コンデンサ・エレメントを有する新規の半導体デバイス形成方法を開示した。本発明によれば、好ましくは、コンデンサ・エレメントは、ドープ・ポリシリコンの代わりに、金属製の下側および上側電極プレートを採用し、金属電極の高いQ特性を利用する。加えて、前述の第2エッチング工程によって、電極および誘電体層が全て同一の幾何学的形状を有するように、コンデンサ・エレメントを規定する。したがって、エッジ効果のような、サイズが異なる電極プレートに伴う問題が解消する。加えて、同一の堆積工程およびパターニング工程を用いて上側電極および第1メタライゼーション層を同時に形成するので、プロセス・フローが簡略化され、既存のプロセス・フローに容易に組み込むことが可能となった。

【0014】

以上本発明の実施例に関して本発明を特に詳細に説明したが、当業者であれば、特許請求の範囲から逸脱することなく、本発明を変更可能であることは理解されよう。

【図面の簡単な説明】

【図1】コンタクト形成に先立つ、本発明の一実施例による工程を示す図。

【図2】堆積および研磨工程によるコンタクトの形成を示す図。

【図3】堆積および研磨工程によるコンタクトの形成を示す図。

【図4】本発明の一実施例によるコンデンサ・エレメントの数層の形成を示す図。

【図5】図4に示す層のパターニングを示す図。

【図6】図4に示す層のパターニングを示す図。

【図7】本発明による二重機能を有する最上部電極層の堆積を示す図。

【図8】コンデンサ・エレメントおよび金属相互接続層を形成するための層のパターニングを示す図。

【図9】コンデンサ・エレメントおよび金属相互接続層を形成するための層のパターニングを示す図。

【図10】層間誘電体,および電気コンタクトのためにそれを貫通するビアを形成する追加工程を示す図。

【図11】層間誘電体,および電気コンタクトのためにそれを貫通するビアを形成する追加工程を示す図。

【図12】層間誘電体,および電気コンタクトのためにそれを貫通するビアを形成する追加工程を示す図。

【符号の説明】

10 半導体基板

12,14 ソース/ドレイン

16 ゲート

18 第1層間誘電体

20 開口

22 導電層

24a,24b コンタクト

26 下側電極層

28 誘電体層

30 保護層

31 フォトレジスト

32 上側電極層

34 フォトレジスト層

36 金属相互接続部

38 下側電極プレート

40 誘電体プレート

42 上側電極プレート

44 第2層間誘電体

46 開口

48 金属層

50 ビア

52 金属相互接続部

Claims (3)

- 半導体素子の形成方法であって、

半導体基板(10)を用意する段階と、

前記半導体基板(10)上に層間誘電体(18)を形成する段階と、

前記層間誘電体(18)を覆うように下側電極層(26)を堆積する段階と、

前記下側電極層(26)上に誘電体層(28)を堆積する段階と、

前記誘電体層(28)上に保護層(30)を堆積する段階と、

前記下側電極層(26)、前記誘電体層(28)、及び前記保護層(30)を選択的にエッチングし、前記下側電極層(26)、前記誘電体層(28)、及び前記保護層(30)を部分的に除去し、前記層間誘電体(18)の一部を露出させる段階と、

前記保護層(30)及び前記層間誘電体(18)上に上側電極層(32)を堆積する段階と、

前記上側電極層(32)、前記保護層(30)、前記誘電体層(28)、及び前記下側電極層(26)をエッチングし、上側電極プレート(42)、誘電体プレート(40)、及び下側電極プレート(38)をそれぞれ形成してコンデンサ構造を形成する段階であって、前記上側電極層(32)のエッチングの間、前記層間誘電体(18)の上にある前記上側電極層(32)の少なくとも一部を残し、金属相互接続部(36)を規定する段階と

から成ることを特徴とする方法。 - 半導体素子の形成方法であって、

半導体基板(10)を用意する段階と、

前記半導体基板(10)上に層間誘電体(18)を形成する段階と、

前記層間誘電体(18)を覆うように下側電極層(26)を堆積する段階と、

前記下側電極層(26)上に誘電体層(28)を堆積する段階と、

前記誘電体層(28)上に保護層(30)を堆積する段階と、

前記下側電極層(26)、前記誘電体層(28)、及び前記保護層(30)を選択的にエッチングし、前記下側電極層(26)、前記誘電体層(28)、及び前記保護層(30)を部分的に除去し、前記層間誘電体(18)の一部を露出させる段階と、

前記保護層(30)及び前記層間誘電体(18)上に上側電極層(32)を堆積する段階と、

前記上側電極層(32)、前記保護層(30)、前記誘電体層(28)、及び前記下側電極層(26)をエッチングし、上側電極プレート(42)、誘電体プレート(40)、及び下側電極プレート(38)を形成してコンデンサ構造を形成する段階であって、前記上側電極プレート(42)及び前記下側電極プレート(38)が1X10−5オームcm未満の抵抗率を有する段階と

から成ることを特徴とする方法。 - 半導体素子の形成方法であって、

半導体基板(10)を用意する段階と、

前記半導体基板(10)上に層間誘電体(18)を形成する段階であって、第1コンタクト(24a)と、それを貫通する第2コンタクト(24b)とを有する前記層間誘電体(18)を形成する段階と、

前記第1コンタクト(24a)及び前記層間誘電体(18)上に下側電極層(26)を堆積し、前記下側電極層(26)と前記第1コンタクト(24a)との間に電気接続を形成する段階と、

前記下側電極層上に誘電体層(28)を堆積する段階と、

前記誘電体層(28)上に保護層(30)を堆積する段階と、

前記下側電極層(26)、前記誘電体層(28)、及び前記保護層(30)を選択的にエッチングし、前記下側電極層(26)、前記誘電体層(28)、及び保護層(30)を部分的に除去し、前記層間誘電体(18)及び前記第2コンタクト(24b)の一部を露出させる段階と、

前記保護層(30)及び前記層間電極(18)上に上側電極層(32)を一括堆積する段階であって、前記上側電極層(32)がAl及びCuから成る群より選ばれた材料により構成されている段階と、

前記上側電極層(32)、前記保護層(30)、前記誘電体層(28)、及び前記下側電極層(26)をエッチングし、上側電極プレート(42)、誘電体プレート(40)、及び下側電極プレート(38)を形成して、前記第1コンタクト(24a)上に位置しこれと電気的に接続するコンデンサ構造を形成する段階であって、前記上側電極層(36)のエッチングの間、前記第2コンタクト(24b)の上にある前記上側電極層(32)の一部を残し、金属相互接続(36)を規定する段階と

から成ることを特徴とする方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/135,634 US5985731A (en) | 1998-08-17 | 1998-08-17 | Method for forming a semiconductor device having a capacitor structure |

| US135634 | 1998-08-17 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000068453A JP2000068453A (ja) | 2000-03-03 |

| JP4286397B2 true JP4286397B2 (ja) | 2009-06-24 |

Family

ID=22468948

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP22910199A Expired - Lifetime JP4286397B2 (ja) | 1998-08-17 | 1999-08-13 | コンデンサ構造を有する半導体素子の形成方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US5985731A (ja) |

| JP (1) | JP4286397B2 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6316801B1 (en) | 1998-03-04 | 2001-11-13 | Nec Corporation | Semiconductor device having capacitive element structure and multilevel interconnection structure and method of fabricating the same |

| GB2337633B (en) * | 1998-05-20 | 2003-04-02 | Mitel Corp | Method of forming capacitors in a semiconductor device |

| KR100287176B1 (ko) * | 1998-06-25 | 2001-04-16 | 윤종용 | 고온산화를이용한반도체소자의커패시터형성방법 |

| KR100290895B1 (ko) * | 1998-06-30 | 2001-07-12 | 김영환 | 반도체 소자의 커패시터 구조 및 이의 제조 방법 |

| US6600185B1 (en) * | 1999-03-10 | 2003-07-29 | Oki Electric Industry Co., Ltd. | Ferroelectric capacitor with dielectric lining, semiconductor memory device employing same, and fabrication methods thereof |

| US6335557B1 (en) | 1999-11-17 | 2002-01-01 | Agere Systems Guardian Corp. | Metal silicide as a barrier for MOM capacitors in CMOS technologies |

| US6331460B1 (en) * | 1999-11-17 | 2001-12-18 | Agere Systems Guardian Corp. | Method of fabricating a mom capacitor having a metal silicide barrier |

| US6500724B1 (en) | 2000-08-21 | 2002-12-31 | Motorola, Inc. | Method of making semiconductor device having passive elements including forming capacitor electrode and resistor from same layer of material |

| US7192827B2 (en) * | 2001-01-05 | 2007-03-20 | Micron Technology, Inc. | Methods of forming capacitor structures |

| US6900498B2 (en) * | 2001-05-08 | 2005-05-31 | Advanced Technology Materials, Inc. | Barrier structures for integration of high K oxides with Cu and Al electrodes |

| US6677635B2 (en) * | 2001-06-01 | 2004-01-13 | Infineon Technologies Ag | Stacked MIMCap between Cu dual damascene levels |

| KR100662504B1 (ko) * | 2001-06-23 | 2007-01-02 | 매그나칩 반도체 유한회사 | 반도체 소자의 캐패시터 및 그 제조방법 |

| US6576526B2 (en) | 2001-07-09 | 2003-06-10 | Chartered Semiconductor Manufacturing Ltd. | Darc layer for MIM process integration |

| US20030197215A1 (en) * | 2002-02-05 | 2003-10-23 | International Business Machines Corporation | A dual stacked metal-insulator-metal capacitor and method for making same |

| FR2855323A1 (fr) * | 2003-05-20 | 2004-11-26 | St Microelectronics Sa | Procede de realisation d'un circuit electronique integre comprenant un condensateur |

| JP2006339343A (ja) | 2005-06-01 | 2006-12-14 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US8896096B2 (en) * | 2012-07-19 | 2014-11-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Process-compatible decoupling capacitor and method for making the same |

| US20190035562A1 (en) | 2017-05-26 | 2019-01-31 | Flash Power Capacitors, Llc | High energy density capacitor system and method |

| WO2018218164A1 (en) * | 2017-05-26 | 2018-11-29 | Flash Power Capacitors, Llc | High energy density capacitor and wireless charging system |

| US12218181B2 (en) | 2020-03-26 | 2025-02-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Barrier layer for metal insulator metal capacitors |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4821085A (en) * | 1985-05-01 | 1989-04-11 | Texas Instruments Incorporated | VLSI local interconnect structure |

| US4638400A (en) * | 1985-10-24 | 1987-01-20 | General Electric Company | Refractory metal capacitor structures, particularly for analog integrated circuit devices |

| US5109357A (en) * | 1988-04-22 | 1992-04-28 | Ramtron Corporation | DRAM memory cell and method of operation thereof for transferring increased amount of charge to a bit line |

| US5196909A (en) * | 1989-11-30 | 1993-03-23 | Sgs-Thomson Microelectronics, Inc. | Capacitor for DRAM cell |

| JPH03296262A (ja) * | 1990-04-13 | 1991-12-26 | Mitsubishi Electric Corp | 半導体メモリセル |

| US5119154A (en) * | 1990-12-03 | 1992-06-02 | Micron Technology, Inc. | Ferroelectric capacitor and method for forming local interconnect |

| JP3207227B2 (ja) * | 1991-11-08 | 2001-09-10 | ローム株式会社 | 不揮発性半導体記憶装置 |

| US5185689A (en) * | 1992-04-29 | 1993-02-09 | Motorola Inc. | Capacitor having a ruthenate electrode and method of formation |

| US5381302A (en) * | 1993-04-02 | 1995-01-10 | Micron Semiconductor, Inc. | Capacitor compatible with high dielectric constant materials having a low contact resistance layer and the method for forming same |

| US5479316A (en) * | 1993-08-24 | 1995-12-26 | Analog Devices, Inc. | Integrated circuit metal-oxide-metal capacitor and method of making same |

| US5576240A (en) * | 1994-12-09 | 1996-11-19 | Lucent Technologies Inc. | Method for making a metal to metal capacitor |

-

1998

- 1998-08-17 US US09/135,634 patent/US5985731A/en not_active Expired - Lifetime

-

1999

- 1999-08-13 JP JP22910199A patent/JP4286397B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000068453A (ja) | 2000-03-03 |

| US5985731A (en) | 1999-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4286397B2 (ja) | コンデンサ構造を有する半導体素子の形成方法 | |

| US6259128B1 (en) | Metal-insulator-metal capacitor for copper damascene process and method of forming the same | |

| US6180976B1 (en) | Thin-film capacitors and methods for forming the same | |

| US6593185B1 (en) | Method of forming embedded capacitor structure applied to logic integrated circuit | |

| US6344964B1 (en) | Capacitor having sidewall spacer protecting the dielectric layer | |

| JP2004193602A (ja) | 銅による後工程(beol)技術用の金属−絶縁体−金属(mim)コンデンサ及び金属レジスタを製造する方法 | |

| JP2002237523A (ja) | 金属−酸化物−金属コンデンサ及び関連する装置を製造する方法 | |

| KR100564626B1 (ko) | 대용량 mim 캐패시터 및 그 제조방법 | |

| JP4216588B2 (ja) | キャパシタの製造方法 | |

| US6680542B1 (en) | Damascene structure having a metal-oxide-metal capacitor associated therewith | |

| US20020028552A1 (en) | Capacitor of semiconductor integrated circuit and its fabricating method | |

| US7745280B2 (en) | Metal-insulator-metal capacitor structure | |

| US20090059466A1 (en) | Metal-insulator-metal capacitor and method for manufacturing the same | |

| US6677635B2 (en) | Stacked MIMCap between Cu dual damascene levels | |

| JP3820003B2 (ja) | 薄膜キャパシタの製造方法 | |

| US6040616A (en) | Device and method of forming a metal to metal capacitor within an integrated circuit | |

| US6472124B1 (en) | Self-aligned metal-insulator-metal capacitor for integrated circuits | |

| CN111952287B (zh) | 电容器件及其形成方法 | |

| KR19990015384A (ko) | 복합 반도체 장치의 커패시터 제조 방법 | |

| US7612399B2 (en) | Semiconductor integrated circuit devices | |

| JP2000252422A (ja) | 半導体装置及びその製造方法 | |

| KR100398570B1 (ko) | 강유전체 커패시터의 제조방법 | |

| KR100370130B1 (ko) | 반도체 소자의 제조방법 | |

| KR100721626B1 (ko) | 반도체 소자의 mim 캐패시터 형성방법 | |

| KR100527868B1 (ko) | 고용량 엠아이엠 캐패시터 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20040927 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060809 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081021 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081023 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090121 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090317 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090325 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120403 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4286397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120403 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130403 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130403 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140403 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |