JP4168397B2 - 高アスペクト比の半導体デバイス用のボロンドープ窒化チタン層 - Google Patents

高アスペクト比の半導体デバイス用のボロンドープ窒化チタン層 Download PDFInfo

- Publication number

- JP4168397B2 JP4168397B2 JP2003517937A JP2003517937A JP4168397B2 JP 4168397 B2 JP4168397 B2 JP 4168397B2 JP 2003517937 A JP2003517937 A JP 2003517937A JP 2003517937 A JP2003517937 A JP 2003517937A JP 4168397 B2 JP4168397 B2 JP 4168397B2

- Authority

- JP

- Japan

- Prior art keywords

- contact

- layer

- conductive contact

- titanium

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/482—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body (electrodes)

- H01L23/485—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body (electrodes) consisting of layered constructions comprising conductive layers and insulating layers, e.g. planar contacts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Semiconductor Memories (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

Description

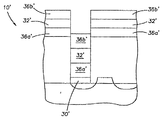

めにシード層上に堆積される。好ましくは、TiBxNy層は、約1から約15Torrの圧力、約550から約700℃の温度で熱CVDにより、TiCl4、NH3、B2H6並びに一つ若しくはそれ以上のキャリアガスのガス混合物から堆積される。基板はその後、例えば化学的機械的研磨により、余剰の材料を除去するために処理されて開口部に導電性コンタクトが形成され得る。

Claims (16)

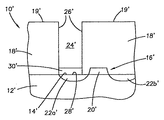

- 基板上に存在する絶縁性層中の開口部内に導電性コンタクトを形成する方法であって、

前記開口部内における前記基板上にチタンシリサイド層を形成することと、

前記チタンシリサイド層上にホウ窒化チタンを含む充填物を形成して、前記開口部を充填することと

を有する方法。 - 半導体デバイスのシリコン含有基板まで絶縁性層を介して延在するコンタクト開口部内にホウ窒化チタン層を備える導電性コンタクトであって、前記ホウ窒化チタン層は、前記開口部内における前記シリコン含有基板上に配置されたチタンシリサイドを含む層上にあり、前記コンタクト開口部は側壁により規定されている、導電性コンタクト。

- 絶縁性コンタクト開口部内に、基板内のアクティブエリアと電気的に接触する少なくとも1つの導電性コンタクト充填物を有する集積回路デバイスであって、前記少なくとも1つの導電性コンタクト充填物がホウ窒化チタンを含む、集積回路デバイス。

- 前記充填物を形成することが、前記開口部内への熱的化学気相堆積によって、四塩化チタン、アンモニア、及びジボランを含むガス混合物から前記ホウ窒化チタンを堆積することを含む、請求項1に記載の方法。

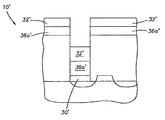

- 前記充填物を形成することが、窒化チタンとホウ窒化チタンが交互に重なった層を堆積して、前記開口部を充填することを含む、請求項1に記載の方法。

- 前記充填物を形成することが、四塩化チタン、アンモニア、及びジボランを含むガス混

合物、ならびにジボランを含まない、四塩化チタン及びアンモニアを含むガス混合物を用いる化学気相堆積を含む、請求項5に記載の方法。 - 前記充填物を形成することが、窒化チタン層を形成するための四塩化チタン及びアンモニアを含む第1ガス混合物と、1つ又はそれ以上のホウ窒化チタン層を形成するための四塩化チタン、アンモニア、及びジボランを含む第2ガス混合物と、を流すことによる熱的化学気相堆積を含む、請求項5に記載の方法。

- 前記コンタクトが窒化チタン層の間に置かれたホウ窒化チタン層を含む、請求項2に記載の導電性コンタクト。

- 前記開口部が約3:1以上の縦横比を有する、請求項2に記載の導電性コンタクト。

- 前記導電性コンタクトが、局部的相互接続、コンタクト、埋め込みコンタクト、ビア、プラグ、及び充填トレンチからなる群から選択される、請求項2に記載の導電性コンタクト。

- 前記導電性コンタクトが、前記開口部の側壁からの前記導電性コンタクトの剥離をなくす、前記開口部内での前記絶縁性層への密着レベル、及び、前記絶縁性層のクラックをなくす熱ストレスレベル、を前記導電性コンタクトに与える量のホウ素と、前記基板中に配置された導電性エリアとの電気的接触のための所定のレベルで前記コンタクトの導電性を維持する量の窒素と、を含む、請求項2に記載の導電性コンタクト。

- 前記導電性コンタクトが少なくとも約200オングストロームの厚さを有し、前記導電性コンタクトは、前記側壁から剥離することなく、かつ、前記絶縁性層にクラックを生じさせることなく、前記開口部の前記側壁に密着されている、請求項2に記載の導電性コンタクト。

- 前記ホウ窒化チタン層が約1000〜約3000オングストロームの厚さを有する、請求項2に記載の導電性コンタクト。

- 前記導電性コンタクトが、窒化チタンとホウ窒化チタンが交互に重なった層を含む、請求項2に記載の導電性コンタクト。

- 前記導電性コンタクトがメモリセル及び内部回路のアレイに結合される、請求項2に記載の導電性コンタクト。

- 導電性コンタクトを含む半導体回路であって、前記導電性コンタクトは、半導体デバイスのシリコン含有基板まで絶縁性層を介して延在するコンタクト開口部内のホウ窒化チタン層を備え、前記ホウ窒化チタン層は、前記開口部内における前記シリコン含有基板上のチタンシリサイドを含む層上にあり、前記コンタクト開口部は側壁により規定されている、半導体回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/918,919 US6696368B2 (en) | 2001-07-31 | 2001-07-31 | Titanium boronitride layer for high aspect ratio semiconductor devices |

| PCT/US2002/024088 WO2003012860A2 (en) | 2001-07-31 | 2002-07-30 | Boron-doped titanium nitride layer for high aspect ratio semiconductor devices |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005527098A JP2005527098A (ja) | 2005-09-08 |

| JP2005527098A5 JP2005527098A5 (ja) | 2006-01-05 |

| JP4168397B2 true JP4168397B2 (ja) | 2008-10-22 |

Family

ID=25441171

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003517937A Expired - Lifetime JP4168397B2 (ja) | 2001-07-31 | 2002-07-30 | 高アスペクト比の半導体デバイス用のボロンドープ窒化チタン層 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6696368B2 (ja) |

| EP (1) | EP1412976B1 (ja) |

| JP (1) | JP4168397B2 (ja) |

| KR (1) | KR100715389B1 (ja) |

| CN (1) | CN100352035C (ja) |

| AT (1) | ATE532212T1 (ja) |

| WO (1) | WO2003012860A2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030036242A1 (en) * | 2001-08-16 | 2003-02-20 | Haining Yang | Methods of forming metal-comprising materials and capacitor electrodes; and capacitor constructions |

| US7067416B2 (en) * | 2001-08-29 | 2006-06-27 | Micron Technology, Inc. | Method of forming a conductive contact |

| US6746952B2 (en) | 2001-08-29 | 2004-06-08 | Micron Technology, Inc. | Diffusion barrier layer for semiconductor wafer fabrication |

| US7164165B2 (en) * | 2002-05-16 | 2007-01-16 | Micron Technology, Inc. | MIS capacitor |

| US7150789B2 (en) * | 2002-07-29 | 2006-12-19 | Micron Technology, Inc. | Atomic layer deposition methods |

| US6890596B2 (en) * | 2002-08-15 | 2005-05-10 | Micron Technology, Inc. | Deposition methods |

| US6753271B2 (en) * | 2002-08-15 | 2004-06-22 | Micron Technology, Inc. | Atomic layer deposition methods |

| US6673701B1 (en) * | 2002-08-27 | 2004-01-06 | Micron Technology, Inc. | Atomic layer deposition methods |

| KR100487563B1 (ko) * | 2003-04-30 | 2005-05-03 | 삼성전자주식회사 | 반도체 소자 및 그 형성 방법 |

| US7233073B2 (en) * | 2003-07-31 | 2007-06-19 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device and method for fabricating the same |

| US7358172B2 (en) * | 2006-02-21 | 2008-04-15 | International Business Machines Corporation | Poly filled substrate contact on SOI structure |

| CN103022163A (zh) * | 2011-09-22 | 2013-04-03 | 比亚迪股份有限公司 | 一种晶硅太阳能电池及其制备方法 |

| EP3032575B1 (en) * | 2014-12-08 | 2020-10-21 | IMEC vzw | Method for forming an electrical contact. |

| US10854505B2 (en) | 2016-03-24 | 2020-12-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Removing polymer through treatment |

| US10355139B2 (en) | 2016-06-28 | 2019-07-16 | Sandisk Technologies Llc | Three-dimensional memory device with amorphous barrier layer and method of making thereof |

| US10361213B2 (en) * | 2016-06-28 | 2019-07-23 | Sandisk Technologies Llc | Three dimensional memory device containing multilayer wordline barrier films and method of making thereof |

| US20180331118A1 (en) * | 2017-05-12 | 2018-11-15 | Sandisk Technologies Llc | Multi-layer barrier for cmos under array type memory device and method of making thereof |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05267220A (ja) | 1992-03-19 | 1993-10-15 | Sony Corp | 半導体装置の密着層及びメタルプラグ形成方法 |

| US5747116A (en) | 1994-11-08 | 1998-05-05 | Micron Technology, Inc. | Method of forming an electrical contact to a silicon substrate |

| US5946594A (en) | 1996-01-02 | 1999-08-31 | Micron Technology, Inc. | Chemical vapor deposition of titanium from titanium tetrachloride and hydrocarbon reactants |

| FR2744461B1 (fr) * | 1996-02-01 | 1998-05-22 | Tecmachine | Nitrure de titane dope par du bore, revetement de substrat a base de ce nouveau compose, possedant une durete elevee et permettant une tres bonne resistance a l'usure, et pieces comportant un tel revetement |

| US5908947A (en) | 1996-02-09 | 1999-06-01 | Micron Technology, Inc. | Difunctional amino precursors for the deposition of films comprising metals |

| US5990021A (en) | 1997-12-19 | 1999-11-23 | Micron Technology, Inc. | Integrated circuit having self-aligned CVD-tungsten/titanium contact plugs strapped with metal interconnect and method of manufacture |

| US5700716A (en) | 1996-02-23 | 1997-12-23 | Micron Technology, Inc. | Method for forming low contact resistance contacts, vias, and plugs with diffusion barriers |

| JPH09306870A (ja) | 1996-05-15 | 1997-11-28 | Nec Corp | バリア膜の形成方法 |

| US5977636A (en) | 1997-01-17 | 1999-11-02 | Micron Technology, Inc. | Method of forming an electrically conductive contact plug, method of forming a reactive or diffusion barrier layer over a substrate, integrated circuitry, and method of forming a layer of titanium boride |

| US5976976A (en) | 1997-08-21 | 1999-11-02 | Micron Technology, Inc. | Method of forming titanium silicide and titanium by chemical vapor deposition |

| US5856237A (en) * | 1997-10-20 | 1999-01-05 | Industrial Technology Research Institute | Insitu formation of TiSi2/TiN bi-layer structures using self-aligned nitridation treatment on underlying CVD-TiSi2 layer |

| US6037252A (en) | 1997-11-05 | 2000-03-14 | Tokyo Electron Limited | Method of titanium nitride contact plug formation |

| US6156638A (en) | 1998-04-10 | 2000-12-05 | Micron Technology, Inc. | Integrated circuitry and method of restricting diffusion from one material to another |

| KR100331261B1 (ko) * | 1998-12-30 | 2002-08-22 | 주식회사 하이닉스반도체 | 반도체장치의 제조 방법 |

| US6086442A (en) | 1999-03-01 | 2000-07-11 | Micron Technology, Inc. | Method of forming field emission devices |

| US6329670B1 (en) | 1999-04-06 | 2001-12-11 | Micron Technology, Inc. | Conductive material for integrated circuit fabrication |

| US6200649B1 (en) * | 1999-07-21 | 2001-03-13 | Southwest Research Institute | Method of making titanium boronitride coatings using ion beam assisted deposition |

| US6635939B2 (en) * | 1999-08-24 | 2003-10-21 | Micron Technology, Inc. | Boron incorporated diffusion barrier material |

| DE10019164A1 (de) | 2000-04-12 | 2001-10-18 | Mannesmann Ag | SIM-Lock auf bestimmte IMSI-Bereiche einer SIM-Karte für Prepaid- und Postpaid-Karten |

| US6746952B2 (en) * | 2001-08-29 | 2004-06-08 | Micron Technology, Inc. | Diffusion barrier layer for semiconductor wafer fabrication |

| US7067416B2 (en) * | 2001-08-29 | 2006-06-27 | Micron Technology, Inc. | Method of forming a conductive contact |

-

2001

- 2001-07-31 US US09/918,919 patent/US6696368B2/en not_active Expired - Lifetime

-

2002

- 2002-07-30 EP EP02765900A patent/EP1412976B1/en not_active Expired - Lifetime

- 2002-07-30 CN CNB028152131A patent/CN100352035C/zh not_active Expired - Lifetime

- 2002-07-30 JP JP2003517937A patent/JP4168397B2/ja not_active Expired - Lifetime

- 2002-07-30 AT AT02765900T patent/ATE532212T1/de active

- 2002-07-30 KR KR1020047001585A patent/KR100715389B1/ko not_active Expired - Lifetime

- 2002-07-30 WO PCT/US2002/024088 patent/WO2003012860A2/en not_active Ceased

- 2002-11-04 US US10/287,203 patent/US6822299B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| ATE532212T1 (de) | 2011-11-15 |

| JP2005527098A (ja) | 2005-09-08 |

| US20030025206A1 (en) | 2003-02-06 |

| KR20040019102A (ko) | 2004-03-04 |

| WO2003012860A3 (en) | 2003-11-27 |

| US6822299B2 (en) | 2004-11-23 |

| EP1412976B1 (en) | 2011-11-02 |

| US20030075802A1 (en) | 2003-04-24 |

| US6696368B2 (en) | 2004-02-24 |

| CN100352035C (zh) | 2007-11-28 |

| EP1412976A2 (en) | 2004-04-28 |

| CN1539164A (zh) | 2004-10-20 |

| WO2003012860A2 (en) | 2003-02-13 |

| KR100715389B1 (ko) | 2007-05-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100546943B1 (ko) | 반도체장치형성방법 | |

| US6255209B1 (en) | Methods of forming a contact having titanium formed by chemical vapor deposition | |

| US6940172B2 (en) | Chemical vapor deposition of titanium | |

| JP4168397B2 (ja) | 高アスペクト比の半導体デバイス用のボロンドープ窒化チタン層 | |

| US6888252B2 (en) | Method of forming a conductive contact | |

| US6746952B2 (en) | Diffusion barrier layer for semiconductor wafer fabrication | |

| US5977636A (en) | Method of forming an electrically conductive contact plug, method of forming a reactive or diffusion barrier layer over a substrate, integrated circuitry, and method of forming a layer of titanium boride | |

| US6245674B1 (en) | Method of forming a metal silicide comprising contact over a substrate | |

| US6433434B1 (en) | Apparatus having a titanium alloy layer | |

| KR100543653B1 (ko) | 반도체 소자의 금속 배선 형성 방법 | |

| KR100607756B1 (ko) | 반도체 소자의 텅스텐 콘택 전극 제조 방법 | |

| KR20060058583A (ko) | 도전성 구조물, 이의 제조 방법, 이를 포함하는 반도체장치 및 그 제조 방법 | |

| KR100406562B1 (ko) | 금속배선형성방법 | |

| KR20050002094A (ko) | 반도체 소자의 금속배선 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050729 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050729 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070403 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20071004 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20071004 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20071005 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080325 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20080617 Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080617 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080715 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080724 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4168397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120815 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130815 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |