JP4142141B2 - コンピュータ・システム - Google Patents

コンピュータ・システム Download PDFInfo

- Publication number

- JP4142141B2 JP4142141B2 JP35991697A JP35991697A JP4142141B2 JP 4142141 B2 JP4142141 B2 JP 4142141B2 JP 35991697 A JP35991697 A JP 35991697A JP 35991697 A JP35991697 A JP 35991697A JP 4142141 B2 JP4142141 B2 JP 4142141B2

- Authority

- JP

- Japan

- Prior art keywords

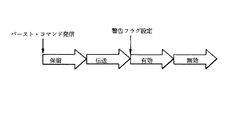

- burst

- memory

- buffer

- data

- instruction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/28—Handling requests for interconnection or transfer for access to input/output bus using burst mode transfer, e.g. direct memory access DMA, cycle steal

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/28—DMA

- G06F2213/2806—Space or buffer allocation for DMA transfers

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Memory System (AREA)

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP97300113A EP0853283A1 (en) | 1997-01-09 | 1997-01-09 | Computer system with memory controller for burst transfer |

| GB9723704.4 | 1997-11-11 | ||

| GB97300113.4 | 1997-11-11 | ||

| GBGB9723704.4A GB9723704D0 (en) | 1997-11-11 | 1997-11-11 | Computer systems |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH10232826A JPH10232826A (ja) | 1998-09-02 |

| JPH10232826A5 JPH10232826A5 (enExample) | 2005-06-23 |

| JP4142141B2 true JP4142141B2 (ja) | 2008-08-27 |

Family

ID=26147251

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP35991697A Expired - Fee Related JP4142141B2 (ja) | 1997-01-09 | 1997-12-26 | コンピュータ・システム |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6321310B1 (enExample) |

| JP (1) | JP4142141B2 (enExample) |

| DE (1) | DE69727465T2 (enExample) |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1061439A1 (en) * | 1999-06-15 | 2000-12-20 | Hewlett-Packard Company | Memory and instructions in computer architecture containing processor and coprocessor |

| EP1061438A1 (en) * | 1999-06-15 | 2000-12-20 | Hewlett-Packard Company | Computer architecture containing processor and coprocessor |

| JP4354583B2 (ja) * | 1999-09-09 | 2009-10-28 | 独立行政法人科学技術振興機構 | アクセス方法及びアクセス処理プログラムを記録した記録媒体 |

| US6859862B1 (en) * | 2000-04-07 | 2005-02-22 | Nintendo Co., Ltd. | Method and apparatus for software management of on-chip cache |

| GB2366426B (en) * | 2000-04-12 | 2004-11-17 | Ibm | Coprocessor data processing system |

| US6807587B1 (en) * | 2000-09-18 | 2004-10-19 | Xilinx Inc. | Methods and apparatuses for guaranteed coherency of buffered direct-memory-access data |

| US6862653B1 (en) * | 2000-09-18 | 2005-03-01 | Intel Corporation | System and method for controlling data flow direction in a memory system |

| US6711646B1 (en) * | 2000-10-20 | 2004-03-23 | Sun Microsystems, Inc. | Dual mode (registered/unbuffered) memory interface |

| US6557090B2 (en) * | 2001-03-09 | 2003-04-29 | Micron Technology, Inc. | Column address path circuit and method for memory devices having a burst access mode |

| JP2002366509A (ja) * | 2001-06-06 | 2002-12-20 | Mitsubishi Electric Corp | ダイレクトメモリアクセスコントローラおよびそのアクセス制御方法 |

| US7139873B1 (en) * | 2001-06-08 | 2006-11-21 | Maxtor Corporation | System and method for caching data streams on a storage media |

| CN1280734C (zh) * | 2001-09-07 | 2006-10-18 | 皇家菲利浦电子有限公司 | 用于分段存取控制的控制装置和方法和具有该控制装置的视频存储器装置 |

| JP2003140886A (ja) * | 2001-10-31 | 2003-05-16 | Seiko Epson Corp | インストラクションセット及びコンパイラ |

| US20030126591A1 (en) * | 2001-12-21 | 2003-07-03 | Youfeng Wu | Stride-profile guided prefetching for irregular code |

| US7389315B1 (en) * | 2002-02-28 | 2008-06-17 | Network Appliance, Inc. | System and method for byte swapping file access data structures |

| US7222170B2 (en) * | 2002-03-14 | 2007-05-22 | Hewlett-Packard Development Company, L.P. | Tracking hits for network files using transmitted counter instructions |

| JP2003281084A (ja) * | 2002-03-19 | 2003-10-03 | Fujitsu Ltd | 外部バスへのアクセスを効率的に行うマイクロプロセッサ |

| GB0221464D0 (en) | 2002-09-16 | 2002-10-23 | Cambridge Internetworking Ltd | Network interface and protocol |

| CN1602499A (zh) * | 2002-10-04 | 2005-03-30 | 索尼株式会社 | 数据管理系统、数据管理方法、虚拟存储设备、虚拟存储器控制方法、阅读器/写入器装置、 ic模块访问设备、以及ic模块访问控制方法 |

| US7191318B2 (en) * | 2002-12-12 | 2007-03-13 | Alacritech, Inc. | Native copy instruction for file-access processor with copy-rule-based validation |

| CN100416494C (zh) * | 2003-04-15 | 2008-09-03 | 威盛电子股份有限公司 | 显示控制器读取系统存储器中的存储数据的方法 |

| US7478016B2 (en) * | 2003-04-16 | 2009-01-13 | The Mathworks, Inc. | Block modeling input/output buffer |

| US7055000B1 (en) | 2003-08-29 | 2006-05-30 | Western Digital Technologies, Inc. | Disk drive employing enhanced instruction cache management to facilitate non-sequential immediate operands |

| US20050063008A1 (en) * | 2003-09-24 | 2005-03-24 | Perry Lea | System and method of processing image data |

| JP4455593B2 (ja) * | 2004-06-30 | 2010-04-21 | 株式会社ルネサステクノロジ | データプロセッサ |

| US7962731B2 (en) * | 2005-10-20 | 2011-06-14 | Qualcomm Incorporated | Backing store buffer for the register save engine of a stacked register file |

| US7844804B2 (en) * | 2005-11-10 | 2010-11-30 | Qualcomm Incorporated | Expansion of a stacked register file using shadow registers |

| US9201819B2 (en) | 2005-12-26 | 2015-12-01 | Socionext Inc. | Command processing apparatus, method and integrated circuit apparatus |

| US8572302B1 (en) * | 2006-10-13 | 2013-10-29 | Marvell International Ltd. | Controller for storage device with improved burst efficiency |

| US7617354B2 (en) * | 2007-03-08 | 2009-11-10 | Qimonda North America Corp. | Abbreviated burst data transfers for semiconductor memory |

| KR100891508B1 (ko) * | 2007-03-16 | 2009-04-06 | 삼성전자주식회사 | 가상 디엠에이를 포함하는 시스템 |

| US8806461B2 (en) * | 2007-06-21 | 2014-08-12 | Microsoft Corporation | Using memory usage to pinpoint sub-optimal code for gaming systems |

| US7730244B1 (en) * | 2008-03-27 | 2010-06-01 | Xilinx, Inc. | Translation of commands in an interconnection of an embedded processor block core in an integrated circuit |

| US8386664B2 (en) * | 2008-05-22 | 2013-02-26 | International Business Machines Corporation | Reducing runtime coherency checking with global data flow analysis |

| US8281295B2 (en) * | 2008-05-23 | 2012-10-02 | International Business Machines Corporation | Computer analysis and runtime coherency checking |

| US8285670B2 (en) * | 2008-07-22 | 2012-10-09 | International Business Machines Corporation | Dynamically maintaining coherency within live ranges of direct buffers |

| JP2010146084A (ja) * | 2008-12-16 | 2010-07-01 | Toshiba Corp | キャッシュメモリ制御部を備えるデータ処理装置 |

| US9417685B2 (en) * | 2013-01-07 | 2016-08-16 | Micron Technology, Inc. | Power management |

| KR102449333B1 (ko) * | 2015-10-30 | 2022-10-04 | 삼성전자주식회사 | 메모리 시스템 및 그것의 읽기 요청 관리 방법 |

| US9965326B1 (en) * | 2016-06-27 | 2018-05-08 | Rockwell Collins, Inc. | Prediction and management of multi-core computation deration |

| US10108374B2 (en) * | 2016-07-12 | 2018-10-23 | Nxp Usa, Inc. | Memory controller for performing write transaction with stall when write buffer is full and abort when transaction spans page boundary |

| US10409727B2 (en) * | 2017-03-31 | 2019-09-10 | Intel Corporation | System, apparatus and method for selective enabling of locality-based instruction handling |

| US10175912B1 (en) * | 2017-07-05 | 2019-01-08 | Google Llc | Hardware double buffering using a special purpose computational unit |

| US12066955B2 (en) * | 2021-05-19 | 2024-08-20 | Hughes Network Systems, Llc | System and method for enhancing throughput during data transfer |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4099236A (en) | 1977-05-20 | 1978-07-04 | Intel Corporation | Slave microprocessor for operation with a master microprocessor and a direct memory access controller |

| JPS5840214B2 (ja) | 1979-06-26 | 1983-09-03 | 株式会社東芝 | 計算機システム |

| US4589067A (en) | 1983-05-27 | 1986-05-13 | Analogic Corporation | Full floating point vector processor with dynamically configurable multifunction pipelined ALU |

| US5121498A (en) | 1988-05-11 | 1992-06-09 | Massachusetts Institute Of Technology | Translator for translating source code for selective unrolling of loops in the source code |

| JPH02250138A (ja) | 1989-01-18 | 1990-10-05 | Fujitsu Ltd | メモリ制御装置 |

| JPH02250137A (ja) | 1989-01-18 | 1990-10-05 | Fujitsu Ltd | メモリ制御装置 |

| US5175825A (en) | 1990-02-02 | 1992-12-29 | Auspex Systems, Inc. | High speed, flexible source/destination data burst direct memory access controller |

| EP0447145B1 (en) | 1990-03-12 | 2000-07-12 | Hewlett-Packard Company | User scheduled direct memory access using virtual addresses |

| GB2250615B (en) | 1990-11-21 | 1995-06-14 | Apple Computer | Apparatus for performing direct memory access with stride |

| EP0549924A1 (en) | 1992-01-03 | 1993-07-07 | International Business Machines Corporation | Asynchronous co-processor data mover method and means |

| US6438683B1 (en) | 1992-07-28 | 2002-08-20 | Eastman Kodak Company | Technique using FIFO memory for booting a programmable microprocessor from a host computer |

| US5708830A (en) | 1992-09-15 | 1998-01-13 | Morphometrix Inc. | Asynchronous data coprocessor utilizing systolic array processors and an auxiliary microprocessor interacting therewith |

| JP3220881B2 (ja) | 1992-12-29 | 2001-10-22 | 株式会社日立製作所 | 情報処理装置 |

| US5590307A (en) * | 1993-01-05 | 1996-12-31 | Sgs-Thomson Microelectronics, Inc. | Dual-port data cache memory |

| JP3417984B2 (ja) | 1993-09-10 | 2003-06-16 | 株式会社日立製作所 | キャッシュ競合削減コンパイル方法 |

| US5603007A (en) * | 1994-03-14 | 1997-02-11 | Apple Computer, Inc. | Methods and apparatus for controlling back-to-back burst reads in a cache system |

| US5627994A (en) * | 1994-07-29 | 1997-05-06 | International Business Machines Corporation | Method for the assignment of request streams to cache memories |

| US5537620A (en) | 1994-09-16 | 1996-07-16 | International Business Machines Corporation | Redundant load elimination on optimizing compilers |

| US5664230A (en) * | 1995-05-26 | 1997-09-02 | Texas Instruments Incorporated | Data processing with adaptable external burst memory access |

| US6209071B1 (en) * | 1996-05-07 | 2001-03-27 | Rambus Inc. | Asynchronous request/synchronous data dynamic random access memory |

| US5884050A (en) | 1996-06-21 | 1999-03-16 | Digital Equipment Corporation | Mechanism for high bandwidth DMA transfers in a PCI environment |

| US6085261A (en) * | 1996-07-29 | 2000-07-04 | Motorola, Inc. | Method and apparatus for burst protocol in a data processing system |

| JPH10124447A (ja) * | 1996-10-18 | 1998-05-15 | Fujitsu Ltd | データ転送制御方法及び装置 |

| US5784582A (en) * | 1996-10-28 | 1998-07-21 | 3Com Corporation | Data processing system having memory controller for supplying current request and next request for access to the shared memory pipeline |

| US6006289A (en) * | 1996-11-12 | 1999-12-21 | Apple Computer, Inc. | System for transferring data specified in a transaction request as a plurality of move transactions responsive to receipt of a target availability signal |

| EP0853283A1 (en) | 1997-01-09 | 1998-07-15 | Hewlett-Packard Company | Computer system with memory controller for burst transfer |

-

1997

- 1997-11-26 DE DE69727465T patent/DE69727465T2/de not_active Expired - Lifetime

- 1997-12-26 JP JP35991697A patent/JP4142141B2/ja not_active Expired - Fee Related

-

1998

- 1998-01-06 US US09/003,526 patent/US6321310B1/en not_active Expired - Fee Related

-

2000

- 2000-06-20 US US09/599,030 patent/US6336154B1/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE69727465T2 (de) | 2004-12-23 |

| US6321310B1 (en) | 2001-11-20 |

| JPH10232826A (ja) | 1998-09-02 |

| DE69727465D1 (de) | 2004-03-11 |

| US6336154B1 (en) | 2002-01-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4142141B2 (ja) | コンピュータ・システム | |

| US6076151A (en) | Dynamic memory allocation suitable for stride-based prefetching | |

| JP3816586B2 (ja) | 先取り命令を生成する方法とシステム | |

| US5375216A (en) | Apparatus and method for optimizing performance of a cache memory in a data processing system | |

| US7437517B2 (en) | Methods and arrangements to manage on-chip memory to reduce memory latency | |

| US5944815A (en) | Microprocessor configured to execute a prefetch instruction including an access count field defining an expected number of access | |

| US6665749B1 (en) | Bus protocol for efficiently transferring vector data | |

| US20030145136A1 (en) | Method and apparatus for implementing a relaxed ordering model in a computer system | |

| JP3425158B2 (ja) | マルチバッファデータキャッシュを具えているコンピュータシステム | |

| US6782454B1 (en) | System and method for pre-fetching for pointer linked data structures | |

| EP0439025B1 (en) | A data processor having a deferred cache load | |

| JP4599172B2 (ja) | フリーバッファプールを使用することによるメモリの管理 | |

| US6513107B1 (en) | Vector transfer system generating address error exception when vector to be transferred does not start and end on same memory page | |

| JPH08272779A (ja) | コンピュータ・システム | |

| US5893159A (en) | Methods and apparatus for managing scratchpad memory in a multiprocessor data processing system | |

| EP1039377B1 (en) | System and method supporting multiple outstanding requests to multiple targets of a memory hierarchy | |

| US6892280B2 (en) | Multiprocessor system having distributed shared memory and instruction scheduling method used in the same system | |

| US7321964B2 (en) | Store-to-load forwarding buffer using indexed lookup | |

| EP0862118B1 (en) | Computer system comprising a memory controller for burst transfer | |

| Berenbaum et al. | Architectural Innovations in the CRISP Microprocessor. | |

| EP0156307A2 (en) | Pipelined processor having dual cache memories | |

| JPH0756808A (ja) | データキャッシュバッファ及び記憶方法 | |

| JP2000148584A (ja) | プリフェッチ方法および装置 | |

| JP2668987B2 (ja) | データ処理装置 | |

| JP4680340B2 (ja) | プロセッサ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040927 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040927 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071225 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080317 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080415 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080520 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080612 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110620 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120620 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130620 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |