JP4119227B2 - 電力増幅装置、及び無線通信装置 - Google Patents

電力増幅装置、及び無線通信装置 Download PDFInfo

- Publication number

- JP4119227B2 JP4119227B2 JP2002328773A JP2002328773A JP4119227B2 JP 4119227 B2 JP4119227 B2 JP 4119227B2 JP 2002328773 A JP2002328773 A JP 2002328773A JP 2002328773 A JP2002328773 A JP 2002328773A JP 4119227 B2 JP4119227 B2 JP 4119227B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- modulated wave

- frequency

- output

- amplifying

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Amplifiers (AREA)

- Transmitters (AREA)

Description

【発明の属する技術分野】

本発明は、高周波電力を増幅する電力増幅装置、及びそれを用いた無線通信装置に関するものである。

【0002】

【従来の技術】

携帯電話端末やその基地局に用いられる電力増幅装置には、小型化及び低消費電力化のために、高出力かつ高効率な特性が要求される。特に、W−CDMA方式等の広帯域な送信信号を扱う場合には、電力増幅装置は、広帯域で歪みが少ないことが必要である。

【0003】

ところが、搬送波が変調波により変調された被変調波の周波数スペクトルは、通常変調波の周波数程度の帯域に分布している。このような周波数スペクトルを持つ被変調波の周波数の信号が電力増幅装置に入力されると、電力増幅装置に用いられているFET(Field effect Transistor)などの増幅素子の非線形性により、相互変調歪み成分以外に、被変調波の異なる周波数成分の信号どうしの差の周波数に現れる2次相互変調歪み成分が生じる。

【0004】

また、上述したように、高出力特性とするために、電力増幅装置の増幅素子として、FETを並列に多フィンガー構成したものや、FETを多数並列に合成してゲート幅を増大したもの等が用いられる。

【0005】

このような電力増幅装置にあっては、FETの出力側の、被変調波の変調波の周波数におけるインピーダンスがある程度高い場合には、被変調波の異なる周波数成分の信号どうしの差の周波数に現れる2次相互変調歪み成分が生じる。この2次相互変調歪み成分の周波数は、変調波の周波数付近に分布しており、この2次相互変調歪み成分が、再度FETのドレイン電極で増幅信号とミキシングを起こし、相互変調歪みをさらに悪化させる。これではFETの線形性が有効に利用されていないことになる。

【0006】

図10に、従来の歪み特性が良好な電力増幅装置1113を示す(例えば、特許文献1参照。)。図10の電力増幅装置1113は、入力端子1101、整合回路1102、1106、1110、FET1103、インダクタ1104、1109、キャパシタ1105、1108、2倍波短絡回路1107、出力端子1111、バイアス供給端子1112から構成される。

【0007】

整合回路1102は、入力端子1101とFET1103のドレイン側とのインピーダンスを整合させる回路である。

【0008】

インダクタ1104とキャパシタ1105とは、被変調波の周波数において直列共振する回路である。なお、被変調波の周波数は例えば1GHzであり、被変調波の変調波の周波数は例えば20MHzであるとする。

【0009】

整合回路1106は、FET1103の出力側と整合回路1110の側とのインピーダンスを整合させる回路である。

【0010】

2倍波短絡回路1107は、被変調波の周波数の高調波に対して短絡となる回路であり、例えば1/4波長ストリップラインである。

【0011】

キャパシタ1108、インダクタ1109、及びバイアス供給端子1112は、FET1103のゲートにバイアス電圧を供給するバイアスチョーク回路を構成する。

【0012】

整合回路1110は、整合回路1106の側と出力端子1111の側とのインピーダンスを整合させる回路である。

【0013】

次に、このような従来の電力増幅装置の動作を説明する。

【0014】

上述したように被変調波(1GHz)の周波数の信号は、その変調波(20MHz)により変調されたものであるので、被変調波の周波数の信号の周波数は、1GHz付近を中心として例えば±20MHz程度の帯域に渡って分布しているものとする。

【0015】

このような被変調波の周波数の信号が入力端子1101に入力されと、整合回路1102でインピーダンスが整合されて、FET1103のゲートに入力される。FET1103のドレインには、そのバイアス供給端子1112及びキャパシタ1108及びインダクタ1109で構成されるバイアスチョーク回路により、バイアス電圧が供給されている。

【0016】

従って、FET1103のゲートに入力された被変調波の周波数の信号は、FET1103で電力増幅され、FET1103のドレインから増幅信号として出力される。この増幅信号には、FET1103の非線形性のために、被変調波の異なる周波数成分の信号どうしの差の周波数に現れる2次相互変調歪み成分も含まれている。この2次相互変調歪み成分は、変調波の周波数(20MHz)付近に分布している。

【0017】

インダクタ1104及びキャパシタ1105で構成される共振回路は、変調波の周波数付近で直列共振するように定数を設定している。従って、そのインピーダンスは、変調波の周波数(20MHz)では短絡となり、被変調波の周波数(1GHz)では高インピーダンスとなる。

【0018】

従って、増幅成分に含まれる2次相互変調歪み成分は、インダクタ1104及びキャパシタ1105で構成される共振回路により短絡されることになるので、FET1103のドレイン側の電圧は、変調波の周波数で変動する信号成分が低減されることになる。従って、上述したようにドレインで2次相互変調歪み成分と増幅信号がミキシングを起こし相互歪みを悪化させるという不具合が低減される。

【0019】

FET1103から出力された増幅信号は、上述したようにインダクタ1104及びキャパシタ1105で2次相互変調歪み成分が平滑化され、整合回路1106でインピーダンスが整合される。2倍波短絡回路1107及びキャパシタ1108から構成される回路は、被変調波の高次高調波(2GHz程度及び2GHz以上の周波数スペクトルを持つ信号)で短絡となる。従って、整合回路1106から出力された増幅信号に含まれる被変調波の高次高調波は、2倍波短絡回路1107及びキャパシタ1108から構成される回路で短絡される。このように高次高調波が低減された増幅信号は、整合回路1110でインピーダンスが整合され、出力端子1111から出力される。

【0020】

【特許文献1】

特開2001−111364号公報

【0021】

【発明が解決しようとする課題】

このように、W−CDMAなどの通信方式で用いられる電力増幅装置は、広帯域で歪みが少ないことが必要である。そして、そのためには、上述したように増幅素子の出力側の被変調波の周波数(1GHz)に対して変調波の周波数(20MHz)における増幅素子の出力側の回路部分のインピーダンスをより低くすることが非常に重要である。

【0022】

また、図10で説明した従来の電力増幅装置1113が用いている構成以外の他の構成で、出力側の回路部分のインピーダンスを低くすることが出来ればその分設計の自由度が向上する。

【0023】

すなわち、従来とは異なった構成で、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスを低くすることが出来る電力増幅装置が必要であるという課題がある。

【0024】

また、図10で説明した従来の電力増幅装置1113では、インダクタ1104及びキャパシタ1105から構成される共振器で変調波の周波数(20MHz)におけるインピーダンスを短絡に近づけているが、実際にはインダクタ1104及びキャパシタ1105は変調波の周波数においてある程度の損失があるので、変調波の周波数において理想的な短絡を作るのが困難である。また、損失をより少なくするためには、インダクタ1104やキャパシタ1105の物理的サイズを大きくしなければならず、このため電力増幅装置のサイズが大きくなる。

【0025】

すなわち、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスをより低くするのは困難であり、従って増幅素子の線形性をより有効に利用することは困難であるという課題がある。

【0026】

W−CDMAなどの通信方式以前の無線通信システムでは、通信に用いられる周波数帯域が狭帯域であったため、このような課題は発生しなかったが、近年のW−CDMAなどの広帯域システムでは、重要な問題になってきている。

【0027】

本発明は、上記課題を考慮し、従来とは異なった構成で、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスを低くすることが出来る電力増幅装置、及び無線通信装置を提供することを目的とするものである。

【0028】

本発明は、上記課題を考慮し、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスをより低くすることが出来、増幅素子の線形性をより有効に利用することが出来る電力増幅装置、及び無線通信装置を提供することを目的とするものである。

【0029】

【課題を解決するための手段】

上述した課題を解決するために、第1の本発明は、被変調波の周波数の信号を2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力と前記第2の増幅素子の出力とを合成して出力する合成回路と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の周波数の信号の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の周波数の信号の変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方と前記第2のフィルタの他方との間に接続され、前記変調波の周波数帯の信号を、その位相を反転させて通過させる反転回路とを備え、

前記反転回路は、第1のインダクタと、

第2のインダクタと、

第4のインダクタと、

第1のキャパシタと、

第2のキャパシタと、

第3のキャパシタと、

第4のキャパシタとを有し、

前記第1のインダクタは、その一方が前記第1のフィルタの他方に接続され、その他方が前記第2のインダクタの一方に接続され、

前記第2のインダクタの他方は、前記第2のフィルタの他方に接続され、

前記第1のキャパシタは、その一方が前記第1のインダクタの一方に接続され、その他方が接地されており、

前記第2のキャパシタは、その一方が前記第1のインダクタの他方に接続され、その他方が接地されており、

前記第3のキャパシタは、その一方が前記第2のインダクタの他方に接続され、その他方が接地されており、

前記第4のインダクタは、その一方がバイアス電源に接続され、その他方が前記第1のインダクタの他方に接続されており、

前記第4のキャパシタは、その一方が前記第4のインダクタの一方に接続され、その他方が接地されている電力増幅装置である。

【0035】

また、第2の本発明は、被変調波の周波数の信号を少なくとも2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方に出力が接続され、前記第2のフィルタの他方に入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器とを備え、

前記第1の増幅素子の出力は外部に出力され、かつ前記第2の増幅素子の出力は終端されている電力増幅装置である。

【0036】

また、第3の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれの出力が接続された(N−1)分配回路の入力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記第1のフィルタの他方にその出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置である。

【0037】

また、第4の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記(N−1)個の第1のフィルタの他方は、前記反転増幅器の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続されており、前記第2の増幅素子の出力は終端されている電力増幅装置である。

【0038】

また、第5の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、入力が前記第2のフィルタの他方に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置である。

【0039】

また、第6の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

前記(N−1)個の反転増幅器の入力にそれぞれ一方が接続され、他方が前記第2の増幅素子の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる(N−1)個の第2のフィルタと、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置である。

また、第7の本発明は、被変調波の周波数の信号を少なくとも2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方に出力が接続され、前記第2のフィルタの他方に入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器とを備え、

少なくとも前記第1の増幅素子の出力は外部に出力されており、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置である。

また、第8の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれの出力が接続された(N−1)分配回路の入力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記第1のフィルタの他方にその出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置である。

また、第9の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記(N−1)個の第1のフィルタの他方は、前記反転増幅器の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続されており、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置である。

また、第10の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、入力が前記第2のフィルタの他方に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置である。

また、第11の本発明は、被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

前記(N−1)個の反転増幅器の入力にそれぞれ一方が接続され、他方が前記第2の増 幅素子の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる(N−1)個の第2のフィルタと、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置である。

【0041】

また、第12の本発明は、前記終端されているとは、前記第2の増幅素子の出力に終端抵抗を接続した、または前記第2の増幅素子の出力にキャパシタ及び/またはインダクタから構成される終端負荷を接続したことである第2〜6のいずれかの本発明の電力増幅装置である。

【0043】

また、第13の本発明は、第1、3〜6、8〜11の本発明のいずれかの電力増幅装置を複数備え、

それらの電力増幅装置の各分配回路は、共通化されており、同じ前記被変調波の周波数の信号を入力し、

それらの電力増幅装置の各合成回路は、共通化されており、一つに合成された出力信号を出力する電力増幅装置である。

【0044】

また、第14の本発明は、第2または第7の本発明の電力増幅装置複数と、

それらの電力増幅装置の外部に出力すべき出力を合成して出力する合成回路とを備え、

それらの電力増幅装置の各分配回路は共通化されており、同じ前記被変調波の周波数の信号を入力する電力増幅装置である。

【0045】

また、第15の本発明は、第1〜11の本発明のいずれかの電力増幅装置が形成されている誘電体多層基板を備えた電力増幅装置である。

【0046】

また、第16の本発明は、前記誘電体多層基板は、その上部に配置された半導体基板と、前記半導体基板の下部に配置された誘電体多層基板とを有する第15の本発明の電力増幅装置である。

【0047】

また、第17の本発明は、その内部に前記誘電体多層基板が配置されている内部整合基板を備えた第16の本発明の電力増幅装置である。

【0048】

また、第18の本発明は、前記被変調波の周波数の信号の周波数は、前記変調波の周波数帯の信号の周波数帯域の千倍以下である第1〜11の本発明のいずれかの電力増幅装置である。

【0049】

また、第19の本発明は、前記第1のフィルタ及び前記第2のフィルタは、前記変調波の周波数の信号の高調波成分を通過させる第1〜11の本発明のいずれかの電力増幅装置である。

【0050】

また、第20の本発明は、送信波を出力する送信回路を少なくとも備え、

前記送信回路には第1〜11の本発明のいずれかの電力増幅装置が用いられている無線通信装置である。

【0051】

【発明の実施の形態】

以下に、本発明の実施の形態を図面を参照して説明する。

【0052】

(第1の実施の形態)

図1に、本発明の第1の実施の形態における電力増幅装置61の構成を示す。

【0053】

図1の電力増幅装置61は、例えば図9に示す無線回路63の電力増幅器5として用いられるものである。

【0054】

まず、図9の無線回路63について簡単に説明する。

【0055】

無線回路63は、発振器1及び2、変調器3、ミキサ4及び9、電力増幅器5、低雑音増幅器8、アンテナ共用器6、アンテナ7から構成される。

【0056】

変調器3は、図示していないベースバンド部で発生されたベースバンドI信号及びベースバンドQ信号により、発振器1から出力される信号を変調する直交変調器である。なお、以下の説明ではベースバンドI信号及びベースバンドQ信号の周波数を変調波の周波数と呼ぶことにし、例えば変調波の周波数は20MHzであるとする。

【0057】

ミキサ4は、変調器3で変調された信号と発振器2から出力される信号とをミキシングすることにより送信周波数の信号に変換する回路である。

【0058】

なお、以下の説明では、送信周波数を被変調波の周波数と呼ぶことにし、例えば被変調波の周波数は1GHzであるとする。また従来の技術と同様に、被変調波の周波数の信号の周波数は、1GHz付近で変調周波数である±20MHz程度の帯域に分布しているものとする。

【0059】

電力増幅器5は、送信周波数の信号すなわち、被変調波の周波数の信号の電力を増幅し、この増幅信号をアンテナ共用器6に出力する回路である。

【0060】

アンテナ共用器6は、増幅信号をアンテナ7に導きまたアンテナ7で受信された受信信号を低雑音増幅器8に導く回路である。

【0061】

低雑音増幅器8は、アンテナ共用器6から出力された受信信号を増幅する回路である。

【0062】

ミキサ9は、低雑音増幅器8から出力された信号と発振器2から出力された信号とを合成することにより中間周波数の信号に変換する回路である。

【0063】

フィルタ10は、その中間周波数の信号に変換された信号の不要周波数成分を低減する回路である。

【0064】

復調器11は、中間周波数の信号と発振器1から出力される信号とを合成することにより、ベースバンドI信号及びベースバンドQ信号を復元する直交復調器である。

【0065】

このような、無線回路63は、W−CDMA等の通信方式を用いた携帯電話端末やその基地局の無線回路として用いられるものである。そして、図1の電力増幅装置61を、無線回路63の電力増幅器5として用いることにより、広帯域に渡って良好な歪み特性を有し、かつ消費電力が少ない無線回路63を実現することが出来る。以下に、無線回路63の電力増幅器5として用いられる図1の電力増幅装置61について説明する。

【0066】

すなわち、図1において、電力増幅装置61の入力端子21には整合回路/分配回路22の入力が接続されており、また、整合回路/分配回路22の2つの出力には、それぞれにはFET23aのゲート及びFET23bのゲートが接続されている。FET23aのドレインは、直流遮断用のキャパシタ27aを介して合成回路/整合回路28の一方の入力に接続されており、FET23bのドレインは、直流遮断用キャパシタ27bを介して合成回路/整合回路28の他方の入力に接続されている。また、合成回路/整合回路28の出力は、出力端子29に接続されている。

【0067】

また、FET23a及びFET23bのソースはともに接地されている。そして、FET23aのドレインには、2倍波短絡/バイアスチョーク回路24aの一方が接続されている。同様に、FET24aのドレインには、2倍波短絡/バイアスチョーク回路24bの一方が接続されている。

【0068】

2倍波短絡/バイアスチョーク回路24aの他方と2倍波短絡/バイアスチョーク回路24bの他方との間には差周波反転回路26が接続されており、差周波反転回路26の一方には、2倍波バイパス用のキャパシタ25aの一方が接続されており、その他方は接地されている。また、同様に、差周波反転回路26の他方には、2倍波バイパス用のキャパシタ25bの一方が接続されており、その他方は接地されている。

【0069】

入力端子21は、入力信号である被変調波の周波数の信号が入力される端子である。また、出力端子29は、出力信号である増幅信号が出力される端子である。

【0070】

整合回路/分配回路22は、入力端子側と、FET23aのゲート側及びFET23bのゲート側とのインピーダンスを整合させるとともに、入力端子21から入力される被変調波の周波数の信号を2分配して、FET23aのゲート及びFET23bのゲートに入力する回路である。

【0071】

FET23a、及びFET23bは、それぞれそのゲートに入力された被変調波の周波数の信号の電力を増幅する増幅素子である。

【0072】

2倍波短絡/バイアスチョーク回路24aは、被変調波の周波数の信号(1GHz程度の周波数の信号)を通過させず、変調波の周波数の信号(20MHz程度の周波数の信号)を通過させるフィルタの機能と、被変調波の周波数の高次高調波の周波数におけるインピーダンスを短絡する機能と、FET23aのドレインにバイアス電圧を供給するバイアスチョーク回路の機能とを有する回路である。

【0073】

同様に、2倍波短絡/バイアスチョーク回路24bは、被変調波の周波数の信号(1GHz程度の周波数の信号)を通過させず、変調波の周波数の信号(20MHz程度の周波数の信号)を通過させるフィルタの機能と、被変調波の周波数の高次高調波の周波数におけるインピーダンスを短絡する機能と、FET23bのドレインにバイアス電圧を供給するバイアスチョーク回路の機能とを有する回路である。

【0074】

差周波反転回路26は、変調波の周波数の信号が通過した場合、その変調波の周波数の信号の位相を反転する回路である。

【0075】

合成回路/整合回路28は、キャパシタ27aの側及びキャパシタ27bの側と、出力端子29との側とのインピーダンスを整合させるとともに、キャパシタ27aを通過した増幅信号とキャパシタ27bを通過した増幅信号とを合成して出力端子29に出力する回路である。

【0076】

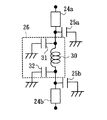

図2に、2倍波短絡/バイアスチョーク回路24a、2倍波短絡/バイアスチョーク回路24b、及び差周波反転回路26の部分の詳細な構成を示す。

【0077】

すなわち、差周波反転回路26は、キャパシタ31及び32と、インダクタ30とから構成される。インダクタ30の一方は、2倍波短絡/バイアスチョーク回路24aの他方に接続されており、インダクタ30の他方は、2倍波短絡/バイアスチョーク回路24bの他方に接続されている。そして、インダクタ30の一方には、キャパシタ31の一方が接続され、キャパシタ31の他方は接地されている。またインダクタ30の他方には、キャパシタ32の一方が接続され、キャパシタ32の他方は接地されている。キャパシタ31及びキャパシタ32のそれぞれのキャパシタンスと、インダクタ30のインダクタンスとは、差周波反転回路26を通過した変調波の周波数の信号(20MHz)の位相が180度反転されるように調整されているものである。

【0078】

また、2倍波短絡/バイアスチョーク回路24a及び24bは、それぞれ被変調波の周波数の波長の1/4の長さを有するストリップライン線路に、図示していないバイアス供給端子の出力端が接続され、バイアス供給端子の入力端は、直流バイアスを供給するバイアス供給端子に接続された構成を持つ。

【0079】

次に、このような本実施の形態の動作を説明する。

【0080】

入力端子21に被変調波の周波数の信号が入力されたとする。上述したように、この信号は1GHzの周波数の信号であって、変調波の周波数(20MHz)程度の帯域で周波数が分布している信号である。

【0081】

入力端子21に入力された被変調波の周波数の信号は、整合回路/分配回路22で2分配され、2分配された被変調波の周波数の信号は、それぞれFET23aのゲート及びFET24bのゲートに入力される。また、このとき、整合回路/分配回路22は、入力端子21の側とFET23aのゲート側及びFET23bのゲート側とのインピーダンスを整合させる。

【0082】

FET23aのドレインには、2倍波短絡/バイアスチョーク回路24aから直流バイアスが供給されており、FET23aのゲートに出力された被変調波の周波数の信号は、FET23aで増幅されて、そのドレインに出力される。

【0083】

同様に、FET23bのドレインには、2倍波短絡/バイアスチョーク回路24bから直流バイアスが供給されており、FET23bのゲートに出力された被変調波の周波数の信号は、FET23bで増幅されて、そのドレインに出力される。

【0084】

FET23a及びFET23bは線形な特性を有するが、高効率動作時には非線形な特性が顕著になってくる。この非線形な特性のために、被変調波の周波数の信号がFET23aで増幅された信号である増幅信号には、歪み成分が含まれることになる。このような歪み成分には、被変調波の周波数の信号の高次高調波の歪み成分(2GHz程度以上の周波数の歪み成分)、被変調波の周波数の近傍の周波数に現れる3次相互変調歪み成分(1GHz近傍に現れる歪み成分)、及び増幅されるべき被変調波の周波数の信号のうちの異なった周波数成分どうしの差の周波数を有する2次相互変調歪み成分(20MHz程度の周波数の歪み成分)などがある。

【0085】

2倍波短絡/バイアスチョーク回路24aは、2次相互変調歪み成分すなわち変調波の周波数の信号を通過させ、高次高調波の周波数の信号は短絡して全反射させる。また被変調波の周波数では高インピーダンスであるので被変調波の周波数の信号は通過させない。従って、このような歪み成分をも含む増幅信号が、FET23aのドレインから出力されると、増幅信号のうち、2次相互変調歪み成分は、2倍波短絡/バイアスチョーク回路24aの一方に入力され、この変調波の周波数の信号は、2倍波短絡/バイアスチョーク回路24aを通過する。一方、変調波の周波数の信号は、差周波反転回路26に入力される。

【0086】

一方、このような増幅信号のうちの被変調波の信号は、2倍波短絡/バイアスチョーク回路24aを通過せず、キャパシタ27aを介して合成回路/整合回路28の一方の入力に出力される。

【0087】

2倍波短絡/バイアスチョーク回路24aを通過した変調波の周波数の信号は、差周波反転回路26を通過することによりその位相が180度反転される。すなわち、差周波反転回路26のキャパシタ31及び32のそれぞれのキャパシタンスと、インダクタ30のインダクタンスは、通過した変調波の周波数の位相が180度反転するように予め調整されている。差周波反転回路26を通過した変調波の周波数の信号は、さらに2倍波短絡/バイアスチョーク回路24bを通過して、FET23bのドレイン端にまで達する。この変調波の周波数の信号と、FET23bで増幅され、そのドレイン端に出力された増幅成分に含まれる2次相互変調歪み成分である変調波の周波数の信号とは位相が180度異なっている。従ってFET23bのドレイン端でこれら2つの変調波の周波数の信号が互いに他を打ち消し合うことになる。従って、FET23bのドレインでは、変調波の周波数の信号が打ち消されているので、2次相互変調歪み成分である変調波の周波数の信号がFET23bのドレインで被変調波の信号とミキシングされることにより相互変調歪みを悪化させるという事態を避けることが出来る。

【0088】

同様に、FET23bの増幅信号は、2倍波反転回路26で180度位相を反転されて、FET23aのドレイン端に達する。そして、この変調波の信号は、FET23aのドレイン端から出力される増幅信号に含まれる2次相互変調歪み成分である変調周波数の信号とは位相が180度異なっているので、これら2つの変調波の周波数の信号はFET23aのドレインで互いに打ち消し合うことになる。従って、FET23aにおいても、FET23bと同様にドレインで変調波の周波数の信号と被変調波の周波数の信号とがミキシングされることにより相互変調歪みを悪化させるという事態を避けることが出来る。

【0089】

また、FET23bから出力された増幅信号のうちの被変調波の周波数の信号は、2倍波短絡/バイアスチョーク回路24bを通過せず、キャパシタ27bを介して合成回路/整合回路28の他方の入力に出力される。

【0090】

合成回路/整合回路28は、一方の入力及び他方の入力に入力された変調波の信号を合成し、出力端子29に出力する。なお、このとき合成回路/整合回路28は、キャパシタ27a及びキャパシタ27bの側と、出力端子29の側とのインピーダンスを整合させる。

【0091】

このようにして増幅された被変調波の信号が出力端子29から出力される。

【0092】

なお、本実施の形態では、差周波反転回路26、及び2倍波短絡/バイアスチョーク回路24a及び24bが図2のように構成されているとして説明したが、これに限らず、図3のように構成されていても構わない。

【0093】

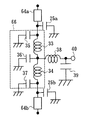

図3は、2倍波短絡/バイアスチョーク回路24a及び24bの代わりに2倍波短絡回路64a及び64bを用い、差周波反転回路26の代わりに、差周波反転回路66を用い、差周波反転回路66にバイアスチョーク回路を接続した構成である。

【0094】

図3において、2倍波短絡回路64a及び64bはそれぞれ、被変調波の周波数における波長の1/4倍の長さを有するストリップライン線路である。また、差周波反転回路66は、インダクタ33、34、及びキャパシタ35、36、37から構成される。インダクタ33の一方は、2倍波短絡回路64aの他方に接続され、インダクタ33の他方は、インダクタ34の一方に接続され、インダクタ34の他方は、2倍波短絡回路64bの他方に接続されている。また、インダクタ33の一方にはキャパシタ35の一方が接続され、キャパシタ33の他方は接地されており、インダクタ33の他方には、キャパシタ36の一方が接続され、キャパシタ36の他方は接地されており、インダクタ34の他方にはキャパシタ37の一方が接続され、キャパシタ37の他方は接地されている。

【0095】

インダクタ33及び34のそれぞれのインダクタンスと、キャパシタ35、36及び37のそれぞれのキャパシタンスは、差周波反転回路26と同様に、変調波の周波数の信号が通過した場合、その位相が180度反転するように予め調整されているものである。

【0096】

また、バイアスチョーク回路は、バイアス供給端子40にインダクタ38の一方とキャパシタ39の一方が接続され、キャパシタ39の他方は接地され、インダクタ38の他方はインダクタ33の他方に接続された構成を有する。

【0097】

図2の代わりに図3のような回路を用いた場合であっても、FET23a及び23bに直流バイアスを供給することが出来、また、差周波反転回路66を通過する変調波の周波数の信号の位相を180度反転することが出来る。従って、図2の回路を用いた場合と同等の効果を得ることが出来る。

【0098】

このように本実施の形態の電力増幅装置61は、変調波の周波数の信号どうしが、FET23a及びFET23bのそれぞれのドレイン端で互いに他を打ち消し合うので、ドレインで、変調波の周波数の信号と被変調波の周波数の信号とがミキシングすることによる相互変調歪みの悪化を防止することが出来る。

【0099】

図5は、本実施の形態の電力増幅装置61を誘電体基板71〜76を積層した誘電体積層構造内に形成した例である。

【0100】

誘電体基板71には整合回路/分配回路22、FET23a、23b、チップコンデンサとして形成されたキャパシタ27a及び27b、及び合成回路/整合回路28が形成されている。

【0101】

誘電体基板71の下層に配置された誘電体基板72には、シールド電極が形成されており、誘電体基板72の下層に配置された誘電体基板73には、2倍波短絡/バイアスチョーク回路24a及び24b、インダクタ30が形成されており、誘電体基板73と、誘電体基板72及び誘電体基板74のシールド電極である接地層との間にバイパスキャパシタ25a及び25bが形成されている。

【0102】

また、誘電体基板73の下層に配置された誘電体基板74にはシールド電極が形成されており、誘電体基板73の下層に配置された誘電体基板75には、キャパシタ31及び32が形成されている。そして、誘電体基板75の下層に配置された誘電体基板76にはシールド電極が形成されている。

【0103】

図6は、本実施の形態の電力増幅装置61を半導体基板上の誘電体層に形成した例である。

【0104】

半導体基板77にはポリイミドなどの絶縁膜が形成されており、半導体基板77上には、整合回路/分配回路22、FET23a及び23b、合成回路/整合回路28が形成されている。

【0105】

半導体基板77の下層には、誘電体基板78が積層されており、誘電体基板78には、2倍波短絡/バイアスチョーク回路24a及び24b、キャパシタ27a及び27bが形成されており、誘電体基板78と、誘電体基板79のシールド電極である接地層との間にバイパスキャパシタ25a及び25bが形成されている。誘電体基板78の下層にはシールド電極が形成された誘電体基板79が形成されており、その下層には誘電体基板80が形成されている。誘電体基板80にはキャパシタ31及び32、及びインダクタ30が形成されている。

【0106】

図7は、本実施の形態の電力増幅装置61をセラミック高周波パッケージ内に実装した例を示す。なお、図7のものはハイパワー用であり携帯電話の基地局に用いられるものである。また、図7の電力増幅装置61は図3の回路を用いたものである。

【0107】

高周波パッケージ81の内部に配置されている内部整合基板82に半導体基板83aと、誘電体基板83b、84〜88がこの順で積層された誘電体多層基板が実装されており、入力端子21、出力端子29、バイアス供給端子40が高周波パッケージ81の内部から外部に引き出されている。

【0108】

半導体基板83aには、整合回路/分配回路22、FET23a及び23b、キャパシタ39、合成回路/整合回路28が形成されている。誘電体基板83bの下層には、誘電体基板84が形成されている。誘電体基板84には、キャパシタ27a及び27bが形成されている。

【0109】

誘電体基板84の下層には、シールド電極が形成された誘電体基板85が形成されており、その下層には誘電体基板86が形成されている。誘電体基板86には、インダクタ38、33及び34、及び2倍波短絡/バイアスチョーク回路64a及び64bが形成されており、誘電体基板86と、誘電体基板85のシールド電極である接地層との間にバイパスキャパシタ25a及び25bが形成されている。

【0110】

誘電体基板86の下層には誘電体基板87が形成されており、誘電体基板87と、誘電体基板88のシールド電極である接地層との間にキャパシタ35、36、37、39が形成されている。誘電体基板87の下層にはシールド電極が形成された誘電体基板88が形成されている。

【0111】

なお、本実施の形態では、被変調波の周波数の信号の周波数が1GHzであり、変調波の周波数の信号の周波数帯域が20MHzであるとして説明したが、これに限らない。被変調波の周波数の信号の周波数が、変調波の周波数帯の信号の周波数帯域の千倍以下であれば、従来技術と比較して、本実施の形態の方がより良好に相互変調歪みを改善することが出来る。

【0112】

このように、被変調波の周波数の信号が、変調波の周波数帯の信号の周波数帯域の千倍以下になる例として次のようなものがある。

【0113】

まず、通信方式としてCDMA2000を用いる場合がある。この場合、被変調波の周波数の信号として800MHz帯の周波数の信号及び2GHz帯の周波数の信号を用いる。CDMA2000で被変調波の周波数の信号として800MHz帯の周波数の信号を用いる場合、変調波の周波数帯の信号の周波数帯域は1.23MHzとなり、被変調波の周波数の信号の周波数が変調波の周波数帯の信号の周波数帯域の千倍以下になっている。従って良好に相互変調歪みを改善することが出来る。

【0114】

また、CDMA2000の2GHz帯はデータ通信専用に用いられる周波数帯であり、高速なデータ通信を行うために複数チャンネルを使用することが行われる。すなわち、高速通信のためには最大3チャンネル分の周波数帯域を使用してデータ通信が行われ、最大3チャンネル分の周波数帯域を使用する場合には、変調波の周波数帯の信号の周波数帯域が3.69MHzになっている。このようにCDMA2000における2GHz帯は、パソコンや、PDAと携帯電話との機能が統合された端末でデータ通信を行う際に用いられるものである。この場合にも被変調波の周波数の信号の周波数が変調波の周波数帯の信号の周波数帯域の千倍以下になっており、従来技術に比べてより良好に相互変調歪みを改善することが出来る。

【0115】

また、無線LANの規格であるIEEE802.11aでは、被変調波の周波数の信号の周波数として5GHz帯を用い、変調波の周波数帯の信号の周波数帯域は、20MHzであるので、上記と同様に良好に相互変調歪みを改善することが出来る。

【0116】

また、いわゆる第4世代の移動帯通信では被変調波の周波数の信号の周波数として5GHz帯の周波数帯を用い、変調波の周波数帯の信号の周波数帯域は100MHzの帯域である。従ってこの場合にも、被変調波の周波数の信号の周波数が変調波の周波数帯の信号の周波数帯域の千倍以下になっているので、従来技術に比べてより良好に相互変調歪みを改善することが出来る。

【0117】

また、デジタルテレビ放送の放送局やその中継局では被変調波の周波数の信号の周波数が400MHz〜700MHzの周波数を用いる。そして、変調波の周波数帯の信号の周波数帯域は、6MHzである。従って、この場合も、被変調波の周波数の信号の周波数が変調波の周波数帯の信号の周波数帯域の千倍以下になっているので、従来技術に比べてより良好に相互変調歪みを改善することが出来る。

【0118】

なお、本実施の形態では、2倍波短絡/バイアスチョーク回路が被変調波の周波数の高次高調波の周波数におけるインピーダンスを短絡されるとして説明したが、被変調波の周波数の高次高調波の周波数の信号を通過させる働きを有するものであってもよい。このような場合の方が電力増幅装置として良好な特性が得られる。

【0119】

このように、本実施の形態によれば、2倍波短絡/バイアスチョーク回路24a及び24b等と差周波反転回路26とを一体化する、すなわち、一つの積層体に一体化することにより、回路全体の小型化を図ることが出来る。

【0120】

(第2の実施の形態)

次に、本発明の第2の実施の形態について説明する。

【0121】

図4に、第2の実施の形態における電力増幅装置62の構成を示す。

【0122】

本実施の形態の電力増幅装置62は、例えば第1の実施の形態で説明した図9の無線回路63の電力増幅器5として用いられるものである。

【0123】

電力増幅装置62の入力端子21には整合回路/分配回路41の入力が接続されており、また、整合回路/分配回路41の3つの出力には、それぞれにはFET42aのゲート及びFET42bのゲート及びFET42cのゲートが接続されている。

【0124】

FET42aのドレインは、直流遮断用のキャパシタ27aを介して合成回路/整合回路28の2つの入力の一方に接続されており、FET42cのドレインは、直流遮断用キャパシタ27bを介して合成回路/整合回路28の他方の入力に接続されている。また、合成回路/整合回路28の出力は、出力端子29に接続されている。また、FET42bのドレインは、終端抵抗48により終端されている。

【0125】

また、FET42a、42b、及び42cのソースはそれぞれ接地されている。そして、FET42aのドレインには、2倍波短絡回路43aの一方が接続されている。同様に、FET42cのドレインには、2倍波短絡回路43dの一方が接続されている。また、FET42bのドレインに接続された図示していない分配回路の一方の出力に2倍波短絡回路43bの一方及びその分配回路の他方の出力に2倍波短絡回路43cの一方が接続されている。

【0126】

2倍波短絡回路43aの他方と2倍波短絡回路43bの他方との間には反転増幅器45aが接続されており、反転増幅器45aの出力及び入力にはそれぞれ、2倍波バイパス用のキャパシタ44aの一方及び2倍波バイパス用のキャパシタ46aの一方が接続されており、キャパシタ44aの他方及びキャパシタ46aの他方はそれぞれ接地されている。

【0127】

また、2倍波短絡回路43dの他方と2倍波短絡回路43cの他方との間には反転増幅器45bが接続されており、反転増幅器45bの出力及び入力にはそれぞれ、2倍波バイパス用のキャパシタ44bの一方及び2倍波バイパス用のキャパシタ46bの一方が接続されており、キャパシタ44bの他方及びキャパシタ46bの他方はそれぞれ接地されている。

【0128】

入力端子21は、第1の実施の形態と同様に入力信号である被変調波の周波数の信号が入力される端子である。また、出力端子29は、出力信号である増幅信号が出力される端子である。

【0129】

整合回路/分配回路41は、入力端子21側と、FET42aのゲート側及びFET42bのゲート側及びFET42cのゲート側とのインピーダンスをそれぞれ整合させるとともに、入力端子21から入力される被変調波の周波数の信号を3分配して、FET42aのゲート及びFET42bのゲート及びFET42cのゲートに入力する回路である。

【0130】

FET42a、42b、及び42cは、それぞれそのゲートに入力された被変調波の周波数の信号の電力を増幅する増幅素子である。FET42bのFETサイズは、FET42aやFET42cのFETサイズよりも小さいものとする。また、FET42aとFET42cとはFETサイズが同一であるとする。

【0131】

2倍波短絡回路43a、43b、43c、及び43dは、被変調波の周波数の信号(1GHz程度の周波数の信号)を通過させず、変調波の周波数の信号(20MHz程度の周波数の信号)を通過させるフィルタの機能と、被変調波の周波数の高次高調波の周波数におけるインピーダンスを短絡する機能とを有する回路である。

【0132】

反転増幅器45a及び45bは、変調波の周波数の信号を180度位相を反転させて増幅する回路である。

【0133】

合成回路/整合回路28は、キャパシタ27aの側及びキャパシタ27bの側と、出力端子29との側とのインピーダンスを整合させるとともに、キャパシタ27aを通過した増幅信号とキャパシタ27bを通過した増幅信号とを合成して出力端子29に出力する回路である。

【0134】

次に、このような本実施の形態の動作を説明する。

【0135】

入力端子21に被変調波の周波数の信号が入力されたとする。上述したように、この信号は1GHzの周波数の信号であって、変調波の周波数(20MHz)程度の帯域で周波数が分布している信号である。

【0136】

入力端子21に入力された被変調波の周波数の信号は、整合回路/分配回路41で3分配され、3分配された被変調波の周波数の信号は、それぞれの出力からそれぞれFET42aのゲート及びFET42bのゲート及びFET42cのゲートに入力される。また、このとき、整合回路/分配回路41は、入力端子21の側とFET42a、42b、及び42cのそれぞれのゲート側とのインピーダンスを整合させる。

【0137】

FET42a、42b、及び42cのそれぞれのゲートに出力された被変調波の周波数の信号は、それぞれFET42a、42b、42cで増幅されて、それぞれのドレインに出力される。

【0138】

第1の実施の形態と同様に、FET42a、42b、及び42cはそれぞれ線形な特性を有するが、高効率動作時には非線形な特性が顕著になってくる。この非線形な特性のために、被変調波の周波数の信号がFET42a、42b、及び42cでそれぞれ増幅された信号である増幅信号には、歪み成分が含まれることになる。このような歪み成分には、被変調波の周波数の信号の高次高調波の歪み成分(2GHz程度以上の周波数の歪み成分)、被変調波の周波数の近傍の周波数に現れる3次相互変調歪み成分(1GHz近傍に現れる歪み成分)、及び増幅されるべき被変調波の周波数の信号のうちの異なった周波数成分どうしの差の周波数を有する2次相互変調歪み成分(20MHz程度の周波数の歪み成分)などがある。

【0139】

2倍波短絡回路43a、及び43b、43c、及び43dは、2次相互変調歪み成分すなわち変調波の周波数の信号を通過させ、高次高調波の周波数の信号は短絡して全反射させる。また被変調波の周波数では高インピーダンスであるので被変調波の周波数の信号は通過させない。

【0140】

従って、このような歪み成分をも含む増幅信号がそれぞれFET42a、42cのドレインから出力されると、増幅信号のうち、2次相互変調歪み成分は、2倍波短絡回路43a及び43dをそれぞれ通過する。

【0141】

一方、FET42bのドレインからこのような歪成分を含む増幅信号が出力されると、増幅信号のうち、2次相互変調歪み成分と高次高調波の周波数の歪み成分とは、2倍波短絡回路43b及び43cをそれぞれ通過する。そして、高次高調波の周波数の信号は、2倍波バイパス用のキャパシタ44a及び44bでそれぞれ接地にバイパスされる。また、この増幅信号のうち、被変調波の周波数の信号は、2倍波短絡回路43b、43cを通過せず、終端抵抗48で終端される。

【0142】

また、変調周波数の信号は、2倍波短絡回路43b、43cをそれぞれ通過して、それぞれ反転増幅器45a及び45bに入力される。反転増幅器45a及び45bは、それぞれ、入力された変調周波数の信号の位相を180度反転して変調周波数の信号を増幅する。

【0143】

反転増幅器45aで増幅された変調波の周波数の信号は、2倍波短絡回路43aを通過してFET42aのドレイン端に達する。なお、変調波の周波数の信号が2倍波短絡回路43aを通過する際、2倍波短絡回路43aの損失のために多少減衰する。

【0144】

また、反転増幅器45aの利得は、反転増幅器45aから反転増幅されて出力された信号が2倍波短絡回路43aの損失により減衰して通過し、FET42aのドレイン端に達した時の振幅と、FET42aのドレイン端から出力される増幅信号に含まれる変調波の周波数の信号の振幅とが等振幅になるように予め調整されている。

【0145】

従って、FET42aのドレイン端に達した変調波の周波数の信号と、FET42aのドレイン端から出力される増幅信号に含まれる変調波の周波数の信号とは等振幅かつ逆位相になる。従ってこれら2つの変調波の周波数の信号は互いに打ち消し合うことになるので、2次相互変調歪み成分である変調波の周波数の信号がFET42bのドレインで被変調波の信号とミキシングされることにより相互変調歪みを悪化させるという事態を避けることが出来る。

【0146】

同様に、反転増幅器45bで増幅された変調波の周波数の信号は、2倍波短絡回路43dを通過してFET42cのドレイン端に達する。なお、変調波の周波数の信号が2倍波短絡回路43dを通過する際、2倍波短絡回路43dの損失のために多少減衰する。

【0147】

また、反転増幅器45bの利得は、反転増幅器45bから反転増幅されて出力された信号が2倍波短絡回路43bの損失により減衰して通過し、FET42cのドレイン端に達した時の振幅と、FET42cのドレイン端から出力される増幅信号に含まれる変調波の周波数の信号の振幅とが等振幅になるように予め調整されている。

【0148】

従って、FET42cのドレイン端に達した変調波の周波数の信号と、FET42cのドレイン端から出力される増幅信号に含まれる変調波の周波数の信号とは等振幅かつ逆位相になる。従ってこれら2つの変調波の周波数の信号は互いに打ち消し合うことになるので、2次相互変調歪み成分である変調波の周波数の信号がFET42cのドレインで被変調波の信号とミキシングされることにより3次相互変調歪みを悪化させるという事態を避けることが出来る。

【0149】

FET42a及びFET42cのドレインから出力された増幅信号は、第1の実施の形態と同様に合成回路/整合回路28でインピーダンスが整合されるとともに合成されて出力端子29に出力される。

【0150】

このように本実施の形態の電力増幅装置62は、変調波の周波数の信号どうしが、FET42a及びFET42cのそれぞれのドレイン端で互いに他を打ち消し合うので、ドレインで、変調波の周波数の信号と被変調波の周波数の信号とがミキシングすることによる相互変調歪みの悪化を防止することが出来る。

【0151】

さらに、本実施の形態の電力増幅装置62は、2倍波短絡回路43a、43b、43c、43d等の損失により変調波の周波数の信号が減衰する場合であっても、変調波の周波数の信号を反転増幅器45a、45bで増幅するので、FET42a及びFET42cのそれぞれのドレイン端で2つの変調波の周波数の信号を等振幅逆位相とすることが出来る。従って、FET42aなどの線形性を最大限に利用した広帯域で低歪みな特性を得ることが出来る。

【0152】

さらに、FET42bのFETサイズをFET42a及びFET42cより小さくし、それに応じて反転増幅器45a及び45bの利得を増加させることにより、FET42bに入力される被変調波の周波数の信号を小さくすることが出来るので、電力増幅装置62の効率を向上させることが出来る。さらに、このような場合には、FET42bのドレインから出力された増幅信号はFET42aやFET42cのドレインから出力される増幅信号に比べて微弱である。従って、FET42bの増幅信号を終端抵抗48により終端する代わりに、FET42aやFET42cから出力された増幅信号とともに合成して出力端子29から出力しても歪み成分は平均的にはほとんど増加しない。従ってFET42bの増幅信号を終端抵抗48の代わりに、FET42aやFET42cから出力された増幅信号とともに合成して出力端子29から出力してもよい。

【0153】

なお、図8に、本実施の形態の電力増幅装置62を誘電体多層基板内に形成した例を示す。

【0154】

誘電体基板91上には整合回路/分配回路41、FET42a、42b、及び42c、反転増幅器45a及び45b、チップコンデンサであるキャパシタ27a及び27b、及び合成回路/整合回路28が形成されている。誘電体基板91の下層には、シールド電極が形成された誘電体基板92が形成されている。

【0155】

誘電体基板92の下層には誘電体基板93が形成されている。誘電体基板93には2倍波短絡回路43a、43b、43c、及び43dが形成されている。また、誘電体基板93と誘電体基板94のシールド電極である接地層との間に、キャパシタ44a、44b、46a、46bが形成されている。そして、誘電体基板92の下層にはシールド電極が形成された誘電体基板94が形成されている。

【0156】

なお、本実施の形態では、FET42aとFET42cとはFETサイズが同一であるとしたが、これに限らない。FET42aとFET42cとがFETサイズが異なっていても構わない。なお、この場合には、FET42bのサイズは、FET42aとFET42cとのうちFETサイズが小さい方よりもFETサイズが小さいことが好ましい。

【0157】

さらに、本実施の形態の終端抵抗48の代わりにキャパシタ、インダクタ及び抵抗を組み合わせた構成を持つ終端負荷や、キャパシタと抵抗とを組み合わせた構成を持つ終端負荷や、インダクタと抵抗とを組み合わせた構成を持つ終端負荷や、キャパシタとインダクタとを組み合わせた構成を持つ終端負荷を用いることも出来る。

【0158】

なお、第2の実施の形態の電力増幅装置62のうち、FET42c、2倍波短絡回路43c及び43d、反転増幅器45b、キャパシタ44b及び46b、キャパシタ27bを設けない構成の電力増幅器であっても本実施の形態と同等の効果を得ることが出来る。

【0159】

すなわち、図4において、整合回路/分配回路41の代わりに入力を2分配する整合回路/分配回路に置き換え、また、合成回路/整合回路28の代わりに、キャパシタ27aを通過した増幅信号を出力端子29に出力するととともに、そのインピーダンスを整合させる整合回路に置き換えればよい。このようにすることによっても本実施の形態と同等の効果を得ることが出来る。

【0160】

さらに、第2の実施の形態の電力増幅装置62では、増幅信号が出力端子に出力されるFET42a及びFET42cは2個であり、変調波の周波数の信号を打ち消すためのFET42bは1個使用されているがこれに限らない。変調波の周波数の信号を打ち消すためのFETを一つ設け、増幅信号が出力端子に出力されるFETを(N−1)個設けた電力増幅器であってもよい。この場合(N−1)個のFETのそれぞれFETのゲートには、被変調波の周波数の信号をN分配する整合回路/分配回路のそれぞれの出力が接続されている。また変調波の周波数の信号を打ち消すためのFETのゲートには、この整合回路/分配回路の残りの出力が接続されている。そして、(N−1)個のFETのそれぞれのFETと変調波の周波数の信号を打ち消すためのFETとの間には、それぞれ図4の2倍波短絡回路43b、キャパシタ46a、反転増幅器45a、キャパシタ44a、2倍波短絡回路43a、及びキャパシタ27aの回路部分と同等の回路構成を有する回路が接続される。また、(N−1)個のFETのそれぞれのFETから出力された信号は、それぞれのFETのキャパシタ27aと同等のキャパシタを経由して、(N−1)個の入力を合成してインピーダンスを整合させる合成回路/整合回路から出力端子29に出力されるものとする。

【0161】

さらに、本実施の形態では、FET42bのドレインには、FET42a及び42cのそれぞれに至る回路の経路上にそれぞれ2倍波短絡回路43b及び2倍波短絡回路43cを設けたが、これに限らない。FET42bのドレインに2倍波短絡回路の一方を接続し、その2倍波短絡回路の他方を反転増幅器45aの入力、及び反転増幅器45bの入力に接続する構成も可能である。また、このような電力増幅装置において、上述したように、増幅信号が出力端子に出力されるFETを(N−1)個設けた構成にすることも可能である。このようにすれば、2倍波短絡回路の個数を少なくすることが出来る。

【0162】

このように、FET42bのドレインからFET42a及びFET42cに至る回路のそれぞれの経路上の各素子のうち、2倍波短絡回路43b及び2倍波短絡回路43cを共通化することが出来るが、さらに、FET42bのドレインからFET42a及びFET42cに至る経路上のそれぞれの素子の全部または一部をさらに共通化することも出来る。

【0163】

例えばFET42bのドレインからFET42aのドレインに至る経路上の素子のうち、2倍波短絡回路43b及びキャパシタ46aを、FET42bのドレインからFET42cのドレインに至る回路部分のうちの2倍波短絡回路43c及びキャパシタ46bと共通化することが出来る。すなわち、FET42bのドレインに2倍波短絡回路の一方を接続し、その2倍波短絡回路の他方を図示していない分配回路で2分配し、その2分配した一方の出力を反転増幅器45aの入力に接続し、他方の出力を反転増幅器45bの入力に接続する。また、2倍波短絡回路の他方にはキャパシタ46a及び46bを共通化したキャパシタの一方を接続し、その他方を接地する。

【0164】

また、例えばFET42bのドレインからFET42aのドレインに至る経路上の回路部分のうち、2倍波短絡回路43b及びキャパシタ46a及び反転増幅器45aを、FET42bのドレインからFET42cのドレインに至る経路上の回路部分のうちの2倍波短絡回路43c及びキャパシタ46b及び反転増幅器45bとを共通化することが出来る。すなわち、FET42bのドレインに2倍波短絡回路の一方を接続し、その2倍波短絡回路の他方にキャパシタの一方及び反転増幅器の入力を接続し、そのキャパシタの他方は接地し、反転増幅器の出力に図示していない分配回路の入力を接続し、その分配回路で2分配された出力を2倍波短絡回路43aの他方及び2倍波短絡回路43dの他方に接続し、2倍波短絡回路43a及び43dの他方に、キャパシタ44a及び44bを接続する。

【0165】

また、例えばFET42bのドレインからFET42aのドレインに至る回路部分のうち、2倍波短絡回路43b及びキャパシタ46a及び反転増幅器45a及びキャパシタ44aを、FET42bのドレインからFET42cのドレインに至る回路部分のうちの2倍波短絡回路43c及びキャパシタ46b及び反転増幅器45b及びキャパシタ44bとを共通化することが出来る。すなわち、FET42bのドレインに2倍波短絡回路の一方を接続し、その2倍波短絡回路の他方にキャパシタの一方及び反転増幅器の入力を接続し、そのキャパシタの他方は接地し、反転増幅器の出力にキャパシタ及び図示していない分配回路の入力を接続し、そのキャパシタの他方は接地し、その分配回路で2分配された出力を2倍波短絡回路43aの他方及び2倍波短絡回路43dの他方に接続する。

【0166】

また、例えば、FET42bのドレインからFET42aのドレインに至る回路部分のうち、2倍波短絡回路43b及びキャパシタ46a及び反転増幅器45a及びキャパシタ44a、2倍波短絡回路43aを、FET42bのドレインからFET42cのドレインに至る回路部分のうちの2倍波短絡回路43c及びキャパシタ46b及び反転増幅器45b及びキャパシタ44b、2倍波短絡回路43dとを共通化することが出来る。すなわち、FET42bのドレインに2倍波短絡回路の一方を接続し、その2倍波短絡回路の他方にキャパシタの一方及び反転増幅器の入力を接続し、そのキャパシタの他方は接地し、反転増幅器の出力にキャパシタ及びもう一つの2倍波短絡回路の他方を接続し、その2倍波短絡回路の他方に図示していない分配回路の入力を接続し、その分配回路で2分配された出力をFET42aのドレイン及びFET42cのドレインに接続する。

【0167】

このような電力増幅装置において、上述したように、増幅信号が出力端子に出力されるFETを(N−1)個設けた構成にすることも出来ることはいうまでもない。

【0168】

さらに、第1の実施の形態や第2の実施の形態で説明した電力増幅装置を複数組み合わせた構成を有する電力増幅装置であってもよい。

【0169】

例えば、図4の電力増幅装置62を2つ組み合わせるとは、2つの電力増幅装置62の整合回路/分配回路41を共通化することを意味する。すなわち、共通化するとは、2つの整合回路/分配回路41を一つの整合回路/分配回路として実現することを意味する。従ってこのように共通化した整合回路/分配回路は、一つの入力端子21から被変調波の周波数の信号を入力し、6分配する。このうち3つの出力は一方の電力増幅装置62のFETに入力され、残りの3つの出力は他方の電力増幅装置62のFETに入力される。

【0170】

そして、合成回路/整合回路28も同様に共通化する。すなわち、共通化するとは、2つの合成回路/整合回路28を一つの合成回路/整合回路として実現することを意味する。従ってこのように共通化した合成回路/整合回路28は、4つの増幅信号を合成して一つの出力端子29に出力するとともにそのインピーダンスを整合させるものとなる。そして、一方の電力増幅装置62のキャパシタ27a及び27bを通過した増幅信号が共通化された合成回路/整合回路の2つの入力に入力され、他方の電力増幅装置62のキャパシタ27a及び27bを通過した増幅信号が共通化された合成回路/整合回路の残りの2つの入力に入力されるものとする。そして、これら4つの増幅信号が共通化された合成回路/整合回路で合成されるとともに、インピーダンスが整合されて一つの出力端子29から出力されるものとする。

【0171】

このようにすれば、第1の実施の形態の電力増幅装置61、及び第2の実施の形態の電力増幅装置62、及び第2の実施の形態で説明した電力増幅装置62を変形した電力増幅装置を複数個及び/または複数種類組み合わせた電力増幅装置も得ることが出来る。このように本実施の形態の電力増幅装置を複数個及び/または複数種類組み合わせた電力増幅装置の整合回路/分配回路は、組み合わせる前の各整合回路/分配回路を上記と同様に共通化したものを用いる。また、同様に本実施の形態の電力増幅装置を複数個及び/または複数種類組み合わせた電力増幅装置の合成回路/整合回路は、組み合わせる前の各合成回路/整合回路を上記と同様に共通化したものを用いる。このように本実施の形態の電力増幅装置を組み合わせた電力増幅装置も本実施の形態と同等の効果を得ることが出来る。

【0172】

なお、本実施の形態のFETは本発明の増幅素子の例であり、本実施の形態の2倍波短絡回路は本発明のフィルタの例であり、本実施の形態のFET23aは本発明の第1の増幅素子の例であり、本実施の形態のFET23bは本発明の第2の増幅素子の例であり、本実施の形態の2倍波短絡/バイアスチョーク回路24aは本発明の第1のフィルタの例であり、本実施の形態の2倍波短絡/バイアスチョーク回路24bは本発明の第2のフィルタの例であり、本実施の形態のFET42aは本発明の第1の増幅素子の例であり、本実施の形態のFET42cは本発明の第1の増幅素子の例であり、本実施の形態のFET42bは本発明の第2の増幅素子の例である。

【0173】

なお、本発明の増幅素子は、本実施の形態におけるFETに限らず、トランジスタなど他の増幅素子であっても構わない。

【0174】

さらに、本発明の無線通信装置とは、例えば、携帯電話、PHS、自動車電話、列車電話、船舶電話、航空機電話、コードレス電話、ポケットベルなどの移動体無線装置及びその基地局装置を含む。

【0175】

【発明の効果】

以上説明したところから明らかなように、本発明は、従来とは異なった構成で、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスを低くすることが出来る電力増幅装置、及び無線通信装置を提供することが出来る。

【0176】

また、本発明は、増幅素子の出力側の回路部分の変調波の周波数におけるインピーダンスをより低くすることが出来、増幅素子の線形性をより有効に利用することが出来る電力増幅装置、及び無線通信装置を提供することが出来る。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態における電力増幅装置の構成を示す図

【図2】本発明の第1の実施の形態における電力増幅装置のうち、差周波反転回路、2倍波短絡/バイアスチョーク回路の部分の詳細な構成を示す図

【図3】本発明の第1の実施の形態における電力増幅装置のうち、差周波反転回路、2倍波短絡/バイアスチョーク回路の部分の詳細な構成を示す図

【図4】本発明の第2の実施の形態における電力増幅装置の構成を示す図

【図5】本発明の第1の実施の形態における電力増幅装置を誘電体多層基板内に形成した例を示す図

【図6】本発明の第1の実施の形態における電力増幅装置を半導体基板上に誘電体層を配置して形成した例を示す図

【図7】本発明の第1の実施の形態における電力増幅装置をセラミック高周波パッケージ内に実装した例を示す図

【図8】本発明の第1の実施の形態における電力増幅装置を誘電体多層基板内に形成した例を示す図

【図9】本発明の第1、及び第2の実施の形態における無線回路の構成を示す図

【図10】従来の歪み特性が良好な電力増幅装置の構成を示す図

【符号の説明】

1 発振器

2 発振器

3 変調器

4 ミキサ

5 電力増幅器

6 アンテナ共用器

7 アンテナ

21 入力端子

22 整合回路/分配回路

23a FET

23b FET

24a 2倍波短絡/バイアスチョーク回路

24b 2倍波短絡/バイアスチョーク回路

25a キャパシタ

25b キャパシタ

26 差周波反転回路

27a キャパシタ

27b キャパシタ

28 合成回路/整合回路

29 出力端子

41 整合回路/分配回路

42a FET

42b FET

42c FET

45a 反転増幅器

45b 反転増幅器

Claims (20)

- 被変調波の周波数の信号を2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力と前記第2の増幅素子の出力とを合成して出力する合成回路と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の周波数の信号の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の周波数の信号の変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方と前記第2のフィルタの他方との間に接続され、前記変調波の周波数帯の信号を、その位相を反転させて通過させる反転回路とを備え、

前記反転回路は、第1のインダクタと、

第2のインダクタと、

第4のインダクタと、

第1のキャパシタと、

第2のキャパシタと、

第3のキャパシタと、

第4のキャパシタとを有し、

前記第1のインダクタは、その一方が前記第1のフィルタの他方に接続され、その他方が前記第2のインダクタの一方に接続され、

前記第2のインダクタの他方は、前記第2のフィルタの他方に接続され、

前記第1のキャパシタは、その一方が前記第1のインダクタの一方に接続され、その他方が接地されており、

前記第2のキャパシタは、その一方が前記第1のインダクタの他方に接続され、その他方が接地されており、

前記第3のキャパシタは、その一方が前記第2のインダクタの他方に接続され、その他方が接地されており、

前記第4のインダクタは、その一方がバイアス電源に接続され、その他方が前記第1のインダクタの他方に接続されており、

前記第4のキャパシタは、その一方が前記第4のインダクタの一方に接続され、その他方が接地されている電力増幅装置。 - 被変調波の周波数の信号を少なくとも2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方に出力が接続され、前記第2のフィルタの他方に入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器とを備え、

前記第1の増幅素子の出力は外部に出力され、かつ前記第2の増幅素子の出力は終端されている電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれの出力が接続された(N−1)分配回路の入力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記第1のフィルタの他方にその出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記(N−1)個の第1のフィルタの他方は、前記反転増幅器の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続されており、前記第2の増幅素子の出力は終端されている電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、入力が前記第2のフィルタの他方に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

前記(N−1)個の反転増幅器の入力にそれぞれ一方が接続され、他方が前記第2の増幅素子の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる(N−1)個の第2のフィルタと、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子の出力は終端されている電力増幅装置。 - 被変調波の周波数の信号を少なくとも2分配する分配回路と、

前記分配回路の一方の出力に入力が接続された第1の増幅素子と、

前記分配回路の他方の出力に入力が接続された第2の増幅素子と、

前記第1の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第1のフィルタの他方に出力が接続され、前記第2のフィルタの他方に入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器とを備え、

少なくとも前記第1の増幅素子の出力は外部に出力されており、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれの出力が接続された(N−1)分配回路の入力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記第1のフィルタの他方にその出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記第2のフィルタの他方にその入力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記(N−1)個の第1のフィルタの他方は、前記反転増幅器の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続されており、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記第2の増幅素子の出力に一方が接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる第2のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、入力が前記第2のフィルタの他方に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置。 - 被変調波の周波数の信号をN(Nは3以上の整数)分配する分配回路と、

前記分配回路のN個の出力のうち(N−1)個の出力にそれぞれ入力が接続された(N−1)個の第1の増幅素子と、

前記分配回路の前記(N−1)個の出力以外の前記分配回路の出力に入力が接続された第2の増幅素子と、

前記(N−1)個の第1の増幅素子の出力にそれぞれ一方が接続され、前記被変調波の周波数の信号を通過させず、前記被変調波の変調波の周波数帯の信号を通過させる(N−1)個の第1のフィルタと、

前記(N−1)個の第1のフィルタの他方にそれぞれ出力が接続され、前記変調波の周波数帯の信号を、その位相を反転させて増幅する(N−1)個の反転増幅器と、

前記(N−1)個の反転増幅器の入力にそれぞれ一方が接続され、他方が前記第2の増幅素子の出力に接続された(N−1)分配回路の(N−1)個の出力のそれぞれに接続され、前記被変調波の周波数の信号を通過させず、前記変調波の周波数帯の信号を通過させる(N−1)個の第2のフィルタと、

少なくとも前記(N−1)個の第1の増幅素子の出力を合成して出力する合成回路とを備え、

前記第2の増幅素子は、前記第1の増幅素子より増幅素子サイズが小さい電力増幅装置。 - 前記終端されているとは、前記第2の増幅素子の出力に終端抵抗を接続した、または前記第2の増幅素子の出力にキャパシタ及び/またはインダクタから構成される終端負荷を接続したことである請求項2〜6のいずれかに記載の電力増幅装置。

- 請求項1、3〜6、8〜11のいずれかに記載の電力増幅装置を複数備え、

それらの電力増幅装置の各分配回路は、共通化されており、同じ前記被変調波の周波数の信号を入力し、

それらの電力増幅装置の各合成回路は、共通化されており、一つに合成された出力信号を出力する電力増幅装置。 - 請求項2または7に記載の電力増幅装置複数と、

それらの電力増幅装置の外部に出力すべき出力を合成して出力する合成回路とを備え、

それらの電力増幅装置の各分配回路は共通化されており、同じ前記被変調波の周波数の信号を入力する電力増幅装置。 - 請求項1〜11のいずれかに記載の電力増幅装置が形成されている誘電体多層基板を備えた電力増幅装置。

- 前記誘電体多層基板は、その上部に配置された半導体基板と、前記半導体基板の下部に配置された誘電体多層基板とを有する請求項15記載の電力増幅装置。

- その内部に前記誘電体多層基板が配置されている内部整合基板を備えた請求項16記載の電力増幅装置。

- 前記被変調波の周波数の信号の周波数は、前記変調波の周波数帯の信号の周波数帯域の千倍以下である請求項1〜11のいずれかに記載の電力増幅装置。

- 前記第1のフィルタ及び前記第2のフィルタは、前記変調波の周波数の信号の高調波成分を通過させる請求項1〜11のいずれかに記載の電力増幅装置。

- 送信波を出力する送信回路を少なくとも備え、

前記送信回路には請求項1〜11のいずれかに記載の電力増幅装置が用いられている無線通信装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002328773A JP4119227B2 (ja) | 2001-11-16 | 2002-11-12 | 電力増幅装置、及び無線通信装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001-351816 | 2001-11-16 | ||

| JP2001351816 | 2001-11-16 | ||

| JP2002328773A JP4119227B2 (ja) | 2001-11-16 | 2002-11-12 | 電力増幅装置、及び無線通信装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003218646A JP2003218646A (ja) | 2003-07-31 |

| JP2003218646A5 JP2003218646A5 (ja) | 2005-10-27 |

| JP4119227B2 true JP4119227B2 (ja) | 2008-07-16 |

Family

ID=27667292

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002328773A Expired - Fee Related JP4119227B2 (ja) | 2001-11-16 | 2002-11-12 | 電力増幅装置、及び無線通信装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4119227B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4712546B2 (ja) * | 2005-12-05 | 2011-06-29 | 三菱電機株式会社 | マイクロ波増幅器 |

| JP2007295329A (ja) * | 2006-04-26 | 2007-11-08 | Nec Corp | 増幅器 |

| KR101298538B1 (ko) * | 2006-11-29 | 2013-08-22 | 삼성전자주식회사 | 공유 드레인 전류 패스를 갖는 평형 증폭기 |

| JP2012222394A (ja) * | 2011-04-04 | 2012-11-12 | Wave Technology Inc | 電力増幅器 |

| JP2014138312A (ja) * | 2013-01-17 | 2014-07-28 | Murata Mfg Co Ltd | 半導体モジュール |

| US9160289B2 (en) * | 2013-05-10 | 2015-10-13 | Raytheon Company | Broadband power amplifier having high efficiency |

| JP7371340B2 (ja) * | 2019-03-20 | 2023-10-31 | 富士通株式会社 | 電力増幅装置及び電磁波放射装置 |

-

2002

- 2002-11-12 JP JP2002328773A patent/JP4119227B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003218646A (ja) | 2003-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6847258B2 (en) | Power amplifier, power amplifying method and radio communication apparatus | |

| US6057714A (en) | Double balance differential active ring mixer with current shared active input balun | |

| KR101287318B1 (ko) | 부고조파 믹서를 갖는 직접 변환 수신기 | |

| US7706835B2 (en) | High-frequency circuit device | |

| EP1421676B1 (en) | Method and apparatus for conversion of radio frequency (rf) signals using aperiodic mixing signals | |

| US7653372B2 (en) | Communication device, mixer and method thereof | |

| Larson | RF and microwave hardware challenges for future radio spectrum access | |

| KR100868817B1 (ko) | 고 주파수 수신기, 통신 장치 및 저 잡음 증폭기 | |

| Rasekh et al. | Wide-band RF front end for SAW-less receivers employing active feedback and far out-of-band blocker rejection circuit | |

| JP4119227B2 (ja) | 電力増幅装置、及び無線通信装置 | |

| Nam et al. | A compact I/Q upconversion chain for a 5G wireless transmitter in 65-nm CMOS technology | |

| JP2009207031A (ja) | 増幅回路 | |

| JP3806078B2 (ja) | 電圧制御発振器及びこれを用いた無線通信装置 | |

| Yishay et al. | A single-path reconfigurable frequency multiplier for 28/39 GHz dual-band transceivers | |

| JPH1141042A (ja) | マイクロ波増幅器 | |

| JP3105820B2 (ja) | 無線装置の相互変調歪低減回路 | |

| WO2022160248A1 (zh) | 多频段功率放大电路和射频收发机 | |

| JP3560774B2 (ja) | 偶高調波ミクサ、直交ミクサ、イメージリジェクションミクサ、受信装置及び位相同期発振器 | |

| KR100345456B1 (ko) | 마이크로웨이브모노리식집적회로용주파수혼합기 | |

| WO2022202048A1 (ja) | 高周波回路 | |

| US7308243B2 (en) | Mixer arrangement and method for mixing signals | |

| JP4245342B2 (ja) | ミクサ、受信装置及び送信装置 | |

| KR100657009B1 (ko) | 초광대역 상향 주파수 변환 장치 | |

| Jamie et al. | A 2.8-4.3 GHz Simultaneous Dual-Carrier Transformer-Coupled Passive Mixer-First Receiver Front-End Supporting Blocker Suppression | |

| JPWO2004001989A1 (ja) | 送信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050830 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050830 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080205 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080307 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080401 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080424 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110502 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110502 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120502 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120502 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130502 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |