JP3920994B2 - プロセッサをコプロセッサにインタフェースするための方法および装置 - Google Patents

プロセッサをコプロセッサにインタフェースするための方法および装置 Download PDFInfo

- Publication number

- JP3920994B2 JP3920994B2 JP25936498A JP25936498A JP3920994B2 JP 3920994 B2 JP3920994 B2 JP 3920994B2 JP 25936498 A JP25936498 A JP 25936498A JP 25936498 A JP25936498 A JP 25936498A JP 3920994 B2 JP3920994 B2 JP 3920994B2

- Authority

- JP

- Japan

- Prior art keywords

- coprocessor

- processor

- instruction

- bus

- control signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 35

- 238000004891 communication Methods 0.000 claims description 13

- 238000012545 processing Methods 0.000 claims description 13

- 230000004044 response Effects 0.000 claims description 7

- 230000008569 process Effects 0.000 claims description 2

- 230000000977 initiatory effect Effects 0.000 claims 2

- 238000010586 diagram Methods 0.000 description 49

- 238000012546 transfer Methods 0.000 description 37

- 239000004020 conductor Substances 0.000 description 23

- 230000006870 function Effects 0.000 description 22

- 239000008186 active pharmaceutical agent Substances 0.000 description 9

- 230000007246 mechanism Effects 0.000 description 7

- 238000009434 installation Methods 0.000 description 5

- 238000013459 approach Methods 0.000 description 3

- 230000003139 buffering effect Effects 0.000 description 3

- 238000012163 sequencing technique Methods 0.000 description 3

- 101100396933 Pseudomonas aeruginosa (strain ATCC 15692 / DSM 22644 / CIP 104116 / JCM 14847 / LMG 12228 / 1C / PRS 101 / PAO1) imm2 gene Proteins 0.000 description 2

- 102100023116 Sodium/nucleoside cotransporter 1 Human genes 0.000 description 2

- 101710123675 Sodium/nucleoside cotransporter 1 Proteins 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000002457 bidirectional effect Effects 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 206010000210 abortion Diseases 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000003999 initiator Substances 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/3012—Organisation of register space, e.g. banked or distributed register file

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/30105—Register structure

- G06F9/30116—Shadow registers, e.g. coupled registers, not forming part of the register space

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

- G06F9/3879—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor for non-native instruction execution, e.g. executing a command; for Java instruction set

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

- G06F9/3879—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor for non-native instruction execution, e.g. executing a command; for Java instruction set

- G06F9/3881—Arrangements for communication of instructions and data

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Advance Control (AREA)

- Executing Machine-Instructions (AREA)

- Microcomputers (AREA)

Description

【発明の属する技術分野】

本発明は一般的にはプロセッサおよび少なくとも1つのコプロセッサ(coprocessor)を有するデータ処理システムに関し、かつより特定的には、該コプロセッサに対しプロセッサをインタフェースするための方法および装置に関する。

【0002】

【従来の技術】

専用のかつ専門化されたハードウエア機能要素によって基礎(ベースライン:baseline)アーキテクチャプロセッサの機能性を拡張する能力は規模変更可能な(scaleable)および拡張性のあるアーキテクチャの重要な観点である。

【0003】

基礎アーキテクチャプロセッサの機能を拡張するための1つの好ましい方法はコプロセッサを使用することによるものである。これらはプロセッサの指令で動作する専用の通常は単一目的のプロセッサである。コプロセッサの伝統的な用途の1つは浮動少数点能力をそのようなものを直接サポートしないアーキテクチャに対して選択的に提供するための数学的または数値演算コプロセッサとしてのものであった。そのような数学的コプロセッサのいくつかの例はインテル(Intel)社の8087型および80287型のものである。コプロセッサのいくつかの他の可能性ある用途または形式は、乗算−累算器(multiply−accumulators)、変調器/復調器(モデム)、デジタル信号プロセッサ(DSP)、ビタービ計算機(vitturbi calculators)、暗号プロセッサ、画像プロセッサ、およびベクトルプロセッサを含む。

【0004】

【発明が解決しようとする課題】

コプロセッサに対する2つの異なる手法がある。一方においては、デジタル・イクイップメント・コーポレイション(DEC)のPDP−11型ファミリのコンピュータのための浮動小数点ユニットはその主プロセッサに対して非常に密接に(tightly)結合された。発生した1つの問題はこの密接な結合が主プロセッサがコプロセッサの動作についてかなりの程度まで知っていることを必要としたことである。これは新しいコプロセッサを集積または統合システムに付加することが主たる工学技術上の問題になるほど回路設計を複雑にする。

【0005】

別の構成はコプロセッサを主プロセッサに対してルーズに(loosely)結合することであった。これは主プロセッサからコプロセッサの動作を引き離し(abstracting)かつ分離する利点を有し、かつ従って新しいコプロセッサを現存のプロセッサと共に集積または統合するのに必要な努力を実質的に軽減した。しかしながら、これは常にかなりの犠牲をはらって行われた。性能の喪失がこの手法の1つの問題である。このルーズな結合から生じる形式の性能ヒットをとることに伴う1つの問題はそのようなコプロセッサに頼ることに対する損益分岐点が相応じて増大することである。従って、コプロセッサに対するそうでなければ魅力的な数多くの応用はコスト効率がよくない。さらに、そのような手法はしばしば、すべての対応する付加的な回路およびチップ面積と共に、バスを使用することを必要とする。

【0006】

従って、たとえ非常に簡単な機能に頼ることでも有利になるようにインタフェースを使用することが十分高速となるよう十分密接に結合され、一方プロセッサのアーキテクチャがいずれか与えられたコプロセッサのできるだけ多くの細部から分離できるようにインタフェースを引き離すようなコプロセッサインタフェースをもつことが重要である。この後者の一部はハードウエアに代えてソフトウエアで新しいコプロセッサのアプリケーションをあつらえることができるようにするためインタフェースのプログラマが親しみ易くする(friendly)ことを含む。

【0007】

【課題を解決するための手段】

本発明の一態様では、通信バス(30)を介して結合されたコプロセッサ(14,16)とカウントフィールドおよびコードフィールドを備えた少なくとも1つの命令(H_CALL)の実行において協働するよう構成されたプロセッサ(12)における、前記命令を実行をする方法が提供され、該方法は、前記命令を受ける段階、前記通信バスにより第1のサイクルを介して、前記コプロセッサに前記カウントおよびコードフィールドを提供する段階、もし前記カウントフィールドがゼロより大きなある値、n、を有していれば、前記コプロセッサに、前記通信バスによって第2のサイクルを介して、第1のオペランドを提供する段階、そして前記命令を完了する段階、を具備することを特徴とする。

【0008】

本発明の別の態様では、通信バス(30)を介して結合されたコプロセッサ(14,16)と実効アドレス計算フィールドを備えた少なくとも1つの命令(H_LD)の実行において協働するよう構成されたプロセッサ(12)における、前記命令を実行する方法が提供され、該方法は、前記命令を受ける段階、前記通信バスによって第1のサイクルを介して、前記コプロセッサに前記実効アドレス計算フィールドを提供する段階、前記実効アドレス計算フィールドに従って実効アドレスを計算する段階、前記計算された実効アドレスに格納されたオペランドをフェッチする段階、前記通信バスによって第2のサイクルを介して、前記コプロセッサに前記フェッチされたオペランドを提供する段階、そして前記命令を完了する段階、を具備することを特徴とする。

【0009】

本発明のさらに別の態様では、通信バス(30)を介して結合されたコプロセッサ(14,16)と実効アドレス計算フィールドを備えた少なくとも1つの命令(H_ST)の実行において協働するよう構成されたプロセッサ(12)における、前記命令を実行する方法が提供され、該方法は、前記命令を受ける段階、前記通信バスによって第1のサイクルを介して、前記コプロセッサに前記実効アドレス計算フィールドを提供する段階、前記実効アドレス計算フィールドに従って実効アドレスを計算する段階、前記通信バスによって第2のサイクルを介して、前記コプロセッサからオペランドを受ける段階、前記計算された実効アドレスに前記受けたオペランドを格納する段階、そして前記命令を完了する段階、を具備することを特徴とする。

【0010】

【発明の実施の形態】

本発明の特徴および利点は添付の図面と共に以下の詳細な説明を参照することによりさらに明瞭に理解され、図面においては同じまたは同様の参照数字は同じかつ対応する部分を示している。

【0011】

以下の説明においては、数多くの特定の細部は特定のワードまたはバイト長などで説明され本発明の完全な理解を与えている。しかしながら、当業者には本発明はそのような特定の細部なしで実施できることが明らかであろう。他の場合には、本発明を不必要な細部によって不明確にすることのないよう回路がブロック図形式で示されている。たいていの場合、タイミングの考慮事項その他に関する詳細は本発明の完全な理解を得るのに必要でない限り省略されておりかつ関連する技術に習熟した当業者の技術の範囲内にある。

【0012】

用語「バス(bus)」は、データ、アドレス、制御またはステータスのような、1つまたはそれ以上の種々の形式の情報を転送するために使用できる複数の信号または導体に言及している。用語「肯定する(assert)」および「否定する(negate)」は信号、ステータスビットまたは同様の装置をそれぞれその論理的に真のまたは論理的に偽の状態にすることに言及する場合に使用される。もし論理的に真の状態が論理レベル“1”であれば、論理的に偽の状態は論理レベル“0”である。また、もし論理的に真の状態が論理レベル“0”であれば、論理的に偽の状態は論理レベル“1”である。

【0013】

図1は、データ処理システム10の一実施形態を示すブロック図であり、該データ処理システム10はプロセッサ12、コプロセッサ14、コプロセッサ16、メモリ18、他のモジュール20および外部バスインタフェース22を含みこれらはすべてバス28によって双方向的に結合されている。本発明の別の実施形態は1個だけのコプロセッサ14、2つのコプロセッサ14および16、またはさらに多くのコプロセッサ(図示せず)をもつものとすることができる。外部バスインタフェース22は集積回路端子35によって外部バス26に双方向的に結合されている。メモリ24は双方向的に外部バス26に結合されている。プロセッサ12は任意選択的に集積回路端子31によってデータ処理システム10の外部に結合することができる。コプロセッサ14は任意選択的に集積回路端子32によってデータ処理システム10の外部に接続することができる。メモリ18は任意選択的に集積回路端子33を介してデータ処理システム10の外部に接続することができる。他のモジュール20も任意選択的に集積回路端子34を介してデータ処理システム10の外部に結合することができる。プロセッサ12はコプロセッサインタフェース30によってコプロセッサ14およびコプロセッサ16の双方に双方向的に接続されている。

【0014】

図2は、図1のプロセッサ12の一部を示すブロック図である。一実施形態では、プロセッサ12は制御回路40、命令デコード回路42、命令パイプ44、レジスタ46、演算論理ユニット(ALU)48、ラッチングマルチプレクサ(latching multiplexer:MUX)50、ラッチングマルチプレクサ(MUX)52、およびマルチプレクサ(MUX)54を含む。本発明の一実施形態では、コプロセッサインタフェース30は信号60〜71を含む。クロック信号60は制御回路40によって発生される。コプロセッサオペレーション信号61は制御回路40によって発生されかつコプロセッサ14および16に与えられる。

【0015】

スーパバイザモード信号62は制御回路40によって発生されかつコプロセッサ14および16に提供される。デコード信号63は制御回路40によって発生されかつコプロセッサ14および16に提供される。コプロセッサビジー信号(busy signal)64はコプロセッサ14またはコプロセッサ16から制御回路40によって受信される。実行信号(Execute signal)65は制御回路40によって発生されかつコプロセッサ14および16に提供される。例外信号(Exception signal)66はコプロセッサ14またはコプロセッサ16から制御回路40によって受信される。レジスタ書込み(REGWR*)信号67は制御回路40によって発生されかつコプロセッサ14および16に提供される。レジスタ信号(REG{4:0})68は制御回路40によって発生されかつコプロセッサ14および16に提供される。エラー信号(H_ERR*)69は制御回路40によって発生されかつコプロセッサ14および16に提供される。データストローブ信号(H_DS*)70は制御回路40によって発生されかつコプロセッサ14および16に提供される。データアクノレッジ(肯定応答)信号(H_DA*)71は制御回路40によってコプロセッサ14およびコプロセッサ16から受信される。コプロセッサインタフェース70の一部とも考えられる、ハードウエアデータポート信号(HDP{31:0})72はコプロセッサ14および16とプロセッサ12内の内部回路との間で双方向的なものである。

【0016】

本発明の一実施形態では、複数の信号がバス28に対しまたはバス28から提供されてメモリ18および/またはメモリ24に対しデータをロードしまたは格納(ストア)する。一実施形態では、これらの信号は制御回路40によって発生されかつバス28に提供される転送要求信号(TREQ*)73を含む。転送エラーアクノレッジ信号(TEA*)74はバス28によって制御回路40に提供される。転送アクノレッジ信号(TA*)75はバス28によって制御回路40に提供される。命令はバス28から導体76によって命令パイプ(instruction pipe)44に提供される。データは導体76によってMUX54に提供される。

【0017】

ドライブデータ信号79はトライステートバッファ95をイネーブルして導体88および76によってラッチングMUX52からデータを提供できるようにする。アドレス選択信号78はラッチングMUX50が導体77によってバス28にアドレスを提供できるようにする。MUX54への他の入力はHDP信号(HDP{31:0})72によって提供される。MUX54への他の入力はALU結果導体86によって提供される。MUX54の出力、結果信号(resultsignal)83、はレジスタ46にかつトライステートバッファ96の入力に提供される。ドライブHDP信号82はトライステートバッファ96がHDP信号72によって結果信号83をドライブできるようにする。トライステートバッファ96の出力はまたラッチングMUX52の入力に結合されている。

【0018】

本発明の別の実施形態はレジスタ46に任意の数のレジスタを含めることができる。結果信号83はラッチングMUX50への入力として提供される。結果信号83はMUX54によってレジスタ46に提供される。結果選択信号(結果_選択:RESULT_SELECT)81はMUX54のどの入力が結果導体83にドライブされるべきかを選択する。ソース選択信号(ソース_選択:SOURCE_SELECT)80はラッチングMUX52に提供されてどの信号が導体88によってトライステートバッファ95にドライブされるかを選択する。

【0019】

制御回路40は導体91によって制御情報を提供しかつレジスタ46からステータス情報を受信する。制御回路40は導体92によって制御信号を提供しかつ演算論理ユニット48からステータス信号を受信する。制御回路40は導体93によって制御信号を提供しかつ命令パイプ44および命令デコード回路42からステータス信号を受信する。命令パイプ44は導体89によって命令デコード回路42に命令を提供するよう結合されている。命令デコード回路42は導体90によって制御回路40に対しデコードされた命令情報を提供する。レジスタ46は導体84によってソースオペランドを演算論理ユニット48に提供する。レジスタ46は導体80、ラッチングMUX52、トライステートバッファ95および導体76によってメモリ18またはメモリ24に格納されるべきデータを提供する。レジスタ46は導体84、ラッチングMUX50およびアドレス導体77によってメモリ18またはメモリ24にアドレス情報を提供する。レジスタ46は導体85によって演算論理ユニット48に第2のソースオペランドを提供する。

【0020】

図3は、コプロセッサ14の一部の一実施形態を示すブロック図である。一実施形態では、コプロセッサ14は制御回路100、計算回路102および任意選択的な記憶回路104を含む。制御回路100は信号60〜72を含むコプロセッサインタフェース30によってプロセッサ12に双方向的に結合されている。本発明の一実施形態では、制御回路100はデコード回路106を含み、該デコード回路106はプロセッサ12からオペレーション信号61およびデコード信号63を受信する。制御回路100は導体108によって制御情報を提供しかつ任意選択的な記憶回路104からステータス情報を受信する。制御回路100は導体109によって制御情報を提供しかつ計算回路102からステータス情報を受信する。計算回路102および任意選択的な記憶回路104は導体110によって双方向的に結合されている。信号110の1つまたはそれ以上はバス28または集積回路端子32に対しまたはこれらから提供できる。制御回路100は導体112によってバス28または集積回路端子32に対し情報を受信しあるいは情報を提供することができる。信号72は計算回路102および任意選択的な記憶回路104に双方向的に結合されている。さらに、信号72は双方向的にバス28または集積回路端子32に結合することができる。本発明の別の実施形態では、任意選択的な記憶回路104は実施しなくてもよい。任意選択的な記憶回路104が実施されない本発明の実施形態においては、それはレジスタ、任意の種類のメモリ、ラッチまたはプログラマブル論理アレイ、その他を含む任意の種類の記憶回路を使用して構成できる。本発明の別の実施形態では、計算回路102は任意の種類の論理または計算機能を行うことができる。

【0021】

本システムは特定の用途に関連する動作のために最適化された外部コプロセッサ14(またはハードウエアアクセラレータ)によるタスク加速のためのサポートを提供する。これらの外部コプロセッサ14,16は人口または母集団(population)のカウントを行うためのコプロセッサ14としての簡単なものでもよく、あるいはDSP加速コプロセッサ14または高速乗算/累算操作が可能なコプロセッサ14のようなより複雑な機能のものとすることもできる。

【0022】

データは特定の構成に対して適切な1つまたはそれ以上のいくつかのメカニズムによってプロセッサ12とコプロセッサ14との間で転送される。これらはコプロセッサ14への転送、およびコプロセッサ14からの転送へと分割できる。

【0023】

コプロセッサ14へのデータの転送のための1つのメカニズムはレジスタスヌーピングメカニズム(Register Snooping mechanism)であり、これは命令プリミティブ(instruction primitive)を含まないが、通常のプロセッサ12の動作の副産物である。これはコプロセッサ14が1つまたはそれ以上のプロセッサ12のレジスタへの更新を監視できるようにインタフェースにわたってプロセッサ12の汎用目的のレジスタ(“GPR”)46に対する更新を反映することを含む。これはもしコプロセッサ14が内部レジスタまたは機能に対してGPR46を「オーバレイ(overlays)」する場合に適切であろう。この場合、プロセッサ12からコプロセッサ14への明確な(explicit)受け渡しは必要とされないであろう。

【0024】

命令プリミィティブ(Instruction primitives)は外部コプロセッサ14,16およびプロセッサ12の間でオペランドおよび命令の明確な転送のためにベースプロセッサ12において提供される。命令およびデータ転送のレートに対する制御を可能にするためハンドシェイクメカニズムが提供される。

【0025】

コプロセッサ14の機能は構成に特有の(implementation specific)ユニットとなるよう設計され、従って与えられたユニットの正確な機能は、同じ命令マッピングが存在しても、異なる構成にわたり自由に変更できる。

【0026】

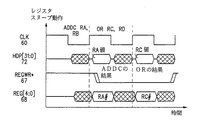

図4は、レジスタスヌーピング動作を示すタイミング図である。コプロセッサ14または外部モニタへのパラメータの受け渡しの性能オーバヘッドを避けるため、レジスタスヌーピングメカニズムが提供される。これはコプロセッサ14がプロセッサ12の汎用レジスタ46の1つまたはそれ以上のシャドウコピー(shadow copy)を実施できるようにする。この能力はプロセッサのGPR46の1つへ書き込まれる値を転送しかつどのレジスタ46が各々のGPRの更新に対して更新されるかを指示することによって実施される。ストローブ信号REGWR*67が各々のレジスタの更新に対して肯定される。この値は32ビットの双方向データパスHDP[31:0]72にわたって転送され、かつ5ビットのレジスタナンババスが更新される(REG[4:0])68の実際のプロセッサレジスタ46へのポインタを提供する。前記レジスタナンバは通常のファイル(normal file)におけるあるいは代わりのファイル(alternate file)におけるレジスタ46に言及または参照することができる。好ましい実施形態では、オルタネイトまたは代わりのファイルのレジスタはREG[4]==1によって示されかつノーマルまたは通常のファイルのレジスタはREG[4]==0によって示される。しかしながら、この発明はレジスタセットの実際の区分(partitioning)には依存しないことに注意を要する。

【0027】

専用の12ビット命令バス(H_OP[11:0])61は外部コプロセッサ14に対して発行されるコプロセッサインタフェース30のオペコード(opcode)を提供する。このバスはプロセッサのオペコードの下位(low order)12ビットを反映する。上位(high−order)4ビットはそれらは常に0b0100であるため反映されない。スーパバイザモード指示子(H−SUP)62もまたPSR(S)ビットの現在の状態を示すために提供され、プロセッサがスーパバイザまたはユーザモードのいずれで動作しているかを示す。これはあるコプロセッサ機能をスーパバイザモードに限定するのに有用なものとすることができる。プロセッサ12と外部コプロセッサ14,16の間の一組のハンドシェイク信号はコプロセッサインタフェース30の命令実行を調整する。

【0028】

プロセッサ12によって発生される制御信号はプロセッサ12の内部パイプライン構造の反映である。プロセッサパイプライン44は命令フェッチ、命令デコード42、実行、および結果の書き戻し(writeback)のステージから構成される。それは1つまたはそれ以上の命令レジスタ(IR)を含む。プロセッサ12はまた命令プリフェッチバッファを含みデコードステージ42の前に命令のバッファリングを可能にする。命令は命令デコードレジスタIRに入ることによりこのバッファから命令デコードステージ42へと進行する。

【0029】

命令デコーダ42はIRから入力を受け、かつIRに保持された値に基づき出力を発生する。これらのデコード42の出力は常に有効であるとは限らず、かつ例外条件または命令フローの変更により捨てられることがある。有効な場合でも、命令はそれらが命令パイプラインの実行ステージへ進行することができるまでIRに保持することができる。これは前の命令が実行を完了するまで(これは複数クロックを必要とするであろう)生じ得ないから、デコーダはIRが更新されるまでIRに含まれる値をデコードし続けることになる。

【0030】

図5は、命令ハンドシェイクのための基本的な命令インタフェース動作を示すタイミング図である。命令デコードストローブ(H_DEC*)信号63はプロセッサ12によってコプロセッサインタフェース30のオペコードのデコードを示すために与えられる。この信号は、たとえ命令が実行されずに捨てられる場合でも、コプロセッサインタフェース30のオペコードがIRに存在する場合に肯定されることになる。前記H_DEC*63の出力は命令が実際に発行されまたは捨てられるまで同じ命令に対して複数クロックの間肯定された状態に留まることができる。

【0031】

ビジー信号(H_BUSY*)64は外部コプロセッサ14がコプロセッサインタフェース30の命令を受け入れることができるか否かを判定するためプロセッサ12によって監視され、かつ命令の発行が生じる場合に対し部分的に制御を行う。もし前記H_BUSY*64信号が、H_DEC*63が肯定されている間に、否定されれば、命令実行はインタフェースによってストールされず、かつH_EXEC*65信号が命令実行が進行できるや否や肯定できるようになる。もしH_BUSY*64信号がプロセッサ12がコプロセッサインタフェース30のオペコードをデコードする場合に(H_DEC63*の肯定によって示される)肯定されれば、コプロセッサインタフェース30のオペコードの実行は強制的にストールされることになる。いったんH_BUSY*64信号が否定されると、プロセッサ12はH_EXEC*65を肯定することにより命令を発行することができる。もしコプロセッサ14が命令をバッファリングできれば、H_BUSY*64信号はバッファの充填を助けるために使用することができる。

【0032】

図6は、H_BUSY*64がコプロセッサインタフェース30の命令実行を制御するために使用される場合の命令インタフェース動作を示すタイミンク図である。いったん何らかの内部インストール条件が解消されると、かつH_BUSY*64信号が否定されると、プロセッサはH_EXEC*65を肯定してコプロセッサインタフェース30の命令がパイプラインの実行ステージに入ったことを示す。外部コプロセッサ14は命令の実際の実行を制御するためにH_EXEC*65信号を監視すべきであり、その理由はプロセッサがある状況において実行する前にその命令を放棄できるからである。もし前の命令の実行が結果として例外(exception)が取られることになれば、H_EXEC*65信号は肯定されず、かつH_DEC*63出力は否定されることになる。同様のプロセスはIRにおける命令がプログラムフローの変化の結果として廃棄されれば生じ得る。

【0033】

図7は、命令廃棄または命令放棄(instruction discard)を示すタイミング図である。もしある命令が廃棄されれば、H_DEC*63信号は他のコプロセッサインタフェース30のオペコードがH_OP[11:0]61のバスに与えられる前に否定されることになる。

【0034】

図8は、命令パイプラインストールの例を示すタイミング図である。H_DEC*63が肯定されかつH_BUSY*64が否定されてもプロセッサ12がH_EXEC*65の肯定を遅らせることができる状況がある。これは前の命令が完了するのを待機している間に生じる得る。

【0035】

図9は、ストールのないバック−バック(back−to−back)実行の例を示すタイミング図である。バック−バックコプロセッサインタフェース30の命令に対しては、H_OP[11:0]61バスが新しい命令がIRに入る際に更新されても、否定されることなく肯定された状態に留まることができる。一般に、H_EXEC*65の肯定は前のクロックに際してデコードされた命令の実行に対応する。

【0036】

図10は、内部パイプラインストールを有するバック−バック動作を示すタイミング図である。この場合、H_BUSY*64は否定されるが、プロセッサは内部ストール条件が消えるまで第2のコプロセッサインタフェース30の命令に対してH_EXEC*65を肯定しない。

【0037】

図11は、H_BUSY*64ストールを有するバック−バックコプロセッサインタフェース30の命令を示すタイミング図である。この例では、外部コプロセッサ14はビジーであり、かつ直ちに第2の命令を受け入れることはできない。H_BUSY*64は第2の命令がプロセッサ12によって発行されることを防止するため肯定する。いったんコプロセッサ14が自由になると、H_BUSY*64が否定され、かつ次のコプロセッサインタフェース30の命令が実行ステージへと進む。

【0038】

コプロセッサインタフェース30のオペコードのデコードに関連する例外は外部コプロセッサ14によってH_EXCP*66信号によって通知することができる。プロセッサ12へのこの入力はH_DEC*63が肯定されかつH_BUSY*64が否定されるクロックサイクルの間にサンプルされ、かつもしコプロセッサインタフェース30のオペコードが前に述べたように廃棄されなければハードウエアコプロセッサ14の例外に対して例外処理を生じる結果となる。この例外処理の詳細は以下に説明する。

【0039】

図12は、コプロセッサインタフェース30のオペコードのデコードおよび試みられた実行に応じてコプロセッサ14により肯定されるH_EXCP*66信号の例を示すタイミング図である。H_EXCP*66信号はH_DEC*63が肯定されかつH_BUSY*64が否定されるクロックの間にプロセッサ12によってサンプルされる。H_EXEC*65信号は例外がインタフェースによって通知されるか否かにかかわりなく肯定され、この肯定は例外が取られる場合を命令廃棄の場合と区別する。

【0040】

前記例外は前のクロックサイクルにデコードされた命令に対応し、かつ実際の実行は行われるべきでないことに注意を要する。コプロセッサ14は違背(offending)命令を受け入れかつそれに対するプロセッサパイプラインの実行ステージが認識される前に例外を通知しなければならない。前記H_EXCP*66信号はH_DEC*63が否定されあるいはH_BUSY*64が肯定されるすべてのクロックサイクルに対して無視される。

【0041】

図13は、コプロセッサインタフェース30のオペコードのデコードおよび試みられた実行に応じてコプロセッサ14によって肯定される前記H_EXCP*66信号の例を示すタイミング図である。これを図14のタイミング図と比較すると、この例では、コプロセッサインタフェース30の命令は廃棄され、従ってH_EXEC*65信号は肯定されず、かつH_DEC*63は否定される。

【0042】

図14は、H_BUSY*64が肯定されて例外を生じる結果となるコプロセッサインタフェース30のオペコードの実行を遅らせる例を示すタイミング図である。

【0043】

H_BUSY*64およびH_EXCP*66信号はすべてのコプロセッサ14,16によって共有され、従ってそれらは調整された方法でドライブされなければならない。これらの信号はH_DEC*63が肯定されるクロックサイクルに際してH_OP[11:10]61に対応してコプロセッサ14,16により(ハイまたはローに、いずれか適切なものに)ドライブされるべきである。出力をクロックのローの部分の間にのみドライブすることにより、これらの信号は競合なしに複数のコプロセッサ14,16によって共有することができる。ラッチをプロセッサ12の内部に保持することはこの入力に対してそれを何らのユニットもそれをドライブしていない間にクロックのハイのフェーズに対して有効な状態に保持するために提供される。

【0044】

コプロセッサインタフェース30の命令プリミティブのいくつかはまたプロセッサ12および外部コプロセッサ14の間でデータ項目またはデータアイテムの転送を行うことを含む。オペランドはコプロセッサインタフェース30にわたって実行されている特定のプリミティブの関数として転送することができる。プロセッサ12のGPRの1つまたはそれ以上を32ビットの双方向のデータパスにわたってコプロセッサ14からあるいはコプロセッサ14へ転送するための備えが設けられている。さらに、データシンク/ソース(sink/source)がコプロセッサインタフェース30として単一データ項目をメモリ18にロードしあるいはメモリ18からストアするための備えも設けられている。プロセッサ12はパラメータをCLK60のハイ部分の間にHDP[31:0]72を介して外部コプロセッサ14に受け渡し、オペランドはクロックのローフェーズの間にプロセッサ12によってコプロセッサインタフェース30から受信されかつラッチされる。小さな期間のバスハンドオフを可能にするためドライブが行われる前にクロックがハイに遷移する際に遅延が与えられる。コプロセッサ14のインタフェースは立下りクロックエッジにおいて同じ小さな遅延を提供しなければならない。データ項目のハンドシェイクはデータストローブ(H_DS*70)出力、データアクノレッジ(H_DA*71)入力、およびデータエラー(H_ERR*69)出力信号によってサポートされる。

【0045】

プロセッサ12はソフトウエアサブルーチンが呼び出され(called)または戻る(returned)のとほぼ同じ方法でコプロセッサインタフェース30に対し呼出しまたはコール(call)または戻り(return)パラメータのリストを転送する能力を提供する。アーギュメント(arguments)のカウントは渡されるパラメータの数を制御するためH_CALLまたはH_RETプリミティブに示される。プロセッサ12のレジスタR4の内容で始まるレジスタ値はH_CALL(H_RET)プリミティブの実行の一部として外部コプロセッサ14へ(から)転送される。7つまでのレジスタパラメータが受け渡しできる。この規約はソフトウエアサブルーチンコールの規約と同様のものである。

【0046】

オペランド転送のハンドシェイクはデータストローブ(H_DS*70)出力およびデータアクノレッジ(H_DA*71)入力信号によって制御される。データストローブは転送の期間の間プロセッサ12によって肯定され、かつ転送はプロセッサ12のインタフェース動作とほぼ同様に、重複した方法で行われることになる。データアクノレッジ(H_DA*71)はデータエレメントがコプロセッサ14によって受け入れられまたはドライブされたことを示すために使用される。

【0047】

図15は、前記H_CALLプリミティブに関連するレジスタ46の転送の例を示すタイミング図である。命令プリミティブは複数のプロセッサレジスタを転送するために提供されかつ該転送は理想的にはクロックごとに行うことができる。外部コプロセッサ14への転送のために、プロセッサは現在のアイテムのアクノレッジの前に(または同時に)次のオペランドを自動的にドライブし始める(もし必要であれば)。外部論理はデータの喪失がないことを保証するため1つのレベルのバッファリングが可能でなくてはならない。この図はコプロセッサインタフェース30へのH_CALL転送のシーケンシングまたは順序付けを示しており、この場合2つのレジスタが転送されるべきものである。第2の転送は否定されたデータアクノレッジ(H_DA*)71により反復される。

【0048】

外部コプロセッサ14からプロセッサレジスタ46への転送のために、プロセッサ12はH_DS*70が肯定された後のクロックサイクルごとに外部コプロセッサ14から値を受け入れることができ、かつこれらの値はそれらが受信される際にレジスタファイル46へと書き込まれ、従ってバッファリングは必要とされない。

【0049】

図16は、前記H_RETプリミティブに関連するレジスタ46の転送の例を示すタイミング図である。この例では、2つのレジスタ46の値が転送される。コプロセッサ14はH_EXEC*65信号の肯定に続くクロックで始まりデータを駆動することができ、それはこれがH_DS*70が始めに肯定されるクロックであるためである。H_DS*70の出力はCLK60の立上がりエッジで遷移し、一方H_DA*71の入力はCLK60のローフェーズの間にサンプルされる。

【0050】

プロセッサ12はH_LDまたはH_ST命令プリミティブによってコプロセッサインタフェース30へあるいはから単一命令オペランドを転送する能力を提供する。

【0051】

H_LDプリミティブはメモリ18からコプロセッサ14へデータを転送するために使用される。コプロセッサ14へのオペランド転送のハンドシェイクはデータストローブ(H_DS*)70信号によって制御される。データストローブはプロセッサ12によって肯定されて有効なオペランドがHDP[31:0]72バス上に与えられたことを示す。データアクノレッジ(H_DA*)71入力はこの転送に対しては無視される。

【0052】

図17は、コプロセッサインタフェース30へのH_LD転送のシーケンシングを示すタイミング図である。この場合、1つのノーウエイト状態(no−wait state)のメモリ18のアクセスがある。nのウエイト状態を有するメモリ18のアクセスに対しては、オペランドおよびH_DS*70はnクロック後にドライブされる。もしベースレジスタ46をロードの実効アドレスによって更新するためのオプションが選択されれば、更新値はそれが計算された後の最初のクロック(H_EXEC*65の肯定に続くクロック)でHDP[31:0]72においてドライブされる。

【0053】

図18は、メモリ18のアクセスが結果としてアクセス例外になる場合のプロトコルを示すタイミング図である。そのような場合、H_ERR*69信号は外部コプロセッサ14へと肯定し戻される。

【0054】

H_STプリミティブはデータをコプロセッサ14からメモリ18に転送するために使用できる。もし前記ストアの実効アドレスによってベースレジスタ46を更新するオプションが選択されれば、該更新値はそれが計算された後の最初のクロック(H_EXEC*65の肯定に続くクロック)でHDP[31:0]72においてドライブされる。

【0055】

図19は、H_STプリミティブに関連する転送の例を示すタイミング図である。H_STプリミティブに関連するハンドシェイクは2つの部分からなり、すなわちストアのためのデータを提供しなければならない、コプロセッサ14からの初期ハンドシェイク、およびいったんメモリ18へのストアが完了した場合のプロセッサ12からの完了ハンドシェイクである。

【0056】

前記初期ハンドシェイクはコプロセッサ14がストアデータをプロセッサ12へとドライブしたことを通知するためプロセッサ12へのH_DA*71入力を使用する。H_DA*71信号はコプロセッサ14によってデータがHDP[31:0]72へとドライブされるのと同じクロックで肯定される。ストアデータはハーフワードサイズのストアに対してはバスの下半分(lower half)から取られ、上位16ビットはメモリ18に書き込まれない。前記H_DA*71信号はH_EXEC*65信号が肯定されたクロックと共に始まりサンプルされることになる。メモリサイクルはH_DA*71が認識されるクロックの間要求され、かつストアデータは引き続くクロックに際してメモリ18にドライブされる。いったんストアが完了すると、プロセッサ12はH_DS*70信号を肯定する。

【0057】

図20は遅延されたストアデータを備えた転送の例を示すタイミング図である。

【0058】

図21は、ストアがアクセスエラーの結果となる場合のプロトコル信号を示すタイミング図である。ここでは、H_ERR*69信号が肯定されることに注意を要する。もしハードウエアユニットがH_EXEC*65が肯定されるクロックでH_EXCP*66を肯定することにより命令を中止すれば、H_DA*71信号は肯定されるべきではない。

【0059】

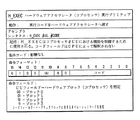

図22〜26はハードウエアアクセラレータ(またはコプロセッサ)14へのインタフェースのために命令セットの一部として提供される命令を示す。プロセッサ12が前記プリミティブのフィールドのいくつかを解釈し、他のものはコプロセッサ14のみによって解釈される。

【0060】

図22は、H_CALLプリミティブに対する命令フォーマットを示す。この命令はコプロセッサ14によって実施される機能を「コール」するまたは「呼び出す」(call)ために使用される。パラダイム(paradigm)は、ハードウエアコンテクストにおけるものを除き、標準的なソフトウエアコール規約と同様である。H_CALLプリミティブはプロセッサ12およびコプロセッサ14の双方によって解釈されて「コールパラメータ(call parameters)」またはアーギュメントのリストをプロセッサ12から転送しかつコプロセッサ14において特定の機能を開始する。

【0061】

命令ワードのUUおよびCODE(コード)フィールドはプロセッサ12によって解釈されず、これらはコプロセッサ14の特定の機能を示すために使用される。UUフィールドは特定のコプロセッサ14,16を特定することができ、かつCODEフィールドは特定の動作または操作を特定することができる。CNTフィールドはプロセッサ12およびコプロセッサ14の双方によって解釈され、かつコプロセッサ14に受け渡すためにレジスタアーギュメントの数を特定する。

【0062】

アーギュメントは汎用レジスタ46からR4で始まりかつR(4+CNT−1)へと続いて受け渡される。7個までのパラメータまたはレジスタ46が単一のH_CALLの実施または発動において受け渡すことができる。

【0063】

H_CALL命令はモジュール方式のモジュール発動(modular module invocation)を実施するために使用できる。この種のインタフェースを使用することは長い間より高い信頼性およびより少ないバグを備えたソフトウエアシステムを生み出すために知られてきている。通常、機能パラメータは値(value)によって最もよく受け渡される。これは副作用を大幅に低減する。多くの場合、CおよびC++のようなブロック構造言語に対する近代のコンパイラは短いシーケンスのパラメータまたはアーギュメントをレジスタ46における発動された機能またはサブルーチンに渡す。この技術はH_CALL命令と共に実施することができる。コンパイラは7個までのパラメータまたはアーギュメントをR4で始まり引き続くレジスタ46にロードするよう構成でき、次にH_CALL命令を発生し、これは標準的なコンパイラ発生サブルーチンリンケージ命令を置き換える。

【0064】

図23は、H_RETプリミティブに対する命令フォーマットを示す。この命令はコプロセッサ14によって実施される機能「からの戻り(return from)」のために使用される。パラダイムは、ハードウエアコンテクストにおけるものを除き、プロセッサ12によって使用されるソフトウエアコール規約と同様である。H_RETプリミティブはプロセッサ12およびコプロセッサ14の双方によって解釈されて「戻りパラメータ(return parameters)」または値のリストをコプロセッサ14からプロセッサ12へと転送する。

【0065】

前記命令ワードのUUおよびCODE(コード)フィールドはプロセッサ12によって解釈されず、これらはコプロセッサ14の特定の機能を示すために使用される。UUフィールドはハードウエアユニットを特定することができ、かつCODEフィールドは戻りのためにコプロセッサ14における特定の動作または一組のレジスタ46を特定することができる。CNTフィールドはプロセッサ12およびコプロセッサ14の双方によって解釈され、かつコプロセッサ14からプロセッサ12へと渡すレジスタ46のアーギュメントの数を特定する。

【0066】

アーギュメントはR4で始まりかつR(4+CNT−1)へとプロセッサ12の一般または汎用レジスタ46へ渡される。7個までのパラメータ(またはレジスタ内容)を戻すことができる。

【0067】

H_CALL命令と同様に、H_RET命令はまたモジュール方式のプログラミングを実施するために使用できる。構造プログラミング(structured programming)は機能戻り値が値によってコーリングルーチンへと最もよく渡し戻されることを要求する。これはしばしばコンパイラによって1つまたはそれ以上の戻り値をサブルーチンまたは機能戻りのためのレジスタに与えることによって効率的に行われる。しかしながら、伝統的な構造プログラミングはサブルーチンまたは機能が該サブルーチンまたは機能の発動の直後に戻ることを期待することに注目すべきである。コプロセッサ14の場合には、実行はしばしば発動プロセッサ12のものと非同期である。H_RET命令はプロセッサ12およびコプロセッサ14を再同期するために使用できる。従って、プロセッサ12は1つまたはそれ以上のレジスタ46をロードし、コプロセッサ14を1つまたはそれ以上のH_CALL命令によってアクティベイトまたは活性化し、関連のない命令を実行し、かつ次にコプロセッサ14と再同期し一方でH_RET命令を発行することによりコプロセッサ14から結果としての値(単数または複数)を受けることができる。

【0068】

図24は、H_EXECプリミティブに対する命令フォーマットを示す。この命令は機能を開始しあるいはアクセラレータによって実施される動作モードに入るために使用できる。H_EXEC命令はUUフィールドによって特定される特定のコプロセッサ14,16における機能を制御するために使用できる。コードフィールドはプロセッサ12によって解釈されずむしろ指定されたコプロセッサ14,16のために確保される。該命令ワードのUUおよびCODEフィールドはプロセッサ12によって解釈または変換処理されず、これらはコプロセッサ14の特定の機能を特定するために使用される。UUフィールドは特定のコプロセッサ14,16を指定することができ、かつCODEフィールドは特定の動作を示すことができる。

【0069】

図25は、H_LD命令のための命令フォーマットを示す。この命令はメモリオペランドを汎用目的のレジスタ(GPR)46に一時的に格納することなくある値をメモリ18からコプロセッサ14に受け渡すために使用される。メモリオペランドはベースポインタおよびオフセットを使用してアドレスされる。

【0070】

H_LD命令はメモリ18へのある値のロードを行い、かつメモリオペランドをそれをレジスタ46に格納することなくコプロセッサ14に渡す。H_LD動作は3つのオプション、w−ワード、h−ハーフワードおよびu−更新(update)を有する。DISPはIMM2フィールドをロードのサイズでスケーリングし、かつゼロ拡張(zero−extending)を行うことによって得られる。この値はレジスタRXの値に加えられかつ特定されたサイズのロードはこのアドレスから行われ、ロードの結果はハードウエアインタフェース28に渡される。ハーフワードのロードに対しては、フェッチされたデータは32ビットへとゼロ拡張される。もしuオプションが特定されれば、ロードの実効アドレスはそれが計算された後にレジスタRX46に入れられる。

【0071】

前記命令ワードのUUフィールドはプロセッサ12によって解釈されず、このフィールドは特定のコプロセッサ14,16を特定することができる。Szフィールドはオペランドのサイズ(ハーフワードまたはワードのみ)を特定する。DispフィールドはRbaseフィールドによって特定されるレジスタの内容に加えられるべき符号なしの(unsigned)オフセット値を特定してロードのための実効アドレスを形成する。Dispフィールドの値は転送されるべきオペランドのサイズによってスケーリングされる。Upフィールドは前記Rbaseレジスタ46がロードの実効アドレスによってそれが計算された後に更新されるべきか否かを特定する。このオプションまたは選択肢は「自動更新(auto−update)」アドレシングモードを可能にする。

【0072】

図26は、H_ST命令に対する命令フォーマットを示す。この命令はプロセッサ12のレジスタ46にメモリオペランドを一時的に記憶することなくある値をコプロセッサ14からメモリ18に渡すために使用される。前記メモリオペランドはベースポインタおよびオフセットを使用してアドレスされる。

【0073】

前記命令ワードのUUフィールドはプロセッサ12によって解釈されない。むしろ、このフィールドは特定のコプロセッサ14,16を特定することができる。Szフィールドはオペランドのサイズ(ハーフワードまたはワードのみ)を特定する。DispフィールドはRbaseフィールドによって特定されるレジスタ46の内容に加えられるべき符号なしのオフセット値を特定しストアのための実効アドレスを形成する。Dispフィールドの値は転送されるべきオペランドのサイズによってスケーリングまたは尺度変更される。Upフィールドは前記Rbaseレジスタが前記ストアの実効アドレスによってそれが計算された後に更新されるべきか否かを特定する。このオプションは「自動更新」アドレシングモードを可能にする。

【0074】

H_ST命令はメモリ18へのコプロセッサ14からのオペランドのストアを、それをレジスタ46に格納することなく、達成する。H_ST動作は3つのオプション、w−ワード、h−ハーフワード、およびu−更新を有する。DispはIMM2フィールドをストアのサイズによってスケーリングすることおよびゼロ拡張により得られる。この値はレジスタRXの値に加えられかつ特定されたサイズのストアはこのアドレスに対して行なわれ、該ストアのためのデータはハードウェアインタフェースから得られる。もし前記uオプションが特定されれば、ロードの実効アドレスがそれが計算された後にレジスタRXに入れられる。

【0075】

前記H_LD命令およびH_ST命令はデータがレジスタ46を通って導き移動されることなくオペランドをメモリ18からコプロセッサ14へかつコプロセッサ14からメモリ18へ移動するための効率的なメカニズムを提供する。オフセットおよびインデクスの備えはアレイを効率的に歩進するためのメカニズムを提供する。したがって、これらの命令は特にループ内で有用である。両方の命令はプロセッサ12をコプロセッサ14とロードまたはストアされるそれぞれのオペランドに対して同期させることに注目すべきである。もしこれが必要ではないかあるいは好ましい場合には、あるいは、指定されたレジスタ(単数または複数)46をメモリ18からのデータによって反復的にロードすることによりデータをコプロセッサ14に流し、かつコプロセッサインタフェースバス30もまたレジスタスヌーピングのために使用されるからコプロセッサ14がこれらのロードを検出するようにすることができる。

【0076】

当業者は本発明の精神から離れることなく修正および変更を行なうことができることを理解するであろう。したがって、この発明は添付の特許請求の範囲に含まれるすべてのそのような変更および修正を含むものと考える。

【0077】

【発明の効果】

以上のように、本発明によれば、プロセッサおよび少なくとも1つのコプロセッサを有するデータ処理システムにおいて、プロセッサとコプロセッサとの間のインタフェースにおける従来技術の欠点を克服し高性能のデータ処理システムが実現できる。

【図面の簡単な説明】

【図1】本発明に係わるデータ処理システムの一実施形態を示すブロック図である。

【図2】図1のプロセッサの一部を示すブロック図である。

【図3】図1のコプロセッサの一部の一実施形態を示すブロック図である。

【図4】本発明に係わるレジスタスヌーピング動作を示すタイミング図である。

【図5】命令ハンドシェイクのための基本的な命令インタフェース動作を示すタイミング図である。

【図6】H_BUSY*信号がコプロセッサインタフェース命令の実行を制御するために使用される場合の命令インタフェース動作を示すタイミング図である。

【図7】命令放棄を示すタイミング図である

【図8】命令パイプラインストールの例を示すタイミング図である。

【図9】ストールのないバック−バック実行の例を示すタイミング図である。

【図10】内部パイプラインストールを有するバック−バック動作を示すタイミング図である。

【図11】H_BUSY*ストールを有するバック−バックコプロセッサインタフェース30の命令を示すタイミング図である。

【図12】コプロセッサインタフェースオペコードのデコードおよび試みられた実行に応じてコプロセッサにより肯定されるH_EXCP*信号の例を示すタイミング図である。

【図13】コプロセッサインタフェース命令が放棄された場合のコプロセッサインタフェースオペコードのデコードおよび試みられた実行に応じてコプロセッサにより肯定されるH_EXCP*信号の例を示すタイミング図である。

【図14】コプロセッサインタフェースオペコードの実行を遅延するためにH_BUSY*が肯定された例を示すタイミング図である。

【図15】H_CALLプリミティブに関連するレジスタ転送の例を示すタイミング図である。

【図16】H_RETプリミティブに関連するレジスタ転送の例を示すタイミング図である。

【図17】コプロセッサインタフェースへのH_LD転送のシーケンシングを示すタイミング図である。

【図18】メモリアクセスが結果としてアクセス例外となるプロトコルを示すタイミング図である。

【図19】H_STプリミティブに関連する転送の例を示すタイミング図である。

【図20】遅延されたストアデータを有する転送の例を示すタイミング図である。

【図21】ストアが結果としてアクセスエラーとなる場合のプロトコル信号を示すタイミング図である。

【図22】本発明に係わるH_CALLプリミティブのための命令フォーマットを示す説明図である。

【図23】本発明に係わるH_RETプリミティブのための命令フォーマットを示す説明図である。

【図24】本発明に係わるH_EXECプリミティブのための命令フォーマットを示す説明図である。

【図25】本発明に係わるH_LD命令に対する命令フォーマットを示す説明図である。

【図26】本発明に係わるH_ST命令のための命令フォーマットを示す説明図である。

【符号の説明】

10 データ処理システム

12 プロセッサ

14,16 コプロセッサ

18 メモリ

20 他のモジュール

22 外部バスインタフェース

24 メモリ

26 外部バス

28 バス

30 コプロセッサインタフェース

31,32,33,34,35 集積回路端子

Claims (11)

- コプロセッサバス(30)を介して結合されたコプロセッサ(14,16)と協働するよう構成されたプロセッサ(12)を動作させる方法であって、前記コプロセッサバスはシステムバスから分離されておりかつ前記プロセッサは前記システムバスを使用することなく前記コプロセッサバスを介して前記コプロセッサと通信することが可能であり、前記プロセッサ(12)は前記コプロセッサ(14,16)と、前記コプロセッサに転送されるべきアーギュメントの数を規定するカウントフィールドおよびコードフィールドを備えた少なくとも1つの命令(H_CALL)の実行において協働し、前記方法は、

前記命令を受ける段階、

前記コプロセッサバスにより第1のサイクルを介して、前記コプロセッサに前記カウントおよびコードフィールドを提供する段階、

もし前記カウントフィールドがゼロより大きなある値、n、を有していれば、前記コプロセッサに、前記コプロセッサバスによって第2のサイクルを介して、第1のオペランドを提供する段階、そして

前記命令を完了する段階、

を具備することを特徴とするプロセッサ(12)を動作させる方法。 - コプロセッサバス(30)を介して結合されたコプロセッサ(14,16)と協働するよう構成されたプロセッサ(12)を動作させる方法であって、前記コプロセッサバスはシステムバスから分離されておりかつ前記プロセッサは前記システムバスを使用することなく前記コプロセッサバスを介して前記コプロセッサと通信可能であり、前記プロセッサ(12)は前記コプロセッサ(14,16)と、前記コプロセッサから受信すべきアーギュメントの数を規定するカウントフィールドおよびコードフィールドを備えた少なくとも1つの命令(H_RET)の実行において協働し、前記方法は、

前記命令を受ける段階、

前記コプロセッサバスにより第1のサイクルを介して、前記コプロセッサに前記カウントおよびコードフィールドを提供する段階、

もし前記カウントフィールドがゼロより大きなある値、n、を有していれば、前記コプロセッサバスによって第2のサイクルを介して、前記コプロセッサから第1のオペランドを受ける段階、そして

前記命令を完了する段階、

を具備することを特徴とするプロセッサ(12)を動作させる方法。 - 複数のレジスタを備えたレジスタファイルを有する、プロセッサによって、コプロセッサ通信バスを介して、前記レジスタファイルにおける全ての書き込み処理を放送する方法であって、

前記レジスタファイルに書き込まれるべきオペランドを受ける段階、

前記レジスタファイルにおける前記複数のレジスタの内の1つを選択する段階、そして

前記レジスタファイルにかつ前記コプロセッサ通信バスを介して、

前記レジスタファイルに書き込まれるべき前記オペランド、

前記レジスタファイルにおける前記複数のレジスタの内の前記選択された1つを示す第1の制御信号、および

前記オペランドが前記複数のレジスタの内の前記選択された1つに書き込まれることを要求する第2の制御信号、

を提供する段階、

を具備することを特徴とする方法。 - 第1のプロセッサによって、コプロセッサ通信バスを介して、前記第1のプロセッサとは別個の第2のプロセッサにおける、複数のレジスタを備えた、レジスタファイルへの全ての書き込み処理を監視する方法であって、

前記第2のプロセッサから、前記コプロセッサ通信バスを介して、

前記レジスタファイルに書き込まれるべきオペランド、

前記レジスタファイルにおける前記複数のレジスタの内の選択された1つを示す第1の制御信号、および

前記オペランドが前記複数のレジスタの内の前記選択された1つに書き込まれることを要求する第2の制御信号、

を受ける段階、そして

前記オペランド、前記第1の制御信号および前記第2の制御信号を受けたことに応じて所定の操作を行なう段階、

を具備することを特徴とする方法。 - プロセッサによって、コプロセッサバスを介して、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、

少なくとも部分的に前記デコードと一致した時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記命令が前記コプロセッサバスの第2の部分を介して前記プロセッサによりデコードされていることを示す第1の制御信号、

を提供する段階、

前記命令の実行が進行していることを示すために前記コプロセッサバスに第2の制御信号を提供する段階、そして

もし前記第1の制御信号が前記第2の制御信号が肯定される前に否定されれば、前記命令の処理を中断する段階、

を具備することを特徴とする方法。 - プロセッサによって、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、

少なくとも部分的に前記デコードと一致した時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記命令が前記プロセッサによって前記コプロセッサバスの第2の部分を介してデコードされていることを示す第1の制御信号、

を提供する段階、そして

もし前記命令に先立ち、より前の命令の実行が例外を引き起こせば、前記第1の制御信号を否定しかつ前記命令の処理を中断する段階、

を具備することを特徴とする方法。 - プロセッサによって、コプロセッサバスを介して、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、

少なくとも部分的に前記デコードと一致する時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記命令が前記コプロセッサバスの第2の部分を介して前記プロセッサによりデコードされていることを示す第1の制御信号、

を提供する段階、そして

もし前記命令が前記プロセッサ内の命令レジスタから放棄されれば、前記第1の制御信号を否定しかつ前記命令の処理を中断する段階、

を具備することを特徴とする方法。 - プロセッサによって、コプロセッサバスを介して、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、

少なくとも部分的に前記デコードと一致する時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記命令が前記コプロセッサバスの第2の部分を介して前記プロセッサによりデコードされていることを示す第1の制御信号、

を提供する段階、そして

前記コプロセッサバスから第2の制御信号を受ける段階であって、該第2の制御信号は前記コプロセッサが前記コプロセッサ内の命令バッファを充填することを可能にする、段階、

を具備することを特徴とする方法。 - プロセッサによって、コプロセッサバスを介して、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、そして

少なくとも部分的に前記デコードと一致した時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記コプロセッサバスの第2の部分を介して前記プロセッサがスーパバイザモードで動作しているか否かを示す第1の制御信号、

を提供する段階、

を具備することを特徴とする方法。 - プロセッサによって、コプロセッサバスを介して、実行のために前記プロセッサによって受けた命令のコプロセッサによる実行を開始する方法であって、

前記命令を受ける段階、

前記命令をデコードする段階、

少なくとも部分的に前記デコードと一致した時間に、前記コプロセッサに対し、

前記コプロセッサバスの第1の部分を介して、前記命令の少なくとも所定の部分、および

前記コプロセッサバスの第2の部分を介して前記命令が前記プロセッサによりデコードされていることを示す第1の制御信号、

を提供する段階、そして

前記コプロセッサから、前記命令の前記所定の部分が前記コプロセッサ内で例外を引き起こしたか否かを示す第2の制御信号を受ける段階、

を具備することを特徴とする方法。 - コプロセッサによって、コプロセッサバスを介して前記コプロセッサに結合されたプロセッサにより受けた命令に応じて操作を行なう方法であって、

前記プロセッサから、前記コプロセッサバスの第1の部分を介して前記命令の少なくとも所定の部分および、前記コプロセッサバスの第2の部分を介して、前記命令が前記プロセッサによりデコードされていることを示す第1の制御信号を受ける段階、

前記命令の実行を開始する段階、そして

前記プロセッサに対し前記命令が例外を引き起こしたか否かを示す制御信号を提供する段階、

を具備することを特徴とする方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/924,518 | 1997-09-05 | ||

| US08/924,518 US6505290B1 (en) | 1997-09-05 | 1997-09-05 | Method and apparatus for interfacing a processor to a coprocessor |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11154144A JPH11154144A (ja) | 1999-06-08 |

| JP3920994B2 true JP3920994B2 (ja) | 2007-05-30 |

Family

ID=25450311

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP25936498A Expired - Fee Related JP3920994B2 (ja) | 1997-09-05 | 1998-08-28 | プロセッサをコプロセッサにインタフェースするための方法および装置 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US6505290B1 (ja) |

| EP (2) | EP1282035A1 (ja) |

| JP (1) | JP3920994B2 (ja) |

| KR (1) | KR100563012B1 (ja) |

| CN (3) | CN100573445C (ja) |

| DE (1) | DE69814268T2 (ja) |

| SG (2) | SG102528A1 (ja) |

| TW (1) | TW385410B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002169724A (ja) * | 2000-12-01 | 2002-06-14 | Oki Electric Ind Co Ltd | キャッシュメモリにおける部分無効化装置 |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001092663A (ja) * | 1999-09-17 | 2001-04-06 | Sanyo Electric Co Ltd | データ処理装置 |

| EP2804106A1 (en) * | 2000-09-06 | 2014-11-19 | Ericsson Modems SA | Inter-processor communication system |

| US6829697B1 (en) * | 2000-09-06 | 2004-12-07 | International Business Machines Corporation | Multiple logical interfaces to a shared coprocessor resource |

| JP2002149402A (ja) * | 2000-11-14 | 2002-05-24 | Pacific Design Kk | データ処理装置およびその制御方法 |

| US6754804B1 (en) * | 2000-12-29 | 2004-06-22 | Mips Technologies, Inc. | Coprocessor interface transferring multiple instructions simultaneously along with issue path designation and/or issue order designation for the instructions |

| US7287147B1 (en) * | 2000-12-29 | 2007-10-23 | Mips Technologies, Inc. | Configurable co-processor interface |

| US7237090B1 (en) | 2000-12-29 | 2007-06-26 | Mips Technologies, Inc. | Configurable out-of-order data transfer in a coprocessor interface |

| US7168066B1 (en) | 2001-04-30 | 2007-01-23 | Mips Technologies, Inc. | Tracing out-of order load data |

| US7240203B2 (en) * | 2001-07-24 | 2007-07-03 | Cavium Networks, Inc. | Method and apparatus for establishing secure sessions |

| GB2378271B (en) * | 2001-07-30 | 2004-12-29 | Advanced Risc Mach Ltd | Handling of coprocessor instructions in a data processing apparatus |

| US7228401B2 (en) | 2001-11-13 | 2007-06-05 | Freescale Semiconductor, Inc. | Interfacing a processor to a coprocessor in which the processor selectively broadcasts to or selectively alters an execution mode of the coprocessor |

| US6886092B1 (en) * | 2001-11-19 | 2005-04-26 | Xilinx, Inc. | Custom code processing in PGA by providing instructions from fixed logic processor portion to programmable dedicated processor portion |

| US6795877B2 (en) * | 2001-11-29 | 2004-09-21 | Intel Corporation | Configurable serial bus to couple baseband and application processors |

| FR2834154B1 (fr) * | 2001-12-21 | 2005-03-11 | Oberthur Card Syst Sa | Unite electronique incluant des moyens de cryptographie capables de traiter des informations a haut debit |

| US7305567B1 (en) | 2002-03-01 | 2007-12-04 | Cavium Networks, In. | Decoupled architecture for data ciphering operations |

| US7154941B2 (en) * | 2002-06-28 | 2006-12-26 | Nokia Corporation | Modem having a vector-architecture processor, and associated methodology therefor |

| EP1387259B1 (en) * | 2002-07-31 | 2017-09-20 | Texas Instruments Incorporated | Inter-processor control |

| JP4182801B2 (ja) * | 2003-04-24 | 2008-11-19 | 日本電気株式会社 | マルチプロセサシステム |

| KR100849296B1 (ko) * | 2003-06-13 | 2008-07-29 | 삼성전자주식회사 | 주제어부와 보조제어부를 구비하는 시스템에서의보조제어부의 초기화 장치 및 방법 |

| JP4224430B2 (ja) * | 2003-07-07 | 2009-02-12 | 株式会社ルネサステクノロジ | 情報処理装置 |

| US7441106B2 (en) | 2004-07-02 | 2008-10-21 | Seagate Technology Llc | Distributed processing in a multiple processing unit environment |

| ATE463786T1 (de) * | 2004-07-09 | 2010-04-15 | Michael Colin George Chapman | Hochleistungsfähiger benutzer-konfigurierbarer prozessor |

| JP3768516B1 (ja) * | 2004-12-03 | 2006-04-19 | 株式会社ソニー・コンピュータエンタテインメント | マルチプロセッサシステムとそのシステムにおけるプログラム実行方法 |

| US20060155974A1 (en) * | 2005-01-07 | 2006-07-13 | Moyer William C | Data processing system having flexible instruction capability and selection mechanism |

| JP3867804B2 (ja) * | 2005-03-22 | 2007-01-17 | セイコーエプソン株式会社 | 集積回路装置 |

| US7472261B2 (en) * | 2005-11-08 | 2008-12-30 | International Business Machines Corporation | Method for performing externally assisted calls in a heterogeneous processing complex |

| KR100781340B1 (ko) * | 2006-09-18 | 2007-11-30 | 삼성전자주식회사 | 사용자 정의 확장 연산을 처리하는 연산 시스템 및 방법 |

| US8095699B2 (en) * | 2006-09-29 | 2012-01-10 | Mediatek Inc. | Methods and apparatus for interfacing between a host processor and a coprocessor |

| WO2008045341A1 (en) * | 2006-10-05 | 2008-04-17 | Arc International | Inter-processor communication method |

| US20080147357A1 (en) * | 2006-12-15 | 2008-06-19 | Iintrinisyc Software International | System and method of assessing performance of a processor |

| FR2942556B1 (fr) * | 2009-02-24 | 2011-03-25 | Commissariat Energie Atomique | Unite d'allocation et de controle |

| CN102804136B (zh) | 2009-06-23 | 2015-03-11 | 精工爱普生株式会社 | 副处理器、集成电路装置及电子设备 |

| EP2278452A1 (en) * | 2009-07-15 | 2011-01-26 | Nxp B.V. | Coprocessor programming |

| JP5632651B2 (ja) * | 2010-05-19 | 2014-11-26 | スパンション エルエルシー | 半導体回路及び設計装置 |

| US20130305020A1 (en) * | 2011-04-01 | 2013-11-14 | Robert C. Valentine | Vector friendly instruction format and execution thereof |

| CN102736895B (zh) | 2011-04-07 | 2015-06-10 | 中兴通讯股份有限公司 | 一种实现寄存器文件间的数据传输方法及装置 |

| EP2525286A1 (en) * | 2011-05-17 | 2012-11-21 | Nxp B.V. | Co-processor interface |

| JP2012252374A (ja) * | 2011-05-31 | 2012-12-20 | Renesas Electronics Corp | 情報処理装置 |

| JP5653865B2 (ja) * | 2011-08-23 | 2015-01-14 | 日本電信電話株式会社 | データ処理システム |

| CN104011670B (zh) | 2011-12-22 | 2016-12-28 | 英特尔公司 | 用于基于向量写掩码的内容而在通用寄存器中存储两个标量常数之一的指令 |

| US9329870B2 (en) | 2013-02-13 | 2016-05-03 | International Business Machines Corporation | Extensible execution unit interface architecture with multiple decode logic and multiple execution units |

| US9203835B2 (en) | 2013-03-01 | 2015-12-01 | Paypal, Inc. | Systems and methods for authenticating a user based on a biometric model associated with the user |

| US20150261535A1 (en) * | 2014-03-11 | 2015-09-17 | Cavium, Inc. | Method and apparatus for low latency exchange of data between a processor and coprocessor |

| CN105988773B (zh) * | 2015-02-10 | 2021-03-09 | 恩智浦美国有限公司 | 硬件接口组件和用于硬件接口组件的方法 |

| CN106648400B (zh) * | 2015-11-03 | 2020-04-03 | 华为终端有限公司 | 一种触摸数据上报的方法及电子设备 |

| CN108076476B (zh) * | 2016-11-18 | 2020-11-06 | 华为技术有限公司 | 用于传输数据的方法和装置 |

| US11263014B2 (en) * | 2019-08-05 | 2022-03-01 | Arm Limited | Sharing instruction encoding space between a coprocessor and auxiliary execution circuitry |

| CN110532040A (zh) * | 2019-08-29 | 2019-12-03 | 北京地平线机器人技术研发有限公司 | 固件程序的加载方法及装置、存储介质和电子设备 |

| CN111917471B (zh) * | 2020-09-09 | 2021-09-28 | 西安工程大学 | 一种自由空间可见光通信系统及其通信性能优化算法 |

Family Cites Families (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4270167A (en) | 1978-06-30 | 1981-05-26 | Intel Corporation | Apparatus and method for cooperative and concurrent coprocessing of digital information |

| US4547849A (en) | 1981-12-09 | 1985-10-15 | Glenn Louie | Interface between a microprocessor and a coprocessor |

| US4509116A (en) | 1982-04-21 | 1985-04-02 | Digital Equipment Corporation | Special instruction processing unit for data processing system |

| US4729094A (en) | 1983-04-18 | 1988-03-01 | Motorola, Inc. | Method and apparatus for coordinating execution of an instruction by a coprocessor |

| US4715013A (en) | 1983-04-18 | 1987-12-22 | Motorola, Inc. | Coprocessor instruction format |

| US4731736A (en) | 1983-04-18 | 1988-03-15 | Motorola, Inc. | Method and apparatus for coordinating execution of an instruction by a selected coprocessor |

| US4763242A (en) * | 1985-10-23 | 1988-08-09 | Hewlett-Packard Company | Computer providing flexible processor extension, flexible instruction set extension, and implicit emulation for upward software compatibility |

| JPH079643B2 (ja) | 1986-09-24 | 1995-02-01 | 株式会社日立マイコンシステム | コプロセツサデ−タ転送制御方式 |

| US5001624A (en) | 1987-02-13 | 1991-03-19 | Harrell Hoffman | Processor controlled DMA controller for transferring instruction and data from memory to coprocessor |

| US5091845A (en) * | 1987-02-24 | 1992-02-25 | Digital Equipment Corporation | System for controlling the storage of information in a cache memory |

| IN171198B (ja) | 1987-02-24 | 1992-08-15 | Digital Equipment Corp | |

| US5226170A (en) * | 1987-02-24 | 1993-07-06 | Digital Equipment Corporation | Interface between processor and special instruction processor in digital data processing system |

| US5341482A (en) * | 1987-03-20 | 1994-08-23 | Digital Equipment Corporation | Method for synchronization of arithmetic exceptions in central processing units having pipelined execution units simultaneously executing instructions |

| JPS63259727A (ja) | 1987-04-17 | 1988-10-26 | Hitachi Ltd | コプロセツサのインタ−フエイス方式 |

| US4991078A (en) | 1987-09-29 | 1991-02-05 | Digital Equipment Corporation | Apparatus and method for a pipelined central processing unit in a data processing system |

| JPH0679307B2 (ja) | 1987-10-22 | 1994-10-05 | 日本電気株式会社 | コプロセッサの並行動作制御方式 |

| JPH01147656A (ja) | 1987-12-03 | 1989-06-09 | Nec Corp | マイクロプロセッサ |

| JPH01277934A (ja) * | 1988-04-29 | 1989-11-08 | Nec Corp | パラメータリスト参照方法の切換え方式 |

| JP2741867B2 (ja) * | 1988-05-27 | 1998-04-22 | 株式会社日立製作所 | 情報処理システムおよびプロセツサ |

| US5109514A (en) * | 1988-07-28 | 1992-04-28 | Sun Microsystems, Inc. | Method and apparatus for executing concurrent CO processor operations and precisely handling related exceptions |

| JP2754825B2 (ja) | 1989-02-03 | 1998-05-20 | 日本電気株式会社 | マイクロプロセッサ |

| US5093908A (en) | 1989-04-17 | 1992-03-03 | International Business Machines Corporation | Method and apparatus for executing instructions in a single sequential instruction stream in a main processor and a coprocessor |

| US5218711A (en) | 1989-05-15 | 1993-06-08 | Mitsubishi Denki Kabushiki Kaisha | Microprocessor having program counter registers for its coprocessors |

| US5247650A (en) * | 1989-08-30 | 1993-09-21 | Industrial Technology Institute | System for combining originally software incompatible control, kinematic, and discrete event simulation systems into a single integrated simulation system |

| WO1991011765A1 (en) | 1990-01-29 | 1991-08-08 | Teraplex, Inc. | Architecture for minimal instruction set computing system |

| DE69127936T2 (de) | 1990-06-29 | 1998-05-07 | Digital Equipment Corp | Busprotokoll für Prozessor mit write-back cache |

| US5305446A (en) | 1990-09-28 | 1994-04-19 | Texas Instruments Incorporated | Processing devices with improved addressing capabilities, systems and methods |

| US5826101A (en) | 1990-09-28 | 1998-10-20 | Texas Instruments Incorporated | Data processing device having split-mode DMA channel |

| US5283881A (en) * | 1991-01-22 | 1994-02-01 | Westinghouse Electric Corp. | Microcoprocessor, memory management unit interface to support one or more coprocessors |

| JP3206006B2 (ja) * | 1991-01-25 | 2001-09-04 | 株式会社日立製作所 | 二重化バス制御方法及び装置 |

| US5488729A (en) | 1991-05-15 | 1996-01-30 | Ross Technology, Inc. | Central processing unit architecture with symmetric instruction scheduling to achieve multiple instruction launch and execution |

| US5430850A (en) | 1991-07-22 | 1995-07-04 | Massachusetts Institute Of Technology | Data processing system with synchronization coprocessor for multiple threads |

| US5767939A (en) | 1991-10-09 | 1998-06-16 | Seiko Epson Corporation | Eyeglass lens |

| US5708784A (en) * | 1991-11-27 | 1998-01-13 | Emc Corporation | Dual bus computer architecture utilizing distributed arbitrators and method of using same |

| WO1993016437A1 (en) | 1992-02-18 | 1993-08-19 | Apple Computer, Inc. | A programming model for a coprocessor on a computer system |

| US5481743A (en) | 1993-09-30 | 1996-01-02 | Apple Computer, Inc. | Minimal instruction set computer architecture and multiple instruction issue method |

| US5706478A (en) * | 1994-05-23 | 1998-01-06 | Cirrus Logic, Inc. | Display list processor for operating in processor and coprocessor modes |

| JP2987308B2 (ja) * | 1995-04-28 | 1999-12-06 | 松下電器産業株式会社 | 情報処理装置 |

| US5603047A (en) | 1995-10-06 | 1997-02-11 | Lsi Logic Corporation | Superscalar microprocessor architecture |

| US5898897A (en) * | 1996-10-18 | 1999-04-27 | Samsung Electronics Company, Ltd. | Bit stream signal feature detection in a signal processing system |

| US5953741A (en) * | 1996-11-27 | 1999-09-14 | Vlsi Technology, Inc. | Stack cache for stack-based processor and method thereof |

| US5715439A (en) * | 1996-12-09 | 1998-02-03 | Allen-Bradley Company, Inc. | Bi-directional co-processor interface |

| GB2326253A (en) | 1997-06-10 | 1998-12-16 | Advanced Risc Mach Ltd | Coprocessor data access control |

| US6760833B1 (en) | 1997-08-01 | 2004-07-06 | Micron Technology, Inc. | Split embedded DRAM processor |

| US6226738B1 (en) | 1997-08-01 | 2001-05-01 | Micron Technology, Inc. | Split embedded DRAM processor |

| US6163836A (en) | 1997-08-01 | 2000-12-19 | Micron Technology, Inc. | Processor with programmable addressing modes |

| US6216222B1 (en) | 1998-05-14 | 2001-04-10 | Arm Limited | Handling exceptions in a pipelined data processing apparatus |

| US6247113B1 (en) | 1998-05-27 | 2001-06-12 | Arm Limited | Coprocessor opcode division by data type |

| US6434689B2 (en) | 1998-11-09 | 2002-08-13 | Infineon Technologies North America Corp. | Data processing unit with interface for sharing registers by a processor and a coprocessor |

| KR100308618B1 (ko) | 1999-02-27 | 2001-09-26 | 윤종용 | 단일 칩 상의 마이크로프로세서-코프로세서 시스템을 구비한 파이프라인 데이터 처리 시스템 및 호스트 마이크로프로세서와 코프로세서 사이의 인터페이스 방법 |

| US6446221B1 (en) | 1999-05-19 | 2002-09-03 | Arm Limited | Debug mechanism for data processing systems |

| US6513091B1 (en) | 1999-11-12 | 2003-01-28 | International Business Machines Corporation | Data routing using status-response signals |

| US6557069B1 (en) | 1999-11-12 | 2003-04-29 | International Business Machines Corporation | Processor-memory bus architecture for supporting multiple processors |

| US6526469B1 (en) | 1999-11-12 | 2003-02-25 | International Business Machines Corporation | Bus architecture employing varying width uni-directional command bus |

| US6658545B1 (en) | 2000-02-16 | 2003-12-02 | Lucent Technologies Inc. | Passing internal bus data external to a completed system |

| US6626489B2 (en) * | 2001-07-18 | 2003-09-30 | Evenflo Company, Inc. | Infant seat providing a cushioned carry |

-

1997

- 1997-09-05 US US08/924,518 patent/US6505290B1/en not_active Expired - Fee Related

-

1998

- 1998-08-24 EP EP02024180A patent/EP1282035A1/en not_active Withdrawn

- 1998-08-24 DE DE69814268T patent/DE69814268T2/de not_active Expired - Fee Related

- 1998-08-24 EP EP98115908A patent/EP0901071B1/en not_active Expired - Lifetime

- 1998-08-28 SG SG9803351A patent/SG102528A1/en unknown

- 1998-08-28 KR KR1019980035079A patent/KR100563012B1/ko not_active IP Right Cessation

- 1998-08-28 TW TW087114309A patent/TW385410B/zh not_active IP Right Cessation

- 1998-08-28 JP JP25936498A patent/JP3920994B2/ja not_active Expired - Fee Related

- 1998-08-28 SG SG200102164A patent/SG103282A1/en unknown

- 1998-09-04 CN CNB2007100016673A patent/CN100573445C/zh not_active Expired - Lifetime

- 1998-09-04 CN CNB981185819A patent/CN1299218C/zh not_active Expired - Lifetime

- 1998-09-04 CN CNB2004100696118A patent/CN1307536C/zh not_active Expired - Lifetime

-

2000

- 2000-06-30 US US09/609,260 patent/US6327647B1/en not_active Expired - Lifetime

-

2001

- 2001-11-05 US US10/007,836 patent/US7007154B2/en not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002169724A (ja) * | 2000-12-01 | 2002-06-14 | Oki Electric Ind Co Ltd | キャッシュメモリにおける部分無効化装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP0901071A3 (en) | 1999-10-13 |

| EP0901071A2 (en) | 1999-03-10 |

| US6505290B1 (en) | 2003-01-07 |

| SG102528A1 (en) | 2004-03-26 |

| CN1211012A (zh) | 1999-03-17 |

| US7007154B2 (en) | 2006-02-28 |

| KR100563012B1 (ko) | 2007-04-10 |

| CN1983167A (zh) | 2007-06-20 |

| CN1560729A (zh) | 2005-01-05 |

| KR19990029361A (ko) | 1999-04-26 |

| CN100573445C (zh) | 2009-12-23 |

| DE69814268D1 (de) | 2003-06-12 |

| EP1282035A1 (en) | 2003-02-05 |

| US20020049894A1 (en) | 2002-04-25 |

| SG103282A1 (en) | 2004-04-29 |

| JPH11154144A (ja) | 1999-06-08 |

| EP0901071B1 (en) | 2003-05-07 |

| US6327647B1 (en) | 2001-12-04 |

| TW385410B (en) | 2000-03-21 |

| CN1307536C (zh) | 2007-03-28 |

| CN1299218C (zh) | 2007-02-07 |

| DE69814268T2 (de) | 2004-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3920994B2 (ja) | プロセッサをコプロセッサにインタフェースするための方法および装置 | |

| US5923893A (en) | Method and apparatus for interfacing a processor to a coprocessor | |

| US5983338A (en) | Method and apparatus for interfacing a processor to a coprocessor for communicating register write information | |

| US5179530A (en) | Architecture for integrated concurrent vector signal processor | |

| US6058465A (en) | Single-instruction-multiple-data processing in a multimedia signal processor | |

| US5838984A (en) | Single-instruction-multiple-data processing using multiple banks of vector registers | |

| US7254695B2 (en) | Coprocessor processing instructions in turn from multiple instruction ports coupled to respective processors | |

| US6003129A (en) | System and method for handling interrupt and exception events in an asymmetric multiprocessor architecture | |

| US7600096B2 (en) | Coprocessor extension architecture built using a novel split-instruction transaction model | |

| US5752071A (en) | Function coprocessor | |

| US5465376A (en) | Microprocessor, coprocessor and data processing system using them | |

| US5822779A (en) | Microprocessor-based data processing apparatus that commences a next overlapping cycle when a ready signal is detected not to be active | |

| EP1089167A2 (en) | Processor architecture for executing two different fixed-length instruction sets | |

| US5864689A (en) | Microprocessor configured to selectively invoke a microcode DSP function or a program subroutine in response to a target address value of branch instruction | |

| US6449712B1 (en) | Emulating execution of smaller fixed-length branch/delay slot instructions with a sequence of larger fixed-length instructions | |

| US7051146B2 (en) | Data processing systems including high performance buses and interfaces, and associated communication methods | |

| JPH07120284B2 (ja) | データ処理装置 | |

| KR100267089B1 (ko) | 스칼라/벡터연산이조합된단일명령복수데이터처리 | |

| JP2002229779A (ja) | 情報処理装置 | |

| US20060095723A1 (en) | Method and apparatus for interfacing a processor to a coprocessor | |

| JP2636074B2 (ja) | マイクロプロセッサ | |

| Marzal et al. | A N-best sentence hypotheses enumeration algorithm with duration constraints based on the two level algorithm |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20041217 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050826 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050826 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20050826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060620 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20060920 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20060926 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070123 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070216 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100223 Year of fee payment: 3 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D03 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110223 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120223 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130223 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130223 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140223 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |