JP3876401B2 - Manufacturing method of semiconductor device - Google Patents

Manufacturing method of semiconductor device Download PDFInfo

- Publication number

- JP3876401B2 JP3876401B2 JP22526699A JP22526699A JP3876401B2 JP 3876401 B2 JP3876401 B2 JP 3876401B2 JP 22526699 A JP22526699 A JP 22526699A JP 22526699 A JP22526699 A JP 22526699A JP 3876401 B2 JP3876401 B2 JP 3876401B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- silicide

- composition ratio

- thickness

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004065 semiconductor Substances 0.000 title claims description 22

- 238000004519 manufacturing process Methods 0.000 title claims description 13

- 229910021332 silicide Inorganic materials 0.000 claims description 51

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 51

- 239000000203 mixture Substances 0.000 claims description 33

- 239000002184 metal Substances 0.000 claims description 23

- 229910052751 metal Inorganic materials 0.000 claims description 23

- 238000000034 method Methods 0.000 claims description 22

- 238000010438 heat treatment Methods 0.000 claims description 17

- 238000009792 diffusion process Methods 0.000 claims description 8

- 238000000151 deposition Methods 0.000 claims description 7

- 150000002736 metal compounds Chemical class 0.000 claims description 7

- 229910052710 silicon Inorganic materials 0.000 description 16

- 238000004151 rapid thermal annealing Methods 0.000 description 13

- 229910008484 TiSi Inorganic materials 0.000 description 11

- 238000010586 diagram Methods 0.000 description 10

- 229910019001 CoSi Inorganic materials 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 239000012071 phase Substances 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000004544 sputter deposition Methods 0.000 description 7

- 230000004888 barrier function Effects 0.000 description 6

- 239000012299 nitrogen atmosphere Substances 0.000 description 6

- 239000013078 crystal Substances 0.000 description 5

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 238000002955 isolation Methods 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 239000007790 solid phase Substances 0.000 description 2

- 229910018598 Si-Co Inorganic materials 0.000 description 1

- 229910008332 Si-Ti Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910008453 Si—Co Inorganic materials 0.000 description 1

- 229910006749 Si—Ti Inorganic materials 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/665—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using self aligned silicidation, i.e. salicide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/161—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table including two or more of the elements provided for in group H01L29/16, e.g. alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66613—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation

- H01L29/66628—Lateral single gate silicon transistors with a gate recessing step, e.g. using local oxidation recessing the gate by forming single crystalline semiconductor material at the source or drain location

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は半導体装置の製造方法に関するものであり、特に、Si及びGeを含む半導体層とその上に堆積させた金属層とを熱処理することによって低抵抗の金属シリサイド電極を形成する際のSi及びGeを含む半導体層の構成に特徴のある半導体装置の製造方法に関するものである。

【0002】

【従来の技術】

近年の半導体集積回路装置の高速化に伴って、ソース・ドレイン電極及びゲート電極に金属シリサイドを用いるサリサイドプロセスが広く用いられているが、この様なサリサイドプロセスを用いたMOS型半導体集積回路装置において、高集積化に伴いゲート寸法が微細化するとソース・ドレイン領域を構成する不純物拡散領域の深さは浅くなる。

【0003】

この様な浅いソース・ドレイン領域に対してpn接合リーク電流の増加を抑制したまま低抵抗のシリサイド電極を形成するために、ソース・ドレイン領域上にシリコン層を堆積し、このシリコン層の上にシリサイド電極を形成することが試みられている。

この様なシリサイド電極の形成方法は、SOI(Silicon On Insulator)基板上に完全空乏化型のMOSFETを形成する場合にも、ソース・ドレイン領域にシリサイド電極を形成する際にも利用できる。

【0004】

最近、この様なシリコン層の代わりに、シリコン層よりの禁制帯幅の小さなSiとGeとを含む層、即ち、Si1-x Gex 層を用いることが提案されており、シリコン層よりの禁制帯幅の小さなSi1-x Gex 層を用いることによって、シリサイド層/Si1-x Gex 層界面のショットキー障壁の高さを低くして、シリサイド層/Si1-x Gex 層界面のコンタクト抵抗を減少させることが試みられているので、図6及び図7を参照してこの様なシリサイド電極の形成工程を説明する。

【0005】

まず、図6を参照して、従来のCoシリサイド電極の形成工程を説明するが、説明を簡単にするために、ソース・ドレイン領域の一部を拡大して図示する。

図6(a)参照

まず、ソース・ドレイン領域41上にCVD法を用いてSi1-x Gex 層42(例えば、Si0.5 Ge0.5 層)を堆積させたのち、スパッタ法によってCo層43を堆積させる。

【0006】

図6(b)参照

次いで、RTA(Rapid Thermal Annealing)法を用いて、例えば、450〜800℃において30〜120秒間、加熱処理することによって、Co層43とSi1-x Gex 層42とを反応させてCoシリサイド層44を形成して、ソース・ドレイン電極とする。

【0007】

次に、図7を参照して、従来のTiシリサイド電極の形成工程を説明するが、この場合も、説明を簡単にするために、ソース・ドレイン領域の一部を拡大して図示する。

図7(a)参照

まず、ソース・ドレイン領域41上にCVD法を用いてSi1-x Gex 層42(例えば、Si0.5 Ge0.5 層)を堆積させたのち、スパッタ法によってTi層45を堆積させる。

【0008】

図7(b)参照

次いで、RTA法を用いて、例えば、550〜800℃において30〜120秒間、加熱処理することによって、Ti層45とSi1-x Gex 層42とを反応させてTiシリサイド層46を形成し、次いで、未反応のTi層45を除去することによってTiSi2 からなるソース・ドレイン電極を形成する。

【0009】

【発明が解決しようとする課題】

しかし、従来のSi1-x Gex 層に対するシリサイド電極の形成方法においては、上述の加熱条件では十分なSi−金属反応が行われず、Si/金属比率の小さな高抵抗のシリサイド層が形成されたり、或いは、金属が未反応のまま残ってしまうという問題がある。

【0010】

例えば、Coシリサイドの場合には、Co層とSi1-x Gex 層とが反応する場合、CoはSiと優先的に反応するのに対して、Geはその反応を抑制するように作用するため、Geの組成比が大きい場合、上述の加熱条件では十分なSi−Co反応が行われず、抵抗の高いCoSi層が形成され、低抵抗のCoSi2 層が形成されないため、シリサイド層自体の比抵抗が大きくなり、それによって、ソース・ドレイン電極全体の抵抗が大きくなる。

【0011】

図8参照

図8は、Si1-x Gex 層上にCoシリサイド層を形成した場合のシート抵抗の配線層幅依存性を示した図であり、配線層幅依存性は殆ど見られないものの、Si層上にCoシリサイド層を形成した場合と比較すると、約20倍シート抵抗値が増加している。

【0012】

一方、Tiシリサイド層の場合にも、TiとSiとは1:2の比率でのみシリサイドを形成するので、即ち、TiSi2 のみを形成するので、上述の加熱条件では十分なSi−Ti反応が起こらず、未反応のTi層が残存し、必要な厚さのTiシリサイド層を形成することができないという問題がある。

【0013】

なお、十分な反応が行われる程度の温度及び時間で熱処理した場合には、サイドウォール上に堆積した金属層もシリサイド化して、ソース・ドレイン領域とゲート電極とがシリサイド層を介して短絡してしまうという問題が生ずる。

【0014】

また、Si1-x Gex 層を構成するGeは、上述の加熱条件では、金属と実効的に反応しないため、シリサイドを形成した領域におけるGeがシリサイドを構成しない領域に拡散して、残存するSi1-x Gex 層の混晶比xを変化させてしまうという問題がある。

【0015】

したがって、本発明は、Si及びGeを含む半導体層と金属層とを反応させて低抵抗のシリサイド層を所望の厚さに形成することを目的とする。

【0016】

【課題を解決するための手段】

図1は本発明の原理的構成の説明図であり、この図1を参照して本発明における課題を解決するための手段を説明する。

図1(a)乃至(c)参照

(1)本発明は、半導体1上に、Six (Gey C1-y )1-x 層2及びSiv (Gew C1-w )1-v 層3(但し、0<x<v<1,0<y≦1,0<w≦1)を順次堆積させたのち、Siv (Gew C1-w )1-v 層3上に金属層4を堆積させ、加熱処理により金属化合物を形成して金属シリサイド電極とする半導体装置の製造方法であって、Si v (Ge w C 1-w ) 1-v 層3におけるSi組成比vをv≧0.6、Cの組成比(1−x)(1−y)及び(1−w)(1−v)を0.05以下に設定するとともに、前記Siv (Gew C1-w )1-v 層3の厚みを、前記金属層4との反応により完全にシリサイド化される厚みに設定することを特徴とする。

【0017】

この様に、Si(GeC)層を用いて低抵抗の金属化合物層5,6、即ち、シリサイド電極を形成する場合に、金属層4側が高Si比のSi組成比の異なる二層構造にすることによって、半導体1側には任意の禁制帯幅を有するSix (Gey C1-y )1-x 層2を設けることができ、それによって金属化合物層6とSix (Gey C1-y )1-x 層2との界面のショットキー障壁を低くすることができ、且つ、金属化合物層5,6を形成する側のSiv (Gew C1-w )1-v 層3のSi比を大きくしておくことによってシリサイド化反応が阻害されることがないので、低抵抗のシリサイド電極を形成することができる。

なお、通常は、シリサイド化反応は、サイドウォール上の金属層4のシリサイド化を防止するために、図1(b)→(c)に示すように二段階反応で行う。

【0019】

また、このSiv (Gew C1-w )1-v 層3は完全にシリサイド化する必要があるので、Siv (Gew C1-w )1-v 層3の厚さは、堆積させる金属層4の膜厚により決定する。

【0020】

(2)また、本発明は、上記(1)において、加熱処理後のSi x (Ge y C 1-y ) 1-x 層2におけるGeの組成比が所定値となるように、加熱処理前のSi x (Ge y C 1-y ) 1-x 層2の組成比を、Si v (Ge w C 1-w ) 1-v 層3からのGeの拡散を見込んで予め所定値より小さく設定することを特徴とする。

【0021】

Siv (Gew C1-w )1-v 層3のシリサイド化反応の際に、化合物を形成しないGeはSix (Gey C1-y )1-x 層2側へ拡散し、Six (Gey C1-y )1-x 層2の組成比を変化させるので、この半導体1側に設けるSix (Gey C1-y )1-x 層2の組成比は、Geの拡散を考慮して最終的に得たい組成比よりGe組成比を小さくする必要があり、この場合の組成比は、堆積させる金属層4の膜厚、及び、Siv (Gew C1-w )1-v 層3の組成比及び膜厚によって決定する。

【0022】

【発明の実施の形態】

ここで、本発明の第1の実施の形態を図2及び図3を参照して説明する。

図2(a)参照

まず、n型シリコン基板11を選択酸化することによって素子分離酸化膜12を形成したのち、素子形成領域にBを導入してp型ウエル領域13を形成する。次いで、p型ウエル領域13の表面に絶縁膜を形成したのちn+ 型多結晶Si膜を堆積させ、パターニングすることによってゲート絶縁膜14及びゲート電極15を形成する。

次いで、このゲート電極15をマスクとしてAsをイオン注入することによってn型LDD(Lightly Doped Drain)領域16を形成したのち、全面にSiO2 膜を堆積させ、異方性エッチングを施すことによってサイドウォール17を形成する。

次いで、ゲート電極15及びサイドウォール17をマスクとしてAsをより高エネルギーでイオン注入することによってn+ 型ソース領域18及びn+ 型ドレイン領域19を形成することによって、nチャネル型MOSFETの基本的構成部分が完成する。

【0023】

次いで、全体を洗浄により清浄化したのち、SiH4 とGeH4 とを用いた選択CVD法によって、露出しているゲート電極15、n+ 型ソース領域18、及び、n+ 型ドレイン領域19上に、厚さが10〜60nm、例えば、30nmで、As濃度が、例えば、5×1020cm-3のSi0.53Ge0.47層20を堆積させ、引き続いて、厚さが、例えば、40nmで、As濃度が、例えば、3×1019cm-3のSi0.9 Ge0.1 層21を堆積させる。

この場合、成長ガス雰囲気中にGeが含まれているので、良好な選択成長が可能になり、素子分離酸化膜12等の絶縁膜の上には堆積しない。

なお、n+ 型ソース領域18及びn+ 型ドレイン領域19に接するSiGe層の最終的な組成比をSi0.5 Ge0.5 層にするために、Geの拡散分を見込んでSi0.53Ge0.47層20としている。

【0024】

図2(b)参照

次いで、スパッタ法を用いて、全面に、厚さが、例えば、10nmのCo層22を堆積させる。

なお、この場合のCo層22の膜厚は、必要とするシリサイド層の厚さによって決定されるものであり、このCo層22の膜厚によってSi0.9 Ge0.1 層21の厚さが決定されることになる。

【0025】

図2(c)参照

次いで、N2 雰囲気中で、400〜600℃、例えば、500℃の温度で、10〜900秒、例えば、30秒間の急速熱処理(Rapid Thermal Annealing:RTA)を施すことによって、Co層22とSi0.9 Ge0.1 層21を反応させてCoSi層23を形成する。

この場合、素子分離酸化膜12及びサイドウォール17等の絶縁膜の上に堆積したCo層22は未反応のまま未反応Co層24,25として残存する。

なお、より高温でより長時間熱処理すると、低抵抗相のCoSi2 層を形成することができるが、サイドウォール17の露出表面に堆積したCo層22もシリサイド化してゲート電極15とn+ 型ソース領域18及びn+ 型ドレイン領域19とが短絡することになるので望ましくない。

【0026】

図3(d)参照

次いで、H2 SO4 :H2 O2 =3:1の混合液で20分間エッチングを行うことによって未反応Co層24,25を除去する。

【0027】

図3(e)参照

次いで、N2 雰囲気中で、700〜900℃、例えば、800℃の温度で、10〜900秒、例えば、30秒間のRTA処理を施すことによってCoSi層23と残りのSi0.9 Ge0.1 層21を反応させて、低抵抗相のCoSi2 層26を形成する。

【0028】

このRTA工程において、Si0.9 Ge0.1 層21中のGeはCoと反応せずにSi0.53Ge0.47層20側に拡散し、Si0.53Ge0.47層20の組成比を変えてSi0.5 Ge0.5 層27となる。

したがって、n+ 型ソース領域18及びn+ 型ドレイン領域19に接する側に堆積させるSi1-x Gex 層の組成比は、Geの拡散を見込んで予めGe組成比xを小さくしておく必要があり、小さくする程度は、シリサイド化反応する側のSi1-x Gex 層の組成比及び厚さによって決定されるものであり、また、シリサイド化反応する側のSi1-x Gex 層の厚さはCo層22の厚さによって決定されるので、n+ 型ソース領域18及びn+ 型ドレイン領域19に接するSi1-x Gex 層の組成比はCo層22の厚さにも依存することになる。

【0029】

この様に、本発明の第1の実施の形態においては、n+ 型ソース領域18及びn+ 型ドレイン領域19と接するSi1-x Gex 層の最終的な組成比がSi0.5 Ge0.5 層27になるようにしているので、シリサイド層/Si1-x Gex 層界面のショットキー障壁の高さを低くすることができ、シリサイド層/Si1-x Gex 層界面のコンタクト抵抗を減少させることができる。

【0030】

また、Co層22と反応してシリサイド層を形成するSi1-x Gex 層をGe比が0.1と小さなSi0.9 Ge0.1 層21にしているので、Geによりシリサイド化反応が阻害されることがほとんどなく、低抵抗相のCoSi2 層26を形成することができるので、ソース・ドレイン電極全体を低抵抗化することができる。

【0031】

また、シリサイド化のための熱処理を2段階で行っているので、サイドウォール17上に堆積したCo層がシリサイド化することなく、Co層のエッチング工程で除去されるので、n+ 型ソース領域18及びn+ 型ドレイン領域19とゲート電極15とがシリサイド層を介して短絡することがない。

【0032】

次に、図4及び図5を参照して、本発明の第2の実施の形態を説明する。

図4(a)参照

まず、上記の第1の実施の形態と同様にnチャネル型MOSFETの基本的構成部分を形成したのち、全体を洗浄により清浄化し、次いで、SiH4 とGeH4 とを用いた選択CVD法によって、露出しているゲート電極15、n+ 型ソース領域18、及び、n+ 型ドレイン領域19上に、厚さが10〜60nm、例えば、30nmで、As濃度が、例えば、5×1020cm-3のSi0.53Ge0.47層20を堆積させ、引き続いて、厚さが、例えば、51nmで、As濃度が、例えば、3×1019cm-3のSi0.9 Ge0.1 層21を堆積させる。

【0033】

図4(b)参照

次いで、スパッタ法を用いて、全面に、厚さが、例えば、30nmのTi層28を堆積させる。

なお、この場合のTi層28の膜厚も、必要とするシリサイド層の厚さによって決定されるものであり、このTi層28の膜厚によってSi0.9 Ge0.1 層21の厚さが決定されることになる。

【0034】

図4(c)参照

次いで、N2 雰囲気中で、650〜750℃、例えば、700℃の温度で、10〜900秒、例えば、30秒間の急速熱処理(Rapid Thermal Annealing:RTA)を施すことによって、Ti層28の表面にTiN層30を形成するとともに、Ti層28とSi0.9 Ge0.1 層21を反応させて準安定な低温相の結晶であるC−49からなるTiSi2 層29を形成する。

この場合、熱処理をN2 雰囲気中で行ってTiN層30を形成することによって、サイドウォール17の露出表面に堆積したTi層28のシリサイド化反応が抑制されるので、ゲート電極15とn+ 型ソース領域18及びn+ 型ドレイン領域19とが短絡することを防止することができる。

なお、この場合も絶縁膜上のTi層28は、未反応Ti層31,33のままでであるとともに、TiSi2 層29上にも未反応Ti層32が残存する場合がある。

【0035】

図5(d)参照

次いで、H2 SO4 :H2 O2 =3:1の混合液をエッチング液として用いてTiN膜30及び未反応Ti層31,33を除去する。

なお、TiSi2 層29上にも未反応Ti層32の多少残存している場合には、未反応Ti層31,33の除去工程において同時に除去されることになる。

【0036】

図5(e)参照

次いで、Ar雰囲気中で、750〜900℃、例えば、800℃の温度で、10〜600秒、例えば、30秒間の急速熱処理(Rapid Thermal Annealing:RTA)を施すことによって、低温相のC−49からなるTiSi2 層29を、安定で低抵抗な高温相のC−54からなるTiSi2 層34に変換することによってシリサイド電極が完成する。

【0037】

この場合も、RTA工程において、Si0.9 Ge0.1 層21中のGeはTiと反応せずにSi0.53Ge0.47層20側に拡散し、Si0.53Ge0.47層20の組成比を変えてSi0.5 Ge0.5 層27となる。

したがって、n+ 型ソース領域18及びn+ 型ドレイン領域19に接する様に堆積させるSi1-x Gex 層の組成比は、シリサイド化反応する側のSi1-x Gex 層の組成比及び厚さ、及び、Ti層28の厚さに依存することになる。

【0038】

この様に、本発明の第2の実施の形態においては、n+ 型ソース領域18及びn+ 型ドレイン領域19と接するSi1-x Gex 層の最終的な組成比がSi0.5 Ge0.5 層27になるようにしているので、シリサイド層/Si1-x Gex 層界面のショットキー障壁の高さを低くして、シリサイド層/Si1-x Gex 層界面のコンタクト抵抗を減少させることができる。

【0039】

また、Ti層28と反応してシリサイド層を形成するSi1-x Gex 層をGe比が0.1と小さなSi0.9 Ge0.1 層21にしているので、Geによりシリサイド化反応が阻害されることがほとんどなく、充分な厚さのTiSi2 層29、したがって、充分な厚さのTiSi2 層34を形成することができるので、ソース・ドレイン電極全体を低抵抗化することができる。

【0040】

以上、本発明の各実施の形態を説明してきたが、本発明は、各実施の形態に記載した構成及び条件に限られるものではなく、各種の変更が可能である。

例えば、上記の各実施の形態の説明においては、格子整合及びショットキー障壁の高さの低減を考慮してソース・ドレイン領域に接するSi1-x Gex 層の最終的な組成がSi0.5 Ge0.5 になるように設定しているが、必ずしもSi0.5 Ge0.5 である必要はなく、組成比は任意であり、xが大きくなると格子不整合が大きくなるのでエピタキシャル成長が困難になり多結晶になる可能性が高くなり、一方、xが小さくなると格子整合はとれるがショットキー障壁の高さが高くなる。

【0041】

また、上記の各実施の形態においては、シリサイド化させるSi1-x Gex 層の組成をSi0.9 Ge0.1 としているが、必ずしもSi0.9 Ge0.1 である必要はなく、ソース・ドレイン領域に接するSi1-x Gex 層よりSiリッチな層であれば良く、Si(x=0)であっても良いが、Siの場合には選択成長が困難になる。

但し、必要とするシリサイド層の厚さを考慮すると、x≦0.4、即ち、Si/Ge≧1.5とすることが望ましい。

【0042】

また、上記の各実施の形態においては、Si及びGeを含む層をSi1-x Gex として構成しているが、Cを加えてSix (Gey C1-y )1-x 層としても良いものである。

即ち、原子半径の小さなCを加えることによってGeの原子半径の大きさを相殺することができ、それによって、ソース・ドレイン領域を構成するSiと格子整合させることができるので、Ge組成比yの自由度を高めることができる。

なお、Cの組成比(1−y)(1−x)は、0.05(5.0%)程度以下であり、禁制帯幅はCの混入によって寧ろ低減するので、ショットキー障壁の高さが高くなることはない。

【0043】

また、上記の各実施の形態においては、Si1-x Gex 層を格子整合が可能なように選択して、単結晶が成長するようにしているが、必ずしも単結晶である必要はなく、多結晶でも良いし、非晶質でも良く、さらには、多結晶と非晶質とが混在した状態の膜でも良い。

但し、低抵抗化の面では、単結晶の方が望ましい。

【0044】

また、上記の各実施の形態においては、Si1-x Gex 層をCVD法を用いて選択成長させているが、必ずしもCVD法である必要はなく、スパッタ法或いは蒸着法を用いても良いものである。

さらには、Si層を堆積させたのちGeをイオン注入してSi1-x Gex 層を形成しても良いし、逆に、Ge層を堆積させたのちSiをイオン注入してSi1-x Gex 層を形成しても良い。

【0045】

また、上記の各実施の形態の説明においては、シリサイド化させる金属層として低抵抗なシリサイド層の得られるCo層或いはTi層を用いているが、Co或いはTiに限られるものではなく、Ni,Pt,W等を用いても良いものである。

但し、Niシリサイドは中温で形成されたシリサイドが低抵抗ではあるが不安定であるので、低抵抗相のシリサイド形成後に高温工程がともなった場合、高抵抗のシリサイドに変化するので、熱工程の管理に注意を要する。

また、Wシリサイドは熱的に安定であるが、比較的抵抗が高く、また、Ptはこれらの中間の特性を示す。

【0046】

また、上記の各実施の形態の説明においては、シリサイド化させる金属層をスパッタ法によって形成しているが、必ずしもスパッタ法である必要はなく、用いる金属の融点及び蒸気圧等に応じて、抵抗加熱による蒸着法、電子ビーム蒸着法、或いは、CVD法等を用いても良いものである。

【0047】

また、上記の第1の実施の形態においては、2度のRTA工程をN2 雰囲気中で行っているが、必ずしもN2 雰囲気である必要はなく、Ar等の他の不活性ガスを用いても良いものである。

【0048】

また、上記の各実施の形態においては、nチャネル型MOSFETとして説明しているが、pチャネル型MOSFETにも当然に適用されるのものであり、その場合には、各Si1-x Gex 層に不純物としてB等のp型不純物をドープすれば良い。

【0049】

また、上記の各実施の形態においては、ソース・ドレイン電極及びゲート電極に対するコンタクト電極として説明しているが、必ずしも、MOS型半導体装置のコンタクト電極に限られるものではなく、バイポーラ型半導体素子のエミッタ電極,ベース電極,コレクタ電極を始めとする各種の半導体素子のコンタクト電極としても用いることができるものである。

【0050】

さらには、必ずしもコンタクト電極に限られるものではなく、ゲート電極自体としても良いものである。

その場合には、ゲート絶縁膜と接する側のSi1-x Gex 層を堆積させ、ゲート電極としてパターニングしたのち、シリサイド化させるSi1-y Gey 層(x>y)を選択成長させれば良い。

但し、シリサイド化に伴うGeの固相拡散によりゲート電極の組成比が変化し、それに伴ってしきい値電圧Vthも変化するので、この様なGeの固相拡散量を見込んで、ゲート絶縁膜と接するSi1-x Gex 層の組成比を制御する必要がある。

【0051】

【発明の効果】

本発明によれば、ソース・ドレイン領域等の半導体領域にシリサイドコンタクト電極を形成する際に、組成比の異なる2層構造のSi1-x Gex 層を用い、低抵抗相のシリサイド層を形成するためのシリサイド化反応の促進と、ショットキーバリアハイトの低減とを両立させているので、製造時間の増加や電極間の短絡を発生させることなしに低抵抗のコンタクト電極を形成することができ、延いては、高集積度半導体装置の高性能化及び製造歩留りの向上に寄与するところが大きい。

【図面の簡単な説明】

【図1】本発明の原理的構成の説明図である。

【図2】本発明の第1の実施の形態の途中までの製造工程の説明図である。

【図3】本発明の第1の実施の形態の図2以降の製造工程の説明図である。

【図4】本発明の第2の実施の形態の途中までの製造工程の説明図である。

【図5】本発明の第2の実施の形態の図4以降の製造工程の説明図である。

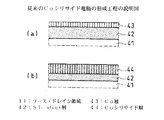

【図6】従来のCoシリサイド電極の形成工程の説明図である。

【図7】従来のTiシリサイド電極の形成工程の説明図である。

【図8】従来のシリサイド電極形成工程における問題点の説明図である。

【符号の説明】

1 半導体

2 Six (Gey C1-y )1-x 層

3 Siv (Gew C1-w )1-v 層

4 金属層

5 金属化合物層

6 金属化合物層

11 n型シリコン基板

12 素子分離酸化膜

13 p型ウエル領域

14 ゲート絶縁膜

15 ゲート電極

16 n型LDD領域

17 サイドウォール

18 n+ 型ソース領域

19 n+ 型ドレイン領域

20 Si0.53Ge0.47層

21 Si0.9 Ge0.1 層

22 Co層

23 CoSi層

24 未反応Co層

25 未反応Co層

26 CoSi2 層

27 Si0.5 Ge0.5 層

28 Ti層

29 TiSi2 層

30 TiN層

31 未反応Ti層

32 未反応Ti層

33 未反応Ti層

34 TiSi2 層[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a method for manufacturing a semiconductor device, and in particular, Si and Ge in forming a low-resistance metal silicide electrode by heat-treating a semiconductor layer containing Si and Ge and a metal layer deposited thereon. The present invention relates to a method for manufacturing a semiconductor device characterized by the structure of a semiconductor layer containing Ge.

[0002]

[Prior art]

With the recent increase in the speed of semiconductor integrated circuit devices, salicide processes using metal silicide for source / drain electrodes and gate electrodes are widely used. In MOS type semiconductor integrated circuit devices using such salicide processes, When the gate dimension is reduced with the increase in integration, the depth of the impurity diffusion region constituting the source / drain region becomes shallower.

[0003]

In order to form a low-resistance silicide electrode while suppressing an increase in the pn junction leakage current with respect to such a shallow source / drain region, a silicon layer is deposited on the source / drain region, and the silicon layer is formed on the silicon layer. Attempts have been made to form silicide electrodes.

Such a method for forming a silicide electrode can be used for forming a fully depleted MOSFET on an SOI (Silicon On Insulator) substrate as well as for forming a silicide electrode in a source / drain region.

[0004]

Recently, instead of such a silicon layer, it has been proposed to use a layer containing Si and Ge having a smaller forbidden band width than the silicon layer, that is, a Si 1-x Ge x layer. by using the Si 1-x Ge x layer having a small band gap, the height of the silicide layer / Si 1-x Ge x layer interface of the Schottky barrier is lowered, the silicide layer / Si 1-x Ge x layer Since attempts have been made to reduce the contact resistance at the interface, the process of forming such a silicide electrode will be described with reference to FIGS.

[0005]

First, a conventional process for forming a Co silicide electrode will be described with reference to FIG. 6. In order to simplify the description, a part of the source / drain region is enlarged and illustrated.

6A. First, after depositing a Si 1-x Ge x layer 42 (for example, Si 0.5 Ge 0.5 layer) on the source /

[0006]

FIG 6 (b) refer then used RTA (Rapid Thermal Annealing) method, for example, 30 to 120 seconds at 450 to 800 ° C., by heating treatment, a

[0007]

Next, a conventional Ti silicide electrode forming process will be described with reference to FIG. 7. In this case as well, in order to simplify the description, a part of the source / drain region is shown enlarged.

7A. First, a Si 1-x Ge x layer 42 (for example, Si 0.5 Ge 0.5 layer) is deposited on the source /

[0008]

Next, referring to FIG. 7B, the

[0009]

[Problems to be solved by the invention]

However, in the conventional method of forming a silicide electrode for a Si 1-x Ge x layer, a sufficient Si-metal reaction is not performed under the above heating conditions, and a high-resistance silicide layer with a small Si / metal ratio is formed. Alternatively, there is a problem that the metal remains unreacted.

[0010]

For example, in the case of Co silicide, when the Co layer reacts with the Si 1-x Ge x layer, Co reacts preferentially with Si, whereas Ge acts to suppress the reaction. Therefore, when the composition ratio of Ge is large, a sufficient Si—Co reaction is not performed under the above heating conditions, a CoSi layer having a high resistance is formed, and a low resistance CoSi 2 layer is not formed. The resistance is increased, thereby increasing the resistance of the entire source / drain electrode.

[0011]

FIG. 8 is a diagram showing the dependence of the sheet resistance on the wiring layer width when the Co silicide layer is formed on the Si 1-x Ge x layer, although the wiring layer width dependence is hardly seen. Compared with the case where the Co silicide layer is formed on the Si layer, the sheet resistance value is increased by about 20 times.

[0012]

On the other hand, even in the case of the Ti silicide layer, since Ti and Si form silicide only at a ratio of 1: 2, that is, only TiSi 2 is formed, a sufficient Si—Ti reaction can be achieved under the above heating conditions. There is a problem that an unreacted Ti layer remains, and a Ti silicide layer having a required thickness cannot be formed.

[0013]

In addition, when heat treatment is performed at a temperature and time sufficient for sufficient reaction, the metal layer deposited on the sidewall is also silicided, and the source / drain region and the gate electrode are short-circuited through the silicide layer. Problem arises.

[0014]

Further, Ge constituting the Si 1-x Ge x layer does not effectively react with the metal under the above-described heating conditions, and therefore, the Ge in the region where the silicide is formed diffuses into the region where the silicide is not formed and remains. There is a problem that the mixed crystal ratio x of the Si 1-x Ge x layer is changed.

[0015]

Accordingly, an object of the present invention is to form a low-resistance silicide layer with a desired thickness by reacting a semiconductor layer containing Si and Ge with a metal layer.

[0016]

[Means for Solving the Problems]

FIG. 1 is an explanatory diagram of the principle configuration of the present invention. Means for solving the problems in the present invention will be described with reference to FIG.

1A to 1C. (1) In the present invention, an Si x (Ge y C 1-y ) 1-x

[0017]

In this way, when forming the low resistance

Normally, the silicidation reaction is performed in a two-stage reaction as shown in FIGS. 1B to 1C in order to prevent silicidation of the

[0019]

Further, since the Si v (Ge w C 1-w ) 1-v

[0020]

( 2 ) Further, in the above (1) , the present invention provides that the composition ratio of Ge in the Si x (Ge y C 1-y ) 1-x

[0021]

In the silicidation reaction of the Si v (Ge w C 1-w ) 1-v

[0022]

DETAILED DESCRIPTION OF THE INVENTION

Here, a first embodiment of the present invention will be described with reference to FIGS.

2A. First, an n-

Next, an n-type LDD (Lightly Doped Drain)

Next, the n + -

[0023]

Next, the whole is cleaned by cleaning, and then exposed on the exposed

In this case, since Ge is contained in the growth gas atmosphere, good selective growth is possible, and it is not deposited on the insulating film such as the element

In order to make the final composition ratio of the SiGe layer in contact with the n + -

[0024]

Next, referring to FIG. 2B, a

In this case, the thickness of the

[0025]

Next, by performing rapid thermal annealing (RTA) in a N 2 atmosphere at a temperature of 400 to 600 ° C., for example, 500 ° C., for 10 to 900 seconds, for example, 30 seconds. Then, the

In this case, the

If a heat treatment is performed at a higher temperature for a longer time, a CoSi 2 layer having a low resistance phase can be formed. However, the

[0026]

Next, referring to FIG. 3D, unreacted Co layers 24 and 25 are removed by etching for 20 minutes with a mixed solution of H 2 SO 4 : H 2 O 2 = 3: 1.

[0027]

Next, refer to FIG. 3 (e). Then, in the N 2 atmosphere, the RTA treatment is performed at a temperature of 700 to 900 ° C., for example, 800 ° C., for 10 to 900 seconds, for example, 30 seconds, thereby performing the

[0028]

In this RTA process, Si 0.9 Ge Ge in 0.1-layer 21 is diffused into the Si 0.53 Ge 0.47 layer 20 side without reacting with Co, Si 0.53 Ge 0.47 layer 20 Si 0.5 Ge 0.5 layer by changing the composition ratio of 27 It becomes.

Therefore, the composition ratio of the Si 1-x Ge x layer deposited on the side in contact with the n + -

[0029]

Thus, in the first embodiment of the present invention, the final composition ratio of the Si 1-x Ge x layer in contact with the n +

[0030]

In addition, since the Si 1-x Ge x layer that reacts with the

[0031]

Further, since the heat treatment for silicidation in two stages, without Co layer deposited on the

[0032]

Next, a second embodiment of the present invention will be described with reference to FIGS.

Referring to FIG. 4A, first, the basic components of the n-channel MOSFET are formed in the same manner as in the first embodiment, and then the whole is cleaned by cleaning, and then SiH 4 and GeH 4 are used. On the exposed

[0033]

Next, referring to FIG. 4B, a

In this case, the thickness of the

[0034]

Next, by performing rapid thermal annealing (RTA) in a N 2 atmosphere at a temperature of 650 to 750 ° C., for example, 700 ° C., for 10 to 900 seconds, for example, 30 seconds. The

In this case, the silicidation reaction of the

In this case as well, the

[0035]

Next, referring to FIG. 5D, the

If some of the

[0036]

Next, referring to FIG. 5 (e), rapid thermal annealing (RTA) is performed in an Ar atmosphere at a temperature of 750 to 900 ° C., for example, 800 ° C., for 10 to 600 seconds, for example, 30 seconds. The silicide electrode is completed by converting the TiSi 2 layer 29 made of C-49 in the low temperature phase into the TiSi 2 layer 34 made of C-54 in the stable and low resistance high temperature phase.

[0037]

Again, in the RTA process, Si 0.9 Ge Ge in 0.1-layer 21 is diffused into the Si 0.53 Ge 0.47 layer 20 side without reacting with Ti, Si 0.53 Ge Si 0.5 by changing the composition ratio of 0.47

Therefore, the composition ratio of the Si 1-x Ge x layer deposited so as to be in contact with the n + -

[0038]

Thus, in the second embodiment of the present invention, the final composition ratio of the Si 1-x Ge x layer in contact with the n +

[0039]

In addition, since the Si 1-x Ge x layer that reacts with the

[0040]

Although the embodiments of the present invention have been described above, the present invention is not limited to the configurations and conditions described in the embodiments, and various modifications can be made.

For example, in the description of each of the above embodiments, the final composition of the Si 1-x Ge x layer in contact with the source / drain regions is Si 0.5 Ge in consideration of lattice matching and reduction in the height of the Schottky barrier. Although it is set to be 0.5 , it is not necessarily Si 0.5 Ge 0.5 , the composition ratio is arbitrary, and the lattice mismatch becomes larger as x becomes larger, so that epitaxial growth becomes difficult and it may become polycrystalline. On the other hand, when x becomes small, lattice matching can be obtained, but the height of the Schottky barrier becomes high.

[0041]

In each of the above embodiments, the composition of the Si 1-x Ge x layer to be silicided is Si 0.9 Ge 0.1 , but it is not necessarily Si 0.9 Ge 0.1 , and it is not necessarily Si 0.9 Ge 0.1. Any Si-rich layer than the 1-x Ge x layer may be used, and Si (x = 0) may be used. However, in the case of Si, selective growth becomes difficult.

However, considering the required thickness of the silicide layer, it is desirable that x ≦ 0.4, that is, Si / Ge ≧ 1.5.

[0042]

Further, in each of the above embodiments, the layer containing Si and Ge is configured as Si 1-x Ge x , but C is added to form a Si x (Ge y C 1-y ) 1-x layer. Is also good.

That is, by adding C having a small atomic radius, the size of the atomic radius of Ge can be offset, and thereby lattice matching with Si constituting the source / drain region can be achieved. The degree of freedom can be increased.

Note that the composition ratio (1-y) (1-x) of C is about 0.05 (5.0%) or less, and the forbidden band width is rather reduced by the inclusion of C. Will not be high.

[0043]

Further, in each of the above embodiments, the Si 1-x Ge x layer is selected so that lattice matching is possible, and a single crystal is grown, but it is not necessarily a single crystal, It may be polycrystalline, amorphous, or a film in which polycrystalline and amorphous are mixed.

However, in terms of lowering resistance, a single crystal is preferable.

[0044]

In each of the above embodiments, the Si 1-x Ge x layer is selectively grown using the CVD method. However, the CVD method is not necessarily used, and a sputtering method or a vapor deposition method may be used. Is.

Furthermore, after depositing the Si layer, Ge may be ion-implanted to form the Si 1-x Ge x layer. Conversely, after depositing the Ge layer, Si is ion-implanted to form Si 1- An x Ge x layer may be formed.

[0045]

In the description of each of the above embodiments, a Co layer or a Ti layer from which a low-resistance silicide layer is obtained is used as a metal layer to be silicided, but is not limited to Co or Ti. Pt, W, etc. may be used.

However, since Ni silicide is a low-resistance silicide that is formed at a medium temperature but is unstable, if it is accompanied by a high-temperature process after the formation of a low-resistance phase silicide, it changes to a high-resistance silicide. Attention is required.

W silicide is thermally stable, but has a relatively high resistance, and Pt exhibits intermediate characteristics.

[0046]

In the description of each of the above embodiments, the metal layer to be silicided is formed by the sputtering method. However, the sputtering is not necessarily performed, and the resistance is changed depending on the melting point, vapor pressure, etc. of the metal used. A vapor deposition method by heating, an electron beam vapor deposition method, a CVD method, or the like may be used.

[0047]

In the first embodiment, the two RTA processes are performed in the N 2 atmosphere. However, the N 2 atmosphere is not necessarily used, and other inert gas such as Ar is used. Is also good.

[0048]

In each of the above-described embodiments, the n-channel MOSFET is described. However, the present invention is naturally applied to a p-channel MOSFET. In this case, each Si 1-x Ge x is applied. The layer may be doped with a p-type impurity such as B as an impurity.

[0049]

In each of the above embodiments, the contact electrode for the source / drain electrode and the gate electrode is described. However, the contact electrode is not necessarily limited to the contact electrode of the MOS type semiconductor device, but the emitter of the bipolar type semiconductor element. It can also be used as a contact electrode for various semiconductor elements including an electrode, a base electrode, and a collector electrode.

[0050]

Furthermore, it is not necessarily limited to the contact electrode, but may be the gate electrode itself.

In that case, after depositing a Si 1-x Ge x layer on the side in contact with the gate insulating film and patterning it as a gate electrode, a Si 1-y Ge y layer (x> y) to be silicided can be selectively grown. It ’s fine.

However, the composition ratio of the gate electrode changes due to the solid phase diffusion of Ge accompanying silicidation, and the threshold voltage V th also changes accordingly. Therefore, in consideration of such a solid phase diffusion amount of Ge, gate insulation It is necessary to control the composition ratio of the Si 1-x Ge x layer in contact with the film.

[0051]

【The invention's effect】

According to the present invention, when a silicide contact electrode is formed in a semiconductor region such as a source / drain region, a low resistance phase silicide layer is formed by using a Si 1-x Ge x layer having a different composition ratio. Therefore, it is possible to form a low-resistance contact electrode without increasing the manufacturing time and causing a short circuit between the electrodes. As a result, it greatly contributes to improving the performance and manufacturing yield of highly integrated semiconductor devices.

[Brief description of the drawings]

FIG. 1 is an explanatory diagram of a basic configuration of the present invention.

FIG. 2 is an explanatory diagram of the manufacturing process up to the middle of the first embodiment of the present invention.

FIG. 3 is an explanatory diagram of the manufacturing process from FIG. 2 onward according to the first embodiment of the present invention.

FIG. 4 is an explanatory diagram of the manufacturing process up to the middle of the second embodiment of the present invention.

FIG. 5 is an explanatory diagram of the manufacturing process after FIG. 4 according to the second embodiment of the present invention.

FIG. 6 is an explanatory diagram of a conventional process for forming a Co silicide electrode.

FIG. 7 is an explanatory diagram of a conventional Ti silicide electrode forming process.

FIG. 8 is an explanatory diagram of a problem in a conventional silicide electrode formation process.

[Explanation of symbols]

1 semiconductor 2 Si x (Ge y C 1 -y) 1-x layer 3 Si v (Ge w C 1 -w) 1-

Claims (2)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22526699A JP3876401B2 (en) | 1999-08-09 | 1999-08-09 | Manufacturing method of semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22526699A JP3876401B2 (en) | 1999-08-09 | 1999-08-09 | Manufacturing method of semiconductor device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001053027A JP2001053027A (en) | 2001-02-23 |

| JP2001053027A5 JP2001053027A5 (en) | 2005-06-16 |

| JP3876401B2 true JP3876401B2 (en) | 2007-01-31 |

Family

ID=16826637

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP22526699A Expired - Lifetime JP3876401B2 (en) | 1999-08-09 | 1999-08-09 | Manufacturing method of semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3876401B2 (en) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100446300B1 (en) | 2002-05-30 | 2004-08-30 | 삼성전자주식회사 | Method for forming metal interconnections of semiconductor device |

| JP2004172541A (en) | 2002-11-22 | 2004-06-17 | Renesas Technology Corp | Manufacturing method for semiconductor device |

| US6891192B2 (en) * | 2003-08-04 | 2005-05-10 | International Business Machines Corporation | Structure and method of making strained semiconductor CMOS transistors having lattice-mismatched semiconductor regions underlying source and drain regions |

| US20050253205A1 (en) * | 2004-05-17 | 2005-11-17 | Fujitsu Limited | Semiconductor device and method for fabricating the same |

| JP2006351581A (en) * | 2005-06-13 | 2006-12-28 | Fujitsu Ltd | Manufacturing method of semiconductor device |

| US20070238236A1 (en) * | 2006-03-28 | 2007-10-11 | Cook Ted Jr | Structure and fabrication method of a selectively deposited capping layer on an epitaxially grown source drain |

| US7544997B2 (en) * | 2007-02-16 | 2009-06-09 | Freescale Semiconductor, Inc. | Multi-layer source/drain stressor |

| JP2009043916A (en) | 2007-08-08 | 2009-02-26 | Toshiba Corp | Semiconductor device and manufacturing method thereof |

| JP2009123960A (en) * | 2007-11-15 | 2009-06-04 | Toshiba Corp | Semiconductor device |

-

1999

- 1999-08-09 JP JP22526699A patent/JP3876401B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001053027A (en) | 2001-02-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2978736B2 (en) | Method for manufacturing semiconductor device | |

| US6806534B2 (en) | Damascene method for improved MOS transistor | |

| JP2630290B2 (en) | Method for manufacturing semiconductor device | |

| JP3209164B2 (en) | Method for manufacturing semiconductor device | |

| JPH11111980A (en) | Semiconductor device and its manufacture | |

| JP2008004776A (en) | Semiconductor device and its manufacturing method | |

| JPH10284728A (en) | Manufacture of mosfet having cobalt silicide film | |

| JP2925008B2 (en) | Method for manufacturing semiconductor device | |

| JP2010109122A (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP3876401B2 (en) | Manufacturing method of semiconductor device | |

| JP2009164200A (en) | Semiconductor device and manufacturing method thereof | |

| JP3496723B2 (en) | Method for manufacturing semiconductor device | |

| JPH05315286A (en) | Electrode section of semiconductor device and its formation | |

| JP3948290B2 (en) | Manufacturing method of semiconductor device | |

| JPH09283462A (en) | Semiconductor device and manufacture thereof | |

| JPH10313117A (en) | Mis transistor and manufacture thereof | |

| JP3581253B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2014036213A (en) | Semiconductor device and method for manufacturing the same | |

| JPH09219516A (en) | N-channel mos semiconductor element and manufacture semiconductor element | |

| JP2008085306A (en) | Semiconductor device, and method for manufacturing the same | |

| KR100264209B1 (en) | Method for fabricating semiconductor device | |

| JP3918218B2 (en) | Manufacturing method of semiconductor device | |

| JPH10229052A (en) | Semiconductor integrated circuit device and manufacture thereof | |

| KR100620235B1 (en) | Method for manufacturing Ti-silicide | |

| JPH10116797A (en) | Manufacture of semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040917 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040917 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20051228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060110 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060725 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060922 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061017 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061019 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3876401 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091110 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101110 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101110 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111110 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111110 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111110 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111110 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121110 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121110 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131110 Year of fee payment: 7 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |