JP3764074B2 - 電子機器の製造方法および加工システム - Google Patents

電子機器の製造方法および加工システム Download PDFInfo

- Publication number

- JP3764074B2 JP3764074B2 JP2001236547A JP2001236547A JP3764074B2 JP 3764074 B2 JP3764074 B2 JP 3764074B2 JP 2001236547 A JP2001236547 A JP 2001236547A JP 2001236547 A JP2001236547 A JP 2001236547A JP 3764074 B2 JP3764074 B2 JP 3764074B2

- Authority

- JP

- Japan

- Prior art keywords

- hole

- electronic component

- wire

- width

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/58—Structural electrical arrangements for semiconductor devices not otherwise provided for

- H01L2223/64—Impedance arrangements

- H01L2223/66—High-frequency adaptations

- H01L2223/6605—High-frequency electrical connections

- H01L2223/6611—Wire connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48472—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area also being a wedge bond, i.e. wedge-to-wedge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49111—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting two common bonding areas, e.g. Litz or braid wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01039—Yttrium [Y]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16152—Cap comprising a cavity for hosting the device, e.g. U-shaped cap

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Wire Bonding (AREA)

Description

【発明の属する技術分野】

本発明は、ミリ波モジュール等の電子機器の組立て部品となる電子部品の加工技術に関する。

【0002】

【従来の技術】

ボンディングの際の位置合わせ技術として、特開平10−50760号公報記載の技術が知られている。この技術は、インナーリードと電極とを位置合わせに先立ち、インナーリードおよび電極について、それぞれ、予め入力された設計座標値とカメラを利用した実測座標値との照合を行うものである。このような照合を位置合わせ前に実行することによって、インナーリード変形等のTABテープに起因する位置ずれの未然防止を図っている。

【0003】

【発明が解決しようとする課題】

ところが、上記従来の技術は、インナーリードの設計座標値と実測座標値との差が許容範囲を超えた場合、そのインナーリードの代わりに他のインナーリードをボンディングに使用する。すなわち、所定の条件を満たさないインナーリードがあれば、それを、半導体チップの電極のボンディング対象から除外することによって、半導体装置の品質向上を図っている。このため、インナーリードの形状にバラツキがあることを考慮すると、インナーリードを、無駄なく製品に利用することは困難である。

【0004】

そこで、本発明は、形状にバラツキのある電子部品が組立て部品に含まれていても、信頼性の高い電子装置を製造可能とすることを目的とする。

【0005】

【課題を解決するための手段】

上記課題を解決するため、本発明の一態様に係る電子機器おいては、第一の電子部品に形成する孔の幅の寸法値が、この孔に挿入される第二の電子部品の幅の寸法の測定値に基づき定められることとした。

【0006】

【発明の実施の形態】

以下、添付の図面を参照しながら、本発明に係る実施の一形態について説明する。

【0007】

まず、本実施の形態において製造対象とするミリ波レーダについて説明しておく。なお、ここでは、車両搭載用のミリ波レーダを一例に挙げることとする。

【0008】

図1に示すように、車両搭載用のミリ波レーダ100は、その搭載車両200の前方に向けて電波Zを送波し、先行車両300からのエコーZ'を受波することによって、先行車両300までの車間距離D等を検出するものである。このミリ波レーダ100のRFフロントエンド部には、高周波の増幅等を行うRFモジュールが含まれている。

【0009】

このRFモジュールは、図2に示すように、複数の貫通孔11が所定の位置に開けられた金属板10、金属板10の一方の面(内側面と呼ぶ)の周縁部にろう付け等された金属製キャップ15、金属板10と金属製キャップ15とにより気密封止された電子部品群、金属板10の貫通孔11に充填されたガラス12でその貫通孔11に固定された複数の外部端子(充電端子50、2本の出力端子51)を有している。なお、金属板10と金属製キャップ15とによって形成された室16には不活性ガスが充填されている。

【0010】

ここで、電子部品群には、各出力端子51に接続された2つの配線パターン(銅パターン等)21が一方の面(以下、表面と呼ぶ)に形成された基板20、2つの電極パッド(不図示)が上面に設けられた複数のチップコンデンサ40、複数の電極パッド(コンデンサ用電極パッド31、出力用電極パッド32)が上面に設けられたICチップ30、チップコンデンサ40の2つの電極パッドをICチップ30のコンデンサ用電極パッド31および充電端子50に接続したワイヤ71、基板20の各配線パターン21をICチップ30の出力用電極パッド32に接続したワイヤ70、が含まれている。これらは、以下の状態で、金属板10と金属製キャップ15とにより形成された室16内部に収納されている。

【0011】

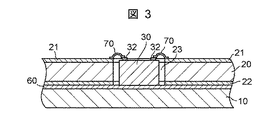

基板20の他方の面(以下、裏面と呼ぶ)には、図3に示すように、その全領域を覆う導体膜(銅膜等)22が形成されている。そして、この導体膜22が導電性接着剤60で金属板10の内側面に貼り合わせられている。また、基板20の2つの電極パターン21の間には、それらの電極パターン21に縁が接した長方形の貫通孔(以下、角形貫通孔と呼ぶ)23が開けられており、この貫通孔23から露出した金属板10の内側面に、ICチップ30の裏面(上面の反対側の面)が接着されている。ここで、ICチップ30は、出力用電極パッド32と基板20の配線パターン21との間隔を最短にする向きに配置されている。そして、ICチップ30の各出力用電極パッド32は、自身に近い側の配線パターン21とワイヤ70で接続されている。なお、基板20には、各配線パターン21に出力端子50を接続すべく、各出力端子50の端部を基板表面側に露出させるための円形の貫通孔25が開けられている。

【0012】

さらに、基板20の矩形貫通孔23から露出した金属板10の内側面には、各チップコンデンサ40の裏面(上面の反対側の面)が接着されている。ここで、各チップコンデンサ40は、ICチップ30のコンデンサ用電極パッド31に対応する位置に配置されている。そして、各チップコンデンサ40の一方の電極パッドは、自身に最も近い位置にあるコンデンサ用電極パッド31にワイヤ71で接続されている。また、基板20には、図1に示したように、各チップコンデンサ40の位置に対応付けて、充電端子50の端部を基板表面側に露出させるための円形貫通孔24が開けられている。そして、各チップコンデンサ40の他方の電極パッドは、自身に最も近い位置にある充電端子50にワイヤ71で接続されている。

【0013】

このような構成において、ICチップ30の出力用電極パッド32と基板20の電極パターン23とをつなぐワイヤ70が長くなると、信号の伝送損失が増加する。このため、図4に示した、ICチップ30の出力用電極パッド32と基板20の配線パターン21との間隔L1,L2、すなわち、基板20の角形貫通孔24の内壁とICチップ30との間隔L1,L2を規定値以下に抑える必要がある。ところが、ICチップ30の形状寸法にはバラツキがあるため、角形貫通孔24の内壁とICチップ30との間隔L1,L2にバラツキが生じやすい。そこで、本実施の形態では、基板20の角形貫通孔24の内壁とICチップ30との間隔L1,L2のバラツキを抑制すべく、以下の製造方法によってRFモジュールを製造することとした。

【0014】

まず、図5(A)に示すように、裏面が導体膜22で覆われた基板20の表面に、Y方向に一列に並ぶ2つの配線パターン21を形成する。なお、次工程における角形貫通孔23の形成によって、2つの配線パターン21の対向側端部が基板20とともに削りとられるように、ここでは、ICチップ30の設計寸法よりも適当な値だけ小さな寸法S1の間隔が、2つの配線パターン21の間にあくようにする。

【0015】

このように2つの配線パターン21を形成した基板20に対して、今度は、孔加工を行う。具体的には、2つの導体パターン21の対向側端部が基板20の一部と共に除去されるように、ICチップ30の幅(図4における、2つの出力用電極パッド32を結んだ方向の幅S3:以下、横幅と呼ぶ)の実測寸法と所定の余裕値との和に相当する寸法のY方向幅S2(以下、横幅と呼ぶ)の角形貫通孔23を開ける。これにより、図5(B)に示すように、2つの配線パターン21が縁にかかった角形貫通孔23が形成される。このとき、あわせて、金属板10の貫通孔12に固定された各充電端子50,51の端部が挿入される円形貫通孔24,25も基板20に形成する。

【0016】

そして、金属板10に固定された各外部端子50,51の端部がそれぞれ基板20の円形貫通孔24,25に挿入されるように、基板20の裏面側を金属板10に導電性接着剤5で貼り付ける。その後、図5(C)に示すように、ICチップ30とコンデンサ40とを、所定のレイアウトで、基板20の角形貫通孔23内に配置する。

【0017】

さらに、ワイヤ70,71のボンディング、金属製キャップ15のろう付け等の処理を行うことによって、図2に示したRFモジュールが完成する。なお、ワイヤ70,71のボンディングは、カメラでICチップ等を撮影し、その撮影画像に、電極パッドおよび配線パターンの認識処理(閾値処理等)を施すようにすれば、完全自動化することができる。

【0018】

このような製造方法によれば、角形貫通孔23の横幅の加工寸法が、その内部に配置されるICチップ30の横幅S3の実測寸法に応じて決定されるため、個々のICチップの形状にバラツキがあっても、ICチップ30の出力用電極パッド32と基板20の配線パターン21との間隔L1,L2のバラツキを抑制することができる。このため、この間隔L1,L2に渡されるワイヤ70(ICチップ30の出力用電極パッド32と基板20の電極パターン23とをつなぐワイヤ70)の長さのバラツキが抑制され、結果的に、信号の伝送損失の大きなRFモジュールの発生が防止される。すなわち、本実施の形態に係る製造方法によれば、組み込まれるICチップ30の形状寸法にバラツキがあっても、信頼性の高いRFモジュールを製造することができる。

【0019】

つぎに、図6により、この製造方法における孔加工に適した加工システムの構成について説明する。

【0020】

本加工システムは、図6(A)に示すように、基板20に対して孔加工を行うレーザ加工機220、レーザ加工機220に制御指令を与える情報処理装置210、管理情報201が予め格納された外部記憶装置200、を有している。外部記憶装置200に格納された管理情報201には、図6(B)に示すように、RFモジュールに使用されるICチップ群の個々のICチップ30について、それぞれ、使用順序に合わせてシーケンシャルにふられたID201A、ICチップ30の横幅S3の実測寸法201B等が格納されている。なお、この管理情報201は、必ずしも外部記憶装置に格納されている必要はなく、例えば、着脱可能な記憶媒体(フロッピィディスク等)、情報処理装置のハードディスク等に格納されていてもよい。もちろん、そのようにする場合には、外部記憶装置が設置されている必要は必ずしもない。

【0021】

このようなシステムにおいて、情報処理装置210が、内蔵ハードディスクからメモリ上に読み込んだプログラムを実行することによって、基板20に対する孔加工が実行される。具体的には、以下の通りである。

【0022】

情報処理装置210は、1枚の基板に対する孔加工が終了すると、基板装着指令T1をレーザ加工機220のハンドリング装置に与えることによって、新たな基板20をレーザ加工機220の加工台上の所定の位置にセットさせる。つぎに、情報処理装置210は、管理情報201の未読IDのうち、最も若いID201Aに対応付けられた実測寸法201Bを外部記憶装置200から読み出し、その実測寸法201Bと所定の余裕値との加算値を角形貫通孔23の横幅寸法として算出する。そして、ここで算出した横幅寸法、角形貫通孔23の横幅寸法以外の既定の寸法、角形貫通孔23の形成位置を表す既定の座標情報等を含む孔加工指令T2をレーザ加工機220に与える。レーザ加工機220は、この孔加工指令T2にしたがって、加工台上の基板20に孔加工を行う。これにより、基板20の一部および配線パターン21の対向側端部が切り取られて、IDチップ30の横幅の実測寸法に応じた横幅の角形貫通孔23が形成される。その後、情報処理装置210は、各円形貫通孔24,25の形成位置を表す座標情報等を含む孔加工指令をレーザ加工機220に順次与えることによって、外部端子50,51が挿入される円形貫通孔24,25を基板20にそれぞれ形成させる。

【0023】

最終的に、情報処理装置210は、基板取外し指令T3をレーザ加工機220のハンドリング装置に与えることによって、孔加工済み基板20をレーザ加工機220の加工台から次工程へ搬送させる。なお、この基板20の角形貫通孔23内には、管理情報201のID201により定まるIDチップ30が配置されることになる。

【0024】

このような孔加工システムによれば、RFモジュールに使用されるICチップの横幅の実測寸法が保存されているため、それを参照することによって、最適な横幅寸法の角形貫通孔を基板に形成することができる。

【0025】

以上においては、基板20に孔加工を行う加工機としてレーザ加工機を用いているが、基板20に孔加工を行う加工機は、必ずしも、レーザ加工機である必要はない。例えば、互いにサイズの異なる貫通孔を打ち抜くことができる複数種類の金型が取り付けられたマルチヘッドを有するプレス機を、レーザ加工機の代わりに(またはレーザ加工機とともに)用いることにしてもよい。以下、このようなプレス機を用いる場合のシステム構成例について説明する。

【0026】

この場合における孔加工システムは、図7(A)に示すように、基板20に対して孔加工を行うプレス機230、プレス機械230に制御指令を与える情報処理装置210、前述の管理情報201とプレス機械230の金型情報202とが格納された外部記憶装置200、を有している。プレス機230は、図8(A)に示すような、複数種類の金型(ここでは、4種類の金型A,B,C,D)が取り付けられたマルチヘッド231を有している。各金型A,B,C,Dは、それぞれ、図8(B)に示すように、基板20に角形貫通孔を打ち抜くための1対の型板(A1,A2)(B1,B2)(C1,C2)(D1,D2)を有している。ただし、各金型A,B,C,Dにより抜かれる角形貫通孔の横幅が互いに異なるように、各金型A,B,C,Dの固定型板A1,B1,C1,D1のパーティング面には、互いに異なる幅の角形凹溝(a≠b≠c≠d)が形成されている。もちろん、各金型A,B,C,Dの可動型板A2,B2,C2,D2のパーティング面には、それぞれ、対になる固定型板のパーティング面の角形凹溝に応じたサイズの角形凸部が形成されている。そして、外部記憶装置200に格納された金型情報202には、図7(B)に示すように、これらの各金型A,B,C,DのID202Aに対応付けて、その金型により打ち抜かれる角形貫通孔内への配置に適したICチップの横幅の寸法範囲が選択条件202Bとして格納されている。なお、この金型情報202とは、管理情報201と同様、必ずしも外部記憶装置に格納されている必要はなく、例えば、着脱可能な記憶媒体(フロッピィディスク等)、情報処理装置のハードディスク等に格納されていてもよい。

【0027】

このようなシステムにおいて、情報処理装置210が、内蔵ハードディスクからメモリ上に読み込んだプログラムを実行することによって、基板20に対する孔加工が実行される。具体的には、以下の通りである。

【0028】

情報処理装置210は、1枚の基板に対する孔加工が終了すると、管理情報201の未読IDのうち、最も若いID201Aに対応付けられた実測寸法201Bを外部記憶装置200から読み出す。そして、その実測寸法201の数値を含んだ選択条件202Bを金型情報202内で検索し、該当する選択条件202Bに対応付けられたID202Aを読みだす。つぎに、情報処理装置210は、このID202A、角形貫通孔23の位置を表す座標情報等を含む孔加工指令T2'をプレス機230に与える。プレス機230は、この孔加工指令T2'にしたがってマルチヘッドを移動させる。これにより、ICチップ30の実測寸法と選択条件202Bとにより定まった金型が使用金型として孔開け位置に位置付けられる。例えば、前の基板に対する孔加工で金型Dが使用されたために、図9(a)に示すように金型Dが孔開け位置に位置付けられている場合に、金型AのIDを含む次の孔加工指令T2が発せられると、プレス機230は、その孔加工指令T2'に応じて、図9(b)に示すように、金型Aを孔開け位置に位置付けるようにマルチヘッド231を移動させる。その後、所定の位置にストックされた基板がハンドリング装置によって使用金型の間に挿入され、さらに使用金型が閉じられる。これにより、基板20の一部および配線パターン21の対向側端部が打ち抜かれて、基板20に角形貫通孔23が形成される。

【0029】

最終的に、情報処理装置210は、基板取外し指令T3'をプレス機230のハンドリング装置に与えることによって、孔加工済み基板20をプレス機230の加工台から次工程へ搬送させる。なお、この基板20の角形貫通孔23内には、前述の場合と同様、管理情報201のID201により定まるIDチップ30が配置されることになる。

【0030】

このような孔加工システムによれば、ICチップの横幅の適用寸法範囲が金型の選択条件として保存されているため、それを参照することによって、ICチップの横幅の実測寸法に応じた角形貫通孔を打ち抜く金型を使用金型として選択することができる。このため、最適な横幅寸法の角形貫通孔を基板に形成することができる。

【0031】

なお、ここでは、4つの金型が取り付けられたマルチヘッドを有するプレス機を使用しているが、実際には、ICチップ群の形状のバラツキの程度等に応じた適当な数の金型が取り付けられたマルチヘッドを有するプレス機を使用すればよい。また、このマルチヘッドには、角形貫通孔を打ち抜くための金型以外に、例えば、外部端子50,51の端部が挿入される円形貫通孔を打ち抜くための金型を取り付けてもよい。

【0032】

また、ここでは、RFモジュールに使用される各ICチップの横幅の実測寸法を管理情報に登録し、ICチップの横幅の適用寸法範囲を金型選択条件として金型情報に登録しているが、必ずしも、このようにする必要はない。例えば、RFモジュールに使用されるICチップ群を、その横幅の実測寸法の値によって複数のグループにランク分けする場合には、RFモジュールに使用される各ICチップごとにそれが属するグループIDを管理情報に登録し、マルチヘッドの各金型ごとにそれが適用されるグループIDを金型情報に登録することにしてもよい。

【0033】

ところで、以上においては、RFモジュールに使用される各ICチップの横幅の実測寸法が予め準備されているが、必ずしも、そのようにする必要はない。例えば、ICチップの横幅の寸法がインラインで測定されるようにしてもよい。以下、そのようにする場合のシステム構成例について説明する。なお、ここでは、レーザ加工機とプレス機との双方を用いることとするが、もちろん、いずれか一方の孔加工機だけを用いることとしてもよい。

【0034】

この場合の孔加工システムは、図10に示すように、基板20に対して孔加工を行うプレス機230、基板20に対して孔加工を行うレーザ加工機220、前述の金型情報202が格納された外部記憶装置200、ICチップ30を1つずつ次工程へ搬送する搬送装置(不図示)、搬送中のICチップ30を撮影するTVカメラ250、基板20をプレス機械230またはレーザ加工機220まで搬送するとともに孔加工済みの基板20を次工程へ搬送する搬送装置(不図示)、プレス機械230とレーザ加工機220等に制御指令を与える情報処理装置210、を有している。

【0035】

このようなシステムにおいて、情報処理装置210が、内蔵ハードディスクからメモリ上に読み込んだプログラムを実行することによって、基板20に対する孔加工が実行される。具体的には、以下の通りである。

【0036】

情報処理装置210は、1枚の基板に対する孔加工が終了すると、新たなICチップ30の搬送指令を搬送装置に与える。これに応じて、搬送装置は、新たなICチップ30を、まず、TVカメラ250の撮影範囲内へと搬送する。このとき、情報処理装置210は、TVカメラ250から出力された画像に2値化処理等を施すことによって、搬送中のICチップ30の横幅S3の寸法を検出する。

【0037】

そして、情報処理装置210は、その寸法S3を寸法範囲に含む選択条件202Bを金型情報202内で検索し、該当する選択条件202Bが見つかったら、それに対応付けられたID202Aを読みだす。つぎに、情報処理装置210は、このID202A等を含む孔加工指令T2'をプレス機230に与えることによって、ICチップ30の実測寸法と選択条件202Bとにより定まる金型が孔開け位置に位置付けさせるとともに、新たな基板20の搬送指令を搬送装置に与えることによってプレス機230まで新たな基板20を搬送させる。その後は、前述の場合と同様、ハンドリング装置によって使用金型の間に基板20が挿入され、さらに使用金型が閉じられる。これにより、基板20の一部および配線パターン21の対向側端部が打ち抜かれて、基板20に角形貫通孔23が形成される。

【0038】

一方、ICチップの横幅S3の寸法を寸法範囲に含む選択条件202Bが見つからなければ、情報処理装置210は、その寸法と所定の余裕値との加算値を角形貫通孔23の横幅寸法として算出するともに、新たな基板20の搬送指令を搬送装置に与えることによってレーザ加工機220まで新たな基板20を搬送させる。その後、情報処理装置210は、基板装着指令T1をレーザ加工機220のハンドリング装置に与えることによって、新たな基板20をレーザ加工機220の加工台上の所定の位置にセットさせてから、前述の場合と同様、角形貫通孔23の横幅寸法等を含む孔加工指令T2をレーザ加工機220に与える。これにより、基板20の一部および配線パターン21の対向側端部が切り取られて、IDチップ30の横幅の実測寸法に応じた横幅の角形貫通孔23が形成される。

【0039】

このようにして、プレス機230およびレーザ加工機220のいずれかによって基板20に角形貫通孔23が形成し終えたら、情報処理装置は、2つの搬送装置に搬送指令を与えることによって、孔加工済みの基板20とその孔加工に利用したICチップとを次工程に搬送させる。これにより、ICチップ30とその横幅寸法に合わせて角形貫通孔23を形成した基板20とが一緒に次工程へ搬送させる。

【0040】

さて、最後に、本実施の形態に係る製造方法を適用可能な電子機器の他の構成例を挙げておく。

【0041】

以上においては、基板20に角形貫通孔を形成し、そこから露出する金属板10にICチップ30およびチップコンデンサ40を接着したが、図11に示すように、金属層26で被覆された底付きの角形孔23'を基板20に形成し、この角形孔23'の底の金属層26に導電性接着剤60'でICチップ30およびチップコンデンサ40を接着するようにしてもよい。この角形穴23'をレーザ加工機220で形成する場合には、基板20に金属層26'を内包させておき、この金属層26'を、レーザ加工機220によるレーザ加工のストッパーとして利用すればよい。

【0042】

また、複数の電子部品を嵌め合せることによって組み立てられる電子機器であれば、どのような電子機器にも適用可能である。例えば、図12に示すように、一方の部材310に形成された貫通孔に他方の部材300を圧入することによって組み立てられた電子機器にも適用可能である。具体的には、図13に示すように、熱伝導性に優れた銅系の金属ブロック300が鉄系の金属板300の貫通孔に圧入された後、配線パターンが形成された回路基板20とパワートランジスタ30とが導電性接着剤60,60'で接着されたパワーモジュールに適用すれば、パワートランジスタ30と貫通孔23との間隔のバラツキが抑制されるため、信頼性の高いパワーモジュールを実現することができる。

【0043】

【発明の効果】

本発明によれば、形状にバラツキのある電子部品が組立て部品に含まれていても、信頼性の高い電子装置を製造可能とすることができる。

【図面の簡単な説明】

【図1】本発明の実施の一形態において製造対象とするRFモジュールの使用例を説明するための図である。

【図2】本実施の形態に係るRFモジュールの断面図である。

【図3】本実施の形態に係るRFモジュールの基板の角形貫通孔部の拡大断面図である。

【図4】RFモジュールの基板の角形貫通孔部の部分図である。

【図5】本発明の実施の一形態に係るRFモジュールの製造方法を説明するための図である。

【図6】(A)は、本発明の実施の一形態に係る孔加工システムの概略構成図であり、(B)は、その外部記憶装置に格納された管理情報のデータ構造を概念的に示した図である。

【図7】(A)は、本発明の実施の一形態に係る孔加工システムの概略構成図であり、(B)は、その外部記憶装置に格納された金型情報のデータ構造を概念的に示した図である。

【図8】図8のプレス機に取り付けられたマルチヘッドの構造を説明するための図である。

【図9】図8のプレス機のマルチヘッドの動きを説明するための図である。

【図10】本発明の実施の一形態に係る孔加工システムの概略構成図である。

【図11】本発明の実施の一形態に係る孔加工システムの基板の角形貫通孔部の拡大断面図である。

【図12】本発明の実施の一形態に係る孔加工システムにより孔加工された部品と、他の部品との嵌め合い部の断面図である。

【図13】本発明の実施の一形態に係るパワーモジュールの部分断面図である。

【符号の説明】

10…金属板、15…金属製キャップ、20…基板、21…配線パターン、22…導体膜、23…角形貫通孔、23'…底付きの角形孔、24,25…円形貫通孔、26…ストッパ、30…ICチップ、31,32…電極パッド、40…チップコンデンサ、50,51…外部端子、70,71…ワイヤ、100…ミリ波レーダ、200…外部記憶装置、210…情報処理装置、220…レーザ加工機、230…プレス機、231…マルチヘッド、250…CCDカメラ

Claims (5)

- 第一の電子部品に形成された孔の縁部と、当該孔内に配置された第二の電子部品とが、第一のワイヤと、当該第二の電子部品に対して当該第一のワイヤと反対側に伸びた第二のワイヤとで接続された電子機器を製造する、電子機器の製造方法であって、

前記第二の電子部品の、前記第一のワイヤとの接続部側から前記第二のワイヤとの接続部側への幅の寸法の測定値に基づき、前記孔の、前記第一のワイヤとの接続部側から前記第二のワイヤとの接続部側への幅の寸法値を定め、当該寸法値の幅の孔を前記孔として前記第一の電子部品に形成する処理を含むことを特徴とする、電子機器の製造方法。 - 第一の電子部品に形成された孔の縁部と、当該孔内に配置された第二の電子部品とが、第一のワイヤと、当該第二の電子部品に対して当該第一のワイヤと反対側に伸びた第二のワイヤとで接続された電子機器を製造する、電子機器の製造方法であって、

前記第一のワイヤとの接続部側から前記第二のワイヤとの接続部側への幅が互いに異なる孔を前記第一の電子部品に打ち抜く複数の金型を準備しておき、

前記第二の電子部品の、前記第一のワイヤとの接続部側から前記第二のワイヤとの接続部側への幅の寸法の測定値に基づき、前記複数の金型のなかから、前記第一の電子部品に孔を打ち抜くための金型を選択し、当該金型で前記第一の電子部品に前記孔を打ち抜く処理を含むことを特徴とする、電子機器の製造方法。 - 第一の電子部品が挿入される孔を第二の電子部品に形成する加工システムであって、

指示された寸法の孔を前記第二の電子部品に形成する加工部と、

前記第二の電子部品に形成する孔の寸法を、前記第一の電子部品の幅の測定値に基づき算出し、当該算出値を含む指示を前記加工部に与える制御部と、

を備えることを特徴とする加工システム。 - 第一の電子部品が挿入される孔を第二の電子部品に形成する加工システムであって、

互いに異なる寸法の孔を打ち抜く金型を複数備え、指定された金型で、前記第二の電子部品に孔を打ち抜く加工部と、

前記複数の金型のなかから、前記第一の電子部品の幅の測定値に応じた幅の孔を打ち抜く金型を選択し、当該金型の指定を含む指示を前記加工部に与える制御部と、

を備えることを特徴とする加工システム。 - 請求項3または4記載の加工システムであって、

前記第一の電子部品の幅を測定するインライン測定部を備え、

前記制御部は、前記インライン測定部による測定値に基づき、前記指示を前記加工部に与えることを特徴とする加工システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001236547A JP3764074B2 (ja) | 2001-08-03 | 2001-08-03 | 電子機器の製造方法および加工システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001236547A JP3764074B2 (ja) | 2001-08-03 | 2001-08-03 | 電子機器の製造方法および加工システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003051579A JP2003051579A (ja) | 2003-02-21 |

| JP2003051579A5 JP2003051579A5 (ja) | 2004-08-26 |

| JP3764074B2 true JP3764074B2 (ja) | 2006-04-05 |

Family

ID=19067794

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001236547A Expired - Fee Related JP3764074B2 (ja) | 2001-08-03 | 2001-08-03 | 電子機器の製造方法および加工システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3764074B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100751471B1 (ko) | 2006-02-02 | 2007-08-23 | 영풍전자 주식회사 | 연성인쇄회로기판의 윈도우 오픈부 형성 방법 |

| WO2008078746A1 (ja) * | 2006-12-26 | 2008-07-03 | Panasonic Corporation | 半導体素子の実装構造体及び半導体素子の実装方法 |

| JP6956823B2 (ja) * | 2015-05-08 | 2021-11-02 | アジャイル・パワー・スイッチ・3・ディー−インテグレイション・エイ・ピー・エス・アイ・3・ディー | 半導体パワーデバイスの組立て方法 |

-

2001

- 2001-08-03 JP JP2001236547A patent/JP3764074B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003051579A (ja) | 2003-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JPH08255861A (ja) | 回路基板の製造方法と回路検査装置 | |

| KR101106234B1 (ko) | 고 용량 메모리 카드를 위한 단일층 기판을 형성하는 방법 | |

| US7065869B2 (en) | Method for plating of printed circuit board strip | |

| US6617200B2 (en) | System and method for fabricating a semiconductor device | |

| CN103247580B (zh) | 电子器件模块以及制造方法 | |

| JP3764074B2 (ja) | 電子機器の製造方法および加工システム | |

| EP0880178B1 (en) | Method of manufacturing a semiconductor device with a pair of radiating terminals and a plurality of lead terminals formed from single lead frame | |

| US5596171A (en) | Package for a high frequency semiconductor device and methods for fabricating and connecting the same to an external circuit | |

| EP0835047A2 (en) | RF-driven semiconductor device | |

| KR101110968B1 (ko) | 메탈기재장치, 아이씨카드모듈 제조방법 및아이씨카드모듈체 | |

| US5665649A (en) | Process for forming a semiconductor device base array and mounting semiconductor devices thereon | |

| JP3420147B2 (ja) | プリント配線母板の加工方法及びプリント配線母板 | |

| CN210042351U (zh) | 一种pcb单板和pcb拼版 | |

| US20220344228A1 (en) | Power Semiconductor Package Unit of Surface Mount Technology and Manufacturing Method Thereof | |

| EP4156254A1 (en) | Electronic packaging architecture with customized variable metal thickness on same buildup layer | |

| KR200243279Y1 (ko) | 반도체장치용써킷테이프 | |

| US5345363A (en) | Method and apparatus of coupling a die to a lead frame with a tape automated bonded tape that has openings which expose portions of the tape leads | |

| JP2002299782A (ja) | 回路基板 | |

| JPH0687472B2 (ja) | フィルムキャリアテープ | |

| KR100578088B1 (ko) | 소형 카메라 모듈용 다층 연성인쇄회로기판 제조방법 및이에 의해 제조되는 다층 연성인쇄회로기판 | |

| KR101113839B1 (ko) | 반도체칩 및 상기 반도체칩의 제조방법 | |

| JPH03283484A (ja) | 大電流回路基板 | |

| US20050054126A1 (en) | System and method for marking the surface of a semiconductor package | |

| JP3348596B2 (ja) | 集積回路装置の製造方法 | |

| CN115696741A (zh) | 天线封装件及其形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20051003 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051011 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051212 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20051212 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20051212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060118 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090127 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100127 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100127 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110127 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110127 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120127 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |