JP3661594B2 - データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム - Google Patents

データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム Download PDFInfo

- Publication number

- JP3661594B2 JP3661594B2 JP2001031485A JP2001031485A JP3661594B2 JP 3661594 B2 JP3661594 B2 JP 3661594B2 JP 2001031485 A JP2001031485 A JP 2001031485A JP 2001031485 A JP2001031485 A JP 2001031485A JP 3661594 B2 JP3661594 B2 JP 3661594B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- length

- output

- predetermined

- data length

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/90—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using coding techniques not provided for in groups H04N19/10-H04N19/85, e.g. fractals

- H04N19/93—Run-length coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/32—Circuits or arrangements for control or supervision between transmitter and receiver or between image input and image output device, e.g. between a still-image camera and its memory or between a still-image camera and a printer device

- H04N1/32609—Fault detection or counter-measures, e.g. original mis-positioned, shortage of paper

- H04N1/32614—Fault detection or counter-measures, e.g. original mis-positioned, shortage of paper related to a single-mode communication, e.g. at the transmitter or at the receiver

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/32—Circuits or arrangements for control or supervision between transmitter and receiver or between image input and image output device, e.g. between a still-image camera and its memory or between a still-image camera and a printer device

- H04N1/32609—Fault detection or counter-measures, e.g. original mis-positioned, shortage of paper

- H04N1/32625—Fault detection

- H04N1/32641—Fault detection of transmission or transmitted data, e.g. interruption or wrong number of pages

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/32—Circuits or arrangements for control or supervision between transmitter and receiver or between image input and image output device, e.g. between a still-image camera and its memory or between a still-image camera and a printer device

- H04N1/32609—Fault detection or counter-measures, e.g. original mis-positioned, shortage of paper

- H04N1/32646—Counter-measures

- H04N1/32683—Preventive counter-measures, e.g. using redundant hardware, or anticipating a fault

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2101/00—Still video cameras

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

- Compression Of Band Width Or Redundancy In Fax (AREA)

Description

【発明の属する技術分野】

本発明は、入力されるデータ列から所定データ長のデータ列を生成するデータストリーム生成装置とその方法、そのような装置および方法を例えばJPEGなどの可変長符号化に適用して所定のデータストリームを生成する可変長データストリーム生成装置とその方法、ならびに、撮影した画像の信号を可変符号化して処理するカメラシステムに関するものである。

【0002】

【従来の技術】

画像データやオーディオデータなどの符号化には種々の方式があるが、その代表的な例であり、静止画像を符号化する際に広く使用されている方式として、JPEG(Joint Photographic Experts Group)がある。

このJPEGでは、圧縮符号化されたビットストリームの構造を規定するために、マーカと呼ばれる種々の制御コードが使用される。

【0003】

例えば、JPEGで採用されているDCT(Discrete Cosine Transform )を用いた符号化方式においては、情報量の削減のために、ブロック間の相関性が高いDCT係数のDC成分は隣接するブロック間における差分値で符号化されている。そのため、JPEG圧縮符号化データを転送する際に何らかの原因によりデータ中にエラーが発生すると、以降に続くブロックに大きな影響を及ぼしてしまう。これを防止するため、JPEG画像データには保持しているDC成分値をクリアするためのリスタートマーカ(RSTm)と呼ばれるマーカが、例えば8×8画素のブロックの集合であるMCU(Minimum Coded Unit)と呼ばれる単位ごとに、ビットストリームの中に挿入される。

その他、例えば1つの画像の始まりを示すSOI(Start Of Image)や、画像の終わりを示すEOI(End Of Image)などのマーカもある。

【0004】

これらのマーカには、FFh(hは16進数表示であることを示す)で表される1バイトのヘッダを有した2バイトのコードが割り当てられている。例えば、RSTmにはFFD0h〜FFD7hというコードが、SOIにはFFD8hというコードが、EOIにはFFD9hというコードが各々割り当てられている。

【0005】

ところでJPEGにおいては、これらのマーカは圧縮符号化ビットストリームにおけるバイト単位の境界に対して適切な位置に挿入されることが要求されている。しかしながら、JPEGの圧縮符号化は可変長符号化であるため、そのままマーカを圧縮符号化ビットストリームに挿入させてしまうと、バイト境界に対するマーカの挿入位置は一定とならない。

そこで、マーカを圧縮符号化ビットストリームに挿入させる場合には、挿入位置を調整するための適切なデータ長を有するビットデータ(フィルビットと呼ばれている)を生成して、これをマーカの手前に挿入する必要がある。

【0006】

【発明が解決しようとする課題】

このように、例えばJPEGにより圧縮符号化された画像データのストリームが生成される場合には、圧縮符号化されて生成されたビットストリームに対して、種々のマーカが挿入されるとともにと、マーカの挿入のたびに上述したフィルビットを生成してマーカの前に挿入しなければならない。このような処理は複雑な制御を必要とするので、従来こうした処理はソフトウェアによって行われていた。しかしながら、データをビットシフトさせて結合させる処理など、ソフトウェアでは多くの実行サイクルが必要となる処理が多い上に、画像データはデータ量が大量になる場合が多く、そのためソフトウェアでは実用的な処理速度が得られにくい問題がある。

また、こうした処理をハードウェアで実現させる場合においても、構成が複雑で回路規模が大きくなるという問題がある。これは、このような回路をLSI上に構成しようとした時などにおいて特に問題となり、改善が望まれている。

【0007】

本発明はかかる事情に鑑みてなされたものであり、その目的は、フィルビットの挿入処理を効率よく行なうことにより、より小さい回路規模で、簡単な構成、制御により、順次入力されるデータ列から所定データ長のデータ列を生成するデータストリーム生成装置とその方法を提供することにある。

また本発明の他の目的は、フィルビットの挿入処理を効率よく行なうことにより、より小さい回路規模で、簡単な構成、制御により、所望のデータを可変長符号化し所定のデータストリームを生成する可変長符号化データストリーム生成装置とその方法を提供することにある。

さらに本発明の他の目的は、所望の画像を撮影し、撮影した画像データを可変長符号化するカメラシステムであって、特に、より小さい回路規模で、簡単な構成、制御により、撮影した画像データを可変長符号化した画像データストリームを生成するカメラシステムを提供することにある。

【0008】

【課題を解決するための手段】

上記の目的を達成するため、本発明の第1の観点に係るデータストリーム生成装置は、順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成装置であって、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記入力データが所定のデータの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、上記帰還データの上記末尾ビット側に上記入力データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理手段とを有する。上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する。

【0009】

本発明の第1の観点に係るデータストリーム生成装置によれば、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータが上記データ出力手段より出力され、当該出力後の残りのデータが帰還データとして出力される。また、上記未出力データのデータ長が上記所定データ長に達しない場合には、当該未出力データが上記帰還データとして上記データ出力手段より出力される。

上記データ付加手段においては、上記入力データが所定のデータの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データが生成され、当該帰還データの上記末尾ビット側に付加される。

上記データ結合手段においては、上記帰還データの上記末尾ビット側に上記入力データの上記先頭ビットが結合され、当該結合されたデータが上記未出力データとして上記データ出力手段に供給される。

【0011】

また、上記データ付加手段は、上記入力データが所定のデータの場合、上記データ長処理手段の積算データ長に応じた調整データ長を設定する調整データ長設定手段と、上記設定された調整データ長に応じた上記調整データを生成する調整データ生成手段と、上記生成された調整データを上記帰還データの上記末尾ビット側に付加する付加手段とを含み、上記データ長処理部は、上記入力データが所定のデータの場合、上記設定された調整データ長を上記積算データ長に加算する。

【0012】

本発明の第2の観点に係るデータストリーム生成装置は、順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成装置であって、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、入力される所定のデータの上記先頭ビット側に付加するデータ付加手段と、供給される選択信号に応じて、上記調整データが付加された所定のデータまたは他の入力データを選択するデータ選択手段と上記帰還データの上記末尾ビット側に、上記選択された入力データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理手段とを有する。上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する。

【0013】

本発明の第2の観点に係るデータストリーム生成装置によれば、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータが上記データ出力手段より出力され、当該出力後の残りのデータが帰還データとして出力される。上記未出力データのデータ長が上記所定データ長に達しない場合には、当該未出力データが上記帰還データとして上記データ出力手段より出力される。

上記データ付加手段においては、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データが生成され、入力される所定のデータの上記先頭ビット側に付加される。

上記データ選択手段においては、供給される選択信号に応じて、上記調整データが付加された所定のデータまたは他の入力データが選択される。

上記データ結合手段においては、上記帰還データの上記末尾ビット側に、上記選択された入力データの上記先頭ビットが結合され、当該結合されたデータが上記未出力データとして上記データ出力手段に供給される。

【0015】

また、上記データ付加手段は、上記データ長処理手段の積算データ長と上記入力データ長の和に応じた調整データ長を設定する調整データ長設定手段と、上記設定された調整データ長に応じた上記調整データを生成する調整データ生成手段と、上記生成された調整データを上記制御データの上記先頭ビット側に付加する付加手段とを含む。

【0016】

本発明の第3の観点に係るデータストリーム生成方法は、順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成方法であって、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、上記入力データが所定のデータの場合に、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加ステップと、上記帰還データの上記末尾ビット側に上記入力データの上記先頭ビットを結合して、上記データ出力ステップの未出力データを生成するデータ結合ステップとを反復する。

【0017】

本発明の第4の観点に係るデータストリーム生成方法は、順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成方法であって、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、入力される所定のデータの上記先頭ビット側に付加し、入力される選択信号に応じて、上記調整データが付加された所定のデータ、または順次入力される可変長データを選択し、当該選択されたデータの上記先頭ビットを上記帰還データの上記末尾ビット側に結合するデータ結合ステップとを反復する。

【0018】

本発明の第5の観点に係る可変長符号化データストリーム生成装置は、可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成装置であって、所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成する可変長符号化手段と、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記可変長符号化手段の生成データが上記制御データの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、上記帰還データの上記末尾ビット側に上記可変長符号化手段の生成データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段とを有する。

【0019】

本発明の第6の観点に係る可変長符号化データストリーム生成装置は、可変長符号化データまたは所定の制御データを順次を生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成装置であって、所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を出力する可変長符号化手段と、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、上記制御データの上記先頭ビット側に付加するデータ付加手段と、上記選択信号に応じて、上記調整データが付加された制御データまたは上記可変長符号データを選択するデータ選択手段と、上記帰還データの上記末尾ビット側に上記データ選択手段の選択データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段とを有する。

【0020】

本発明の第7の観点に係る可変長符号化データストリーム生成方法は、可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成方法であって、所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成する可変長符号化ステップと、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、上記可変長符号化ステップにおける生成データが上記制御データの場合に、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加ステップと、上記帰還データの上記末尾ビット側に上記生成データの上記先頭ビットを結合して、上記データ出力ステップの未出力データを生成するデータ結合ステップとを反復する。

【0021】

本発明の第8の観点に係る可変長符号化データストリーム生成方法は、可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成方法であって、所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を生成する可変長符号化ステップと、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データを生成するデータ出力ステップと、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、上記制御データの上記先頭ビット側に付加し、上記選択信号に応じて、上記調整データが付加された制御データ、または順次入力される可変長データを選択し、当該選択されたデータの上記先頭ビットを上記帰還データの上記末尾ビット側に結合するデータ結合ステップとを反復する。

【0022】

本発明の第9の観点に係るカメラシステムは、画像データを可変長符号化したデータまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するカメラシステムであって、所望の画像を撮影し画像データを生成する撮影手段と、上記生成画像データを可変長符号化した可変長符号化データ、または所望の上記制御データを順次生成する可変長符号化手段と上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力画像データとして出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記可変長符号化手段の生成データが上記制御データの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、上記帰還データの上記末尾ビット側に上記可変長符号化手段の生成データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、上記出力画像データの列に対して所定の処理を行う処理手段とを有する。

【0023】

本発明の第10の観点に係るカメラシステムは、画像データを可変長符号化したデータまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するカメラシステムであって、所望の画像を撮影し画像データを生成する撮影手段と、上記生成画像データを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を出力する可変長符号化手段と、上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力画像データとして出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、上記制御データの上記先頭ビット側に付加するデータ付加手段と、上記選択信号に応じて、上記調整データが付加された制御データまたは上記可変長符号データを選択するデータ選択手段と、上記帰還データの上記末尾ビット側に上記データ選択手段の選択データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、上記出力画像データの列に対して所定の処理を行う処理手段とを有する。

【0024】

【発明の実施の形態】

第1の実施の形態

本発明に係る第1の実施の形態について、図1〜図13を参照して説明する。

本実施の形態においては、例えば電子スチルカメラのような、静止画像を撮影して圧縮符号化し記録するカメラシステムを例示して本発明を説明する。

【0025】

〔カメラシステム100〕

まず、そのカメラシステムの全体の構成および動作について図1を参照して説明する。

図1は、本発明に係る第1の実施の形態のカメラシステム100を説明するための概略的な構成図である。カメラシステム100は、光学系101、CCD102、A/D変換部103、画像圧縮部104、SDRAM114およびCPU115を有する。

また、画像圧縮部104は、CCD信号処理部105、バス106、バッファ107、SDRAMインターフェイス(SDRAMI/F)108、JPEG処理部109、クロック生成部110、システムコントローラ111、CPUインターフェイス(CPUI/F)112およびメモリコントローラ113を有する。

【0026】

光学系101は、使用者の操作により所望の画像を撮像し、その光信号をCCD102の撮像面上に結像させる。

CCD102は、光学系101により結像された撮像面上の光信号を電気信号に変換し、アナログ画像信号としてA/D変換部103に出力する。

A/D変換部103は、CCD102より入力されたアナログ画像信号を所定の階調のデジタル信号に変換し、画像圧縮部104のCCD信号処理部105に出力する。

【0027】

画像圧縮部104のCCD信号処理部105は、システムコントローラ111の制御に基づいて、入力されるデジタル画像信号をR(赤)、G(緑)、B(青)の各色信号に分離し、各色信号に対して色再現性のためガンマ補正を行い、さらに輝度信号と色差信号を生成する。生成された輝度信号と色差信号からなる画像信号は、バス106を介してバッファ107に出力される。

【0028】

バッファ107は、CCD信号処理部105よりバス106を介して入力される画像信号を順次記憶し、一定量蓄えられたら、メモリコントローラ113の制御に基づいて、SDRAMI/F108に出力する。また、SDRAMI/F108から入力される、SDRAM114より読み出された画像データを一時的に記憶し、バス106を介してJPEG処理部109に出力する。

SDRAMI/F108は、画像圧縮部104の外部メモリであって、メモリコントローラ113の制御に基づいて、バッファ107より入力される所定の単位ごとの画像データをSDRAM114に記憶する。また、SDRAM114に記憶されている画像データを、8×8のブロック単位で読み出し、バッファ107に出力する。

【0029】

JPEG処理部109は、システムコントローラ111の制御に基づいて、SDRAM114より読み出されバッファ107を介して入力される画像信号をJPEG符号化し、符号化ビットストリームを生成し、バス106およびCPUI/F112を介してCPU115に出力する。このJPEG処理部109の構成および動作については後に詳細に説明する。

【0030】

クロック生成部110は、システムコントローラ111の制御に基づいて、画像圧縮部104内の各部で使用するクロックを生成し、その各構成部に提供する。

バス106は、画像圧縮部104内のデータバスを模式的に示したものである。このバス106を介して、CCD信号処理部105からバッファ107へおよびバッファ107からJPEG処理部109への画像データの転送、および、JPEG処理部109からCPUI/F112への符号化ビットストリームの転送などが行なわれる。

【0031】

システムコントローラ111は、CPU115の制御に基づいて動作し、画像圧縮部104の動作、すなわち、入力される画像データのSDRAM114への記憶、SDRAM114に記憶された画像データのJPEG処理部109への転送、JPEG処理部109におけるJPEG符号化、および、符号化された画像データのCPU115への出力などの動作が適切に実行されるように、画像圧縮部104の各構成部を制御する。

CPUI/F112は、CPU115とのインターフェイスであり、CPU115からの制御信号、画像信号の入力、CPU115への制御信号、符号化データの出力などを行なう。

メモリコントローラ113は、システムコントローラ111の制御に基づいて、バッファ107およびSDRAMI/F108を制御し、画像データのSDRAM114への記憶およびSDRAM114に記憶された画像データの読み出しなどを制御する。

【0032】

SDRAM114は、撮影された輝度信号および色差信号からなる画像データを一時的に記憶するメモリである。光学系101〜A/D変換部103で撮影された画像データは、一旦SDRAM114に記憶された後、JPEG処理部109に順次供給され、符号化され、CPU115に出力され、記憶、表示、伝送などに用いられる。

CPU115は、光学系101〜画像圧縮部104およびSDRAM114による所望の画像の撮像、画像処理、画像データの記憶・再生、JPEG符号化、JPEG符号化データの記憶、表示、伝送などの各処理が適切に行なわれ、カメラシステム100が全体として所望の動作をするように、カメラシステム100の各構成部を制御する。

【0033】

このような構成のカメラシステム100においては、まず、使用者の操作により光学系101に所望の画像が撮像されると、CCD102において光信号が電気信号に変換されて画像信号が生成される。その画像信号は、A/D変換部103でアナログ信号からデジタル信号に変換され、さらに画像圧縮部104のCCD信号処理部105において各色信号に分解され、ガンマ補正が施された後、輝度信号と色差信号からなる画像信号に変換される。

この画像信号は、バッファ107、SDRAMI/F108を介して一旦SDRAM114に記憶された後、8×8画素のブロックごとに順次読み出されてJPEG処理部109に入力される。

JPEG処理部109においては、順次入力されるブロックごとの画像データがJPEG符号化され、所定のフォーマットのJPEG符号化データストリームが生成され、CPUI/F112を介してCPU115に出力され、記憶、表示、伝送などの処理が行なわれる。

【0034】

〔JPEG処理部109〕

次に、カメラシステム100のJPEG処理部109の内部構成およびその動作について、図2および図3を参照して説明する。

図2は、JPEG処理部109の構成を示すブロック図である。

JPEG処理部109は、DCT・量子化部121、マーカ発生部122、可変長符号化部123、JPEG制御レジスタ124およびJPEGコントローラ125を有する。

なお、JPEG処理部109には1画素8ビットの輝度信号または1画素8ビットの色差信号が、8×8画素単位で入力されるものとする。

【0035】

DCT・量子化部121は、入力される8×8画素の画像データSvにDCTを実行して、64個の周波数成分(DCT係数)に変換し、各係数を、図示せぬ量子化テーブルの対応する値を用いて量子化する。量子化されたDCT係数Sq(11ビット)は、可変長符号化部123に出力される。

【0036】

マーカ発生部122は、JPEGコントローラ125の制御に基づいて、JPEGビットストリームに付加する、そのビットストリームの構造を明確に表現するためのマーカSmを生成し、可変長符号化部123に出力する。

【0037】

可変長符号化部123は、DCT・量子化部121より入力されるDCT係数Sqを可変長符号化し、得られた可変長符号化データと付加ビットデータおよびマーカ発生部122より入力されるマーカSmを、8ビット単位の符号化ビットストリームSdに変換して、JPEG処理部109より出力する。

【0038】

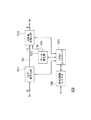

この可変長符号化部123の構成を図3に示す。

図3は、可変長符号化部123の構成を示すブロック図である。

可変長符号化部123は、可変長符号算出部131、可変長符号テーブル132、ビットストリーム生成部133を有する。

【0039】

可変長符号算出部131は、DCT・量子化部121より入力される量子化後のDCT係数Sqに基づいて、可変長符号テーブル132を参照して、DCT係数の大きさに対応する可変長符号化データと、その可変長符号化データの符号長データを検出する。また、そのDCT係数の大きさから付加ビットデータと、その付加ビットデータのデータ長データを検出する。これら検出された可変長符号化データSc、付加ビットデータSa、可変長符号化データ長データScL、付加ビットデータ長データSaLは、各々ビットストリーム生成部133に出力される。

なお、可変長符号化データScは2〜16ビットのデータであり、付加ビットデータSaは0〜11ビットのデータである。したがって、各データ長は、5ビットおよび4ビットのデータとなる。

【0040】

可変長符号テーブル132は、可変長符号化を行なうための符号化テーブルである。

【0041】

ビットストリーム生成部133は、可変長符号算出部131より入力される可変長データである可変長符号化データScおよび付加ビットデータSaを、同じく可変長符号算出部131より入力される可変長符号化データ長データScLおよび付加ビットデータ長データSaLを参照して、8ビット固定長の1つのデータの列に変換し、さらにマーカ発生部122より入力されたマーカSmを付加して、符号化ビットストリームSdとして出力する。

【0042】

JPEG処理部109のJPEG制御レジスタ124は、DCT・量子化部121および可変長符号化部123の動作を制御するデータ、パラメータなどが設定されるレジスタであり、CPU115により、CPUI/F112を介して設定される。

JPEGコントローラ125は、JPEG制御レジスタ124に設定されているデータ、パラメータなどに基づいて、DCT、量子化、マーカ発生、可変長符号化およびビットストリーム生成などの処理が適切に行なわれるように、DCT・量子化部121、マーカ発生部122および可変長符号化部123の動作を制御する。

【0043】

このような構成のJPEG処理部109においては、CPU115からJPEG制御レジスタ124に動作条件などが設定され、これによりJPEGコントローラ125によってDCT・量子化部121および可変長符号化部123が制御され、処理が行なわれる。

すなわち、順次入力される8×8画素ごとの画像データSvを、DCT・量子化部121においてDCTし、量子化する。

量子化されたDCT係数Sqは、可変長符号化部123の可変長符号算出部131において可変長符号化され、可変長符号化データScおよび付加ビットデータSaが生成される。

そして、各々可変長データであるこの可変長符号化データScおよび付加ビットデータSaが、ビットストリーム生成部133において8ビット固定長のデータの列に変換されて、JPEG符号化データストリームSdとして出力される。

【0044】

〔ビットストリーム生成部133〕

次に、上述したJPEG処理部109の、本発明に関わる、可変長符号化部123のビットストリーム生成部133について、図4〜図13を参照して詳細に説明する。

【0045】

まず、図4に示すビットストリーム生成部133の構成について説明する。

図4は、可変長符号化部123のビットストリーム生成部133の構成を説明するための概略的な構成図である。

ビットストリーム生成部133は、結合部1、データ選択部2、データ結合部3、出力部4、フィルビット付加部5、データ長加算部6、データ長選択部7およびデータ長処理部8を有する。

なお、結合部1は、本発明の可変長データ結合手段の一実施形態である。

データ選択部2は、本発明のデータ選択手段の一実施形態である。

データ結合部3は、本発明のデータ結合手段の一実施形態である。

出力部4は、本発明のデータ出力手段の一実施形態である。

フィルビット付加部5は、本発明のデータ付加部の一実施形態である。

データ長加算部6は、本発明のデータ長生成手段の一実施形態である。

データ長選択部7は、本発明のデータ長選択手段の一実施形態である。

データ長処理部8は、本発明のデータ長処理手段の一実施形態である。

【0046】

結合部1は、可変長符号算出部131から入力した16ビットの可変長符号化データScと11ビットの付加ビットデータSaとを結合して27ビットのデータを生成し、データ選択部2に出力する。

【0047】

この27ビットの結合データは、例えば、結合部1に含まれている図示しないシフト回路とOR回路によって、可変長符号化データScと付加ビットデータSaとがMSB側に詰められた状態となるように生成される。この場合、シフト回路に設定されるビットシフト数は、データに同期して入力されるデータ長の情報(可変長符号化データ長データScLまたは付加ビットデータ長データSaL)に基づいて設定される。

例えば、ともにMSB詰めのデータとして入力される可変長符号化データScおよび付加ビットデータSaが、可変長符号化データScが上位となるようにMSB側へ詰められて結合される場合には、まずシフト回路によって、付加ビットデータSaが可変長符号化データ長データScLだけLSB側にビットシフトされる。次に、このシフトされたデータとMSB詰めの可変長符号化データScとがOR回路によって合成される。これにより、MSB詰めにされた27ビットの結合データが生成される。

【0048】

データ選択部2は、結合部1において可変長符号化データScと付加ビットデータSaとが結合された27ビットの結合データS21、または16ビットのマーカSmを選択信号SELに応じて選択し、データ結合部3に出力するブロックである。図4の例においてセレクタ21およびレジスタ22を有している。

セレクタ21は、結合部1による27ビットの結合データ、またはマーカSmを選択信号SELに応じて選択しデータ結合部3に出力する。

またレジスタ22は、セレクタ21において選択されたデータS21を図示しない所定のシステムクロックに同期して保持し、データ結合部3に出力する。ただし、イネーブル信号ENが無効になった場合には、セレクタ21からの新しいデータの入力を停止する。

【0049】

データ結合部3は、データ選択部2において選択された27ビットのデータS2と、フィルビット付加部5から帰還されるデータS5とを結合して58ビットの結合データを生成し、これを出力部4に出力するブロックである。図4の例において結合部31およびレジスタ32を有している。

【0050】

結合部31は、データ選択部2において選択された27ビットのデータS22と、フィルビット付加部5から帰還されるデータS5とを結合して58ビットの結合データを生成し、これをレジスタ32に出力する。

この58ビットの結合データは、例えば、結合部31に含まれている図示しないシフト回路とOR回路によって、データ選択部2からのデータS22とフィルビット付加部5からの帰還データS5とがMSB側に詰められた状態となるように生成される。この場合、シフト回路に設定されるビットシフト数は、フィルビット付加部5から帰還されるデータS5のデータ長(後述する帰還データ長生成部82の出力データS82)に基づいて設定される。

【0051】

レジスタ32は、結合部31において生成された58ビットの結合データを上述したシステムクロックに同期して保持し、これを出力部4に出力する。

【0052】

出力部4は、後述するデータ処理部8において計算された結合データS3のデータ長StLが32ビットに達している場合、MSB側の32ビット分のデータをビットストリームSoutとして出力し、残りのLSB側のデータを帰還データS4としてフィルビット付加部5に出力する。なお、このときの帰還データS4のデータ長は、データ長StLから32ビット長分を減算したデータ長になる。

また、データ長StLが32ビットに達していない場合は、MSB側の31ビット分のデータを帰還データS4としてそのままフィルビット付加部5に出力する。

【0053】

フィルビット付加部5は、イネーブル信号ENが有効の場合、すなわち可変長符号化データScおよび付加ビットデータSaの結合データがレジスタ22に入力されている場合には、出力部4からの帰還データS4をそのまま帰還データS5としてデータ結合部3に出力する。また、イネーブル信号ENが無効の場合には、データ長処理部8において計算された結合データS3のデータ長StLに基づいてフィルビットを生成し、これを出力部4からの帰還データS4のLSB側に付加する。このフィルビットを付加されたデータが、帰還データS5としてデータ結合部3に出力される。また、このとき生成したフィルビットのデータ長SbLをデータ長処理部8に出力する。

なお、このフィルビット付加部5のさらに詳細な構成については後で説明する。

【0054】

データ長加算部6は、可変長符号化データScおよび付加ビットデータSaにそれぞれ対応したデータ長の情報である可変長符号化データ長データScLおよび付加ビットデータ長データSaLを加算し、この加算結果をデータ長選択部7に出力する。したがって、データ長加算部6による加算結果のデータ長は、結合部1による結合データのデータ長と等しい。

【0055】

データ長選択部7は、データ長加算部6の加算結果のデータ長、または入力されるマーカSmのデータ長SmLを選択信号SELに応じて選択し、選択したデータ長をデータ長処理部8に出力する。なお、JPEGにおいてマーカSmのデータ長SmLは通常16ビットの固定値である。このデータ長選択部7は、図4の例において、セレクタ71およびレジスタ72を有している。

【0056】

セレクタ71は、データ長加算部6の加算結果のデータ長、または入力されるマーカSmのデータ長SmLを選択信号SELに応じて選択し、選択したデータ長をレジスタ72に出力する。

レジスタ72は、セレクタ71において選択されたデータ長をシステムクロックに同期して保持し、データ長処理部8に出力する。ただし、イネーブル信号ENが無効になった場合には、セレクタ71からの新しいデータの入力を停止する。

【0057】

データ長処理部8は、データ長選択部7において選択されたデータ長、およびフィルビット付加部5において生成されたフィルビットのデータ長に基づいて、データ結合部3から出力部4に供給される結合データS3のデータ長StLを算出し、これをフィルビット付加部5および出力部4に出力するブロックである。図4の例においては、レジスタ81、帰還データ長生成部82、データ長加算部83、データ長加算部84およびセレクタ85を有する。

【0058】

レジスタ81は、セレクタ85において選択された結合データ長S85をシステムクロックに同期して保持し、保持されたデータ長を結合データS3のデータ長StLとして、出力部4、フィルビット付加部5および帰還データ長生成部82に出力する。レジスタ81には、レジスタ32に保持されているデータのうちの、出力部4で未だ出力されていない出力待ちデータのデータ長が保持されている。

【0059】

帰還データ長生成部82は、フィルビット付加部5に入力される出力部4からの帰還データS4のデータ長を計算するブロックである。すなわち、データ長StLが32ビットに達して出力部4から32ビットのデータSoutが出力される場合、データ長StLから32ビット長分を減算したデータ長S82を生成し、これをデータ長加算部83およびデータ長加算部84に出力する。また、データ長StLが32ビットに達しない場合には、データ長StLをそのままデータ長S82としてデータ長加算部83およびデータ長加算部84に出力する。

【0060】

データ長加算部83は、帰還データ長生成部82からのデータ長S82とデータ長選択部7において選択されたデータ長とを加算し、この加算結果をセレクタ85に出力する。

データ長加算部84は、帰還データ長生成部82からのデータ長S82とフィルビット付加部5において生成されたフィルビットのデータ長SbLとを加算し、この加算結果をセレクタ85に出力する。

【0061】

セレクタ85は、イネーブル信号ENが無効になった場合にデータ長加算部84による加算結果のデータ長S84を選択し、これをレジスタ81に出力する。また、イネーブル信号ENが有効の場合には、データ長加算部83による加算結果のデータ長S83を選択し、これをレジスタ81に出力する。

【0062】

次に、上述した構成を有するビットストリーム生成部133においてビットストリームが生成される動作を説明する。

【0063】

まず、選択信号SELによって可変長データが選択されている場合について説明する。この場合、データ選択部2のセレクタ21には選択信号SELによって結合部1の出力データが選択されており、レジスタ22には可変長符号化データScと付加ビットデータSaとが結合された27ビットの結合データが保持されている。またこれに対応して、データ長選択部7のセレクタ71には選択信号SELによってデータ加算部6の出力データ長が選択されており、レジスタ72には可変長符号化データ長データScLと付加ビットデータ長データSaLとが加算されたデータ長が保持されている。すなわち、レジスタ72には、レジスタ22に保持された結合データのデータ長が保持されている。

【0064】

また、入力データとして可変長データが選択されている場合、イネーブル信号ENは常に有効であるため、フィルビット付加部5によるフィルビットの生成と付加動作は停止され、出力部4からの帰還データS4はそのまま帰還データS5としてデータ結合部3の結合部31に供給されている。この帰還データS5と、データ選択部2において保持された入力の可変長データS2とが結合部31において結合されて、レジスタ32に保持されている。

【0065】

また、イネーブル信号ENが有効であるため、データ長処理部8のセレクタ85においてデータ長加算部83による加算データ長S83が選択され、これがレジスタ81に保持されている。この加算データ長S83はデータ選択部2のレジスタ22に保持された可変長データS2のデータ長と、帰還データ長生成部82において生成された帰還データS4のデータ長S82とが加算されたデータであり、レジスタ32に保持される前の結合データS31のデータ長に相当する。

【0066】

この状態で可変長符号化データScおよび付加ビットデータSaが順次入力されると、データ結合部3のレジスタ32に保持された未出力データのデータ長StLが32ビットに満たない場合、出力部4から帰還される未出力の帰還データS5のLSB側に、レジスタ22の可変長データS2のMSB側が結合され、この結合データがレジスタ32に順次保持される。また、データ長処理部8のレジスタ81には、レジスタ72に入力される可変長データS2のデータ長が順次積算されて保持される。したがって、未出力データのデータ長StLは可変長データ(可変長符号化データSc、付加ビットデータSa)の入力とともに長くなる。

【0067】

そしてこの未出力データ長StLが32ビットに達すると、レジスタ32に保持された未出力データのMSB側32ビットは出力部4から出力データSoutとして出力され、残りのLSB側26ビットはフィルビット付加部5に帰還される。また、データ長処理部8の帰還データ長生成部82においては、未出力データのデータ長StLから出力データ長(32ビット)が減算される。したがって、未出力データ長StLが32ビットに達して出力部4から32ビットづつデータが出力される度に、未出力データのデータ長StLは32ビットづつ短くなる。

【0068】

このように、順次入力される可変長符号化データScおよび付加ビットデータSaはデータ結合部3において順次結合されて保持され、この保持されたデータのMSB側32ビットのデータが出力部4から順次出力される。

出力部4から出力される32ビットのビットストリームSoutは、さらにビットストリーム生成回路133の図示しない回路によって8ビットのビットストリームに変換されて、画像圧縮部104のバス106に順次出力される。例えば、システムクロックの4倍の周波数を有するクロックに同期して動作するセレクタ回路によりこの生成された32ビットから8ビットづつのデータを順次選択し、選択されたデータを8ビットのレジスタに順次保持して出力することにより、8ビットのビットストリームが得られる。

【0069】

次に、選択信号SELが変化して入力データが可変長データからマーカSmに切り換えられる場合について説明する。この場合、データ選択部2のセレクタ21においてはマーカSmが選択されてレジスタ22に保持される。また、データ長選択部7のセレクタ71においてはマーカSmのデータ長SmLが選択されてレジスタ72に保持される。すなわち、レジスタ22にはマーカSmが保持され、レジスタ72にはマーカSmのデータ長SmLが保持される。

【0070】

この選択信号SELの変化に応じてイネーブル信号ENが無効になると、フィルビット付加部5において未出力データ長StLに応じたデータ長のフィルビットが生成されて帰還データS4のLSB側に付加されるとともに、このフィルビット長SbLがデータ長処理部8のデータ長加算部84に出力される。また、データ長処理部8のセレクタ85において、このフィルビット長SbLと帰還データ長S82とが加算された加算データ長S84が選択され、これがレジスタ81に保持される。また、イネーブル信号ENが無効なので、レジスタ22およびレジスタ72による新たなデータの保持が停止される。すなわち、レジスタ22のマーカSmおよびレジスタ72のデータ長SmLはそのまま保持され続ける。

【0071】

こうして一旦フィルビットが帰還データS4に付加されると、レジスタ32に保持される未出力データ長StLは1バイトの整数倍のデータ長になり、この後のクロックサイクルで生成されるフィルビット長SbLはゼロになる。したがって、レジスタ81に保持される未出力データ長StLは一定となる。

また、レジスタ22に保持されたマーカSmは、フィルビット付加部5において付加されたフィルビットの末尾に結合されてレジスタ32に保持されるが、未出力データ長StLにマーカSmのデータ長SmLが加算されていないためマーカSmの部分は未出力データの範囲に含まれない。したがって、この部分が出力部4から出力されることはない。

【0072】

ここで、再び選択信号SELによる入力データの選択がマーカSmから可変長データに切り換わり、これに応じてイネーブル信号ENが有効状態に戻ると、停止されていたレジスタ22およびレジスタ72による新たなデータの保持が再開される。

また、レジスタ81には未出力データ長StLにマーカデータ長SmLが加算されたデータ長が保持されるので、フィルビットの末尾に結合されたマーカSmを含む結合データS3が出力部4による出力対象のデータとなる。

以降、可変長データの結合と32ビットデータの出力によるビットストリームの上述した生成動作が反復される。

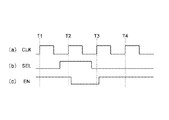

【0073】

ここで、上述したビットストリームの生成動作の具体例について、図5および図6を参照しながら説明する。図5は、システムクロックに対する選択信号SELおよびイネーブル信号ENのタイミング例を示すタイミング図である。また図6は、図5に示すタイミング図の時刻T1〜時刻T4においてレジスタ22およびレジスタ32に保持されるデータの例を示す図である。

なお、図5の例においては選択信号SELがハイレベルの場合にマーカSmが選択され、ローレベルの場合に可変長データが選択される。イネーブル信号ENは、ハイレベルの場合に有効となり、ローレベルの場合に無効となる。また、図4の各レジスタには、システムクロックCLKの立ち上がりに同期してデータが保持される。

【0074】

時刻T1:

セレクタ21において可変長データが選択されており、結合部1からの11ビットの可変長データがレジスタ22に保持される。またレジスタ32には7ビットの未出力データが保持される。

【0075】

時刻T2:

選択信号SELがハイレベルとなり、セレクタ21において16ビットのマーカSmが選択されてレジスタ22に保持される。また、時刻T1にレジスタ22に保持されていた11ビットの可変長データが7ビットの未出力データのLSB側に結合されて、レジスタ32に保持される。

【0076】

時刻T3:

選択信号SELがハイレベルとなり、レジスタ22には結合部1からの出力データが選択されているが、イネーブル信号ENが無効となっているため、レジスタ22に保持されたマーカSmはそのまま保持され続ける。

また、イネーブル信号ENが無効であるためフィルビット付加部5におけるフィルビットの生成および付加動作が有効となり、レジスタ32に保持された未出力データのデータ長18ビット(7ビット+11ビット)に応じた6ビットのフィルビットが生成される。未出力データのデータ長は32ビットに達していないので、この未出力データはそのまま帰還データS4としてフィルビット付加部5に帰還され、LSB側に6ビットのフィルビットが付加される。これにより24ビットの帰還データS5が生成されて、結合部31に入力される。この24ビットの帰還データS5はMSB側に詰められて結合部31から出力され、そのままレジスタ32に保持される。

【0077】

時刻T4:

イネーブル信号ENが有効となりレジスタ22の保持動作が再開されることにより、結合部1からの20ビットの可変データがクロックの立ち上がりに同期してレジスタ22に保持される。

また、レジスタ22に保持されていた16ビットのマーカSmは、結合部31において24ビットの帰還データS5のLSB側に結合されてレジスタ32に保持される。

【0078】

このように、6ビットのフィルビットがフィルビット付加部5において未出力データの末尾側に付加されることにより、マーカSmのデータ境界はビットストリームのバイト境界と一致する。

【0079】

[フィルビット付加部5]

次に、上述したビットストリーム生成部133のフィルビット付加部5について、図7〜図13を参照して詳細に説明する。

【0080】

図7は、図4に示したフィルビット付加部5を説明するための概略的な構成図であり、この図においてフィルビット付加部5は、フィルビット長生成部51、フィルビット生成部および結合部53を有する。

なお、フィルビット長生成部51は、本発明の調整データ長設定手段の一実施形態である。

フィルビット生成部52は、本発明の調整データ生成手段の一実施形態である。

結合部53は、本発明の付加手段の一実施形態である。

【0081】

結合部53は、出力部4から入力した帰還データS4のLSB側にフィルビット生成部52で生成されたフィルビットSbを付加し、全体をMSB側に詰めた32ビットの帰還データS5を生成する。

帰還データS4はMSB側に詰められているので、例えば、結合部53に含まれている図示しないシフト回路によりフィルビットSbをMSBから帰還データS4のデータ長StLだけLSB側にビットシフトさせ、このシフトされたフィルビットSbと帰還データS4とを図示しないOR回路により合成することで、フィルビットSbが付加された帰還データS5を生成することができる。

【0082】

フィルビット長生成部51は、データ長処理部8において計算された未出力データ長StLの下位3ビットに応じてフィルビットのデータ長SbLを生成し、これをフィルビット生成部52およびデータ長処理部8のデータ長加算部84に出力する。

【0083】

図8は、図7に示したフィルビット長生成部51の一例を説明するための概略的な構成図であり、この図においてフィルビット長生成部51は、3ビット入力のNOT回路511および加算部512を有している。

このフィルビット長生成部51においては、未出力データ長StLの下位3ビットがNOT回路511において各ビットごとにビット値が反転されており、さらに反転後のデータの最下位ビットに値”1”のデータが加算されて、3ビットのフィルビット長SbLが生成されている。

ただし、イネーブル信号ENが有効の場合には、図示しないゲート回路等によってフィルビット長は強制的にゼロに設定されるため、後述のフィルビット生成部52においてフィルビットは生成されない。したがって、上述した結合部53に入力される帰還データS4はそのまま帰還データS5としてデータ結合部3に出力される。

【0084】

図9は、未出力データ長StLとフィルビット長SbLとの対応例を示す図である。図9から分かるように、未出力データ長StLの下位3ビットが値”000”の場合はフィルビットの挿入が必要なく、またフィルビットが挿入必要な場合には、未出力データ長StLの下位3ビットにフィルビット長SbLが加算された結果が値”1000”となるように、フィルビット長SbLが設定されている。したがって、値”1000”から未出力データ長StLの下位3ビットが減算されることによってフィルビット長SbLが得られることになり、これは値”111”からの減算結果に値”1”が加算された結果と等しくなる。すなわち、未出力データ長StLの下位3ビットがビット反転された結果に値”1”が加算される図8のフィルビット長生成部51によって、フィルビット長SbLが生成される。

【0085】

なお、図8に示すフィルビット長生成部は一例であり、他の構成も可能である。より一般的な例として、例えば未出力データ長StLを境界の単位となるデータ長(バイト境界の場合には8ビット)で除した商を計算し、この計算結果と当該単位データ長との差分としてフィルビット長を求めることもできる。

以上がフィルビット長生成部51の説明である。

【0086】

次に図7のフィルビット生成部52について説明する。

フィルビット生成部52は、フィルビット長生成部51において生成されたフィルビット長SbLに応じてMSB詰めにされたフィルビットを生成し、これを結合部53に入力する。

【0087】

図10は、図7に示したフィルビット生成部の一例を説明するための概略的な構成図であり、この図においてフィルビット生成部52はセレクタ521を有する。

図11に示すように、フィルビット長(0ビット〜7ビット)とMSB詰めにされた8種類のフィルビットとは一対一に対応している。この8種類のフィルビットがセレクタ521に入力されており、フィルビット長SbLに応じてこれらのフィルビットから対応するフィルビットが選択され、結合部53に出力される。

【0088】

図12は、図7に示したフィルビット生成部の他の例を説明するための概略的な構成図であり、この図においてフィルビット生成部52’は、セレクタ521’、およびデータ生成部522’〜データ生成部525’を有する。

【0089】

データ生成部522’〜データ生成部525’は、フィルビット長SbLの最下位ビットF0、第1ビットF1の値に応じた2ビットのデータF1v、および第2ビットF2の値に応じた4ビットのデータF2vをそれぞれ所定の順序で結合して7ビットのデータを生成し、これをセレクタ521’に出力する。

セレクタ521’は、データ生成部522’〜データ生成部525’の生成データから、フィルビット長SbLの上位2ビットのデータに応じて一のデータを選択し、フィルビットSbとして出力する。

【0090】

図13は、図12に示したフィルビット生成部52’において生成されるフィルビットとフィルビット長との対応例を示す図である。フィルビット長SbLのビットF1に対応する2ビットのデータF1vは、ビットF1を2ビット分連ねたデータとして生成され、ビットF2に対応する4ビットのデータF2vは、ビットF2を4ビット分連ねたデータとして生成される。

【0091】

このデータF1v、データF2vおよびビットF0が{F0,F1v,F2v}、{F1v,F0,F2v}、{F2v,F0,F1v}および{F2v,F1v,F0}という4通りの組み合わせで結合されることにより、MSB詰めにされた7ビットのフィルビットを図11と同じ対応関係で生成することができる。また、これらの4通りの組み合わせは、それぞれフィルビット長SbLの上位2ビットのデータ(ビットF1およびビットF2)と一対一に対応しているので、この2ビットのデータを使って4通りの組み合わせのうちの1つを選択することにより、図11と同じ対応関係で、フィルビット長SbLからフィルビットSbを生成することができる。

図12に示したフィルビット生成部52’は、図10のフィルビット生成部52に比べてセレクタ回路で選択されるデータの数が半分になるので、フィルビット生成部52より回路規模を小さくすることができる。

【0092】

以上説明したように、第1の実施の形態の図4に示すビットストリーム生成部133によれば、データ結合部3において結合されたデータで未出力のデータのデータ長StLが32ビットに達した場合、当該未出力データの上記MSB側から32ビット分のデータが出力部4において出力され、当該出力後の残りのデータが帰還データS4としてフィルビット付加部5に出力される。また、未出力データのデータ長が32ビットに達しない場合は、この未出力データがそのまま帰還データS4としてフィルビット付加部5に出力される。選択信号SELに応じて選択された入力データが可変長データの場合、フィルビット付加部5に入力された帰還データS4はそのまま帰還データS5としてデータ結合部3に出力され、選択信号SELに応じて選択された入力データがマーカSmの場合には、帰還データS4のデータ長StLと1バイトの整数倍のデータ長との差分のデータ長を有するフィルビットSbがフィルビット付加部5において生成され、帰還データS4のLSB側に付加された後、帰還データS5としてデータ結合部3に出力される。データ結合部3においては、帰還データS5のLSB側にデータ選択部2からの入力データのMSBが結合されて、出力部4に供給される。したがって、システムクロックに同期して順次入力される可変長データは、同じシステムクロックに同期して順次32ビットのデータに変換されるとともに、マーカSmが挿入される場合にも、フィルビットの生成および付加動作による1クロックの待ち時間が発生するだけなので、例えばソフトウェアにより同一の機能を実現させる場合に比べて、フィルビットの挿入処理を含むビットストリーム生成処理を大幅に効率化できる。

【0093】

第2の実施の形態

次に、本発明に係る第2の実施の形態について、図14〜図17を参照して説明する。

上述した第1の実施の形態においては、フィルビットの生成および付加動作が行われる場合に、イネーブル信号ENを受けたレジスタ22およびレジスタ72において新しいデータの入力が停止される。このため、データの入力に少なくとも1クロックの待ち時間が発生してしまう問題がある。本実施の形態は、この待ち時間を発生することなしにフィルビットの生成および付加動作を実行できるものである。

【0094】

本実施の形態のカメラシステムの全体の構成および動作、そのJPEG処理部の内部構成および動作、および、その可変長符号化部の構成については、図1〜図3を参照して上述した第1の実施の形態のカメラシステム100と同じなので、その説明は省略する。

以後、本実施の形態の特徴である、可変長符号化部123のビットストリーム生成部133’について説明する。

【0095】

〔ビットストリーム生成部133’〕

まず、ビットストリーム生成部133’の構成について図14を参照して説明する。

図14は、本発明に係る第2の実施の形態のビットストリーム生成部133’を説明するための概略的な構成図である。ビットストリーム生成部133’は、結合部1、データ選択部2’、データ結合部3、出力部4、フィルビット付加部5’、データ長加算部6、データ長選択部7’、データ長処理部8’およびデータ長加算部9を有する。ただし、図4と図14の同一符号は同一の構成要素を示している。

また、フィルビット付加部5’は、本発明のデータ付加部の一実施形態である。

データ長加算部6は、本発明の第1のデータ長生成手段の一実施形態である。

データ長処理部8’は、本発明のデータ長処理手段の一実施形態である。

データ長加算部9は、本発明の第2のデータ長生成手段の一実施形態である。

【0096】

結合部1は、可変長符号算出部131から入力した16ビットの可変長符号化データScと11ビットの付加ビットデータSaとを結合して27ビットのデータを生成し、データ選択部2’に出力する。

【0097】

データ選択部2’は、結合部1において可変長符号化データScと付加ビットデータSaとが結合された27ビットの結合データS21、または後述するフィルビット付加部5’においてフィルビットが付加されたマーカSm’を選択信号SELに応じて選択し、データ結合部3に出力する。

図4におけるデータ選択部2との違いは、レジスタ22’がイネーブル信号ENに応じてデータの入力を停止されないことにある。

【0098】

データ結合部3は、データ選択部2において選択された27ビットのデータS2と、出力部4から帰還されるデータS4とを結合して58ビットの結合データを生成し、これを出力部4に出力する。

【0099】

出力部4は、後述するデータ長処理部8’において計算された結合データS3のデータ長StLが32ビットに達している場合、MSB側の32ビット分のデータをビットストリームSoutとして出力し、残りのLSB側のデータを帰還データS4としてデータ結合部3に帰還する。なお、このときの帰還データS4のデータ長は、データ長StLから32ビット長分を減算したデータ長になる。また、データ長StLが32ビットに達していない場合は、MSB側の31ビット分のデータを帰還データS4としてデータ結合部3に帰還する。

【0100】

フィルビット付加部5’は、データ長処理部8’において計算された結合部31の結合データS31のデータ長SkLに基づいてフィルビットを生成し、入力される16ビットのマーカSmのMSB側に付加する。このフィルビットを付加されたデータが、マーカSm’としてデータ選択部2に出力される。また、このとき生成したフィルビットのデータ長SbLをデータ長加算部9に出力する。

【0101】

図15は、このフィルビット付加部5’を説明するための概略的な構成図であり、この図においてフィルビット付加部5’は、フィルビット長生成部51’、フィルビット生成部52および結合部53’を有している。ただし、図7と図15の同一符号は同一の構成要素を示している。

図7に示すフィルビット付加部5では、結合部53において、入力される帰還データS4のLSB側にフィルビットが付加されるのに対して、図15に示すフィルビット付加部5’の結合部53’では、入力されるマーカSmのMSB側にフィルビットが付加される。またフィルビット長生成部51’はイネーブル信号ENに応じて出力値が制御されなくなる。これら点においてフィルビット付加部5とフィルビット付加部5’とは異なっているが、その他の構成(フィルビット生成部52)については同一である。

【0102】

データ長加算部6は、可変長符号化データScおよび付加ビットデータSaにそれぞれ対応したデータ長の情報である可変長符号化データ長データScLおよび付加ビットデータ長データSaLを加算し、この加算結果をデータ長選択部7’に出力する。したがって、データ長加算部6による加算結果のデータ長は、結合部1による結合データのデータ長と等しい。

【0103】

データ長加算部9は、マーカSmおよびフィルビットSbにそれぞれ対応したデータ長の情報であるマーカSmLおよびフィルビット長SbLを加算し、この加算結果をデータ長選択部7’に出力する。したがって、データ長加算部9による加算結果のデータ長は、フィルビット付加部5’においてマーカSmにフィルビットSbが付加されたマーカSm’のデータ長と等しい。

【0104】

データ長選択部7’は、データ長加算部6の加算結果のデータ長、またはデータ長加算部9の加算結果のデータ長を選択信号SELに応じて選択してデータ長処理部8’に出力する。

図4におけるデータ長選択部7との違いは、レジスタ72’がイネーブル信号ENに応じてデータの入力を停止されないことにある。

【0105】

データ長処理部8’は、データ長選択部7’において選択されたデータ長に基づいて、データ結合部3から出力部4に供給される結合データS3のデータ長StLを算出し、これを出力部4に出力する。またデータ結合部3の結合部31におけるデータ長StLをフィルビット付加部5’に出力する。

図14に示すデータ長処理部8’は、データ長加算部84およびセレクタ85が削除され、データ長加算部83の加算結果がそのままレジスタ81に出力されている点において図4に示すデータ長処理部8と異なっているが、その他の各構成(レジスタ81、帰還データ長生成部82、データ長加算部83)についてはデータ長処理部8と同一である。

【0106】

次に、上述した構成を有するビットストリーム生成部133’においてビットストリームが生成される動作を説明する。

【0107】

まず、選択信号SELによって可変長データが選択されている場合について説明する。この場合、データ選択部2’のセレクタ21には選択信号SELによって結合部1の出力データが選択されており、レジスタ22’には可変長符号化データScと付加ビットデータSaとが結合された27ビットの結合データが保持されている。またこれに対応して、データ長選択部7’のセレクタ71には選択信号SELによってデータ加算部6の出力データ長が選択されており、レジスタ72’には可変長符号化データ長データScLと付加ビットデータ長データSaLとが加算されたデータ長が保持されている。すなわち、レジスタ72’には、レジスタ22’に保持された結合データのデータ長が保持されている。

【0108】

この状態で可変長符号化データScおよび付加ビットデータSaが順次入力されると、データ結合部3のレジスタ32に保持された未出力データのデータ長StLが32ビットに満たない場合、出力部4から帰還される未出力の帰還データS4のLSB側に、レジスタ22’の可変長データS2のMSB側が結合され、この結合データがレジスタ32に順次保持される。また、データ長処理部8’のレジスタ81には、レジスタ72’に入力される可変長データS2のデータ長が順次積算されて保持される。したがって、未出力データのデータ長StLは可変長データ(可変長符号化データSc、付加ビットデータSa)の入力とともに長くなる。

【0109】

そしてこの未出力データ長StLが32ビットに達すると、レジスタ32に保持された未出力データのMSB側32ビットは出力部4から出力データSoutとして出力され、残りのLSB側26ビットはデータ結合部3に帰還される。また、データ長処理部8’の帰還データ長生成部82においては未出力データのデータ長StLから出力データ長(32ビット)が減算される。したがって、未出力データ長StLが32ビットに達して出力部4から32ビットづつデータが出力される度に、未出力データのデータ長StLは32ビットづつ短くなる。

【0110】

このように、順次入力される可変長符号化データScおよび付加ビットデータSaはデータ結合部3において順次結合されて保持され、この保持されたデータのMSB側32ビットのデータが出力部4から順次出力される。

出力部4から出力される32ビットのビットストリームSoutは、さらにビットストリーム生成回路133’の図示しない回路によって8ビットのビットストリームに変換されて、画像圧縮部104のバス106に順次出力される。例えば、システムクロックの4倍の周波数を有するクロックに同期して動作するセレクタ回路によりこの生成された32ビットから8ビットづつのデータを順次選択し、選択されたデータを8ビットのレジスタに順次保持して出力することにより、8ビットのビットストリームが得られる。

【0111】

次に、選択信号SELが変化して入力データが可変長データからマーカSmに切り換えられる場合であるが、この場合、入力されるデータが可変長データからマーカSmに切り換わっただけであるため、上述したデータの結合と出力の動作は入力データが可変長データの場合と同様に行われる。

【0112】

図4のビットストリーム生成部133と図14のビットストリーム生成部133’との違いは、選択信号SELの状態に係わらずマーカSmに付加すべきフィルビットが常に生成され、このフィルビットを付加されたマーカSm’がレジスタ22’に保持される前に確定していることにある。

【0113】

レジスタ22’に保持される前のマーカSmに対して付加すべきフィルビット長の値は、帰還データS4のデータ長と、既にレジスタ22’に保持された入力データのデータ長との和(すなわち次のクロックでレジスタ32に保持される未出力データS31のデータ長)が、8ビット長の整数倍のデータ長に対して有する差分に応じて決定される。したがって、この和のデータ長に相当するデータ加算部83のデータ長SkLがフィルビット付加部5’に供給されると、選択信号SELの状態とは無関係に、フィルビット長SbLおよびフィルビットSbが決定される。このため、マーカSmとして挿入すべきデータがシステムクロックに同期してセットされると、次のクロックでレジスタ22’に入力データが保持されるより前に、フィルビット付加部5’においてフィルビットが付加されたマーカSm’が生成され、選択信号SELに応じててレジスタ22’に供給される。

【0114】

ここで、上述したビットストリームの生成動作の具体例について、図16および図17を参照しながら説明する。図16は、システムクロックに対する選択信号SELのタイミング例を示すタイミング図である。また図17は、図16に示すタイミング図の時刻T1’〜時刻T3’においてレジスタ22’およびレジスタ32に保持されるデータの例を示す図である。

なお、図16の例においては選択信号SELがハイレベルの場合にマーカSmが選択され、ローレベルの場合に可変長データが選択される。また、図14の各レジスタには、システムクロックCLKの立ち上がりに同期してデータが保持される。

【0115】

時刻T1’:

セレクタ21において可変長データが選択されており、結合部1からの7ビットの可変長データがレジスタ22’に保持される。またレジスタ32には11ビットの未出力データが保持される。

また、この時刻T1’から時刻T2’の間において、レジスタ22’に保持された可変長データのデータ長と、レジスタ32に保持された未出力データのデータ長とが加算されたデータ長(7ビット+11ビット=18ビット)がデータ長SkLとしてフィルビット付加部5’に供給される。フィルビット付加部5’において、この供給されたデータ長SkLに基づいて6ビットのフィルビットが生成され、生成されたフィルビットがマーカSmのMSB側に付加されてデータ選択部2’に供給される。

【0116】

時刻T2’:

選択信号SELがハイレベルとなり、セレクタ21においてフィルビット付加部5’のマーカSm’が選択されてレジスタ22’に保持される。また、時刻T1’においてレジスタ22’に保持されていた7ビットの可変長データが11ビットの未出力データのLSB側に結合されて、レジスタ32に保持される。これにより、未出力データのデータ長は18ビットとなる。

【0117】

時刻T3’:

選択信号SELがハイレベルとなり、レジスタ22’には結合部1からの14ビットの可変長データが保持される。また、時刻T2’にレジスタ22’に保持されていたフィルビットとマーカSmの結合データは、18ビットの未出力データのLSB側に結合されて、レジスタ32に保持される。

【0118】

このように、6ビットのフィルビットがフィルビット付加部5’においてマーカSmのMSB側に付加されることにより、マーカSmのデータ境界はビットストリームのバイト境界と一致する。

【0119】

以上説明したように、第2の実施の形態の図14に示すビットストリーム生成部133’によれば、データ結合部3において結合されたデータで未出力のデータのデータ長StLが32ビットに達した場合、当該未出力データのMSB側から32ビット分のデータが出力部4において出力され、当該出力後の残りのデータが帰還データS4としてデータ結合部3に出力される。また、未出力データのデータ長が32ビットに達しない場合は、この未出力データがそのまま帰還データS4としてデータ結合部3に出力される。またフィルビット付加部5’において、入力データS2と帰還データS4のデータ長がデータ長加算部83において加算されたデータ長SkLと、1バイトの整数倍のデータ長との差分のデータ長を有するフィルビットSbが生成される。この生成されたフィルビットSbは、入力されるマーカSmのMSB側に付加されてデータ選択部2’に出力される。データ選択部2’において、上記フィルビットが付加されたマーカSm’、または順次入力される可変長データが選択信号SELに応じて選択される。データ結合部3において、この選択されたデータのMSB側が帰還データS4のLSB側に結合されて出力部4に供給される。したがって、システムクロックに同期して順次入力される可変長データは、同じシステムクロックに同期して順次32ビットのデータに変換されるとともに、マーカSmが挿入される場合において、フィルビットの生成および付加動作による待ち時間が発生しないので、上記した第1の実施の形態に比べて、フィルビットの挿入処理を含むビットストリーム生成処理をさらに効率化できる。またビットストリーム生成部133’においては、データ長処理部8のセレクタ85やデータ長加算部84が削除されるので、第1の実施の形態に比べて回路規模を小さくすることができる。また、イネーブル信号ENによる制御が不要になるので、制御方法を簡易化できる。

【0120】

なお、本発明は本実施の形態に限られるものではなく、種々の改変が可能である。

たとえば、図1に示したカメラシステム、図2に示したJPEG処理部および図3に示した可変長符号化部の構成は、各々これに限られるものではなく、任意の構成でよい。

また、本発明に係る図4および図14に示したビットストリーム生成部の構成や、図7、図8、図10、図12および図15に示したフィルビット付加部の構成なども、任意に変更してよい。

【0121】

また、本発明は、JPEG符号化以外の任意の符号化データや、符号化の結果ではない任意の可変長データに対しても適用可能である。

また、本発明は、JPEG符号化、画像符号化に限定されるものではない。また、カメラシステムにのみ限定されるものではない。可変長符号化処理を含む任意の信号処理装置に対しても適用可能である。

【0122】

【発明の効果】

このように本発明によれば、フィルビットの挿入処理を効率よく行なうことにより、より小さい回路規模で、簡単な構成、制御により、可変長データの列から所定のビット幅の固定長データの列を生成するデータストリーム生成装置とその方法を提供することができる。

また、フィルビットの挿入処理を効率よく行なうことにより、より小さい回路規模で、簡単な構成、制御により、所望のデータを可変長符号化し効率よく所定のデータストリームを生成する可変長符号化データストリーム生成装置とその方法を提供することができる。

さらに、所望の画像を撮影し、撮影した画像データを可変長符号化するカメラシステムであって、特に、より小さい回路規模で、簡単な構成、制御により、撮影した画像データを可変長符号化し、効率よく画像データストリームを生成するカメラシステムを提供することができる。

【図面の簡単な説明】

【図1】本発明に係る第1の実施の形態のカメラシステムを説明するための概略的な構成図である。

【図2】図1に示したカメラシステムのJPEG処理部を説明するための概略的な構成図である。

【図3】図2に示したJPEG処理部の可変長符号化部を説明するための概略的な構成図である。

【図4】図3に示した可変長符号化部のビットストリーム生成部の構成を説明するための概略的な構成図である。

【図5】システムクロックに対する選択信号およびイネーブル信号のタイミング例を示すタイミング図である。

【図6】図5に示すタイミング図の各時刻において各レジスタに保持されるデータの例を示す図である。

【図7】図4に示したフィルビット付加部を説明するための概略的な構成図である。

【図8】図7に示したフィルビット長生成部を説明するための概略的な構成図である。

【図9】未出力データ長とフィルビット長との対応例を示す図である。

【図10】図7に示したフィルビット生成部を説明するための概略的な構成図である。

【図11】フィルビット長とフィルビットとの対応例を示す図である。

【図12】図7に示したフィルビット生成部の他の例を説明するための概略的な構成図である。

【図13】図12に示したフィルビット生成部によって生成されるフィルビットとフィルビット長との対応例を示す図である。

【図14】本発明に係る第2の実施の形態のビットストリーム生成部を説明するための概略的な構成図である。

【図15】図14に示すビットストリーム生成部のフィルビット付加部を説明するための概略的な構成図である。

【図16】システムクロックに対する選択信号のタイミング例を示すタイミング図である。

【図17】図16に示すタイミング図の各時刻において各レジスタに保持されるデータの例を示す図である。

【符号の説明】

1…結合部、2…データ選択部、3…データ結合部、4…出力部、5,5’…フィルビット付加部、6…データ長加算部、7…データ長選択部、8,8’…データ長処理部、9…データ長加算部、21…セレクタ、22…レジスタ、31…結合部、32…レジスタ、51…フィルビット長生成部、52…フィルビット生成部、53,53’…結合部、81…結合データ長生成部、82…セレクタ、83…レジスタ、84…データ長加算部、100…カメラシステム、101…光学系、102…CCD、103…A/D変換部、104…画像圧縮部、105…CCD信号処理部、106…バス、107…バッファ、108…SDRAMI/F、109…JPEG処理部、110…クロック生成部、111…システムコントローラ、112…CPUI/F、113…メモリコントローラ、114…SDRAM、115…CPU、121…DCT・量子化部、122…マーカ発生部、123…可変長符号化部、124…JPEG制御レジスタ、125…JPEGコントローラ、131…可変長符号算出部、132…可変長符号テーブル、133…ビットストリーム生成部、511…ビット反転部、512…加算部、521,521’…セレクタ、522’〜525’…データ生成部

Claims (22)

- 順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成装置であって、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記入力データが所定の制御データの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、

上記帰還データの上記末尾ビット側に上記入力データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

データストリーム生成装置。 - 上記データ付加手段は、

上記入力データが上記制御データの場合、上記データ長処理手段の積算データ長に応じた調整データ長を設定する調整データ長設定手段と、

上記設定された調整データ長に応じた上記調整データを生成する調整データ生成手段と、

上記生成された調整データを上記帰還データの上記末尾ビット側に付加する付加手段とを含み、

上記データ長処理部は、上記入力データが上記制御データの場合、上記設定された調整データ長を上記積算データ長に加算する、

請求項1に記載のデータストリーム生成装置。 - 上記調整データ長設定手段は、上記データ長処理手段の積算データ長のバイナリ値における最下位ビットから所定ビット数の下位データの各ビット値を反転し、当該ビット反転された下位データに所定値を加算したデータに応じた上記調整データ長を設定する、

請求項2に記載のデータストリーム生成装置。 - 上記調整データ生成手段は、上記設定された調整データ長に応じて複数の所定データから一のデータを選択し、当該選択されたデータに応じた調整データを生成する、

請求項2に記載のデータストリーム生成装置。 - 上記調整データ生成手段は、上記設定された調整データ長のバイナリ値における各ビット値に応じたデータを各ビットごとに生成し、当該各ビットごとに生成されたデータを所定の順序で結合して生成される複数のデータから、当該各ビットのうちの少なくとも一つの所定ビットのビット値に応じて一のデータを選択し、当該選択されたデータに応じた調整データを生成する、

請求項2に記載のデータストリーム生成装置。 - 供給される選択信号に応じて、順次入力される可変長データまたは上記制御データを選択し、当該選択された入力データを上記データ結合手段に供給するデータ選択手段と、

上記選択信号に応じて、上記可変長データまたは上記制御データに対応する入力データ長情報を選択し、当該選択された入力データ長情報を上記データ長処理手段に供給するデータ長選択手段とを有する、

請求項1に記載のデータストリーム生成装置。 - 各々が可変長である複数の可変長データを結合し、上記データ選択手段に供給する、可変長データ結合手段と、

上記複数の可変長データのそれぞれに対応する入力データ長情報に基づいて、上記結合された可変長データの入力データ長情報を生成し、上記データ長選択手段に供給するデータ長生成手段とを有する、

請求項6に記載のデータストリーム生成装置。 - 順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成装置であって、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、入力される所定の制御データの上記先頭ビット側に付加するデータ付加手段と、

供給される選択信号に応じて、上記調整データが付加された制御データまたは他の入力データを選択するデータ選択手段と

上記帰還データの上記末尾ビット側に、上記選択された入力データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

データストリーム生成装置。 - 上記データ付加手段は、

上記データ長処理手段の積算データ長と上記入力データ長の和に応じた調整データ長を設定する調整データ長設定手段と、

上記設定された調整データ長に応じた上記調整データを生成する調整データ生成手段と、

上記生成された調整データを上記制御データの上記先頭ビット側に付加する付加手段とを含む、

請求項8に記載のデータストリーム生成装置。 - 上記調整データ長設定手段は、上記データ長処理手段の積算データ長と上記入力データ長の和のバイナリ値における最下位ビットから所定ビット数の下位データの各ビット値を反転し、当該ビット反転された下位データに所定値を加算したデータに応じた上記調整データ長を設定する、

請求項9に記載のデータストリーム生成装置。 - 上記調整データ生成手段は、上記設定された調整データ長に応じて複数の所定データから一のデータを選択し、当該選択されたデータに応じた調整データを生成する、

請求項9に記載のデータストリーム生成装置。 - 上記調整データ生成手段は、上記設定された調整データ長のバイナリ値における各ビット値に応じたデータを各ビットごとに生成し、当該各ビットごとに生成されたデータを所定の順序で結合して生成される複数のデータから、当該各ビットのうちの少なくとも一つの所定ビットのビット値に応じて一のデータを選択し、当該選択されたデータに応じた調整データを生成する、

請求項9に記載のデータストリーム生成装置。 - 上記データ選択手段は、順次入力される可変長データまたは上記制御データを上記選択信号に応じて選択し、当該選択された入力データを上記データ結合手段に供給し、

上記選択信号に応じて、上記可変長データ、または上記調整データを付加された制御データに対応する入力データ長情報を選択し、当該選択された入力データ長情報を上記データ長処理手段に供給するデータ長選択手段を有する、

請求項9に記載のデータストリーム生成装置。 - 各々が可変長である複数の可変長データを結合し、上記データ選択手段に供給する可変長データ結合手段と、

上記複数の可変長データのそれぞれに対応する入力データ長情報に基づいて、上記結合された可変長データの入力データ長情報を生成し、上記データ長選択手段に供給する第1のデータ長生成手段と、

上記設定された調整データ長に基づいて、上記調整データを付加された制御データの入力データ長情報を生成し、上記データ長選択手段に供給する第2のデータ長生成手段とを有する、

請求項13に記載のデータストリーム生成装置。 - 順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成方法であって、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、

上記入力データが所定の制御データの場合に、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加ステップと、

上記帰還データの上記末尾ビット側に上記入力データの上記先頭ビットを結合して、上記データ出力ステップの未出力データを生成するデータ結合ステップと、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理ステップと

を反復し、

上記データ出力ステップは、上記データ長処理ステップの積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

データストリーム生成方法。 - 順次入力されるデータの所定の先頭ビットを、前に入力されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するデータストリーム生成方法であって、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、

上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、入力される所定の制御データの上記先頭ビット側に付加し、入力される選択信号に応じて、上記調整データが付加された制御データ、または順次入力される可変長データを選択し、当該選択されたデータの上記先頭ビットを上記帰還データの上記末尾ビット側に結合するデータ結合ステップと、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理ステップと

を反復し、

上記データ出力ステップは、上記データ長処理ステップの積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

データストリーム生成方法。 - 可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成装置であって、

所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成する可変長符号化手段と、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記可変長符号化手段の生成データが上記制御データの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、

上記帰還データの上記末尾ビット側に上記可変長符号化手段の生成データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

可変長符号化データストリーム生成装置。 - 可変長符号化データまたは所定の制御データを順次を生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成装置であって、

所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を出力する可変長符号化手段と、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、上記制御データの上記先頭ビット側に付加するデータ付加手段と、

上記選択信号に応じて、上記調整データが付加された制御データまたは上記可変長符号データを選択するデータ選択手段と、

上記帰還データの上記末尾ビット側に上記データ選択手段の選択データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される上記入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

可変長符号化データストリーム生成装置。 - 可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成方法であって、

所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成する可変長符号化ステップと、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データに応じた上記帰還データを生成するデータ出力ステップと、

上記可変長符号化ステップにおける生成データが上記制御データの場合に、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加ステップと、

上記帰還データの上記末尾ビット側に上記生成データの上記先頭ビットを結合して、上記データ出力ステップの未出力データを生成するデータ結合ステップと、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理ステップと

を反復し、

上記データ出力ステップは、上記データ長処理ステップの積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

可変長符号化データストリーム生成方法。 - 可変長符号化データまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力する可変長符号化データストリーム生成方法であって、

所望のデータを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を生成する可変長符号化ステップと、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力し、当該出力後の残りのデータに応じた帰還データを生成し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データを生成するデータ出力ステップと、

上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、上記制御データの上記先頭ビット側に付加し、上記選択信号に応じて、上記調整データが付加された制御データ、または順次入力される可変長データを選択し、当該選択されたデータの上記先頭ビットを上記帰還データの上記末尾ビット側に結合するデータ結合ステップと、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理ステップと

を反復し、

上記データ出力ステップは、上記データ長処理ステップの積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

可変長符号化データストリーム生成方法。 - 画像データを可変長符号化したデータまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するカメラシステムであって、

所望の画像を撮影し画像データを生成する撮影手段と、

上記生成画像データを可変長符号化した可変長符号化データ、または所望の上記制御データを順次生成する可変長符号化手段と、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力画像データとして出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記可変長符号化手段の生成データが上記制御データの場合、上記帰還データのデータ長と所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成して、当該帰還データの上記末尾ビット側に付加するデータ付加手段と、

上記帰還データの上記末尾ビット側に上記可変長符号化手段の生成データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算し、上記入力データが上記制御データの場合、当該積算データ長に上記調整データのデータ長を加算するデータ長処理手段と、

上記出力画像データの列に対して所定の処理を行う処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する

カメラシステム。 - 画像データを可変長符号化したデータまたは所定の制御データを順次生成し、当該生成されたデータの所定の先頭ビットを、前に生成されたデータの末尾ビット側に順次結合し、上記結合されたデータの上記先頭ビット側から所定データ長のデータを順次出力するカメラシステムであって、

所望の画像を撮影し画像データを生成する撮影手段と、

上記生成画像データを可変長符号化した可変長符号化データまたは所望の上記制御データを順次生成し、当該生成データに応じた選択信号を出力する可変長符号化手段と、

上記結合されたデータで未出力のデータのデータ長が上記所定データ長に達した場合、当該未出力データの上記先頭ビット側から上記所定データ長分のデータを出力画像データとして出力し、当該出力後の残りのデータを帰還データとして出力し、上記未出力データのデータ長が上記所定データ長に達しない場合、当該未出力データを上記帰還データとして出力するデータ出力手段と、

上記入力データと上記帰還データのデータ長の和と、所定の単位データ長の整数倍のデータ長との差分のデータ長を有する調整データを生成し、上記制御データの上記先頭ビット側に付加するデータ付加手段と、

上記選択信号に応じて、上記調整データが付加された制御データまたは上記可変長符号データを選択するデータ選択手段と、

上記帰還データの上記末尾ビット側に上記データ選択手段の選択データの上記先頭ビットを結合し、当該結合されたデータを上記未出力データとして上記データ出力手段に供給するデータ結合手段と、

上記入力データに対応して順次入力される入力データ長情報に基づいて、上記入力データのデータ長を積算し、当該積算データ長が上記所定データ長に達した場合、当該積算データ長から上記所定データ長を減算するデータ長処理手段と、

上記出力画像データの列に対して所定の処理を行う処理手段と

を有し、

上記データ出力部は、上記データ長処理手段の積算データ長が上記所定データ長に達した場合に上記所定データ長のデータを出力し、上記所定データ長に達しない場合に上記未出力データを上記帰還データとして出力する、

カメラシステム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001031485A JP3661594B2 (ja) | 2001-02-07 | 2001-02-07 | データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム |

| US10/068,706 US6950043B2 (en) | 2001-02-07 | 2002-02-05 | Data stream generation apparatus and method of same, variable length encoded data stream generation apparatus and method of same, and camera system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001031485A JP3661594B2 (ja) | 2001-02-07 | 2001-02-07 | データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002237755A JP2002237755A (ja) | 2002-08-23 |

| JP3661594B2 true JP3661594B2 (ja) | 2005-06-15 |

Family

ID=18895563

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001031485A Expired - Fee Related JP3661594B2 (ja) | 2001-02-07 | 2001-02-07 | データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6950043B2 (ja) |

| JP (1) | JP3661594B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2003084077A1 (en) * | 2002-03-25 | 2003-10-09 | Allied-Telesis, K.K. | Variable/fixed length data conversion method and device |

| JP3938054B2 (ja) | 2003-01-17 | 2007-06-27 | セイコーエプソン株式会社 | 画像データ構造を有するデータが記録されたコンピュータ読み取り可能な記憶媒体、画像記録方法、装置及びプログラム |

| NZ549548A (en) * | 2006-08-31 | 2009-04-30 | Arc Innovations Ltd | Managing supply of a utility to a customer premises |

| SE531398C2 (sv) * | 2007-02-16 | 2009-03-24 | Scalado Ab | Generering av en dataström och identifiering av positioner inuti en dataström |

| SE533185C2 (sv) * | 2007-02-16 | 2010-07-13 | Scalado Ab | Metod för behandling av en digital bild samt bildrepresentationsformat |

| JP5472610B2 (ja) * | 2009-11-26 | 2014-04-16 | 大日本印刷株式会社 | 数値データ列の符号化/復号化の方法および装置 |

| US9137443B2 (en) | 2011-04-26 | 2015-09-15 | Blackberry Limited | Fast estimation of binary data length using memory corruption |

| US9817728B2 (en) | 2013-02-01 | 2017-11-14 | Symbolic Io Corporation | Fast system state cloning |

| US10133636B2 (en) | 2013-03-12 | 2018-11-20 | Formulus Black Corporation | Data storage and retrieval mediation system and methods for using same |

| US9304703B1 (en) | 2015-04-15 | 2016-04-05 | Symbolic Io Corporation | Method and apparatus for dense hyper IO digital retention |

| US9628108B2 (en) | 2013-02-01 | 2017-04-18 | Symbolic Io Corporation | Method and apparatus for dense hyper IO digital retention |

| US10061514B2 (en) | 2015-04-15 | 2018-08-28 | Formulus Black Corporation | Method and apparatus for dense hyper IO digital retention |

| US10956432B2 (en) * | 2017-08-30 | 2021-03-23 | Gsi Technology Inc. | One by one selection of items of a set |

| US10572186B2 (en) | 2017-12-18 | 2020-02-25 | Formulus Black Corporation | Random access memory (RAM)-based computer systems, devices, and methods |

| WO2020142431A1 (en) | 2019-01-02 | 2020-07-09 | Formulus Black Corporation | Systems and methods for memory failure prevention, management, and mitigation |

| CN119621006B (zh) * | 2024-11-28 | 2025-09-23 | 北京百度网讯科技有限公司 | 数据处理方法及装置、设备和介质 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4967196A (en) * | 1988-03-31 | 1990-10-30 | Intel Corporation | Apparatus for decoding variable-length encoded data |

| US5173695A (en) * | 1990-06-29 | 1992-12-22 | Bell Communications Research, Inc. | High-speed flexible variable-length-code decoder |

| US5168356A (en) * | 1991-02-27 | 1992-12-01 | General Electric Company | Apparatus for segmenting encoded video signal for transmission |

| US5245338A (en) * | 1992-06-04 | 1993-09-14 | Bell Communications Research, Inc. | High-speed variable-length decoder |

| KR0134299B1 (ko) * | 1994-07-11 | 1998-04-29 | 김광호 | 가변장디코딩장치의 동기 복원방법 및 장치 |

| US5552832A (en) * | 1994-10-26 | 1996-09-03 | Intel Corporation | Run-length encoding sequence for video signals |

| KR0178201B1 (ko) * | 1995-08-31 | 1999-05-01 | 배순훈 | 가변 길이 복호화 장치 |

| US5663726A (en) * | 1995-12-01 | 1997-09-02 | U.S. Philips Corporation | High speed variable-length decoder arrangement with reduced memory requirements for tag stream buffering |

| KR0183173B1 (ko) * | 1995-12-13 | 1999-05-15 | 윤종용 | 버퍼 메모리 제어 장치 |

| JP3671595B2 (ja) * | 1997-04-01 | 2005-07-13 | 株式会社日立製作所 | 複合計算機システムおよび複合i/oシステム |

| JPH1118087A (ja) * | 1997-06-20 | 1999-01-22 | Olympus Optical Co Ltd | 画像データの変換装置および変換方法 |

| US5961626A (en) * | 1997-10-10 | 1999-10-05 | Motorola, Inc. | Method and processing interface for transferring data between host systems and a packetized processing system |

| JP2000069292A (ja) * | 1998-08-24 | 2000-03-03 | Canon Inc | 画像処理装置及び方法及び記憶媒体 |

| US6215424B1 (en) * | 1998-12-16 | 2001-04-10 | Thomson Licensing S.A. | System for variable length codeword processing suitable for video and other applications |

-

2001

- 2001-02-07 JP JP2001031485A patent/JP3661594B2/ja not_active Expired - Fee Related

-

2002

- 2002-02-05 US US10/068,706 patent/US6950043B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002237755A (ja) | 2002-08-23 |

| US6950043B2 (en) | 2005-09-27 |

| US20020122597A1 (en) | 2002-09-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3661594B2 (ja) | データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、および、カメラシステム | |

| JP2000138934A (ja) | ファイルサイズが制限されたjpeg符号化装置、方法および記録媒体 | |

| JP2891772B2 (ja) | イメージフレームのランダムスキャンニングを用いるディジタルイメージコーディング法 | |

| JP2000115770A (ja) | 符号化装置及び方法 | |

| JP4329238B2 (ja) | データストリーム生成装置とその方法、可変長符号化データストリーム生成装置とその方法、カメラシステム | |

| CN110087085B (zh) | 图像处理装置 | |

| JP2003032677A (ja) | 動画像圧縮符号化装置 | |

| WO2000002381A1 (en) | Image processing circuit and method for modifying a pixel value | |

| US6437712B1 (en) | Data stream conversion apparatus and method, variable length coded data stream generation apparatus and method, and camera system | |

| JPH1065549A (ja) | 可変長符号化データ値の長さを決定する装置、可変長符号化データ値のデータストリームを復号化する装置および可変長符号化データ値の長さを決定する方法 | |

| JP3341781B2 (ja) | 画像復号化装置および画像符号化装置 | |

| US20070025632A1 (en) | Image coding apparatus and its control method, and computer program and computer readable storage medium | |

| JPH10271016A (ja) | 符号/復号化器 | |

| JP4100836B2 (ja) | 画像処理装置 | |

| US5692074A (en) | Image information coding device and image information communication device with block average information and controllable compression | |

| JP3627659B2 (ja) | データ符号化装置とその方法およびカメラシステム | |

| JP4241517B2 (ja) | 画像符号化装置及び画像復号装置 | |

| JP2004501531A (ja) | ビデオ・データをランレングス符号化するための方法と装置 | |

| KR100530745B1 (ko) | 고해상도 영상신호를 저해상도 디스플레이 장치에 디스플레이하는 디스플레이 방법 | |

| JP3139242B2 (ja) | 映像信号処理装置 | |

| JPH11225341A (ja) | 画像符号化装置及び画像復号化装置 | |

| JPH11338853A (ja) | 画像符号化方法 | |

| JPH02202285A (ja) | 適応符号化装置 | |

| JP2000059635A (ja) | 画像処理装置及びその方法 | |

| JPH0630392A (ja) | 画像符号化装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050210 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050301 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050314 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080401 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090401 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100401 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100401 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110401 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120401 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130401 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130401 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140401 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |