JP2017505545A - バックゲートを有し、パンチスルーなしで、フィン高さのばらつきを減少させたFinFET - Google Patents

バックゲートを有し、パンチスルーなしで、フィン高さのばらつきを減少させたFinFET Download PDFInfo

- Publication number

- JP2017505545A JP2017505545A JP2016550526A JP2016550526A JP2017505545A JP 2017505545 A JP2017505545 A JP 2017505545A JP 2016550526 A JP2016550526 A JP 2016550526A JP 2016550526 A JP2016550526 A JP 2016550526A JP 2017505545 A JP2017505545 A JP 2017505545A

- Authority

- JP

- Japan

- Prior art keywords

- finfet

- layer

- semiconductor

- band gap

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000009792 diffusion process Methods 0.000 claims abstract description 15

- 239000004065 semiconductor Substances 0.000 claims description 67

- 238000000034 method Methods 0.000 claims description 30

- 150000001875 compounds Chemical class 0.000 claims description 20

- 239000000758 substrate Substances 0.000 claims description 18

- 230000008878 coupling Effects 0.000 claims description 10

- 238000010168 coupling process Methods 0.000 claims description 10

- 238000005859 coupling reaction Methods 0.000 claims description 10

- 229910001218 Gallium arsenide Inorganic materials 0.000 claims description 9

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 6

- 229910045601 alloy Inorganic materials 0.000 claims description 6

- 239000000956 alloy Substances 0.000 claims description 6

- 238000005530 etching Methods 0.000 claims description 6

- 238000002955 isolation Methods 0.000 claims description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 5

- 229910010271 silicon carbide Inorganic materials 0.000 claims description 5

- 229910021393 carbon nanotube Inorganic materials 0.000 claims description 3

- 239000002041 carbon nanotube Substances 0.000 claims description 3

- 230000001413 cellular effect Effects 0.000 claims description 3

- 229910021389 graphene Inorganic materials 0.000 claims description 3

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims description 2

- 238000004519 manufacturing process Methods 0.000 claims 1

- 230000004888 barrier function Effects 0.000 abstract description 9

- 239000010410 layer Substances 0.000 description 80

- 238000004891 communication Methods 0.000 description 11

- 239000013078 crystal Substances 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000009471 action Effects 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 229910000927 Ge alloy Inorganic materials 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000006249 magnetic particle Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/7855—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET with at least two independent gates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/26—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, elements provided for in two or more of the groups H01L29/16, H01L29/18, H01L29/20, H01L29/22, H01L29/24, e.g. alloys

- H01L29/267—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, elements provided for in two or more of the groups H01L29/16, H01L29/18, H01L29/20, H01L29/22, H01L29/24, e.g. alloys in different semiconductor regions, e.g. heterojunctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7848—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being located in the source/drain region, e.g. SiGe source and drain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/7851—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET with the body tied to the substrate

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

- H03K2017/6878—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors using multi-gate field-effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0018—Special modifications or use of the back gate voltage of a FET

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0054—Gating switches, e.g. pass gates

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

Description

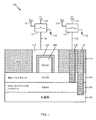

102 基板

104 層

106 層

108 チャネル

110 ゲート誘電体

112 ゲート

114 層間誘電体

116 バックゲートコンタクト

118 深いトレンチ分離(DTI)領域

120 レール

122 レール

124 機能ユニット

126 機能ユニット

128 接続線

130 接続線

132 電力レール

300 FinFET

302 ストレッサ

304 ストレッサ

306 ソース/ドレイン拡散

308 ソース/ドレイン拡散

310 側壁スペーサ

312 側壁スペーサ

314 DTI領域

316 DTI領域

502 ワイヤレス通信ネットワーク

504A 基地局

504B 基地局

504C 基地局

506 通信デバイス

508 矢印

510 矢印

Claims (30)

- 基板と、

前記基板中に形成される第1の層を備えるバックゲートであって、前記第1の層が第1の半導体を備える、バックゲートと、

前記第1の層の上方に形成される第2の層であって、第2の半導体を備える第2の層と、

前記第2の層の上方に形成されるフィンチャネルであって、第3の半導体を備えるフィンチャネルと、

前記第2の層を通り、前記第1の層と電気接触する、バックゲートコンタクトと、

前記基板を掘り下げて形成される深いトレンチ分離領域と

を備え、

前記第1の半導体が第1のバンドギャップを有し、前記第3の半導体が第3のバンドギャップを有し、前記第2の半導体が前記第1のバンドギャップおよび第2のバンドギャップよりも大きい前記第2のバンドギャップを有する、

FinFET。 - 前記第1、第2、および第3の半導体が、III−V族半導体化合物、II−VI族半導体化合物、IV族半導体元素または化合物、グラフィン、およびカーボンナノチューブからなるグループから各々選択される、請求項1に記載のFinFET。

- 前記第1および第3の半導体が各々GaAsを含み、前記第2の半導体がAlAsを含む、請求項2に記載のFinFET。

- 前記第1のバンドギャップが前記第3のバンドギャップと等しい、請求項1に記載のFinFET。

- 前記フィンチャネルの上方に形成される誘電体層と、

前記誘電体層の上方に形成されるゲートと

をさらに備える、請求項1に記載のFinFET。 - 前記FinFETをオンにする第1の電圧を提供するために前記ゲートに結合される第1のレールと、

前記FinFETをオンにする第2の電圧を提供するために前記バックゲートコンタクトに結合される第2のレールと

をさらに備える、請求項5に記載のFinFET。 - 前記第1のレールと第2のレールとが同じ電圧である、請求項6に記載のFinFET。

- 前記フィンチャネルに応力を提供するために、前記第2の層の中にエピタキシャル成長される第1のストレッサと第2のストレッサと

をさらに備える、請求項1に記載のFinFET。 - 前記フィンチャネルに隣接し、前記第1のストレッサに隣接する、第1のソース/ドレイン拡散と、

前記フィンチャネルに隣接し、前記第2のストレッサに隣接する、第2のソース/ドレイン拡散と

をさらに備える、請求項8に記載のFinFET。 - 前記FinFETをオンにする第1の電圧を提供するために前記ゲートに結合される第1のレールと、

前記FinFETをオンにする第2の電圧を提供するために前記バックゲートコンタクトに結合される第2のレールと

をさらに備える、請求項9に記載のFinFET。 - 前記FinFETがnタイプである場合、前記第1の層が、1×1019cm−3から1×1022cm−3の範囲のドーピング濃度で、多量にpタイプでドープされ、前記FinFETがpタイプである場合、前記第1の層が、1×1019cm−3から1×1022cm−3の範囲のドーピング濃度で、多量にnタイプでドープされる、請求項1に記載のFinFET。

- 前記FinFETがnタイプである場合、前記第2の層が、1×1013cm−3から1×1017cm−3の範囲のドーピング濃度で、軽くpタイプでドープされ、前記FinFETがpタイプである場合、前記第2の層が、1×1013cm−3から1×1017cm−3の範囲のドーピング濃度で、軽くnタイプでドープされる、請求項11に記載のFinFET。

- 前記第2の層がドープされない、請求項11に記載のFinFET。

- 前記FinFETが、セルラーフォン、タブレット、コンピュータシステム、および基地局からなるグループから選択されるデバイス中で使用される、請求項1に記載のFinFET。

- FinFETを製造する方法であって、

基板の中に第1の半導体層を形成するステップと、

前記第1の半導体層の上方に第2の半導体層を形成するステップと、

前記第2の半導体層の上方に第3の半導体層を形成するステップと、

FinFETフィンチャネルを形成するために前記第3の半導体層をエッチングするステップと、

前記第2の半導体層を通って前記第1の半導体層までエッチングして、前記第1の半導体層への電気的なバックゲートコンタクトを形成するステップと、

前記基板に深いトレンチ分離領域を形成するステップと

を含み、

前記第1、第2、および第3の半導体層が、それぞれ第1のバンドギャップ、第2のバンドギャップ、および第3のバンドギャップを各々有し、前記第2のバンドギャップが前記第1のバンドギャップおよび前記第2のバンドギャップよりも大きい、

方法。 - 前記FinFETフィンチャネルの上方に誘電体層を形成するステップと、

前記誘電体層の上方にゲートを形成するステップと

をさらに含む、請求項15に記載の方法。 - 前記第1のバンドギャップが前記第3のバンドギャップと等しい、請求項15に記載の方法。

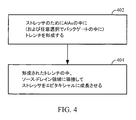

- 前記第2の層の中に第1のトレンチを形成するステップと、

前記FinFETフィンチャネルに応力を提供するために、前記第1のトレンチの中に第1のストレッサをエピタキシャル成長させるステップと、

前記第2の層の中に第2のトレンチを形成するステップと、

前記FinFETフィンチャネルに応力を提供するために、前記第2のトレンチの中に第2のストレッサをエピタキシャル成長させるステップと

をさらに含む、請求項15に記載の方法。 - 前記第1および第2のストレッサが、シリコンゲルマニウム合金(SiGe)、炭化シリコン合金(SiC)、III−V族半導体化合物、II−VI族半導体化合物、IV族半導体元素または化合物からなるグループから選択される、請求項18に記載の方法。

- 第1のソース/ドレイン拡散に隣接して前記第1のストレッサをエピタキシャル成長させるステップと、

第2のソース/ドレイン拡散に隣接して前記第2のストレッサをエピタキシャル成長させるステップと

をさらに含む、請求項18に記載の方法。 - 前記FinFETフィンチャネルの上方に誘電体層を形成するステップと、

前記誘電体層の上方にゲートを形成するステップと

をさらに含む、請求項20に記載の方法。 - 前記第1の層の中に前記第1のトレンチを形成するステップと、

前記第1の層の中に前記第2のトレンチを形成するステップと

をさらに含む、請求項18に記載の方法。 - 前記第1、第2、および第3の半導体層が、III−V族半導体化合物、II−VI族半導体化合物、IV族半導体元素または化合物、グラフィン、およびカーボンナノチューブからなるグループから各々選択される、請求項15に記載の方法。

- 前記第1および第3の半導体層が各々GaAsを含み、前記第2の半導体層がAlAsを含む、請求項23に記載の方法。

- 前記FinFETがnタイプである場合、前記第1の層を、1×1019cm−3から1×1022cm−3の範囲のドーピング濃度で、pタイプでドープし、

前記FinFETがpタイプである場合、前記第1の層を、1×1019cm−3から1×1022cm−3の範囲のドーピング濃度で、nタイプでドープする、

請求項15に記載の方法。 - 前記FinFETがnタイプである場合、前記第2の層を、1×1013cm−3から1×1017cm−3の範囲のドーピング濃度で、pタイプでドープし、

前記FinFETがpタイプである場合、前記第2の層を、1×1013cm−3から1×1017cm−3の範囲のドーピング濃度で、nタイプでドープする、

請求項25に記載の方法。 - 前記第2の層がドープされない、請求項25に記載の方法。

- FinFETをオンにする方法であって、前記FinFETがゲート、バックゲート、および基板を備え、方法が、

前記FinFETの前記ゲートを第1のレールに結合するステップと、

前記FinFETの前記バックゲートを第2のレールに結合するステップであって、前記バックゲートが、前記基板中に形成される第1の層を備え、第1の半導体を備えるステップと

を含み、

前記ゲートが、第2の層の上方に形成されるフィンチャネルの上方に形成され、前記第2の層が前記第1の層の上方に形成されて第2の半導体を備え、前記フィンチャネルが第3の半導体を備え、

前記第1の半導体が第1のバンドギャップを有し、前記第3の半導体が第3のバンドギャップを有し、前記第2の半導体が前記第1のバンドギャップおよび第2のバンドギャップよりも大きい前記第2のバンドギャップを有する、

方法。 - 前記第1のレールと第2のレールとが同じ電圧である、請求項28に記載の方法。

- 前記第1のバンドギャップと前記第3のバンドギャップが互いに等しい、請求項28に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/179,311 | 2014-02-12 | ||

| US14/179,311 US9236483B2 (en) | 2014-02-12 | 2014-02-12 | FinFET with backgate, without punchthrough, and with reduced fin height variation |

| PCT/US2015/015426 WO2015123305A1 (en) | 2014-02-12 | 2015-02-11 | Finfet with backgate, without punchthrough, and with reduced fin height variation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017505545A true JP2017505545A (ja) | 2017-02-16 |

| JP2017505545A5 JP2017505545A5 (ja) | 2018-03-08 |

Family

ID=52577996

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016550526A Pending JP2017505545A (ja) | 2014-02-12 | 2015-02-11 | バックゲートを有し、パンチスルーなしで、フィン高さのばらつきを減少させたFinFET |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9236483B2 (ja) |

| EP (1) | EP3105796A1 (ja) |

| JP (1) | JP2017505545A (ja) |

| CN (1) | CN105981174A (ja) |

| WO (1) | WO2015123305A1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102445837B1 (ko) | 2015-06-26 | 2022-09-22 | 인텔 코포레이션 | 고 이동도 반도체 소스/드레인 스페이서 |

| US10446685B2 (en) | 2015-09-25 | 2019-10-15 | Intel Corporation | High-electron-mobility transistors with heterojunction dopant diffusion barrier |

| US10388764B2 (en) | 2015-09-25 | 2019-08-20 | Intel Corporation | High-electron-mobility transistors with counter-doped dopant diffusion barrier |

| CN108028281B (zh) | 2015-09-25 | 2022-04-15 | 英特尔公司 | 具有带偏移半导体源极/漏极衬垫的高迁移率场效应晶体管 |

| WO2017218015A1 (en) | 2016-06-17 | 2017-12-21 | Intel Corporation | High-mobility field effect transistors with wide bandgap fin cladding |

| US20180337228A1 (en) * | 2017-05-18 | 2018-11-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Novel seal ring for iii-v compound semiconductor-based devices |

| US10872794B2 (en) | 2017-06-20 | 2020-12-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Automatic in-line inspection system |

| WO2019005111A1 (en) * | 2017-06-30 | 2019-01-03 | Intel Corporation | VARIOUS TRANSISTOR CHANNEL MATERIALS ACTIVATED BY A REVERSE GRADIENT GERMANIUM THIN LAYER |

| US20190371891A1 (en) * | 2018-06-01 | 2019-12-05 | Qualcomm Incorporated | Bulk layer transfer based switch with backside silicidation |

| US10756205B1 (en) | 2019-02-13 | 2020-08-25 | International Business Machines Corporation | Double gate two-dimensional material transistor |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002110963A (ja) * | 2000-09-28 | 2002-04-12 | Toshiba Corp | 半導体装置 |

| JP2007287913A (ja) * | 2006-04-17 | 2007-11-01 | Matsushita Electric Ind Co Ltd | 電界効果型トランジスタ及びその製造方法 |

| US20130011983A1 (en) * | 2011-07-07 | 2013-01-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | In-Situ Doping of Arsenic for Source and Drain Epitaxy |

| US20130056795A1 (en) * | 2011-09-06 | 2013-03-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET Design Controlling Channel Thickness |

| JP2013513250A (ja) * | 2009-12-23 | 2013-04-18 | インテル コーポレイション | 非平面ゲルマニウム量子井戸デバイス |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060197129A1 (en) | 2005-03-03 | 2006-09-07 | Triquint Semiconductor, Inc. | Buried and bulk channel finFET and method of making the same |

| US7411252B2 (en) | 2005-06-21 | 2008-08-12 | International Business Machines Corporation | Substrate backgate for trigate FET |

| DE102005059231B4 (de) | 2005-12-12 | 2011-01-13 | Infineon Technologies Ag | Verfahren zum Herstellen eines Verbindungshalbleiter-Feldeffekttransistors mit einer Fin-Struktur und Verbindungshalbleiter-Feldeffekttransistor mit einer Fin-Struktur |

| US7569869B2 (en) | 2007-03-29 | 2009-08-04 | Intel Corporation | Transistor having tensile strained channel and system including same |

| US7485520B2 (en) | 2007-07-05 | 2009-02-03 | International Business Machines Corporation | Method of manufacturing a body-contacted finfet |

| US8120063B2 (en) | 2008-12-29 | 2012-02-21 | Intel Corporation | Modulation-doped multi-gate devices |

| CN101853882B (zh) | 2009-04-01 | 2016-03-23 | 台湾积体电路制造股份有限公司 | 具有改进的开关电流比的高迁移率多面栅晶体管 |

| US8796777B2 (en) * | 2009-09-02 | 2014-08-05 | Qualcomm Incorporated | Fin-type device system and method |

| US9245805B2 (en) * | 2009-09-24 | 2016-01-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Germanium FinFETs with metal gates and stressors |

| US8431994B2 (en) * | 2010-03-16 | 2013-04-30 | International Business Machines Corporation | Thin-BOX metal backgate extremely thin SOI device |

| US8796759B2 (en) | 2010-07-15 | 2014-08-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin-like field effect transistor (FinFET) device and method of manufacturing same |

| US8728881B2 (en) | 2011-08-31 | 2014-05-20 | Institute of Microelectronics, Chinese Academy of Sciences | Semiconductor device and method for manufacturing the same |

| US8624326B2 (en) | 2011-10-20 | 2014-01-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET device and method of manufacturing same |

| US9099388B2 (en) | 2011-10-21 | 2015-08-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | III-V multi-channel FinFETs |

| US8853781B2 (en) | 2011-12-16 | 2014-10-07 | International Business Machines Corporation | Rare-earth oxide isolated semiconductor fin |

| WO2013101003A1 (en) | 2011-12-28 | 2013-07-04 | Intel Corporation | Techniques and configurations for stacking transistors of an integrated circuit device |

| US8836016B2 (en) | 2012-03-08 | 2014-09-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor structures and methods with high mobility and high energy bandgap materials |

| US9171929B2 (en) | 2012-04-25 | 2015-10-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strained structure of semiconductor device and method of making the strained structure |

-

2014

- 2014-02-12 US US14/179,311 patent/US9236483B2/en not_active Expired - Fee Related

-

2015

- 2015-02-11 CN CN201580007861.5A patent/CN105981174A/zh active Pending

- 2015-02-11 JP JP2016550526A patent/JP2017505545A/ja active Pending

- 2015-02-11 WO PCT/US2015/015426 patent/WO2015123305A1/en active Application Filing

- 2015-02-11 EP EP15706346.2A patent/EP3105796A1/en not_active Withdrawn

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002110963A (ja) * | 2000-09-28 | 2002-04-12 | Toshiba Corp | 半導体装置 |

| JP2007287913A (ja) * | 2006-04-17 | 2007-11-01 | Matsushita Electric Ind Co Ltd | 電界効果型トランジスタ及びその製造方法 |

| JP2013513250A (ja) * | 2009-12-23 | 2013-04-18 | インテル コーポレイション | 非平面ゲルマニウム量子井戸デバイス |

| US20130011983A1 (en) * | 2011-07-07 | 2013-01-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | In-Situ Doping of Arsenic for Source and Drain Epitaxy |

| US20130056795A1 (en) * | 2011-09-06 | 2013-03-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET Design Controlling Channel Thickness |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150228795A1 (en) | 2015-08-13 |

| EP3105796A1 (en) | 2016-12-21 |

| US9236483B2 (en) | 2016-01-12 |

| CN105981174A (zh) | 2016-09-28 |

| WO2015123305A1 (en) | 2015-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9236483B2 (en) | FinFET with backgate, without punchthrough, and with reduced fin height variation | |

| US10164099B2 (en) | Device with diffusion blocking layer in source/drain region | |

| US9773868B2 (en) | Nanowire MOSFET with support structures for source and drain | |

| TWI695507B (zh) | 結晶多奈米片iii-v族通道場效電晶體及其製造方法 | |

| US9437681B2 (en) | Dual channel FinFET CMOS device with common strain-relaxed buffer and method for manufacturing thereof | |

| US8987835B2 (en) | FinFET with a buried semiconductor material between two fins | |

| US9728602B2 (en) | Variable channel strain of nanowire transistors to improve drive current | |

| US8853862B2 (en) | Contact structures for semiconductor transistors | |

| US20110049613A1 (en) | Accumulation type finfet, circuits and fabrication method thereof | |

| CN108962749B (zh) | 绝缘栅双极晶体管器件和半导体器件 | |

| CN106471624B (zh) | 用于基于鳍状物的电子设备的固体源扩散结 | |

| US9620591B2 (en) | Semiconductor structures and methods for multi-level work function and multi-valued channel doping of nanowire transistors to improve drive current | |

| JP2018504775A (ja) | トンネル電界効果トランジスタ及びその製造方法 | |

| KR102441728B1 (ko) | 수직 전계 효과 장치 및 이의 제조 방법 | |

| US9502583B2 (en) | Complementary high mobility nanowire neuron device | |

| US10283639B2 (en) | Semiconductor structure and method for forming the same | |

| Goh et al. | Gate-all-around In 0.53 Ga 0.47 As junctionless nanowire FET with tapered source/drain structure | |

| US10297691B2 (en) | Method for forming semiconductor device with P/N stacked layers | |

| US8704296B2 (en) | Trench junction field-effect transistor | |

| US12113065B2 (en) | Fin-based field effect transistor (finFET) device with enhanced on-resistance and breakdown voltage | |

| CN209374452U (zh) | 一种tfet器件 | |

| TW202406095A (zh) | 具有碳摻雜釋放層的單體互補場效電晶體 | |

| CN111384146A (zh) | 一种tfet器件 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160815 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180122 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180122 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181017 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181105 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20190603 |