JP2014059874A - 連続撮影イメージデータを処理する方法と装置 - Google Patents

連続撮影イメージデータを処理する方法と装置 Download PDFInfo

- Publication number

- JP2014059874A JP2014059874A JP2013191525A JP2013191525A JP2014059874A JP 2014059874 A JP2014059874 A JP 2014059874A JP 2013191525 A JP2013191525 A JP 2013191525A JP 2013191525 A JP2013191525 A JP 2013191525A JP 2014059874 A JP2014059874 A JP 2014059874A

- Authority

- JP

- Japan

- Prior art keywords

- image data

- continuous shooting

- shooting image

- area

- storage device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

- 238000012545 processing Methods 0.000 title claims abstract description 50

- 238000000034 method Methods 0.000 title claims abstract description 46

- 238000012546 transfer Methods 0.000 claims description 55

- 230000004044 response Effects 0.000 claims description 14

- 230000003139 buffering effect Effects 0.000 claims description 3

- 238000005516 engineering process Methods 0.000 claims description 2

- 238000004519 manufacturing process Methods 0.000 claims description 2

- 239000000758 substrate Substances 0.000 claims 1

- 230000002159 abnormal effect Effects 0.000 description 8

- 238000013500 data storage Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 6

- 238000013507 mapping Methods 0.000 description 5

- 238000003384 imaging method Methods 0.000 description 4

- 238000004242 micellar liquid chromatography Methods 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 229920001621 AMOLED Polymers 0.000 description 2

- 238000005442 molecular electronic Methods 0.000 description 2

- 239000002071 nanotube Substances 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000004809 thin layer chromatography Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/76—Television signal recording

- H04N5/765—Interface circuits between an apparatus for recording and another apparatus

- H04N5/77—Interface circuits between an apparatus for recording and another apparatus between a recording apparatus and a television camera

- H04N5/772—Interface circuits between an apparatus for recording and another apparatus between a recording apparatus and a television camera the recording apparatus and the television camera being placed in the same enclosure

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/76—Television signal recording

- H04N5/907—Television signal recording using static stores, e.g. storage tubes or semiconductor memories

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Studio Devices (AREA)

- Memory System (AREA)

- Television Signal Processing For Recording (AREA)

- Image Input (AREA)

Abstract

【解決手段】それぞれの連続撮影イメージデータを生成するマルチプル連続撮影動作が実行される間に、イメージ処理システムに含まれ、第1メモリ領域と第2メモリ領域とを含むメモリアレイを含むフラッシュ保存装置の動作方法は、ホストから領域割り当て情報を受信する段階と、連続撮影動作が実行される間に、領域割り当て情報に基づいて、第1メモリ領域の一部を、連続撮影イメージデータを臨時保存するための専用連続撮影イメージデータバッファ領域に割り当てる段階と、正常プログラム動作中に、第2メモリ領域の一部を、正常データを保存するための正常データ領域に割り当てる段階と、を含み、第1メモリ領域は、第1速度で行われる正常プログラム動作を含むデータアクセス動作を支援し、第2メモリ領域は、第1速度よりも遅い第2速度で行われるデータアクセス動作を支援する。

【選択図】 図3

Description

カメラモジュールに含まれたカメラのピクセル(pixels)の数が増加するにつれて、イメージ解像度も増加する。多数のピクセルが、また向上した連続撮影機能を支援する。

また、特定のイメージ処理システムによってキャプチャされる連続撮影イメージの当該個数とRAMに保存された連続撮影イメージデータのライトブロックサイズだけではなく、連続撮影イメージデータ保存に割り当てられたRAMの専用部分のサイズが制限されるという問題もある。

前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む。前記フラッシュ保存装置の動作方法は、前記イメージ処理システムの初期化動作中に、前記ホストに含まれたメモリに前記領域割り当て情報を保存する段階をさらに含む。

前記フラッシュ保存装置は、前記ホストから受信されたSWITCH命令に応答して、前記領域割り当て情報を保存するVENDOR_SPECIFIC_FIELDフィールドを有するEXT_CSDレジスタを含むエンベデッドマルチメディアカードである。

前記フラッシュ保存装置は、前記プロセッサと共に前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータの前記プログラミングを制御するフラッシュコントローラとページバッファとを含む。前記移送命令は、連続撮影動作の実行後、一定の時間が経過した後、前記ホストから前記フラッシュ保存装置に伝送される。

前記RAMに前記連続撮影イメージデータを保存する段階は、前記マルチプル連続撮影動作が実行される間に、前記RAMに前記連続撮影イメージデータをバッファリングし、前記連続撮影イメージデータを前記RAMから前記フラッシュメモリ装置に伝送する。

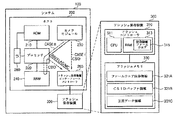

図1は、本発明の実施形態による1つ以上の連続撮影モードでの動作が可能なイメージ処理システムのブロック図を示す。イメージ処理システム100は、ホスト200とフラッシュ保存装置300とを含む。イメージ処理システム100は、パソコン、ラップトップコンピュータ、スマートフォン、タブレットPC、またはデジタルカメラなどの内にまたは一部として具現可能である。

ホスト200は、“連続撮影イメージデータ(continuous shootingimage data)”または“CSID”を生成する1つまたはそれ以上の連続撮影モードで動作する。連続撮影モードは、バーストモード(burst mode)、マルチショットモード(multi−shot mode)または連続ビデオモード(continuous video mode)などを含みうる。

ホスト200は、ROM(Read Only Memory)210、プロセッサ220、カメラモジュール230、RAM240、フラッシュ保存装置インターフェースコントローラ250、及びユーザインターフェース260を含む。ホスト200は、システム・オン・チップ(System on Chip;SoC)製造技術として具現可能である。連続撮影モードの間に、カメラモジュール230は、連続撮影イメージデータ(CSID)を多様に生成することができる。

ホスト200は、UI260の少なくとも一部をディスプレイするためのディスプレイ(図示せず)をさらに含みうる。このディスプレイは、TFT−LCD(Thin Film Transistor−Liquid Crystal Display)、LED(Light Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、AMOLED(Active−Matrix OLED)ディスプレイ、またはフレキシブルディスプレイ(Flexible Display)として具現可能である。

場合I(CASEI)または場合II(CASEII)で、イメージ処理システム100は、リアルタイムで、そして、相対的に高いデータ処理速度で不揮発性メモリ装置300への連続撮影イメージデータ(CSID)の保存に使われる。

その結果、ホスト200は、RAM240によって提供された特別な連続撮影イメージデータ保存容量と無関係に、カメラモジュール230によって提供された連続撮影イメージデータ(CSID)をリアルタイムでフラッシュ保存装置300に処理して保存することができる。

したがって、図1のようなイメージ処理システムは、連続撮影モード機能をユーザにさらに有用に提供することができる。

図1を再び参照すると、フラッシュ保存装置インターフェースコントローラ250は、フラッシュ保存装置300とホスト200との間でライト(write)動作中に、“ライトデータ”を通信し、リード(read)動作中に、“リードデータ”を通信することができる。

フラッシュメモリタイプ保存装置は、図1の実施形態と仮定されうるが、他のタイプの保存装置は、フラッシュメモリの代わりをするか、付け加えて使用される。

フラッシュ保存装置300は、シングルレベルメモリセル及び/またはトリプルレベルセル(Triple Level Cells;TLCs)及び/またはクワッドレベルセル(Quad Level Cells;QLCs)のようなマルチレベルメモリセル(Multi−Level Memory Cells)を含みうる。

連続撮影(CS)モードで、フラッシュコントローラ310は、メモリセルアレイ331内の多様なメモリ領域の定義と割り当て、連続撮影イメージデータ(CSID)の保存、及び移送命令(MC)の受信による移送動作の実行を制御することができる。例えば、フラッシュコントローラ310は、ホスト200から出力された移送命令(MC)を解析し、フラッシュメモリ330による相応する移送命令の実行を制御することができる。すなわち、フラッシュコントローラ310は、連続撮影イメージデータ(CSID)が割り当てされた連続撮影イメージデータメモリ領域に保存される間に、“正常連続撮影イメージデータ時間区間”のモニタに使われる。

図1のフラッシュメモリ330は、メモリアレイ331、制御ロジック回路333、及びページバッファ335を追加的に含む。

ファームウエア保存領域331AとCSIDバッファ領域331Bのそれぞれは、SLCを含みうる。逆に、正常データ領域331Cは、SLC及び/またはMLCを含みうる。

したがって、ファームウエア保存領域331AとCSIDバッファ領域331Bは、第1速度で実行されるデータアクセス動作を支援することができるフラッシュメモリ330の第1メモリ領域を形成し、正常データ領域331Cは、第2速度で実行されるデータアクセス動作を支援することができるフラッシュメモリ330の第2メモリ領域を形成する。ここで、第1速度は、第2速度よりも速い。

図2で、ファームウエア保存領域331A、CSIDバッファ領域331B、及び正常データ領域331Cのそれぞれは、1つまたはそれ以上の割り当てされたメモリブロック(memory block)を含み、各メモリブロックは、割り当てされた領域によってSLCまたはMLCを含みうる。

図2で、各SLCブロックと各MLCブロックは、複数のページ(pages)を含みうる。実施形態によって、特定のページは、共通ワードライン(common wordline)に沿って整列された複数のメモリセル(例えば、複数のSLCまたは複数のMLC)によって形成されうる。他の実施形態によって、ブロック(block)またはメモリブロックは、フラッシュメモリ装置のイレーズ(erase)単位であり、ページ(page)は、フラッシュメモリ装置のライト(プログラム)単位またはリード単位を意味する。

ページバッファ335は、データタイプ及び/または実行される動作のタイプによって、ホスト200から受信したプログラムデータ(すなわち、正常ライトデータまたは連続撮影イメージデータ(CSID))をフラッシュメモリ330の第1メモリ領域または第2メモリ領域にプログラムすることができる。

領域割り当て情報(RAI)に応答して、フラッシュコントローラ310で実行される保存装置ファームウエア315は、受信された領域割り当て情報(RAI)を解析し、1つまたはそれ以上のSLCメモリブロックを専用CSIDバッファ領域に割り当てる(ステップS103)。

すなわち、専用CSIDバッファ領域は、フラッシュメモリ330に保存された領域割り当て情報(RAI)またはEXT_CSDレジスタのVENDOR_SPECIFIC_FIELDフィールドによって割り当てられる。

前記標準は、http://www.jedec.orgに依頼して容易に得られる。例えば、eMMC標準、2012年6月(例えば、JESD84−B451)に発行されたバージョン(version)4.51は、本発明の実施形態を理解するための有用な多くの用語と技術的定義とを含んでいる。

しかし、正常な場合(NORMAL CASE)で、CSIDバッファ領域の残り(または、残存)のメモリ領域のサイズが、連続撮影イメージデータ(CSID)の保存に適切な時(S214=はい)には、フラッシュメモリコントローラ310は、現在連続撮影イメージデータバッファ領域値から連続撮影イメージデータサイズ値を減算して、新たな残りの連続撮影イメージデータバッファ領域値(Remained_CSIDBufferSize)を計算することができる(ステップS216)。

本発明の実施形態によって、フラッシュ保存装置300が、eMMCを用いて具現される時、連続撮影イメージデータフラグ(FLAG)は、命令CMD23を用いて伝送され、連続撮影イメージデータ(CSID)は、命令(CMD25)を用いて伝送することができる。

図1、図2、図3及び図6を参照すると、再割り当て動作は、ホストの連続撮影動作中に、容認されるライト性能を保持または保証するために、専用領域バッファ領域(CSIDBuffer)を必須的に初期化する。ここで、初期化は、CSDIバッファ領域を空に(empty)することを含む。すなわち、ホスト200によって連続撮影(CS)区間の間に、マルチプル、すなわち、連続して実行される連続撮影(CS)動作が行われる。

そして、フラッシュコントローラ310は、専用CSIDバッファ領域の現在割り当てされたサイズ(CSIDBufferSize)が受信された領域割り当て情報(RAI)に符合するか否かを判断する(ステップS314)。

したがって、最後の連続撮影動作を含むマルチプル連続撮影動作が、ホスト200によって行われる時、最後の連続撮影動作の結果として、ホスト200によって提供され、専用CSIDバッファ領域に書き込まれた連続撮影イメージデータ(CSID)は、所定の時間以内に移送命令が受信されないとしても、第2メモリ領域にフラッシュ保存装置300によってコピーされうる。

図8は、図6と図7との320段階、すなわち、専用CSIDバッファ領域から第2メモリ領域に連続撮影イメージデータを移送する段階を説明するフローチャートである。図6、図7、及び図8を参照すると、専用CSIDバッファ領域の残りの利用可能なメモリ領域のサイズ(Remained_CSIDBufferSize)を増やすために、専用CSIDバッファ領域に現在保存された連続撮影イメージデータ(CSID)の移送ユニット(MU)は、専用CSIDバッファ領域から第2メモリ領域に移送されうる(ステップS320)。

フラッシュコントローラ310は、プログラムされたデータのサイズ(P_DataSize)と移送ユニット(MU)とを比較することができる(ステップS320−6)。

フラッシュコントローラ310は、リードユニット(RU)だけプログラムされたデータのサイズ(P_DataSize)を増加させ、そして、ステップS320−6の段階を再び行うことができる。

図8、図9、及び図10を参照すると、プログラムされたデータのサイズ(P_DataSize)が、移送ユニット(MU)と同じか大きい時(ステップS320−6)、ソースブロックのデータは無効化され、ターゲットブロックに移送されたデータは有効化される(ステップS320−7)。図9と図10と参照すると、第1メモリ領域331Bの専用CSIDバッファ領域のソースブロックから移送ユニットだけ読み取られたイメージデータに対するアドレス領域と前記ソースブロックとのアドレスマッピングは、無効化され(ステップS320−7a)、第2メモリ領域331Cのターゲットブロックに移送ユニット(MU)だけ保存されたイメージデータに対するアドレス領域と前記ターゲットブロックとのアドレスマッピングは、有効化される(ステップS320−7b)。

200:ホスト

210:ROM

220:プロセッサ

230:カメラモジュール

240:RAM

250:フラッシュ保存装置インターフェースコントローラ

260:ユーザインターフェース

300:フラッシュ保存装置

310:フラッシュコントローラ

330:フラッシュメモリ

331A:ファームウエア保存領域

331B:連続撮影イメージデータバッファ領域

331C:正常データ領域

Claims (23)

- それぞれの連続撮影イメージデータを生成するマルチプル連続撮影動作が実行される間に、イメージ処理システムに含まれ、第1メモリ領域と第2メモリ領域とを含むメモリアレイを含むフラッシュ保存装置の動作方法において、

ホストから領域割り当て情報を受信する段階と、

前記連続撮影動作が実行される間に、前記領域割り当て情報に基づいて、前記第1メモリ領域の一部を、前記連続撮影イメージデータを臨時保存するための専用連続撮影イメージデータバッファ領域に割り当てる段階と、

正常プログラム動作中に、前記第2メモリ領域の一部を、正常データを保存するための正常データ領域に割り当てる段階と、を含み、

前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータアクセス動作を支援し、

前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援するフラッシュ保存装置の動作方法。 - 前記領域割り当て情報は、イメージ解像度設定、連続撮影フレームレート、及び連続撮影時間のうち少なくとも2つ、または連続撮影イメージデータ(CSID)バッファ領域サイズ値を含む請求項1に記載のフラッシュ保存装置の動作方法。

- 前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む請求項1に記載のフラッシュ保存装置の動作方法。

- 前記フラッシュ保存装置の動作方法は、前記イメージ処理システムの初期化動作中に、前記ホストに含まれたメモリに前記領域割り当て情報を保存する段階をさらに含む請求項1に記載のフラッシュ保存装置の動作方法。

- 前記フラッシュ保存装置は、前記ホストから受信されたSWITCH命令に応答して、前記領域割り当て情報を保存するVENDOR_SPECIFIC_FIELDフィールドを有するEXT_CSDレジスタを含むエンベデッドマルチメディアカードである請求項1に記載のフラッシュ保存装置の動作方法。

- 前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む請求項1に記載のフラッシュ保存装置の動作方法。 - 前記ホストは、プロセッサとカメラモジュールとを含み、前記フラッシュ保存装置は、eMMCであり、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含み、

前記連続撮影イメージデータフラグは、CMD23命令のcontext IDであって、前記ホストから前記eMMCに伝送され、前記連続撮影イメージデータは、CMD25命令のデータであって、前記ホストから前記eMMCに伝送される請求項1に記載のフラッシュ保存装置の動作方法。 - 前記フラッシュ保存装置の動作方法は、

前記マルチプル連続撮影動作のうち少なくとも1つを実行した後、移送命令を前記ホストから前記フラッシュ保存装置に伝送する段階と、

前記専用連続撮影イメージデータバッファ領域に保存された前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする前記移送命令に応答して移送動作を行う段階と、

をさらに含む請求項6に記載のフラッシュ保存装置の動作方法。 - 前記フラッシュ保存装置は、前記プロセッサと共に前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータの前記プログラミングを制御するフラッシュコントローラとページバッファとを含む請求項8に記載のフラッシュ保存装置の動作方法。

- 前記移送命令は、連続撮影動作の実行後、一定の時間が経過した後、前記ホストから前記フラッシュ保存装置に伝送される請求項8に記載のフラッシュ保存装置の動作方法。

- 前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータのサイズを指示する連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記連続撮影イメージデータのサイズと前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズとを比較する段階と、

前記連続撮影イメージデータのサイズが、前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズよりも小さいか同じである時、前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングし、そうではない時、前記プロセッサを用いて前記第2メモリ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む請求項1に記載のフラッシュ保存装置の動作方法。 - 前記RAMに前記連続撮影イメージデータを保存する段階は、

前記マルチプル連続撮影動作が実行される間に、前記RAMに前記連続撮影イメージデータをバッファリングし、前記連続撮影イメージデータを前記RAMから前記フラッシュメモリ装置に伝送する請求項11に記載のフラッシュ保存装置の動作方法。 - 連続撮影イメージデータを生成するホストと、

第1メモリ領域と第2メモリ領域とを含むメモリセルアレイを含むフラッシュ保存装置と、を含み、

前記第1メモリ領域の一部は、前記連続撮影イメージデータを一時的に保存する専用連続撮影イメージデータバッファ領域であり、前記第2メモリ領域は、正常プログラム動作中に、前記ホストから前記フラッシュ保存装置に提供される正常データを保存し、

前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータアクセス動作を支援し、

前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援するイメージ処理システム。 - 前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む請求項13に記載のイメージ処理システム。

- 前記ホストは、

プロセッサと、

前記連続撮影イメージデータを前記プロセッサに提供するカメラモジュールと、

前記イメージ処理システムによって実行される連続撮影動作のシーケンスの間に、リアルタイムで前記プロセッサから受信した前記連続撮影イメージデータをバッファリングするRAMと、

を含む請求項14に記載のイメージ処理システム。 - 前記フラッシュ保存装置は、前記プロセッサから受信した前記領域割り当て情報に応答して、前記第1メモリ領域に前記専用連続撮影イメージデータバッファ領域を定義するフラッシュコントローラを含む請求項15に記載のイメージ処理システム。

- 前記プロセッサは、前記ホストから前記フラッシュ保存装置に伝送されるデータが、前記連続撮影イメージデータであることを指示する連続撮影イメージデータフラグをさらに提供し、

前記フラッシュコントローラは、前記連続撮影イメージデータフラグに応答して、前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータを保存する請求項16に記載のイメージ処理システム。 - 前記フラッシュコントローラは、前記連続撮影イメージデータのサイズが、前記専用連続撮影イメージデータバッファ領域で残りの利用可能なメモリ領域のサイズよりも小さいか同じである時、前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータを保存し、そうではない時、前記フラッシュコントローラは、前記第2メモリ領域に前記連続撮影イメージデータを保存する請求項17に記載のイメージ処理システム。

- 前記プロセッサは、前記フラッシュ保存装置に移送命令をさらに提供し、前記移送命令に応答して、前記フラッシュコントローラは、前記専用連続撮影イメージデータバッファ領域に保存される前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする請求項16に記載のイメージ処理システム。

- 前記フラッシュコントローラは、連続撮影動作の実行後、所定の時間が経った後に、前記ホストから前記移送命令を受信できない時、前記専用連続撮影イメージデータバッファ領域に保存された前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする請求項19に記載のイメージ処理システム。

- 前記ホストは、前記カメラモジュールから前記連続撮影イメージデータを受信するか、前記プロセッサから前記連続撮影イメージデータを受信するフラッシュ保存装置インターフェースコントローラをさらに含む請求項20に記載のイメージ処理システム。

- 前記RAMは、DRAMである請求項20に記載のイメージ処理システム。

- 前記ホストと前記フラッシュ保存装置は、システム・オン・チップ(SoC)製造技術を使って共通基板上に製造される請求項22に記載のイメージ処理システム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2012-0102471 | 2012-09-14 | ||

| KR1020120102471A KR20140035769A (ko) | 2012-09-14 | 2012-09-14 | 연속 촬영 이미지 데이터를 처리할 수 있는 방법들과 장치들 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014059874A true JP2014059874A (ja) | 2014-04-03 |

| JP2014059874A5 JP2014059874A5 (ja) | 2016-10-06 |

Family

ID=50181954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013191525A Ceased JP2014059874A (ja) | 2012-09-14 | 2013-09-17 | 連続撮影イメージデータを処理する方法と装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20140078344A1 (ja) |

| JP (1) | JP2014059874A (ja) |

| KR (1) | KR20140035769A (ja) |

| CN (1) | CN103677666B (ja) |

| DE (1) | DE102013218440A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020003836A (ja) * | 2018-06-25 | 2020-01-09 | 日本精機株式会社 | 車両用表示装置 |

| JP2022078261A (ja) * | 2018-06-25 | 2022-05-24 | 日本精機株式会社 | 車両用表示装置 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106134174A (zh) * | 2014-03-28 | 2016-11-16 | 松下知识产权经营株式会社 | 摄像装置 |

| US9471254B2 (en) * | 2014-04-16 | 2016-10-18 | Sandisk Technologies Llc | Storage module and method for adaptive burst mode |

| KR102258772B1 (ko) * | 2014-10-01 | 2021-06-02 | 한국전자통신연구원 | 독출 회로 어레이 및 이를 포함하는 영상 장치 |

| KR102295223B1 (ko) * | 2015-01-13 | 2021-09-01 | 삼성전자주식회사 | 속도 모드 관리자를 포함하는 저장 장치 및 사용자 장치 |

| CN104902093B (zh) * | 2015-05-28 | 2017-09-01 | 广东欧珀移动通信有限公司 | 一种防止移动终端卡顿死机的方法及装置 |

| US10474570B2 (en) * | 2015-11-24 | 2019-11-12 | Cisco Technology, Inc. | Flashware usage mitigation |

| US10133509B2 (en) | 2016-01-06 | 2018-11-20 | International Business Machines Corporation | Consistency group abstraction |

| US10116743B2 (en) | 2016-01-06 | 2018-10-30 | International Business Machines Corporation | Storage capacity forecasting by capability sets |

| US10126975B2 (en) * | 2016-01-06 | 2018-11-13 | International Business Machines Corporation | Storage mirroring decision by capability sets |

| KR101809044B1 (ko) * | 2016-04-26 | 2017-12-14 | 주식회사 아이디스 | 프리-이벤트 순환 저장 방식 영상녹화장치 |

| TWI707230B (zh) * | 2018-11-22 | 2020-10-11 | 瑞昱半導體股份有限公司 | 電腦系統、記憶體管理方法與非暫態電腦可讀取媒體 |

| WO2020227997A1 (zh) * | 2019-05-15 | 2020-11-19 | 深圳市大疆创新科技有限公司 | 拍摄装置、无人飞行器、控制终端和拍摄方法 |

| CN114398001B (zh) * | 2021-12-03 | 2024-02-20 | 北京数字电视国家工程实验室有限公司 | 一种超大序列图像传输方法、装置以及计算机 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11234653A (ja) * | 1998-02-13 | 1999-08-27 | Optex Co Ltd | 映像監視システム |

| JP2007087149A (ja) * | 2005-09-22 | 2007-04-05 | Matsushita Electric Ind Co Ltd | データ記録装置 |

| JP2008071079A (ja) * | 2006-09-13 | 2008-03-27 | Toshiba Corp | メモリシステム |

| US20080172520A1 (en) * | 2007-01-17 | 2008-07-17 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices including multiple user-selectable program modes and related methods of operation |

| JP2009545783A (ja) * | 2006-07-31 | 2009-12-24 | 株式会社東芝 | 不揮発性メモリシステム、及びそのデータ読み出し/書き込み制御方法 |

| JP2010283809A (ja) * | 2009-05-01 | 2010-12-16 | Nikon Corp | データ記録装置およびデジタルカメラ |

| JP2012034352A (ja) * | 2010-06-30 | 2012-02-16 | Panasonic Corp | ステレオ動画像符号化装置及びステレオ動画像符号化方法 |

| US20120278347A1 (en) * | 2011-04-26 | 2012-11-01 | Research In Motion Limited | Fast estimation of binary data length using memory corruption |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5828578A (en) * | 1995-11-29 | 1998-10-27 | S3 Incorporated | Microprocessor with a large cache shared by redundant CPUs for increasing manufacturing yield |

| JP4189800B2 (ja) * | 2002-12-20 | 2008-12-03 | 富士フイルム株式会社 | 電子カメラ |

| JP4379728B2 (ja) * | 2005-01-31 | 2009-12-09 | カシオ計算機株式会社 | 撮像装置及びそのプログラム |

| US7852654B2 (en) * | 2006-12-28 | 2010-12-14 | Hynix Semiconductor Inc. | Semiconductor memory device, and multi-chip package and method of operating the same |

| US20090094678A1 (en) * | 2007-10-05 | 2009-04-09 | Nokia Corporation | Mulimode device |

| JP5066241B2 (ja) * | 2010-09-24 | 2012-11-07 | 株式会社東芝 | メモリシステム |

| WO2012069862A1 (en) * | 2010-11-24 | 2012-05-31 | Sony Ericsson Mobile Communications Ab | Dynamically configurable embedded flash memory for electronic devices |

-

2012

- 2012-09-14 KR KR1020120102471A patent/KR20140035769A/ko not_active Application Discontinuation

-

2013

- 2013-09-13 DE DE102013218440.9A patent/DE102013218440A1/de active Pending

- 2013-09-13 US US14/025,963 patent/US20140078344A1/en not_active Abandoned

- 2013-09-16 CN CN201310421872.0A patent/CN103677666B/zh active Active

- 2013-09-17 JP JP2013191525A patent/JP2014059874A/ja not_active Ceased

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11234653A (ja) * | 1998-02-13 | 1999-08-27 | Optex Co Ltd | 映像監視システム |

| JP2007087149A (ja) * | 2005-09-22 | 2007-04-05 | Matsushita Electric Ind Co Ltd | データ記録装置 |

| JP2009545783A (ja) * | 2006-07-31 | 2009-12-24 | 株式会社東芝 | 不揮発性メモリシステム、及びそのデータ読み出し/書き込み制御方法 |

| JP2008071079A (ja) * | 2006-09-13 | 2008-03-27 | Toshiba Corp | メモリシステム |

| US20080172520A1 (en) * | 2007-01-17 | 2008-07-17 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices including multiple user-selectable program modes and related methods of operation |

| JP2010283809A (ja) * | 2009-05-01 | 2010-12-16 | Nikon Corp | データ記録装置およびデジタルカメラ |

| JP2012034352A (ja) * | 2010-06-30 | 2012-02-16 | Panasonic Corp | ステレオ動画像符号化装置及びステレオ動画像符号化方法 |

| US20120278347A1 (en) * | 2011-04-26 | 2012-11-01 | Research In Motion Limited | Fast estimation of binary data length using memory corruption |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020003836A (ja) * | 2018-06-25 | 2020-01-09 | 日本精機株式会社 | 車両用表示装置 |

| JP7047628B2 (ja) | 2018-06-25 | 2022-04-05 | 日本精機株式会社 | 車両用表示装置 |

| JP2022078261A (ja) * | 2018-06-25 | 2022-05-24 | 日本精機株式会社 | 車両用表示装置 |

| JP7256976B2 (ja) | 2018-06-25 | 2023-04-13 | 日本精機株式会社 | 車両用表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140078344A1 (en) | 2014-03-20 |

| CN103677666B (zh) | 2017-12-05 |

| CN103677666A (zh) | 2014-03-26 |

| DE102013218440A1 (de) | 2014-03-20 |

| KR20140035769A (ko) | 2014-03-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2014059874A (ja) | 連続撮影イメージデータを処理する方法と装置 | |

| US11860774B2 (en) | User device including a nonvolatile memory device and a data write method thereof | |

| US20190179685A1 (en) | Solid state memory system with low power error correction mechanism and method of operation thereof | |

| US11132143B2 (en) | Universal flash storage (UFS) device and computing device and computing device including storage UFS device for reporting buffer size based on reuse time after erase | |

| US10846017B2 (en) | Secure digital (SD) to NVMe buffer manager | |

| TW201915734A (zh) | 用以在記憶裝置中進行存取管理的方法、相關記憶裝置及其控制器以及相關電子裝置 | |

| US10649692B2 (en) | Storage device, system including the same and method of operating the same | |

| JP2019105873A (ja) | メモリシステムおよび制御方法 | |

| CN109800187B (zh) | 被配置为更新现场可编程门阵列的存储设备及其操作方法 | |

| US10389380B2 (en) | Efficient data path architecture for flash devices configured to perform multi-pass programming | |

| JP2014059874A5 (ja) | ||

| JP2019105874A (ja) | 情報処理装置および方法 | |

| US20170269870A1 (en) | Memory controller, nonvolatile storage device, nonvolatile storage system, and memory control method | |

| TW201807562A (zh) | 資料儲存裝置 | |

| KR20140007990A (ko) | 불휘발성 램을 포함하는 사용자 장치 및 그것의 데이터 관리 방법 | |

| KR20190106005A (ko) | 메모리 시스템, 그것의 동작 방법 및 전자 장치 | |

| CN112052116A (zh) | 存储器系统、存储器控制器和元信息存储装置 | |

| US10372378B1 (en) | Replacement data buffer pointers | |

| US12189956B2 (en) | Optimized SSD for game loading and rendering | |

| US11119938B2 (en) | Apparatus and method to synchronize memory map between a storage device and host | |

| CN112306906A (zh) | 存储设备、包括该存储设备的存储系统及其操作方法 | |

| CN111338995A (zh) | 数据存储装置及操作数据存储装置的方法 | |

| US10146553B2 (en) | Electronic apparatus and booting method thereof | |

| US11625178B2 (en) | Storage device and method of operating the same | |

| KR20240019429A (ko) | 스토리지 장치 및 이를 포함하는 전자 장치와 그 동작 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160823 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160823 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20161222 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20161228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170609 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170620 |

|

| A045 | Written measure of dismissal of application [lapsed due to lack of payment] |

Free format text: JAPANESE INTERMEDIATE CODE: A045 Effective date: 20171031 |