JP2012242535A - 電気光学装置の製造方法 - Google Patents

電気光学装置の製造方法 Download PDFInfo

- Publication number

- JP2012242535A JP2012242535A JP2011111089A JP2011111089A JP2012242535A JP 2012242535 A JP2012242535 A JP 2012242535A JP 2011111089 A JP2011111089 A JP 2011111089A JP 2011111089 A JP2011111089 A JP 2011111089A JP 2012242535 A JP2012242535 A JP 2012242535A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- liquid crystal

- counter

- electro

- substrates

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 27

- 239000000758 substrate Substances 0.000 claims abstract description 216

- 239000004973 liquid crystal related substance Substances 0.000 claims abstract description 83

- 238000005520 cutting process Methods 0.000 claims abstract description 7

- 239000003566 sealing material Substances 0.000 claims description 23

- 238000007689 inspection Methods 0.000 claims description 18

- 238000000034 method Methods 0.000 description 61

- 230000008569 process Effects 0.000 description 29

- 239000010408 film Substances 0.000 description 20

- 230000007547 defect Effects 0.000 description 15

- 239000000523 sample Substances 0.000 description 15

- 238000003860 storage Methods 0.000 description 11

- 239000003990 capacitor Substances 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 239000000047 product Substances 0.000 description 4

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000002950 deficient Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- 238000001179 sorption measurement Methods 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 210000000078 claw Anatomy 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 229920006015 heat resistant resin Polymers 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000001579 optical reflectometry Methods 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 239000011265 semifinished product Substances 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 229920001169 thermoplastic Polymers 0.000 description 1

- 239000004416 thermosoftening plastic Substances 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

【課題】高い生産性と歩留まりとを実現可能な電気光学装置の製造方法を提供すること。

【解決手段】本適用例の電気光学装置としての液晶装置の製造方法は、チップ状の素子基板10とチップ状の対向基板20とが貼り合わされてなる液晶装置を複数製造する液晶装置の製造方法であって、複数の対向基板20を保持部201上に位置決めして保持する対向基板保持工程と、素子基板10を複数切り出すことができるマザー基板110を用意し、マザー基板110の複数の素子基板10となる領域に、複数の対向基板20を同時に貼り合わせる貼り合わせ工程と、を備えた。

【選択図】図6

【解決手段】本適用例の電気光学装置としての液晶装置の製造方法は、チップ状の素子基板10とチップ状の対向基板20とが貼り合わされてなる液晶装置を複数製造する液晶装置の製造方法であって、複数の対向基板20を保持部201上に位置決めして保持する対向基板保持工程と、素子基板10を複数切り出すことができるマザー基板110を用意し、マザー基板110の複数の素子基板10となる領域に、複数の対向基板20を同時に貼り合わせる貼り合わせ工程と、を備えた。

【選択図】図6

Description

本発明は、電気光学装置の製造方法に関する。

電気光学装置として、一対の基板間に電気光学物質としての液晶が挟持され、一対の基板のうちの一方に画素電極と、画素電極をスイッチング制御するトランジスターとを備えたアクティブ駆動型の液晶装置が知られている。

このような液晶装置の製造方法としては、一般的に一対の基板のそれぞれが複数面付けされたマザー基板が用いられる。そして、一方のマザー基板に個々の液晶装置に対応させてシール材を配置し、配置されたシール材を土手としてその内側に所定量の液晶を滴下した後に、他方のマザー基板とシール材を介して貼り合わせる方法が開示されている(特許文献1)。

一対のマザー基板を用いて液晶装置を製造する場合、一方のマザー基板における端子部を露出させるために、当該端子部を覆う他方のマザー基板の部分を分離して除去しなくてはならない。上記特許文献1では、上記除去が必要な部分を挟んだ両側にダイシングにより溝を形成し、一方の溝に空気を吹き込みつつ、他方の溝側から吸引してブレイクし除去している。

しかしながら、マザー基板自体に厚みのばらつきがあり、貼り合わせた後の一対のマザー基板の総厚もばらつくことになるので、上記除去が必要な部分に対してダイシングにより一定の深さの溝を形成することは非常に難しい。溝の深さがばらつくと、容易に除去ができないばかりか、ブレイク不良が発生するおそれがある。

上記ブレイク不良の発生を完全に防止するために、一対の基板のうち一方をマザー基板化し、他方は予め成形された基板を1つずつマザー基板に貼り付ける方法が考えられるが、この方法では生産性が低くなってしまうという課題があった。

しかしながら、マザー基板自体に厚みのばらつきがあり、貼り合わせた後の一対のマザー基板の総厚もばらつくことになるので、上記除去が必要な部分に対してダイシングにより一定の深さの溝を形成することは非常に難しい。溝の深さがばらつくと、容易に除去ができないばかりか、ブレイク不良が発生するおそれがある。

上記ブレイク不良の発生を完全に防止するために、一対の基板のうち一方をマザー基板化し、他方は予め成形された基板を1つずつマザー基板に貼り付ける方法が考えられるが、この方法では生産性が低くなってしまうという課題があった。

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

[適用例1]本適用例の電気光学装置の製造方法は、チップ状の素子基板とチップ状の対向基板とが貼り合わされてなる電気光学装置を複数製造する電気光学装置の製造方法であって、複数の前記対向基板を保持部上に位置決めして保持する対向基板保持工程と、前記素子基板を複数切り出すことができるマザー基板を用意し、前記マザー基板の複数の前記素子基板となる領域に、複数の前記対向基板を同時に貼り合わせる貼り合わせ工程と、を備えることを特徴とする。

この方法によれば、貼り合わせ工程において、複数の素子基板に対して複数の対向基板を同時に貼り合わせるので、複数の素子基板に対して1つずつ対向基板を貼り合わせる場合に比べて、貼り合わせ作業の生産性を高めることができる。また、対向基板を素子基板に貼り合わせた後にブレイク(切断分離)する必要がないので、ブレイク不良の発生を防止できる。

[適用例2]上記適用例の電気光学装置の製造方法において、前記貼り合わせ工程の後に、前記マザー基板における前記素子基板の端子部に電気信号を入力させて電気光学装置を駆動させ、個々の電気光学装置の電気特性を検査する検査工程と、前記検査工程の後に前記マザー基板を切断して個々の電気光学装置を取り出す工程と、を備えることを特徴とする。

この方法によれば、マザー基板に面付けされた素子基板に対向基板を貼り合わせ、半完成品となった電気光学装置に対して、マザー基板を単位として個々の電気光学装置の検査を行うことができる。そして、次工程のマザー基板の切断後には、電気特性における良品と不良品とを容易に区分けすることができる。

言い換えれば、切断して個々に取り出した電気光学装置を1つずつ検査する場合に比べて、検査工程や切断工程における製品の取り扱い性などが向上して生産性を高めることができる。

この方法によれば、マザー基板に面付けされた素子基板に対向基板を貼り合わせ、半完成品となった電気光学装置に対して、マザー基板を単位として個々の電気光学装置の検査を行うことができる。そして、次工程のマザー基板の切断後には、電気特性における良品と不良品とを容易に区分けすることができる。

言い換えれば、切断して個々に取り出した電気光学装置を1つずつ検査する場合に比べて、検査工程や切断工程における製品の取り扱い性などが向上して生産性を高めることができる。

[適用例3]上記適用例の電気光学装置の製造方法において、前記対向基板保持工程は、前記保持部の一方の表面に前記対向基板を静電吸着させて固定することを特徴とする。

この方法によれば、真空吸着して固定する場合に比べて、対向基板の吸着時における変形を抑えて、位置精度よく素子基板と対向基板とを貼り合わせることができる。

この方法によれば、真空吸着して固定する場合に比べて、対向基板の吸着時における変形を抑えて、位置精度よく素子基板と対向基板とを貼り合わせることができる。

[適用例4]上記適用例の電気光学装置の製造方法において、前記マザー基板における前記素子基板ごとにシール材を配置する工程を備え、前記貼り合わせ工程は、前記素子基板ごとに配置された前記シール材の内側に所定量の液晶を滴下する工程を含むことを特徴とする。

この方法によれば、ブレイク不良の発生が低減されると共に、製品の取り扱い性が向上し高い生産性を有する電気光学装置としての液晶装置の製造方法を提供することができる。

この方法によれば、ブレイク不良の発生が低減されると共に、製品の取り扱い性が向上し高い生産性を有する電気光学装置としての液晶装置の製造方法を提供することができる。

以下、本発明を具体化した実施形態について図面に従って説明する。なお、使用する図面は、説明する部分が認識可能な状態となるように、適宜拡大または縮小して表示している。

なお、以下の形態において、例えば「基板上に」と記載された場合、基板の上に接するように配置される場合、または基板の上に他の構成物を介して配置される場合、または基板の上に一部が接するように配置され、一部が他の構成物を介して配置される場合を表すものとする。

本実施形態では、薄膜トランジスター(Thin Film Transistor;TFT)を画素のスイッチング素子として備えた電気光学装置としてのアクティブ駆動型の液晶装置を例に挙げて説明する。この液晶装置は、例えば投射型表示装置(液晶プロジェクター)の光変調素子(液晶ライトバルブ)として好適に用いることができるものである。

<液晶装置>

本実施形態の電気光学装置としての液晶装置について、図1および図2を参照して説明する。図1(a)は液晶装置の構成を示す概略平面図、同図(b)は同図(a)のH−H’線で切った概略断面図、図2は液晶装置の電気的な構成を示す等価回路図である。

本実施形態の電気光学装置としての液晶装置について、図1および図2を参照して説明する。図1(a)は液晶装置の構成を示す概略平面図、同図(b)は同図(a)のH−H’線で切った概略断面図、図2は液晶装置の電気的な構成を示す等価回路図である。

図1(a)および(b)に示すように、本実施形態の液晶装置100は、対向配置された一対の基板としての素子基板10および対向基板20と、素子基板10と対向基板20との間に挟持された液晶層50とを有する液晶パネル120を備えている。素子基板10および対向基板20は、例えば透明な石英などからなる基板であり、例えば熱硬化型または紫外線硬化型の接着剤からなるシール材52によって貼り合わされている。

液晶装置100は、表示領域10a内にマトリクス状の配置された複数の画素103を有する。素子基板10上には画素103を構成する、例えばITO(Indium Tin Oxide)などの透明電極からなる画素電極9と、画素電極9を駆動制御するスイッチング素子としての薄膜トランジスター(TFT;Thin Film Transistor)30とが設けられている。また、これら画素電極9などを覆う配向膜16が設けられている。

対向基板20の液晶層50に面する側には、ほぼ全面に例えばITOなどの透明電極からなる対向電極21と、対向電極21を覆う配向膜22が設けられている。

また、対向基板20には、液晶層50に向かって対向電極21の下(図面では上方)に画素103を格子状に区画する遮光膜23と、表示領域10aの周辺部に配置された遮光膜53とが設けられている。遮光膜23,53は、例えば遮光性を有するCrなどの金属や金属酸化物などの無機化合物、あるいは遮光性を有する有機化合物を用いて形成されている。

素子基板10と対向基板20とを接合するシール材52は、対向基板20の辺部に沿って額縁状に設けられている。シール材52の内側に液晶が充填され両基板間に封着されている。シール材52は、所定の径を有する例えば球状のギャップ材を含んでおり、対向配置された素子基板10と対向基板20との隙間を一定に保つことにより液晶層50の厚みを規定している。

素子基板10は対向基板20に比べて一回り大きく、対向基板20から突出した一辺部には、データ線駆動回路101と、複数の外部接続端子102とが設けられている。

素子基板10のシール材52の内側には、表示領域10aを挟んで一対の走査線駆動回路104と、この間を繋ぐ配線105とが設けられている。対向基板20の遮光膜53は、平面的に走査線駆動回路104に重なるように設けられている。

素子基板10のシール材52の内側には、表示領域10aを挟んで一対の走査線駆動回路104と、この間を繋ぐ配線105とが設けられている。対向基板20の遮光膜53は、平面的に走査線駆動回路104に重なるように設けられている。

素子基板10と対向基板20との間には、シール材52の4つのコーナー部に上下導通材106が配設されており、同じく上下導通材106に対応して配設された上下導通端子107により、対向基板20側の対向電極21が素子基板10側に電気的に導かれ、複数の外部接続端子102のうちの指定された端子に接続されている。

このような液晶装置100は、液晶パネル120の光の入射側と射出側とに光学部材としての偏光板(図示省略)が配置されて用いられる。

液晶パネル120における光学設計は、非駆動時に画素103が白表示となるノーマリーホワイトモードや、同じく非駆動時に画素103が黒表示となるノーマリーブラックモードの表示方式を適用することができる。

例えば、ノーマリーホワイトモードの代表的な光学設計としては、正の誘電異方性を有する液晶を用い、上記光の入射側と射出側の偏光板をクロスニコルに配置する。非駆動時に一方の偏光板を透過した光(直線偏光)が液晶層50により90度旋光して他方の偏光板を透過するように、ポリイミド樹脂などの有機材料からなる配向膜16,22をラビングして、その表面における配向処理方向が互いに直交する配向処理を施す方法が挙げられる。

また例えば、ノーマリーブラックモードの代表的な光学設計としては、負の誘電異方性を有する液晶を用い、ノーマリーホワイトモードの例と同じく偏光板をクロスニコルに配置する。非駆動時に一方の偏光板を透過した光(直線偏光)が液晶層50をそのまま通過して他方の偏光板により吸収されるように配向処理を施す。より具体的には、配向膜16,22を、その表面近傍における液晶分子が所定のチルト角を有して配向するように、酸化シリコンなどの無機材料を斜方蒸着して形成する方法が挙げられる。

図2に示すように、液晶装置100の表示領域10aを構成する各画素103は、画素電極9と画素電極9をスイッチング制御するためのTFT30とを有している。また、走査線3aと並行して配置された共通線3bを有している。なお、図示省略したが、前述したように画素電極9と対向電極21との間に液晶層50が存在する。

データ線駆動回路101から延びるデータ線6がTFT30のソースと電気的に接続されている。データ線駆動回路101は、画像信号D1,D2,…,Dnを、データ線6を介して各画素103に供給する。画像信号D1〜Dnはこの順に線順次に供給しても構わないし、隣り合う複数のデータ線6同士に対して、グループごとに供給するようにしてもよい。

また、TFT30のゲートには、走査線駆動回路104から延びる走査線3aが電気的に接続されている。走査線駆動回路104から所定のタイミングで走査線3aにパルス的に供給される走査信号G1,G2,…,Gmが、この順に線順次でTFT30のゲートに印加されるようになっている。画素電極9は、TFT30のドレインに電気的に接続されている。

スイッチング素子であるTFT30が走査信号G1,G2,…,Gmの入力により一定期間だけオン状態とされることで、データ線6から供給される画像信号D1,D2,…,Dnが所定のタイミングで画素電極9に書き込まれて表示が行われる。画素電極9を介して液晶層50に書き込まれた所定レベルの画像信号D1,D2,…,Dnは、共通線3bとドレインとの間に設けられた蓄積容量40の作用により一定期間保持される。すなわち、蓄積容量40は画素電極9における表示状態を一定期間保持するための保持容量として機能するものである。

<液晶装置の製造方法>

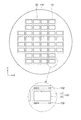

次に、本実施形態の電気光学装置の製造方法としての液晶装置の製造方法について、図3〜図9を参照して説明する。図3は液晶装置の製造方法を示すフローチャート、図4はマザー基板における素子基板の配置を示す概略平面図、図5(a)および(b)は保持部における対向基板の配置を示す概略平面図、図6は貼り合わせ工程を示す概略図、図7は貼り合わせ後のマザー基板を示す概略平面図、図8(a)および(b)は検査工程を示す概略図、図9(a)および(b)は実装工程を示す概略図である。

次に、本実施形態の電気光学装置の製造方法としての液晶装置の製造方法について、図3〜図9を参照して説明する。図3は液晶装置の製造方法を示すフローチャート、図4はマザー基板における素子基板の配置を示す概略平面図、図5(a)および(b)は保持部における対向基板の配置を示す概略平面図、図6は貼り合わせ工程を示す概略図、図7は貼り合わせ後のマザー基板を示す概略平面図、図8(a)および(b)は検査工程を示す概略図、図9(a)および(b)は実装工程を示す概略図である。

図3に示すように、本実施形態の液晶装置の製造方法は、素子基板10にTFT30や蓄積容量40などの素子やこれに繋がる配線等を形成する素子形成工程(ステップS1)と、画素電極9を形成する画素電極形成工程(ステップS2)と、画素電極9を覆って配向膜を形成し配向処理を施す配向処置工程(ステップS3)と、素子基板10にシール材52を配置するシール形成工程(ステップS4)とを備えている。また、対向基板20に遮光膜23,53を覆って対向電極21を形成する対向電極形成工程(ステップS5)と、少なくとも対向電極21を覆って配向膜22を形成し配向処理を施す配向処理工程(ステップS6)と、対向基板20を保持部に位置決めして保持する対向基板保持工程(ステップS7)とを備えている。また、シール材52が配置された素子基板10と対向基板20との間に液晶を充填して、シール材52を介して両基板を貼り合わせる貼り合わせ工程(ステップS8)と、素子基板10と対向基板20とが貼り合わされて得られた液晶パネル120の電気特性を検査する検査工程(ステップS9)と、スクライブ・ブレイク工程(ステップS10)と、液晶パネル120に各種の部品を実装する実装工程(ステップS11)とを備えている。

本実施形態における液晶装置100の製造方法では、図4に示すように、石英からなるウェハー状のマザー基板110を用いる。マザー基板110の大きさは例えば直径が8インチ、厚みが1mm程度のものが用いられる。チップ状の素子基板10は対角線の長さが1インチ未満の例えば長方形であって、マザー基板110から複数切り出すことができるようになっている。

つまり、上記ステップS1の素子形成工程からステップS3の配向処理工程では、マザー基板110を用いて、その一方の表面にTFT30や蓄積容量40をはじめ、これらの素子に接続される配線、そして画素電極9や配向膜16が素子基板10ごとに形成される。これらの構成を形成する方法は、公知の方法を用いることができる。

次に、ステップS4のシール形成工程では、図1に示すように、表示領域10aを囲むようにシール材52がマザー基板110の素子基板10ごとに配置される。シール材52は、熱硬化性の接着剤を用いることも可能ではあるが、本実施形態では、素早い接着性(封着性)を考慮して、紫外線硬化型の接着剤を使用している。環状にシール材52を配置する方法としては、配向膜16に触れないようにしてシール材52を配置可能であることから定量吐出器(ディスペンサー)を用いて描画する方法が採用されている。

一方、対向基板20は、外形が予め整えられたチップ状の基板本体が用意され、ステップS5の対向電極形成工程では、遮光膜23,53を覆うように例えばITOなどの透明導電膜が成膜され、これをパターニングすることによって対向電極21が形成される。続いて、ステップS6の配向処理工程では、少なくとも対向電極21を覆う配向膜22が形成される。遮光膜23,53をはじめとして、これらの構成を形成する方法も、公知の方法を用いることができる。

次に、ステップS7の対向基板保持工程では、図5(a)および(b)に示すように、保持部201の一方の表面に複数の対向基板20を位置決めして保持する。具体的には、保持部201は円盤状の静電チャックであって、電荷を発生させる電極をセラミックスなどの絶縁体で挟んだ構造となっている。マザー基板110における素子基板10の面付け位置に対応して、配向膜22が形成された面を上にして、帯電させた対向基板20をそれぞれ保持部201の所定の位置に静電吸着させ固定させる。

例えば、図6に示すように、ロボットアーム210の先端に把持部を有する例えばスカラロボットを用い、把持部により配向膜22に触れないように対向基板20を挟んで、予め記憶された座標データに基づいて保持部201上に間隔を置いて静電吸着させる。対向基板20を1つずつ吸着固定させてもよいし、把持部の構成の仕方によっては、複数の対向基板20を把持して吸着固定させることも可能である。

次に、ステップS8の貼り合わせ工程は、マザー基板110において素子基板10ごとに、シール材52で囲まれた領域に所定量の液晶を滴下する工程と、素子基板10ごとまたは対向基板20ごとに上下導通材106を所定の位置に塗布する工程と、マザー基板110つまり複数の素子基板10に対して複数の対向基板20を同時に貼り合わせる工程とを含むものである。

具体的には、図6に示すような組立装置200を用いて、両基板を貼り合わせる。組立装置200は、2つのロボット機構(図示省略)を備えたものであって、1つは、前述したように対向基板20を把持して、静電チャックである円盤状の保持部201に位置決め可能なロボットアーム210を有する例えばスカラロボットである。もう1つは、対向基板20が位置決め保持された保持部201を反転させ、テーブル202上に固定されたマザー基板110に対して所定の位置で対向配置させ、保持部201をテーブル202に近づけることにより対向基板20を素子基板10に押し当てて貼り合わせるロボット機構(図示省略)である。

なお、組立装置200は、2つのロボット機構により構成されるものに限定されず、対向基板20の移載に用いられたロボットアーム210を利用して、保持部201を反転させると共に、マザー基板110に対して押し当てるようにすれば、1つのロボット機構でも組立装置200を構成することができる。

なお、組立装置200は、2つのロボット機構により構成されるものに限定されず、対向基板20の移載に用いられたロボットアーム210を利用して、保持部201を反転させると共に、マザー基板110に対して押し当てるようにすれば、1つのロボット機構でも組立装置200を構成することができる。

テーブル202は、例えば透明なガラスなどの材料を用いて製作されており、その表面にマザー基板110を真空吸着可能な構成を備えている。また、テーブル202の下方には、素子基板10と対向基板20とを正確な位置で貼り合わせることができるように、素子基板10と対向基板20とに設けられた合わせマークを撮像可能なカメラ203が設けられている。また、貼り合わせられた素子基板10(マザー基板110)に対して紫外線を照射する光源204が設けられている。これにより、素子基板10と対向基板20とを正確に貼り合わせすることができると共に、素早くシール材52を硬化させることができる。なお、カメラ203が捉えた合わせマークの映像に基づいて、上記ロボット機構の動きを制御可能であることは言うまでもない。

このような組立装置200は、例えば減圧可能なチャンバー内に設置され、減圧下で液晶が滴下された素子基板10(マザー基板110)に対して対向基板20が貼り合わされて接着される。このように減圧下において一対の基板間に液晶を封着する方法は、ODF(One Drop Fill)と呼ばれている。

なお、紫外線硬化型のシール材52を用いた場合、素子基板10と対向基板20との接着をより完全なものとすべく、さらに硬化を促進させる本硬化工程を設けてもよい。本硬化工程は、さらなる紫外線の照射だけでなく、熱を加えて硬化を促進する方法が挙げられる。

なお、紫外線硬化型のシール材52を用いた場合、素子基板10と対向基板20との接着をより完全なものとすべく、さらに硬化を促進させる本硬化工程を設けてもよい。本硬化工程は、さらなる紫外線の照射だけでなく、熱を加えて硬化を促進する方法が挙げられる。

こうして組み立てられたマザー基板110は、図7に示すように、面付けされた素子基板10ごとに対向基板20が所定の位置に接合されて、個々の液晶パネル120を構成する。ゆえに、素子基板10側に設けられた外部接続端子102は、個々の液晶パネル120の配置に従って、一定の間隔で同じくX方向とY方向とにマトリクス状に配置された状態となっている。

次に、ステップS9の検査工程では、マザー基板110上に構成された個々の液晶パネル120の電気特性を検査する。具体的には、図8(a)に示すような、検査装置300を用いる。

検査装置300は、組み立てられたマザー基板110が載置されるステージ301と、検査用の複数のプローブ304が所定の位置に取り付けられたプローブカード302と、可撓性を有する配線ケーブル305を経由して各プローブ304に駆動信号を送出するチェッカー303とを備えている。

ステージ301は円柱状となっており、上面に載置されたマザー基板110を吸着固定可能な構成となっている。また、載置されたマザー基板110を所定の温度に加温可能な加温手段として例えば電気ヒーターを内蔵している。

プローブカード302は例えばセラミック基板やガラスエポキシ積層板などの絶縁基板からなり、外形がマザー基板110と同様に円盤状に加工されている。プローブカード302には、図8(b)に示すように、各液晶パネル120の外部接続端子102の配置に対応して、これに接触し電気的な導通を図るべく、複数のプローブ304がプローブカード302を貫通して接触針が下方に突出するように設けられている。

プローブカード302とマザー基板110とは予め位置決めされており、この場合、ステージ301がプローブカード302に向かって上昇することにより、外部接続端子102とプローブ304とを接触させ導通させるようになっている。なお、ステージ301側を固定し、プローブカード302側をステージ301に向かって下降させて、外部接続端子102とプローブ304とを接触させ導通させる構成としてもよい。また、図8(a)では簡略化して図示しているが、マザー基板110の各液晶パネル120に対応して、複数のプローブ304がプローブカード302に設けられている。

外部接続端子102とプローブ304との導通が確認されると、チェッカー303から外部接続端子102ごとに定められた駆動信号が送出され、マザー基板110上の液晶パネル120に通電が行われる。通電された個々の液晶パネル120の状態を例えば作業者が観察することによって、所望の電気特性が得られるか否かを判断する。あるいは、チェッカー303自体に駆動信号の伝達状態を判断させる構成としてもよい。液晶パネル120の透過率を測定することによって判断可能な駆動電圧特性やコントラストなどは別途計測器を用いる構成としてもよい。少なくとも致命的な不良である、画素欠陥や電気的な短絡を検出可能な駆動信号の伝達方法となっている。致命的な不良が発見された場合には、当該液晶パネル120にマーキングを施して、他の良品の液晶パネル120と区分可能な状態としておく。

次に、ステップS10のスクライブ・ブレイク工程では、図7において破線で示した素子基板10の外形線に沿ってマザー基板110をスクライブ・ブレイクすることにより、個々の液晶パネル120を取り出す。不良な液晶パネル120は、前工程でマーキングされているので、この時点ですぐさま取り除くことができる。なお、個々の液晶パネル120をマザー基板110から取り出す方法は、スクライブ・ブレイクに限らず、例えばダイシングによる切断や、レーザーによる切断を用いてもよい。

次に、ステップS11の実装工程では、まず、図9(a)に示すように、素子基板10の外部接続端子102が設けられた端子部に、外部回路との接続を可能とする中継基板130が実装される。中継基板130は、例えばFPC(フレキシブルプリントサーキット)であり、熱可塑性のACF(異方性導電フィルム)などを用いて上記端子部に熱圧着され、電気的に接続される。

また、液晶パネル120の光の入射側と射出側とに可視光波長域において透明性を有する基板140,150が配置される。これらの基板140,150は、防塵基板と呼ばれるものであって、ライトバルブとして拡大投射されるときに液晶パネル120の表面に付着した粉塵に焦点が結ばれることを防止して、表示品質を確保するものである。したがって、ある程度の厚みを有することが好ましく、この場合、厚みがおよそ1.0mmである。

また、液晶パネル120の光の入射側と射出側とに可視光波長域において透明性を有する基板140,150が配置される。これらの基板140,150は、防塵基板と呼ばれるものであって、ライトバルブとして拡大投射されるときに液晶パネル120の表面に付着した粉塵に焦点が結ばれることを防止して、表示品質を確保するものである。したがって、ある程度の厚みを有することが好ましく、この場合、厚みがおよそ1.0mmである。

実際には、図9(b)に示すように、例えば、耐熱性を有する樹脂製の収納ケース170に対して基板140、液晶パネル120、基板150の順にセットされ、収納ケース170の内壁との間で接着固定される。さらに、平面的に表示領域10a(図1参照)の大きさに相当する開口部160aを有する金枠160が装着される。金枠160は収納ケース170側に折れ曲がった一対の脚部161を有している。一対の脚部161にも開口部162がそれぞれ設けられており、収納ケース170の側面171に設けられたツメ172と嵌合して、金枠160が収納ケース170に固定される。なお、図示省略したが、液晶パネル120が収納される収納ケース170の底面には、金枠160に設けられた開口部160aと同様に光が通過する開口部が設けられている。

このようにして製造された液晶装置100は、再び駆動され表示検査を行って実装工程に起因するところの不具合が検出される。液晶パネル120はウェハー状態で検査が行われ少なくとも致命的な不良が除かれてから、実装工程に投入されるので、実装工程で余計な表示不良が発生することが低減される。つまり、各種の部品が実装され付加価値が付いた状態で不良(損失)が発生することが低減される。

上記実施形態によれば、以下のような効果が得られる。

(1)液晶装置100の製造方法において、貼り合わせ工程(ステップS8)では、素子基板10が複数面付けされたマザー基板110に対して、複数の対向基板20が一方の表面に保持された保持部201を押し当てることにより、複数の素子基板10に対して複数の対向基板20を同時に貼り合わせる。したがって、対向基板20を1つずつ素子基板10に貼り合わせる場合に比べて、効率よく両基板を貼り合わせることができる。

(2)また、対向基板20は予め成形されたものであるため、対向基板20が複数面付けされた対向マザー基板と、素子基板10が複数面付けされたマザー基板110とを貼り合わせる場合に比べて、端子部を覆う不要な部分を除去する必要がないので、当該不要な部分の除去に伴って発生する不良を防止することができる。つまり、歩留まりよく液晶装置100を製造することができる。

(3)加えて、対向基板20が貼り付けられたマザー基板110における個々の液晶パネル120の電気特性を検査する検査工程(ステップS9)を備えている。したがって、個々の液晶パネル120の検査をウェハー状態で実施できるので、個別に検査する場合に比べて取り扱いが容易になり、検査工数を削減できる。

さらには、検査工程で発見された不良にマーキングを施しておくことにより、スクライブ・ブレイク工程後に、不良をすぐさま排除できる。すなわち、実装工程に不良が送られないので、各種の部品が液晶パネル120に実装され、付加価値が付いた状態で不良が発生することを低減できる。

(4)複数の対向基板20を保持する保持部201は、静電チャック方式が採用されているので、真空吸着方式に比べて、対向基板20の吸着による変形が抑えられる。また、対向基板20の大きさが変化したとしても、所望の位置に吸着固定できる。言い換えれば、サイズが異なる液晶パネル120の組立にも柔軟に対応できる。

(1)液晶装置100の製造方法において、貼り合わせ工程(ステップS8)では、素子基板10が複数面付けされたマザー基板110に対して、複数の対向基板20が一方の表面に保持された保持部201を押し当てることにより、複数の素子基板10に対して複数の対向基板20を同時に貼り合わせる。したがって、対向基板20を1つずつ素子基板10に貼り合わせる場合に比べて、効率よく両基板を貼り合わせることができる。

(2)また、対向基板20は予め成形されたものであるため、対向基板20が複数面付けされた対向マザー基板と、素子基板10が複数面付けされたマザー基板110とを貼り合わせる場合に比べて、端子部を覆う不要な部分を除去する必要がないので、当該不要な部分の除去に伴って発生する不良を防止することができる。つまり、歩留まりよく液晶装置100を製造することができる。

(3)加えて、対向基板20が貼り付けられたマザー基板110における個々の液晶パネル120の電気特性を検査する検査工程(ステップS9)を備えている。したがって、個々の液晶パネル120の検査をウェハー状態で実施できるので、個別に検査する場合に比べて取り扱いが容易になり、検査工数を削減できる。

さらには、検査工程で発見された不良にマーキングを施しておくことにより、スクライブ・ブレイク工程後に、不良をすぐさま排除できる。すなわち、実装工程に不良が送られないので、各種の部品が液晶パネル120に実装され、付加価値が付いた状態で不良が発生することを低減できる。

(4)複数の対向基板20を保持する保持部201は、静電チャック方式が採用されているので、真空吸着方式に比べて、対向基板20の吸着による変形が抑えられる。また、対向基板20の大きさが変化したとしても、所望の位置に吸着固定できる。言い換えれば、サイズが異なる液晶パネル120の組立にも柔軟に対応できる。

上記実施形態以外にも様々な変形例が考えられる。以下、変形例を挙げて説明する。

(変形例1)電気光学装置としての液晶装置100は、透過型であることに限定されない。例えば、画素電極9が光反射性を有する部材で構成された反射型の液晶装置であっても、本発明を適用することができる。

(変形例2)本発明を適用可能な電気光学装置は、受光型の液晶装置100に限定されない。例えば、受光型の電気泳動装置や自発光型の有機EL(エレクトロルミネッセンス)装置などの製造方法にも適用することができる。それゆえに、素子基板10が複数面付けされたマザー基板110は、ウェハー状であることに限定されない。例えばマザー基板110が平面視で四角形などの多角形や、あるいはある程度の長さで連続したフィルム状の基板であってもよい。

10…素子基板、20…対向基板、30…スイッチング素子としてのTFT、50…液晶層、100…液晶装置、103…画素、110…マザー基板、120…液晶パネル、200…組立装置、201…保持部、300…検査装置。

Claims (4)

- チップ状の素子基板とチップ状の対向基板とが貼り合わされてなる電気光学装置を複数製造する電気光学装置の製造方法であって、

複数の前記対向基板を保持部上に位置決めして保持する対向基板保持工程と、

前記素子基板を複数切り出すことができるマザー基板を用意し、

前記マザー基板の複数の前記素子基板となる領域に、複数の前記対向基板を同時に貼り合わせる貼り合わせ工程と、を備えることを特徴とする電気光学装置の製造方法。 - 前記貼り合わせ工程の後に、

前記マザー基板における前記素子基板の端子部に電気信号を入力させて電気光学装置を駆動させ、個々の電気光学装置の電気特性を検査する検査工程と、

前記検査工程の後に前記マザー基板を切断して個々の電気光学装置を取り出す工程と、を備えることを特徴とする請求項1に記載の電気光学装置の製造方法。 - 前記対向基板保持工程は、前記保持部の一方の表面に前記対向基板を静電吸着させて固定することを特徴とする請求項1または2に記載の電気光学装置の製造方法。

- 前記マザー基板における前記素子基板ごとにシール材を配置する工程を備え、

前記貼り合わせ工程は、前記素子基板ごとに配置された前記シール材の内側に所定量の液晶を滴下する工程を含むことを特徴とする請求項1乃至3のいずれか一項に記載の電気光学装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011111089A JP2012242535A (ja) | 2011-05-18 | 2011-05-18 | 電気光学装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011111089A JP2012242535A (ja) | 2011-05-18 | 2011-05-18 | 電気光学装置の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012242535A true JP2012242535A (ja) | 2012-12-10 |

Family

ID=47464325

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011111089A Withdrawn JP2012242535A (ja) | 2011-05-18 | 2011-05-18 | 電気光学装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012242535A (ja) |

-

2011

- 2011-05-18 JP JP2011111089A patent/JP2012242535A/ja not_active Withdrawn

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9239495B2 (en) | Display device, electronic device including display device, and method for manufacturing display device | |

| CN101178490A (zh) | 电光装置的制造方法 | |

| CN108885363B (zh) | 液晶面板的制造方法 | |

| US20170229417A1 (en) | Mounting substrate manufacturing apparatus and method of manufacturing mounting substrate | |

| JP5563893B2 (ja) | 液晶表示パネル及びその製造方法、並びに液晶表示装置 | |

| JP2012073669A (ja) | タッチパネル及び画像表示装置 | |

| WO2019021927A1 (ja) | 表示パネル | |

| JP5247615B2 (ja) | 横電界方式の液晶表示装置 | |

| JP2010159187A (ja) | 基板ブレイク方法、基板ブレイク装置及びブレイクバー | |

| JP2012242535A (ja) | 電気光学装置の製造方法 | |

| JP2010139962A (ja) | アレイ基板、平面表示装置、マザー基板及びアレイ基板の製造方法 | |

| US20210240029A1 (en) | Electronic apparatus and method for manufacturing the same | |

| US20170332493A1 (en) | Mounting substrate manufacturing apparatus and method of manufacturing mounting substrate | |

| JP6036610B2 (ja) | 製造装置、及び製造方法 | |

| JP4428358B2 (ja) | 電気光学装置の製造方法及び製造装置 | |

| JP2009053587A (ja) | 液晶装置の製造装置及び液晶装置の製造方法 | |

| JP2008184358A (ja) | 電気光学装置の製造方法、及び電気光学装置 | |

| JP2013205625A (ja) | 液晶表示装置 | |

| JP5841932B2 (ja) | 液晶表示装置の製造方法 | |

| JP2007192853A (ja) | 電気光学装置の製造方法 | |

| JP2013029572A (ja) | 化粧板接合体、表示装置及び化粧板接合体の製造方法 | |

| JP2011154071A (ja) | 電気光学装置の製造方法、及び電気光学装置の製造装置 | |

| JP2009058564A (ja) | 電気光学装置の製造装置、及び製造方法 | |

| JP2010085899A (ja) | 液晶装置の製造方法及び液晶装置の製造装置 | |

| JP2009186705A (ja) | 電気光学装置の検査方法及び電気光学装置の検査装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Withdrawal of application because of no request for examination |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20140805 |