JP2012226041A - 電気光学装置 - Google Patents

電気光学装置 Download PDFInfo

- Publication number

- JP2012226041A JP2012226041A JP2011091941A JP2011091941A JP2012226041A JP 2012226041 A JP2012226041 A JP 2012226041A JP 2011091941 A JP2011091941 A JP 2011091941A JP 2011091941 A JP2011091941 A JP 2011091941A JP 2012226041 A JP2012226041 A JP 2012226041A

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- gradation level

- pixels

- frame

- time

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000008859 change Effects 0.000 claims abstract description 20

- 239000004973 liquid crystal related substance Substances 0.000 claims description 41

- 238000002834 transmittance Methods 0.000 description 15

- 230000004048 modification Effects 0.000 description 14

- 238000012986 modification Methods 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 11

- 230000005684 electric field Effects 0.000 description 11

- 238000010586 diagram Methods 0.000 description 10

- 239000003990 capacitor Substances 0.000 description 7

- 238000000034 method Methods 0.000 description 7

- 239000003086 colorant Substances 0.000 description 6

- 230000007423 decrease Effects 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0434—Flat panel display in which a field is applied parallel to the display plane

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0266—Reduction of sub-frame artefacts

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3655—Details of drivers for counter electrodes, e.g. common electrodes for pixel capacitors or supplementary storage capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

Abstract

【解決手段】本発明の電気光学装置は、複数の画素と、サブフィールド毎に当該画素を明状態または暗状態に駆動する駆動部とを具備し、特定の階調レベルが指定された場合に、少なくとも一の画素と、当該一の画素に隣接する画素とは1フレーム中の駆動内容が異なる。特定の階調レベルは、隣接する暗い側の階調レベルから特定の階調レベルに変化した場合において、一の画素の駆動内容が、暗状態から明状態に変化したサブフィールドのうち最も長い時間のサブフィールドと、変化後の明状態であるサブフィールドのうち最も長い時間のサブフィールドとが一致する関係を満たし、隣接する画素の駆動内容が、当該関係を満たさない階調レベルを示す。

【選択図】図9

Description

この電気光学装置によれば、隣接階調レベル間において長い時間のサブフィールドの駆動内容が異なる場合であっても、その駆動内容の違いに起因するディスクリネーションの表示に与える影響を抑えることができる。

この電気光学装置によれば、隣接階調レベル間において長い時間のサブフィールドの駆動内容が異なる場合であっても、その駆動内容の違いに起因するディスクリネーションの表示に与える影響を抑えることができる。

この電気光学装置によれば、ノーマリーブラックモードにおいて、連続した画素に同一の階調レベルが指定された場合に、連続した画素間においてディスクリネーションが生じて透過率が減少しても、これらの画素全体として指定された階調レベルの表現をすることができる。

この電気光学装置によれば、ノーマリーホワイトモードにおいて、連続した画素に同一の階調レベルが指定された場合に、連続した画素間においてディスクリネーションが生じて透過率が減少しても、これらの画素全体として指定された階調レベルの表現をすることができる。

この電気光学装置によれば、ノーマリーブラックモードにおいて、連続した画素に同一の階調レベルが指定された場合に、連続した画素間においてディスクリネーションが生じて透過率が減少しても、これらの画素全体として指定された階調レベルの表現をすることができる。

この電気光学装置によれば、ノーマリーホワイトモードにおいて、連続した画素に同一の階調レベルが指定された場合に、連続した画素間においてディスクリネーションが生じて透過率が減少しても、これらの画素全体として指定された階調レベルの表現をすることができる。

この電気光学装置によれば、隣接階調レベル間において長い時間のサブフィールドの駆動内容が異なる場合であっても、その駆動内容の違いに起因するディスクリネーションの表示に与える影響を、効果的に抑えることができる。

この電気光学装置によれば、隣接階調レベル間において長い時間のサブフィールドの駆動内容が異なる場合であっても、その駆動内容の違いに起因するディスクリネーションの表示に与える影響を、効果的に抑えることができる。

この電気光学装置によれば、階調レベルを良好に表現した表示を行うことができる。

[プロジェクター2000の構成]

図1は、実施形態におけるプロジェクター2000の構成を示す平面図である。プロジェクター2000は、ハロゲンランプ等の白色光源となるランプユニット220を有する。ランプユニット220から射出された投射光は、第1マルチレンズ2303、第2マルチレンズ2304、偏光変換素子2305、重畳レンズ2306を通過し、2枚のダイクロイックミラー2301および3枚のミラー2302によってR(赤)、G(緑)、B(青)の3原色に分離される。分離された各光は、集光レンズ2308を介して、各原色に対応する表示パネル100R、100Gおよび100Bにそれぞれ導かれる。なお、B光は、R光、G光と比較すると、光路が長いことによる損失を防ぐために、3枚のレンズ2307を用いたリレーレンズ系を介して導かれる。

図2は、実施形態におけるプロジェクター2000の機能構成を説明する図である。プロジェクター2000は、表示パネル100R、100G、100Bに縮小画像を形成させるための駆動部であるコントローラー10と、表示パネル100R、100G、100Bと、複数のLUTを有する。コントローラー10は、タイミング制御回路11、画質調整部12、SFコード変換部13、メモリー制御部14、メモリー15、駆動回路16R、16G、16Bを有する。複数のLUTは、この例においては、LUT(A)31およびLUT(B)32である。

なお、表示パネル100R、100G、100Bは、各々同じ構成であるため、以下の説明において特にそれぞれを区別する必要のない場合には、表示パネル100と記す。

画質調整部12は、映像信号Vidで規定される画像の明るさおよび色合いなどを、表示パネル100の表示特性、図示省略した各種操作子を用いて設定された内容に合わせて前処理するとともに、処理した映像信号Daを出力する。なお、この例において、上位回路から供給される映像信号Vidは、アナログ信号でもあってもよいし、デジタル信号でもあってもよいが、アナログ信号であれば、画質調整部12によってデジタル信号に変換される。

なお、この例においては、映像信号Daを8ビットとして、各画素において表現すべき階調レベルを十進値で、最も暗い「0」から最も明るい「255」まで「1」刻みで256段階の階調レベルを指定している。

図3は、実施形態における表示パネル100Rおよび駆動回路16Rの構成を説明する図である。表示パネル100Rは、例えばアクティブ・マトリクス型であって透過型の液晶表示パネルであり、画素毎に透過率を変調した透過像を生成するものである。

図3に示されるように、表示パネル100Rには、例えば1、2、3、…、1080行の走査線112が図において横方向に延在するように設けられ、また、1、2、3、…、1920列のデータ線114が図において縦方向に延在するように、かつ、各走査線112と互いに電気的に絶縁を保つように設けられている。そして、1080行の走査線112と1920列のデータ線114との交点のそれぞれに対応して、画素110がそれぞれ配列している。したがって、画素110が縦1080行×横1920列でマトリクス状に配列することになる。

図4は、実施形態における画素110の等価回路を説明する図である。画素110は、画素電極118とコモン電極108とで液晶105を挟持した液晶素子120と、走査線112に選択電圧が印加されたときにデータ線114と画素電極118との間で導通状態となり、非選択電圧が印加されたときに非導通状態となる薄膜トランジスター(Thin Film Transistor:以下単に「TFT」と表記する)116とを有する構成である。

コモン電極108は各画素にわたって共通であり、コントローラー10に含まれる図示省略した回路によって電圧LCcomが印加される。また、画素110では、液晶素子120に対して並列に補助容量(蓄積容量)125が設けられる。この補助容量125は、一端が画素電極118に接続され、他端が容量線115に共通接続されている。コントローラー10に含まれる図示省略した回路によって、容量線115は時間的に一定の電圧に保たれている。

この例においては、液晶素子120を交流駆動するため、オンレベルは、振幅中心電圧に対して高位側とする正極性と、振幅中心電圧に対して低位側とする負極性との2種類が必要となる。なお、交流駆動しない場合には、一方の極性のみでよい。

一方、オフレベルは、液晶素子120に電圧を印加しないのであれば、コモン電極108に印加される電圧LCcomの1種類であり、極性に無関係である。液晶素子120を交流駆動し、印加電圧をゼロ近傍とする電圧を印加するのであれば、振幅中心電圧に対して正極性と、負極性との2種類が必要となる。なお、交流駆動しない場合には、一方の極性のみでよい。

図5は、実施形態における駆動回路16R、16G、16Bに供給される信号を説明する図である。ここでは、供給される信号のうち、制御信号Yctに含まれる垂直同期信号Vsync、およびスタートパルスDy、制御信号Xctに含まれる極性指定信号Frpについて説明する。

図5(a)に示すように、垂直同期信号Vsyncは、表示の単位期間である1フレームを規定する信号である。この例においては、1フレームは16.67ms(60Hz)に相当する。極性指定信号Frpは、液晶素子120を交流駆動するときのオンレベルを正極性とする期間と負極性とする期間を規定する信号である。この極性指定信号Frpによっては、1フレームの前半を正極性の期間、後半を負極性の期間として規定する。これにより液晶素子120に印加される電圧の極性バランスをとることができる。

スタートパルスDyにおける1周期の8パルスは、それぞれのパルス間隔が異なり、各間隔がサブフィールドの期間を示し、以下、各サブフィールドをSF1,SF2、・・・、SF8という。この例においては、SF1、SF2、・・・、SF8の時間は、図5(b)に示すように、1.40ms、0.90ms、0.70ms、0.50ms,0.32ms、0.20ms、0.10ms、0.05msと規定され、時間に重み付けがされている。この例においては、1周期のうち前の期間に位置するサブフィールドほど長い時間として規定されている。

なお、各画素におけるサブフィールドのオン駆動(オンレベルの駆動電圧を印加)またはオフ駆動(オフレベルの駆動電圧を印加)は、走査線の選択時になされる。そのため、厳密にいえば、各画素における1フレーム(および各サブフィールド)のタイミングは、時間的にみて走査線毎に異なる。

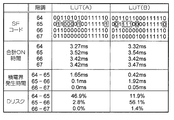

図7は、実施形態におけるLUTを説明する図である。図7(a)はLUT(A)31を示し、図7(b)はLUT(B)32を示している。いずれも、階調レベルが「50」〜「80」の部分を抜き出したものを記載している。LUT(A)31およびLUT(B)32は、ビットc1、c2、・・・、c16の16ビットにより構成され、前半のビットc1からc8の8ビットは、1フレーム中の第1、第3ブロックにおけるSF1、SF2、・・・SF8の画素110の駆動内容を表し、後半のビットc9からc16は、第2、第4ブロックにおけるSF1、SF2、・・・SF8の画素110の駆動内容を表す。そのため、例えば、ビットc1とc9とは、対応するサブフィールドの時間が同じである。その他の関係、例えば、ビットc8とc16との関係などについても、対応するサブフィールドの時間が同じになるという関係は同様である。このように、LUTは、階調レベルと各ビットにより表されるSFコードとの対応関係を規定する。

合計オン時間(明状態の時間)は、上述したように、画素110がオンに駆動されるサブフィールドの時間を合計したものであり、図8に示す例においては、第1、第2ブロックにおけるサブフィールドの時間を合計したものである。そのため、1フレームで考えると値を2倍にする必要がある。

なお、上記の特定の階調レベルの合計オン時間は、この条件を満たす場合に限らず、隣接する低い側の階調レベルの合計オン時間と隣接する高い側の階調レベルの合計オン時間との平均よりも長くなるように、SFコードが決められていてもよい。また、必ずしも、このように合計オン時間が長くなるように調整されていなくてもよい。

なお、図8に示す例においては、第1、第2ブロックにおけるサブフィールドを対象として横電界発生時間を算出しているため、1フレームで考えると値を2倍にする必要がある。

続いて、画素110を駆動するときの各構成の動作について、再び図2、図3、図4を参照しながら説明する。

SFコード変換部13は、画質調整部12から供給される映像信号DaをSFコードに変換する。このとき、SFコード変換部13は、映像信号Daのうち、画素110Aについて指定された階調レベルについては、LUT(A)31を参照してSFコードに変換し、画素110Bについて指定された階調レベルについては、LUT(B)32を参照してSFコードに変換する。そして、SFコード変換部13は、各色に対応して映像信号Daを変換したSFコードScr、Scg、Scbをメモリー制御部14に出力し、メモリー制御部14によってメモリー15に書き込まれる。

例えば、映像信号Daにおいて、ある画素110Aに指定された階調レベルが「66」である場合には、LUT(A)31における階調レベル「66」に対応するSFコードは、ビットc1からc16に対応する「0110000000111110」を2回繰り返した32ビットのコードとして変換され、メモリー制御部14によってメモリー15に書き込まれる。

メモリー制御部14は、読み出したSFコードScrのいずれかの1ビットを、現時点における表示パネル100Rの駆動タイミング(サブフィールド)に応じて選択して出力する。また、メモリー制御部14は、読み出したSFコードScgのいずれかの1ビットを、現時点における表示パネル100Gの駆動タイミング(サブフィールド)に応じて選択して出力し、読み出したSFコードScbのいずれかの1ビットを、現時点における表示パネル100Bの駆動タイミング(サブフィールド)に応じて選択して出力する。

なお、タイミング制御回路11は、垂直同期信号Vsyncで規定されるフレームにおけるスタートパルスDyの出力回数を、現時点における表示パネル100のサブフィールドを示す情報としてメモリー制御部14に供給する。これにより、メモリー制御部14は、現時点における表示パネル100の駆動タイミング(サブフィールド)を知ることができる。

表示パネル100R、100G、100Bのデータ線駆動回路162は、当該1行分のSFビットを、制御信号Xctに含まれる極性指定信号Frpによって指定された極性のオンレベルまたはオフレベルのデータ信号に変換するとともに、当該行の走査線が選択されたときに、データ信号を1〜1920列のデータ線114に供給する。

なお、当該走査線の選択が終了すると、TFT116が非導通状態となるが、液晶素子120は、TFT116の導通状態であったときに画素電極118に印加された電圧を、液晶素子の容量性および補助容量125によって保持するため、次回走査線が再び選択されるまで、オンまたはオフ駆動の状態に維持される。

これにより、各画素は、各サブフィールドにおいて、SFビットに応じてオンまたはオフ駆動され、1フレームを単位期間としてみたときの平均的な透過率は、階調レベルに応じた値となって、これにより階調が表現されることになる。

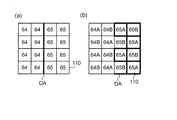

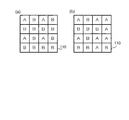

図9は、実施形態におけるディスクリネーションの発生態様を説明する図である。図9においては、表示パネル100の一定範囲の16個の画素110において、左半分の画素110には階調レベル「64」が指定され、右半分の画素110には階調レベル「65」が指定された場合の表示例を示す。図9(a)は、従来例のように、LUTを使い分けない場合、例えば、LUT(A)31のみを参照して画素110が駆動されている場合を示している。図中の「64」、「65」は、各画素110に指定された階調レベルを示している。図9(b)は、本発明の実施形態のように、画素110AはLUT(A)31を参照して駆動され、画素110BはLUT(B)32を参照して駆動された場合を示している。図中の「64A」、「64B」は、階調レベルが「64」に指定された画素110A、110Bを示し、「65A」、「65B」は、階調レベルが「65」に指定された画素110A、110Bを示している。

以上、本発明の実施形態について説明したが、本発明は以下のように、さまざまな態様で実施可能である。

上述した実施形態において、1フレーム毎に画素110を駆動する際に参照するLUTを切り替えるようにしてもよい。この場合には、画素110Aと画素110Bとの位置関係が1フレーム毎に変化するようにSFコード変換部13は、参照するLUTを決定すればよい。

なお、1フレーム毎に切り替えるのではなく、複数フレーム毎に切り替えるようにしてもよい。

上述した実施形態においては、画素110Aと画素110Bとは図6に示すように、市松状に配置されていたが、別の態様で配置されていてもよい。

このように、画素110Aと画素110Bとが分散配置され、ディスクリネーションが空間的に拡散するようになっていればよい。

上述した実施形態においては、LUT(A)31の最大重み変化部とLUT(B)32の最大重み変化部とは、隣接した階調レベルになっていたが、2以上離れた階調レベルに決められていてもよい。

上述した実施形態においては、LUTは、LUT(A)31とLUT(B)32との2つのLUTを用いていたが、3以上のLUTを用いてもよい。

上述した実施形態においては、1フレームは、8のサブフィールドを1周期とした4つのブロックにより構成されていたが、これに限られず、より多くのブロックにより構成されていてもよいし、1つのブロックで構成されていてもよい。ここで、LUTによって規定されているSFコードが複数のブロックのサブフィールドについて、SFコードとして規定されている場合には、実施形態においても示されているように、階調レベルが隣接する高い側の階調レベルに変化したときに、各ブロックにおける長い時間のサブフィールドが同時にオフからオンに変化しないようにしてもよい。このようにすると、Dリスクを減少させディスクリネーションの表示に与える影響を低減することもできる。

上述する実施形態においては、1フレームは、32のサブフィールドにより構成されていたが、この数に限られない。また、LUTにより規定されているSFコードは、16ビットであったが、このビット数に限られるものではない。

上述する実施形態においては、表示パネル100は透過型であったが、反射型であってもよい。さらに、ノーマリーブラックモードでの駆動に限られず、ノーマリーホワイトモードでの駆動であってもよい。ここで、ノーマリーホワイトモードでの駆動としたとき、オンレベルとは、液晶素子120に電圧を印加して暗状態にさせるデータ信号をいい、オフレベルとは、液晶素子120を明状態にさせるデータ信号をいう。なお、ノーマリーホワイトモードでの駆動とした場合には、上記LUTのSFコードについて各ビットの「1」と「0」とを反転させればよい。すなわち、実施形態(ノーマリーブラックモード)における明状態の時間であるオン時間は、ノーマリーホワイトモードにおける明状態の時間は、オフ時間に対応する。ただし、単に各ビットの「1」、「0」を反転させるのではなく、以下の点については、SFコードの内容が変化する。

上述した実施形態においては、1ブロックにおけるサブフィールドの時間はそれぞれ異なるものとなっていたが、その一部が同じ時間であってもよく、少なくとも1つのサブフィールドの時間が、他のサブフィールドの時間と異なる長さであればよい。

上述する実施形態においては、表示パネル100は、プロジェクター2000に用いられる構成として説明したが、直視型の液晶ディスプレイに用いられてもよい。すなわち、液晶素子を用いた電気光学装置として機能するものであれば、どのようなものにも適用可能である。また、この電気光学装置を様々な電子機器に用いることもできる。電子機器としては、テレビジョンや、ビューファインダー型・モニタ直視型のビデオテープレコーダー、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、デジタルスチルカメラ、携帯電話機、タッチパネルを備えた機器等などが挙げられる。

Claims (9)

- 各々が液晶素子を有する複数の画素と、

前記画素に対して指定される階調レベルに応じて、1フレームを分割したサブフィールド毎に当該画素を明状態または暗状態に駆動する駆動部と

を具備し、

1フレームにおける少なくとも一の前記サブフィールドの時間は他の前記サブフィールドの時間とは異なり、

前記駆動部は、前記複数の画素に特定の階調レベルが指定された場合に、少なくとも一の前記画素と、当該一の画素に隣接する前記画素とは1フレーム中の駆動内容が異なるように、前記画素を駆動し、

前記特定の階調レベルは、

隣接する暗い側の階調レベルから当該特定の階調レベルに変化した場合において、前記一の画素の前記駆動内容が、暗状態から明状態に変化したサブフィールドのうち最も長い時間のサブフィールドと、変化後の当該駆動内容が明状態であるサブフィールドのうち最も長い時間のサブフィールドとが一致する関係を満たし、前記隣接する画素の前記駆動内容が、当該関係を満たさない階調レベルを示す

ことを特徴とする電気光学装置。 - 各々が液晶素子を有する複数の画素と、

前記画素に対して指定される階調レベルに応じて、1フレームを分割したサブフィールド毎に当該画素を明状態または暗状態に駆動する駆動部と

を具備し、

1フレームにおける少なくとも一の前記サブフィールドの時間は他の前記サブフィールドの時間とは異なり、

前記駆動部は、前記複数の画素に特定の階調レベルが指定された場合に、少なくとも一の前記画素と、当該一の画素に隣接する前記画素とは1フレーム中の駆動内容が異なるように、前記画素を駆動し、

前記特定の階調レベルは、

隣接する暗い側の階調レベルから当該特定の階調レベルに変化した場合において、前記一の画素の前記駆動内容が、変化後の当該駆動内容が明状態であるサブフィールドの時間の合計に対する前記駆動内容が変化したサブフィールドの時間の合計の割合が予め決められた割合以上になる関係を満たし、前記隣接する画素の前記駆動内容が、当該関係を満たさない階調レベルを示す

ことを特徴とする電気光学装置。 - 前記液晶素子は、ノーマリーブラックモードで駆動され、

前記特定の階調レベルにおける1フレーム中の明状態の時間は、当該階調レベルに隣接する暗い側と明るい側との階調レベルにおける1フレーム中の明状態の時間の平均よりも長くなるように決められている

ことを特徴とする請求項1または請求項2に記載の電気光学装置。 - 前記液晶素子は、ノーマリーホワイトモードで駆動され、

前記特定の階調レベルにおける1フレーム中の明状態の時間は、当該階調レベルに隣接する暗い側と明るい側との階調レベルにおける1フレーム中の明状態の時間の平均よりも短くなるように決められている

ことを特徴とする請求項1または請求項2に記載の電気光学装置。 - 前記液晶素子は、ノーマリーブラックモードで駆動され、

前記特定の階調レベルにおける1フレーム中の明状態の時間は、当該階調レベルに隣接する明るい側の階調レベルにおける1フレーム中の明状態の時間よりも長くなるように決められている

ことを特徴とする請求項1または請求項2に記載の電気光学装置。 - 前記液晶素子は、ノーマリーホワイトモードで駆動され、

前記特定の階調レベルにおける1フレーム中の明状態の時間は、当該階調レベルに隣接する暗い側の階調レベルにおける1フレーム中の明状態の時間よりも短くなるように決められている

ことを特徴とする請求項1または請求項2に記載の電気光学装置。 - 前記駆動部は、前記複数の画素における前記少なくとも一の画素の位置を、1フレームまたは複数フレーム毎に変化させるように、前記画素を駆動する

ことを特徴とする請求項1乃至請求項6のいずれかに記載の電気光学装置。 - 前記駆動部は、前記複数の画素に前記特定の階調レベルが指定された場合に、全ての前記画素を、隣接する前記画素とは1フレーム中の前記駆動内容が異なるように駆動する

ことを特徴とする請求項1乃至請求項7のいずれかに記載の電気光学装置。 - 前記駆動部は、前記複数の画素に前記特定の階調レベルが指定された場合に、前記少なくとも一の画素における明状態の時間と、前記隣接する画素における明状態の時間との差は、これらの和に対して10%以内となるように、前記画素を駆動する

ことを特徴とする請求項1乃至請求項8のいずれかに記載の電気光学装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011091941A JP2012226041A (ja) | 2011-04-18 | 2011-04-18 | 電気光学装置 |

| CN201210103677.9A CN102750917B (zh) | 2011-04-18 | 2012-04-10 | 电光学装置 |

| US13/446,824 US9058767B2 (en) | 2011-04-18 | 2012-04-13 | Electrooptical device having pixel subfields controllable to produce gray levels |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011091941A JP2012226041A (ja) | 2011-04-18 | 2011-04-18 | 電気光学装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012226041A true JP2012226041A (ja) | 2012-11-15 |

Family

ID=47006100

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011091941A Pending JP2012226041A (ja) | 2011-04-18 | 2011-04-18 | 電気光学装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9058767B2 (ja) |

| JP (1) | JP2012226041A (ja) |

| CN (1) | CN102750917B (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014153595A (ja) * | 2013-02-12 | 2014-08-25 | Seiko Epson Corp | 映像処理回路、映像処理方法及び電子機器 |

| JP2015038558A (ja) * | 2013-08-19 | 2015-02-26 | セイコーエプソン株式会社 | 駆動装置、表示装置、電子機器及び駆動方法 |

| JP2016004103A (ja) * | 2014-06-16 | 2016-01-12 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の駆動方法、及び、電子機器 |

| US10163382B2 (en) | 2015-09-08 | 2018-12-25 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus capable of reducing degradation in image quality due to disclination, and storage medium storing liquid crystal drive program capable thereof |

| US10198985B2 (en) | 2015-09-08 | 2019-02-05 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

| US10229625B2 (en) | 2015-09-08 | 2019-03-12 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

| US10304371B2 (en) | 2015-09-08 | 2019-05-28 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008051949A (ja) * | 2006-08-23 | 2008-03-06 | Fujitsu Hitachi Plasma Display Ltd | 階調表示処理方法及びプラズマディスプレイ装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3918536B2 (ja) | 2000-11-30 | 2007-05-23 | セイコーエプソン株式会社 | 電気光学装置の駆動方法、駆動回路及び電気光学装置並びに電子機器 |

| JP4023517B2 (ja) | 2000-11-30 | 2007-12-19 | セイコーエプソン株式会社 | 電気光学装置、駆動回路及び電子機器 |

| JP4020158B2 (ja) | 2000-11-30 | 2007-12-12 | セイコーエプソン株式会社 | 電気光学装置、駆動回路及び電子機器 |

| JP3888076B2 (ja) | 2001-03-28 | 2007-02-28 | セイコーエプソン株式会社 | 電気光学装置の駆動方法、電気光学装置の駆動装置、電気光学装置および電子機器 |

| JP2003177723A (ja) * | 2001-12-11 | 2003-06-27 | Seiko Epson Corp | 電気光学装置の駆動方法、駆動回路及び電気光学装置並びに電子機器 |

| JP4172250B2 (ja) * | 2002-11-01 | 2008-10-29 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の駆動方法及び電子機器 |

| JP5056203B2 (ja) * | 2007-06-28 | 2012-10-24 | セイコーエプソン株式会社 | 電気光学装置、その駆動方法および電子機器 |

| JP5446328B2 (ja) * | 2009-03-06 | 2014-03-19 | セイコーエプソン株式会社 | 表示装置,電子機器および駆動コード生成回路 |

| JP2011059610A (ja) | 2009-09-14 | 2011-03-24 | Seiko Epson Corp | 電気光学装置、その駆動方法および電子機器 |

| JP2011064752A (ja) | 2009-09-15 | 2011-03-31 | Seiko Epson Corp | 電気光学装置、その駆動方法および電子機器 |

| JP5720110B2 (ja) * | 2010-04-08 | 2015-05-20 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の制御方法及び電子機器 |

-

2011

- 2011-04-18 JP JP2011091941A patent/JP2012226041A/ja active Pending

-

2012

- 2012-04-10 CN CN201210103677.9A patent/CN102750917B/zh not_active Expired - Fee Related

- 2012-04-13 US US13/446,824 patent/US9058767B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008051949A (ja) * | 2006-08-23 | 2008-03-06 | Fujitsu Hitachi Plasma Display Ltd | 階調表示処理方法及びプラズマディスプレイ装置 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014153595A (ja) * | 2013-02-12 | 2014-08-25 | Seiko Epson Corp | 映像処理回路、映像処理方法及び電子機器 |

| JP2015038558A (ja) * | 2013-08-19 | 2015-02-26 | セイコーエプソン株式会社 | 駆動装置、表示装置、電子機器及び駆動方法 |

| JP2016004103A (ja) * | 2014-06-16 | 2016-01-12 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の駆動方法、及び、電子機器 |

| US10163382B2 (en) | 2015-09-08 | 2018-12-25 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus capable of reducing degradation in image quality due to disclination, and storage medium storing liquid crystal drive program capable thereof |

| US10198985B2 (en) | 2015-09-08 | 2019-02-05 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

| US10229625B2 (en) | 2015-09-08 | 2019-03-12 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

| US10304371B2 (en) | 2015-09-08 | 2019-05-28 | Canon Kabushiki Kaisha | Liquid crystal drive apparatus, image display apparatus and storage medium storing liquid crystal drive program |

Also Published As

| Publication number | Publication date |

|---|---|

| US9058767B2 (en) | 2015-06-16 |

| US20120262501A1 (en) | 2012-10-18 |

| CN102750917A (zh) | 2012-10-24 |

| CN102750917B (zh) | 2014-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3918536B2 (ja) | 電気光学装置の駆動方法、駆動回路及び電気光学装置並びに電子機器 | |

| JP5720110B2 (ja) | 電気光学装置、電気光学装置の制御方法及び電子機器 | |

| JP4349433B2 (ja) | 電気光学装置、その駆動回路、駆動方法および電子機器 | |

| JP5056203B2 (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP4349434B2 (ja) | 電気光学装置、その駆動回路、駆動方法および電子機器 | |

| CN102750917B (zh) | 电光学装置 | |

| US8531369B2 (en) | Electro-optic device and electronic apparatus | |

| JP2010191038A (ja) | 液晶表示装置の駆動方法、液晶表示装置および電子機器 | |

| JP2020052132A (ja) | 電気光学装置及びその制御方法 | |

| US8212800B2 (en) | Electro-optic device, driving method, and electronic apparatus | |

| KR100501622B1 (ko) | 전기 광학 장치의 구동 방법, 구동 회로, 전기 광학 장치및 전자기기 | |

| JP5082579B2 (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP5798707B2 (ja) | 画像表示装置、その制御方法及び電子機器 | |

| JP2008185993A (ja) | 電気光学装置、処理回路、処理方法およびプロジェクタ | |

| JP4020158B2 (ja) | 電気光学装置、駆動回路及び電子機器 | |

| JP2011059610A (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP2011064752A (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP2020064103A (ja) | 電気光学装置の駆動方法、電気光学装置および電子機器 | |

| JP5682243B2 (ja) | 電気光学装置、電気光学装置の駆動方法および電子機器 | |

| JP6102992B2 (ja) | 画像表示装置、その制御方法及び電子機器 | |

| JP4023517B2 (ja) | 電気光学装置、駆動回路及び電子機器 | |

| JP2010271529A (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP5194735B2 (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP2015038558A (ja) | 駆動装置、表示装置、電子機器及び駆動方法 | |

| JP2010186038A (ja) | 電気光学装置、その駆動方法および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140326 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150217 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150420 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150929 |