JP2012103733A - 反射型液晶表示装置及び反射型液晶表示装置用の基板 - Google Patents

反射型液晶表示装置及び反射型液晶表示装置用の基板 Download PDFInfo

- Publication number

- JP2012103733A JP2012103733A JP2012028888A JP2012028888A JP2012103733A JP 2012103733 A JP2012103733 A JP 2012103733A JP 2012028888 A JP2012028888 A JP 2012028888A JP 2012028888 A JP2012028888 A JP 2012028888A JP 2012103733 A JP2012103733 A JP 2012103733A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- liquid crystal

- crystal display

- display device

- signal line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Projection Apparatus (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

【課題】画素サイズが小さくなったときでも、信号線と保持容量端との間のクロストークを減少させ、良好な出力画像が得られる反射型液晶表示装置を提供する。

【解決手段】各画素に画像信号を伝送する信号線2を第2メタル層で形成し、保持容量を構成する容量電極10と信号線2との間に第1メタル層でシールド線12を配置し、固定電位を与え、シールドを施しクロストークの発生を防ぐ。保持容量は半導体基板上に形成された拡散層からなる共通電極11と容量電極10とで構成される。信号線下に半導体基板上に形成された拡散層からなる容量電極と、固定電位とされた共通電極を配置し、シールドを施しクロストークの発生を防ぐ。

【選択図】 図1

【解決手段】各画素に画像信号を伝送する信号線2を第2メタル層で形成し、保持容量を構成する容量電極10と信号線2との間に第1メタル層でシールド線12を配置し、固定電位を与え、シールドを施しクロストークの発生を防ぐ。保持容量は半導体基板上に形成された拡散層からなる共通電極11と容量電極10とで構成される。信号線下に半導体基板上に形成された拡散層からなる容量電極と、固定電位とされた共通電極を配置し、シールドを施しクロストークの発生を防ぐ。

【選択図】 図1

Description

本発明は、アクティブマトリックス駆動方式を用いた反射型液晶表示装置、反射型液晶表示装置用基板及び液晶プロジェクターシステムに関する。特に、スイッチ素子と保持容量と反射電極とを有する画素をマトリックス状に複数配置した半導体基板と、透明電極が形成された光透過性基板とを、反射電極と透明電極とが対向するように配置した反射型液晶表示装置に関する。また、スイッチ素子と保持容量と反射電極とを有する画素をマトリックス状に複数配置した半導体基板を用いた反射型液晶表示装置用の基板に関する。更に、その反射型液晶表示装置を用いた液晶プロジェクターシステムに関する。

近年、液晶表示装置は、小型表示装置から所謂OA機器の端末用に広く普及しており、特に、OA機器においては映像を大画面に投影する投影型液晶表示装置が盛んに利用されている。

この種の投影型液晶表示装置には、大別すると透過型液晶表示装置と反射型液晶表示装置とがある。前者の透過型液晶装置の場合、各画素に設けられたスイッチング素子(トランジスタ)と容量および配線によって、光を透過させる画素の透過領域の面積が減少し開口率を小さくするという課題がある。

反射型液晶表示装置は、各画素の反射用画素電極(以下反射電極という)を絶縁分離する領域以外を反射電極にすることが可能である。そして、反射電極の下部にアクティブマトリックス駆動に必要なスイッチング素子と容量および配線を配置することができ、液晶表示パネルの小型化、高精細化、高輝度化において、透過型と比較して有利な点が多い。

一般的に、上述した反射型液晶装置では、Si基板等の半導体基板上に、MOSトランジスタなどのスイッチング素子に接続された反射電極がマトリックス状に複数配置される。そして複数の反射電極に対向して、全画素共通となる透明な共通電極が配置され、さらに、半導体基板の反射電極と共通電極との間に液晶が注入された構成をとる。このような反射型液晶装置においては、共通電極側から光を入射させて、共通電極と反射電極の間の電位差を画像信号に対応させ、画素ごとに液晶の配向を制御することで反射光を変調している。

近年、液晶表示装置に対する高精細化が求められており、反射型液晶表示装置は投影して大画面で画像を表示するため高精細画素の要求が強い。したがって、高精細な反射型液晶表示装置を安易な考えで実現していくと半導体基板のチップサイズは巨大化の一途をたどる傾向にある。しかしながら、この巨大化はコストアップに直接繋がる。ゆえに、チップサイズは可能な限り、小さくすることが望ましく、その為には画素サイズの微細化が求められている。

一般的に、液晶表示装置の液晶に印加する電圧は、焼き付き等の信頼性を考慮して液晶に印加される電圧が例えばフレーム毎に反転させる、所謂、反転駆動を行っている。それ故、液晶表示装置を駆動するために必要な電源電圧は15V程度(あるいはそれ以上)が求められる。言い換えると、半導体基板上に形成された画素や周辺駆動回路を構成する素子(トランジスタや容量)の耐圧が15V程度(あるいはそれ以上)必要になることを意味している。

しかし、各素子の耐圧を確保するには、それなりの素子サイズ、あるいは、素子分離スペースが必要である。すなわち、画素サイズを小さくしたいが素子形成のデザインルール(素子サイズや素子分離スペース等のデバイスを形成するときに必要な大きさを定義したもの)は小さくできないことになる。従って、素子サイズを小さくするには、各画素の保持容量を小さくしてしまう傾向にある。

しかしながら、保持容量を小さくしてしまうと、保持容量端のリークによる電圧降下により画質の低下や信号線からのクロストークを受けやすく、出力画像の画質の低下を招いてしまう。従って、画素の保持容量はできる限り大きいことが望ましい。

画素の保持容量を大きくするには、画素の中で保持容量の容量電極をできるだけ大きく

ればよい。

画素の保持容量を大きくするには、画素の中で保持容量の容量電極をできるだけ大きく

ればよい。

図9は従来例の画素レイアウト図であり、図10は図9のX−Y方向の断面構造図である。本構成は、特許文献1に示されているものである。

基台となる半導体基板はP型単結晶シリコン基板(以下、P型Si基板と呼ぶ)を用いており、この基板上にポリシリコンで形成されたゲート線201が水平方向に配線される。そして、ゲート配線の一部が分離して、スイッチング素子となるスイッチングトランジスタ(ここではNMOSトランジスタ)のゲートになる。スイッチ素子となるスイッチングトランジスタのソース領域202は、ソースコンタクト203を介して第1のメタル層で形成された信号線204と接続されている。スイッチングトランジスタのドレイン領域205は、ドレインコンタクト206を介して第1のメタル層で形成されたドレイン配線207に接続される。ドレイン配線207はコンタクト208を介してポリシリコンで形成された容量電極209に接続されている。

容量電極209の対向電極は、イオン注入でシリコン基板に形成されたN+型の拡散層となり、この拡散層が全画素共通の共通電極210となる。また、容量電極209と共通電極210との間の絶縁膜は、NMOSトランジスタを形成するゲート酸化膜と同じ工程で形成されることが一般的である。

図10において、211はP型Si基板であり、図示左側にフィールド酸化膜212a、212bの間にスイッチ素子となるNMOSトランジスタが形成されている。201がNMOSトランジスタのゲート電極(ゲート配線の一部)であり、202がソース領域、205がドレイン領域である。

ソース領域202はソースコンタクト203を介して第1のメタル層で形成された信号線204と接続されている。ドレイン領域205からはドレインコンタクト206を介して第1のメタル層で形成されたドレイン配線207に接続されている。ドレイン配線207はコンタクト208を介して容量電極209に接続され、さらに、スルーホール213を介して第3のメタル層で形成された反射電極214に接続されている。また、容量電極209の対向電極である共通電極(Vcom電極)210はN+型の拡散層で形成されるため、その両サイドはNMOSトランジスタと同様にフィールド酸化膜212b、212cの間に形成されている。また、第1メタル層と反射電極214の間には、隣接する反射電極との隙間から入射する光を遮光するために第2のメタル層で形成された遮光層215が配置されている。そして、遮光層215において、スルーホール213が通るところは電気的絶縁を得るために穴が開けられている。なお、画素の保持容量を少しでも稼ぐために、遮光層215には固定電位が与えられている。

液晶層217は、反射電極214上に図示しない保護膜をつけた後、反射電極214の対向電極となる、透明電極で形成された液晶共通電極216との間に所定の間隔をもって挟み込まれる。

液晶の光学的特性の変化(偏向率の変化)は、反射電極214と液晶共通電極216との電位差によって起こるものであり、各画素の反射電極214の電位を制御することで、画像を形成している。

特許文献1では、信号線204とドレイン配線207との間に、信号線204およびドレイン配線207と同一の層(第1メタル層)で第1のシールド線219を設けている。また、第1のシールド線219には共通電極210と同一の電位を与えている。さらに、隣接する画素の信号線からのクロストークの影響も考慮して第1のシールド線219が配置されている反対側(図9中の右側)にも第2のシールド線220を配置している。第2のシールド線220はGND電位を与え画素中でp型基板にp+領域を介して接続されている。この構成では、隣接画素も含めた信号線204がドレイン配線207に及ぼすクロストークを抑制することが出来るが、信号線204が容量電極209の上部を通過しているので、クロストークは無くならない。信号線204の下部にも容量電極209の一部を作り込んでいるのは、保持容量を大きくするためである。

ここで、信号線204が容量電極209の端部に与えるクロストークが、どのような影響を与えるか説明する。

所定行が選択状態(ゲート線がハイレベルで画素のスイッチングトランジスタがON状態)の時、ほかの行の画素は保持容量にその画素を表示するための画像信号電圧を保持している。このとき、所定行の画素に信号線によって画像信号がスイッチングトランジスタを介して保持容量に書き込まれる。このとき、図9に示すように、信号線204と他の画素の保持容量209の端部との間は寄生容量が存在するために、この寄生容量を介して保持状態中の容量電極端に電位の変動を起こす。保持状態中の容量電極の電位が変化すると、液晶の光学的特性を変化するため、本来の画像が表現できなくなり、著しい画質の低下を招くことになる。これをクロストークと呼んでいる。

クロストークを測定する評価パターンは、例えば、水平方向に3分割、垂直方向に3分割した9分割画面で行う。中央部の分割画面には100%の輝度を表示させ、周りの8つの分割画面にはハーフトーンの輝度(例えば10%輝度)を表示させたときに、寄生容量によるクロストークが輝度の境界部分で発生する。

このクロストークを回避するために、信号線204の下部にポリシリコンで形成された容量電極209を配置しない、すなわち、保持容量を形成しない構成が考えられる。このレイアウト構成を用いれば、信号線204と容量電極209のオーバーラップがないので信号線204が容量電極端に与えるクロストークを少なくすることが出来るが、保持容量が小さくなってしまう。これでは、画素サイズが小さくなったとき、画素電圧の保持能力が低下する。保持能力が低下すると、画像的にはコントラストの小さい画像になってしまい、画質の低下に繋がる。

なお、信号線204と反射電極214との間には反射電極間の隙間から侵入する光を遮光するための遮光層215が配置されている。この遮光層215には固定電位を与えているので、遮光層215がシールド層として機能するため、信号線204が反射電極214にあたえるクロストークは起こりにくい構成となっている。

上述したように、通常、クロストークは、人間の目において、隣接画素の相対輝度差2〜3%以下であれば認識されないとされている。

近年、表示装置の高精細化が進んでおり、これに伴い画素サイズも小さくしなければコストを抑えることが出来ない。しかしながら、液晶の駆動は、前述したように信頼性の面から反転駆動するのが一般的である。そのために必要な駆動電源電圧は10〜15V程度であり、Si基板上に形成されるトランジスタトランジスタや容量は駆動電源電圧に対して安定動作する耐圧が必要である。それ故、画素サイズが小さくなっても素子を形成するサイズ(例えば、素子分離幅など)を容易に小さくすることが出来ない。さらに、クロストークに強い画素構造を得るためには、保持容量は可能な限り大きくすることが望ましい。

本発明の目的は、限られた画素サイズの中に、スイッチ素子と大きい保持容量を形成し、信号線が保持容量端(ドレイン配線、容量電極、および、反射電極)に与えるクロストークを減少させることにある。そして、結果として、高品質な画像を得ることができる反射型液晶表示装置を提供することにある。

本発明の反射型液晶表示装置は、透明電極を有する光透過性基板と、液晶層と、スイッチ素子と保持容量と反射電極とを有する画素と、前記スイッチ素子を介して前記保持容量及び前記反射電極に接続され、且つ前記保持容量の少なくとも一部の上部に配置された第1の導電層からなる信号線と、を有し、前記液晶層を間に挟んで前記透明電極と前記反射電極とが対向するように配置された半導体基板と、を含む反射型液晶表示装置であって、前記保持容量は、前記半導体基板に形成された拡散層からなる第1電極と、前記信号線と前記第1電極の間に配置された第2の導電層からなる第2電極とを有し、前記第1電極は前記スイッチ素子に接続され、前記第2電極には固定電位が供給されている。

また本発明の反射型液晶表示装置は、前記スイッチ素子と前記反射電極とは配線パターンを介して接続され、該配線パターンは前記信号線と同一の前記第1の導電層からなり、前記信号線と前記配線パターンとの間に、固定電位が供給された、前記第1の導電層からなるシールド線が配置されていることを特徴とする。また、前記画素はマトリックス状に複数配置されており、隣接する画素の配線パターンと前記信号線との間に、固定電位が供給された前記第1の導電層からなる前記隣接する画素のシールド線が配置されていることを特徴とする。また、前記反射電極と前記信号線との間に、固定電位が与えられた遮光層が配置されていることを特徴とする。前記第2電極と前記シールド線とがスルーホールを介して接続されていることを特徴とする。

本発明の反射型液晶表示装置用の基板は、スイッチ素子と保持容量と反射電極とを有する画素と、前記スイッチ素子を介して前記保持容量及び前記反射電極に接続され、且つ前記保持容量の少なくとも一部の上部に配置された信号線と、を有する半導体基板からなる反射型液晶表示装置用の基板であって、前記保持容量は、前記半導体基板に形成された拡散層からなる第1電極と、前記信号線と前記第1電極の間に配置された第2の導電層からなる第2電極とを有し、前記第1電極は前記スイッチ素子に接続され、前記第2電極には固定電位が供給されている。

また本発明の液晶プロジェクターシステムは、上記反射型液晶表示装置を有することを特徴とする。

本発明によれば、画素サイズが小さくなっても保持容量の容量値を大きくとることができ、信号線からスイッチングトランジスタのドレイン配線、容量電極、および、反射電極へのクロストークを減少することが可能である。その結果、良好な出力画像を得ることができる反射型液晶表示装置を提供することが出来る。

以下、本発明の実施の形態について図面を用いて詳細に説明する。

[実施形態1]

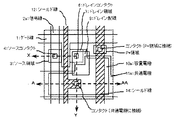

図1は本発明の第1の実施形態を示す1画素の概略平面図であり、図2は図1に示すX−Y方向の断面図であり、図3は、図1中のA−AA方向の断面図である。図7は、本発明の反射型液晶表示装置におけるアクティブマトリックス駆動回路を説明するブロック図である。図11は、図1で示した画素を4×4のマトリックス状に複数配置した概略平面図である。なお、図1は、図面を見やすくするために、図2に示す遮光層よりSi基板(半導体基板)側(反射電極、遮光層、および、反射電極に接続されるスルーホールを含まない)のみを表現している。なお、本実施形態では、アクティブマトリックス駆動回路を有する半導体基板としてP型Si基板を使用し、スイッチ素子はNMOSトランジスタからなるスイッチングトランジスタであるとする。

図1は本発明の第1の実施形態を示す1画素の概略平面図であり、図2は図1に示すX−Y方向の断面図であり、図3は、図1中のA−AA方向の断面図である。図7は、本発明の反射型液晶表示装置におけるアクティブマトリックス駆動回路を説明するブロック図である。図11は、図1で示した画素を4×4のマトリックス状に複数配置した概略平面図である。なお、図1は、図面を見やすくするために、図2に示す遮光層よりSi基板(半導体基板)側(反射電極、遮光層、および、反射電極に接続されるスルーホールを含まない)のみを表現している。なお、本実施形態では、アクティブマトリックス駆動回路を有する半導体基板としてP型Si基板を使用し、スイッチ素子はNMOSトランジスタからなるスイッチングトランジスタであるとする。

まず、液晶表示装置としての回路動作について、図7を用いて説明する。

図7では説明の簡略化のため3×3画素を配置し、またそれぞれの画素の回路構成も記載している。

図7に示すアクティブマトリックス駆動回路はP型Si基板に形成されているものとする。

図7において、101は1つの画素を示し、画素101はスイッチングトランジスタ等からなるスイッチ素子102と保持容量103と反射電極104で構成されている。画素内のスイッチ素子102はNMOSトランジスタで構成されている。同一行の画素内のスイッチ素子102のゲートは、ゲート線105に接続されており、ゲート線105には垂直走査シフトレジスタ106の各レジスタの出力が印加される。同一列の画素内のスイッチ素子102のソース(図示したトランジスタの左側)は信号線107に接続されている。各画素のスイッチ素子102のドレイン(図示した右側)は保持容量103と反射電極104とに接続され、保持容量103のもう一端は、全画素共通のVcom電位に接続されている。信号線107は、転送スイッチ108を介してビデオ線109に接続されている。転送スイッチ108のON/OFFは、水平走査シフトレジスタ110の各レジスタ出力によって制御される。

図7に示すアクティブマトリックス駆動回路の動作を簡単に説明する。順次タイミングをずらして入力されたビデオ信号がビデオ線109に出力される。そして、水平走査シフトレジスタ110によって転送スイッチ108を順次ON状態(導通状態)にしていくことで、ビデオ信号電圧がサンプリングされながら信号線107に供給される。この一つの信号線107と、垂直走査シフトレジスタ106によって選択されたゲート線105との交差した位置にある所望の画素のスイッチ素子102が選択されてON状態とされる。すると、スイッチ素子102を介して画素の保持容量103にビデオ信号電圧が書き込まれる。反射電極104は、保持容量103に書き込まれた電圧になる。そして、反射電極104と透明共通電極(図示していない)との間に生じる電位差が液晶に印加され、液晶の光学特性を変化させている。

次に本実施形態の反射型液晶表示装置の1画素の構成について図1から図3、及び図11を用いて説明する。

図1及び図2において、1はポリシリコン(第2の導電層に相当)で形成されたゲート線であり、その一部が分岐してスイッチングトランジスタのゲートになっている。2は第2メタル層(第1の導電層に相当)で形成された信号線であり、列方向に配置された画素のスイッチングトランジスタのソース領域3にソースコンタクト4を介して接続されている。第2メタル層で形成された信号線2は、その下層の第1メタル層(第3の導電層に相当)で形成されたソース配線5とスルーホールで接続された後、ソース配線5とソース領域3とをソースコンタクト4を介して接続している。スイッチングトランジスタのドレイン領域7はドレインコンタクト6を介して第1メタル層で形成された第1のドレイン配線8に接続されている。第1のドレイン配線8はスルーホールを介して第2メタル層で形成された第2のドレイン配線(配線パターンとなる)9に接続されている。さらに、第2のドレイン配線9はスルーホールを介して、従来技術と同様に遮光層17の穴を通って反射電極16に接続されている。液晶層19は、反射電極16上に図示しない保護膜をつけた後、反射電極16の対向電極となる、光透過性基板に形成された透明電極となる液晶共通電極18との間に所定の間隔をもって挟み込まれる。ここで、第1及び第2メタル層は、Alなどの金属材料が好適に用いられるが、それに限定するものではなく、電気的な導通が可能な材料である導電層であればよい。

また、第1のドレイン配線8は、第1のコンタクトを介してその下層のポリシリコン(第2の導電層に相当)で形成された容量電極10に接続されている。容量電極10は、スイッチングトランジスタを形成するゲート酸化膜を同等の酸化膜を挟んでN+型の拡散領域で形成された共通電極11(Vcom電極)とで各画素の保持容量を形成している。

スイッチングトランジスタのゲート電極の上部には、第1メタル層(第3の導電層に相当)で形成され且つ信号線2に接続されているソース配線5と、第1メタル層で形成されたドレイン配線8との間に配置された第1のシールド線12が設けられている。なお、第1のシールド線は固定電位が供給された導電層となる。

この第1のシールド線12に所定の定電圧を印加して固定電位とすることで、ソース配線5から第1のドレイン配線8へのクロストークが起こらないようにシールドしている。

さらに、第1のシールド線12の上部には、第2メタル層(第1の導電層に相当)で形成された第2のシールド線13がある。そしてシールド線13は信号線2と第2メタル層(第1の導電層に相当)で形成された第2のドレイン配線9との間に配置されている。この第2のシールド線13に第1のシールド線12と同様に所定の定電圧を印加し固定電位することで、信号線2から第2のドレイン配線9へのクロストークが起こらないようにシールドしている。また、第1のシールド線12は、第2のコンタクトを介して容量を構成する共通電極(N+拡散層)11と接続されている。

さらに、図3に示すように、第1のシールド線12は、ポリシリコン(第2の導電層に相当)で形成された容量電極10と第2メタル層(第1の導電層に相当)で形成された信号線2との間に配置されるように容量上部は幅広くパターンニングされている。

これにより、信号線2と容量電極10との間をシールドすることになり、信号線からのクロストークの影響を受けにくくしている。

また、図1中の右側(画素の右側)には、第1メタル層(第3の導電層に相当)で形成されたシールド線14が配置され、容量が形成されていないところで、第3のコンタクトを介してP+領域に接続されP型Si基板の電位をとっている。さらに、図1及び図3に示すように、シールド線14の上部には、第2メタル層(第1の導電層に相当)で形成されたシールド線15が配置されている。これにより、シールド線14は、隣接画素のソース配線5に対してシールドの役割をしており、シールド線15は、隣接画素の信号線に対してシールドの役割を果たしている。

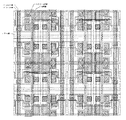

図11は、図1で示した画素を4×4のマトリックス状に複数配置したものである。本実施形態においては、全ての画素は略同一の向きで配置されている。図11に示すように、所定の画素の信号線2と、この所定の画素のドレイン配線9との間には、その画素のシールド線13が配置されている。また、所定の画素の信号線2と、この所定の画素と隣接する画素のドレイン配線9の間には、隣接画素のシールド線15が配置された構成となっている。更に所定の画素のソース配線5と、この所定の画素のドレイン配線8との間にはシールド線12が配置され、所定の画素のソース配線5と、この所定の画素と隣接する画素のドレイン配線8との間にはシールド線14が配置されている。このような構成により、クロストークの発生を低減することが出来る。また、液晶層が封止されている反射電極16から液晶共通電極までは従来と同じ構造なので説明を省く。

なお、本実施形態において、画素のマトリックスレイアウトは図11に示されるものに限定されるものではなく、例えば図12〜図14に示されるマトリックスも好適に適用可能である。

図12は画素を4×4のマトリックス状に複数配置したものである。図12では、奇数列の画素と偶数列の画素が、垂直方向(図面の縦方向)を軸として線対称となるように配置されている。この構成を用いた場合は、2N画素単位(Nは正の整数)で画素電圧を同時に書き込むこと事が必要である。図12で示す構成の場合も、信号線2とドレイン配線9の間には、シールド線13が配置された構成となっている。また、ソース配線5とドレイン配線8と間にはシールド線12が配置される構成となっている。それによりクロストークの発生を低減することが出来る。

図13も画素を4×4のマトリックス状に複数配置したものである。図12では、奇数行の画素と偶数行の画素が、水平方向(図面の横方向)を軸として線対称となるように配置されている。図13で示す構成の場合でも、信号線2とドレイン配線9の間には、シールド線13またはシールド線15が配置された構成となっている。また、ソース配線5とドレイン配線8と間にはシールド線12またはシールド線14が配置される構成となっている。それによりクロストークの発生を低減することが出来る。

図14も画素を4×4のマトリックス状に複数配置したものである。図14では、奇数行の画素と偶数行の画素が、水平方向(図面の横方向)に対して線対称で且つ垂直方向(図面の縦方向)に対して線対称となるように配置されている。この構成を用いた場合も図12で示す構成と同様に、2N画素単位(Nは正の整数)で画素電圧を同時に書き込むこと事が必要である。図14で示す構成の場合も、信号線2とドレイン配線9の間には、シールド線13が配置された構成となっている。また、ソース配線5とドレイン配線8と間にはシールド線12が配置される構成となっている。それによりクロストークの発生を低減することが出来る。

ここで、これまでに示した画素のマトリックスのレイアウトは、本実施形態に限定されるものではなく、本発明の他の実施形態にも好適に適用可能である。

なお、図2および図3中に示す各層(電極、配線等)の間で特記していないところは絶縁膜が配置されている。

さらに、反射電極16も保持容量の一端を形成しているが、信号線2と反射電極16の間には、遮光層17が配置されている。そしてこの遮光層17は、所定の定電圧が印加され、固定電位とされているのでシールド層として機能し、信号線2が反射電極16にクロストークの影響を与えることは抑制される。また、遮光層17に定電圧を印加することで、反射電極16と遮光層17の間も保持容量として使用することが出来る。

上述したように、本実施形態が示す画素レイアウトを用いることにより、図11、図13の画素レイアウトにおいては、図3に示すように、信号線の上下方向および左右方向に対して、所定の固定電位を持った配線パターンが配置される。また、図12、図14の画素レイアウトにおいては、同じ画素電圧が与えられる信号線群の上下方向、左右方向に対して、所定の固定電位を持った配線パターンが配置される。この構成によって、信号線または同じ画素電圧が与えられる信号線群を4方向(図3の上下方向、左右方向)からシールドした形になり、信号線の下も有効に保持容量として形成することが可能なので容量値を大きくとることができる。さらに、ドレイン配線、容量電極、および、反射電極に与えるクロストークを減少させることができ、画素サイズが小さくなっても良好な出力画像が得られる。

また、本実施形態においては、P型Si基板を用いて説明したが、N型Si基板を用いても構わず、どちらの基板を用いても、本実施形態による効果は変わらない。

さらに、本実施形態では、ゲート線にポリシリコンを用いたが、必ずしもゲート線がポリシリコンである必要が無い。すなわち、第1メタル層を用いてゲート線を形成し、必要な場所において、コンタクトを介してポリシリコンに接続して、そのポリシリコンがスイッチングトランジスタのゲートを構成する形になっても構わない。

[実施形態2]

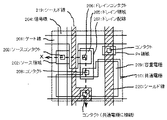

図4は、本発明の第2の実施形態を示す1画素の概略平面図であり、図5は図4に示すX−Y方向の断面図である。また、図6は、図1中のA−AA方向の断面図である。

図4は、本発明の第2の実施形態を示す1画素の概略平面図であり、図5は図4に示すX−Y方向の断面図である。また、図6は、図1中のA−AA方向の断面図である。

本実施形態の第1の実施形態と大きく違う点は、保持容量の第1電極であるN+型の拡散層からなる電極がスイッチングトランジスタのドレイン領域と接しており、ドレイン配線と反射電極とに接続されていることである。また保持容量を形成する第2電極である共通電極はポリシリコンで形成されており、シールド線に接続されていることである。本実施形態では、第1の実施形態の第2メタル層に相当する層が要らない。

以下に、図4に示す画素レイアウト、および、断面構造の説明を行う。

1はポリシリコンで形成されたゲート線であり、その一部が分岐して、画素のスイッチングトランジスタのゲートになっている。2aは第1メタル層で形成された信号線であり、列方向に配置された画素のスイッチングトランジスタのソース領域3にソースコンタクト4を介して接続されている。スイッチングトランジスタのドレイン領域7はドレインコンタクト6を介して第1メタル層で形成されたドレイン配線8に接続されており、ドレイン配線8はスルーホールを介して反射電極16に接続されている。

また、ドレイン領域7は、トランジスタと容量の素子分離を必要とせずに、N+型の拡散層で形成された容量電極10aに拡散領域の延長で接続されている。容量電極10aは、スイッチングトランジスタを形成するゲート酸化膜を同等の酸化膜を挟んでポリシリコンで形成された共通電極11a(Vcom電極)とで各画素の保持容量を形成している。

スイッチングトランジスタのゲート電極(ゲート配線の一部)の上部には、第1メタル層で形成されたシールド線12がある。そして、シールド線12は、信号線2aと第1メタル層で形成されたドレイン配線8との間に配置されている。シールド線12に所定の定電圧を印加することで、信号線2からドレイン配線8へのクロストークが起こらないようにシールドしている。シールド線12は、コンタクトを介して容量を構成する共通電極11aと接続されている。

さらに、ポリシリコンで形成された共通電極11aは、第1のメタル層で形成された信号線2とN+拡散で形成された容量電極10aとの間に配置されている。よって、信号線2と容量電極10aとの間をシールドすることになり、信号線からのクロストークの影響を受けなくなる。

また、図4中の右側(画素の右側)には、第1メタル層で形成されたGNDシールド線14が配置され、容量が形成されていないところで、コンタクトを介してP+領域に接続されP型Si基板の電位をとっている。これにより、GNDシールド線14は、隣接画素の信号線に対してシールドの役割をしている。また、遮光層17は、実施形態1と同様に所望の固定電位をもって配置されているので、信号線2が反射電極16に及ぼすクロストークは抑制される。また、液晶層19が封止されている反射電極16から液晶共通電極18までは実施形態1と同じ構造なので説明を省く。

なお、図5および図6中に示す各層(電極、配線)の間で特記していないところには絶縁膜が配置されている。

上述したように、本実施形態が示す画素レイアウトを用いることにより、信号線の上下方向および左右方向に対して、所定の固定電位を持った配線パターンが配置される。その結果、信号線を4方向(上下、左右)からシールドした形になり、信号線の下も有効に保持容量として形成することが可能なので容量値を大きくとることができる。さらに、ドレイン配線、保持容量電極、および、反射電極に与えるクロストークを減少させることができ、画素サイズが小さくなっても良好な出力画像が得られる。

また、本実施形態においては、P型Si基板を用いて説明したが、N型Si基板を用いても構わず、どちらの基板を用いても、本実施形態が示す効果は変わらない。

なお、本実施形態の構成では、第1の実施形態の構成よりメタル層が一層少なくても実現できる構成である。

[実施形態3]

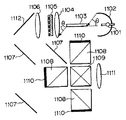

図8を用いて、本発明に係わるアクティブマトリックス基板を用いた反射型液晶表示装置を使用した液晶プロジェクターシステムについて説明する。図8は液晶プロジェクタ用光学システムの一例である。1101はランプ、1102はリフレクター、1103はロッドインテグレーター、1104はコリメーターレンズ、1105は偏光変換系、1106はリレーレンズ、1107はダイクロイックミラーである。また、1108は偏光ビームスプリッター、1109はクロスプリズム、1110は本発明に係わるアクティブマトリックス基板を用いた反射型液晶パネル、1111は投影レンズ、1112は全反射ミラーである。

図8を用いて、本発明に係わるアクティブマトリックス基板を用いた反射型液晶表示装置を使用した液晶プロジェクターシステムについて説明する。図8は液晶プロジェクタ用光学システムの一例である。1101はランプ、1102はリフレクター、1103はロッドインテグレーター、1104はコリメーターレンズ、1105は偏光変換系、1106はリレーレンズ、1107はダイクロイックミラーである。また、1108は偏光ビームスプリッター、1109はクロスプリズム、1110は本発明に係わるアクティブマトリックス基板を用いた反射型液晶パネル、1111は投影レンズ、1112は全反射ミラーである。

ランプ1101から出た光束はリフレクター1102で反射し、インテグレーター1103の入り口に集光する。このリフレクター1103は楕円リフレクターであり、発光部及びインテグレーター入り口にその焦点が存在する。インテグレーター1103に入った光束はインテグレーター内部で0〜数回反射を繰り返し、インテグレーター出口で2次光源像を形成する。2次光源形成法としてはフライアイを用いた方法も有るが、ここでは省略する。2次光源からの光束はコリメーターレンズ1104を通して、おおむね平行光とされ、偏光変換系の偏光ビームスプリッター1105に入射する。P波は偏光ビームスプリッター1105で反射し、λ/2板を通りS波となり、全てがS波となりリレーレンズ1106に入射する。光束はリレーレンズ1106により、パネルに集光される。パネルに集光される間に、色分解ダイクロイックミラー1107、偏光板(不図示)、偏光ビームスプリッター1108、クロスプリズム1109等で色分解系が構成され、S波がそれぞれ3枚の液晶パネル1110に入射する。液晶パネル1110では液晶シャッターが、映像に合わせて画素ごとに電圧を制御する。液晶の作用によりS波を楕円偏光(もしくは直線偏光)に変調し、偏光ビームスプリッター1108でP波成分を透過させ、クロスプリズム1109で色合成した後投影レンズ1111から投影する形態が一般的である。

本発明は、液晶を用いて画像、文字を表示する反射型液晶表示装置、反射型液晶表示装置用基板及び液晶プロジェクターシステムに適用できる。

1 ゲート線

2 信号線

3 ソース領域

4 ソースコンタクト

5 ソース配線(第1メタル層)

6 ドレインコンタクト

7 ドレイン領域

8 ドレイン配線(第1メタル層)

9 ドレイン配線(第2メタル層)

10 容量電極(ポリシリコン)

11 共通電極(N+拡散)

12 シールド線(第1メタル層)

13 シールド線(第2メタル層)

14 シールド線(第1メタル層)

15 シールド線(第2メタル層)

16 反射電極

17 遮光層

2 信号線

3 ソース領域

4 ソースコンタクト

5 ソース配線(第1メタル層)

6 ドレインコンタクト

7 ドレイン領域

8 ドレイン配線(第1メタル層)

9 ドレイン配線(第2メタル層)

10 容量電極(ポリシリコン)

11 共通電極(N+拡散)

12 シールド線(第1メタル層)

13 シールド線(第2メタル層)

14 シールド線(第1メタル層)

15 シールド線(第2メタル層)

16 反射電極

17 遮光層

Claims (7)

- 透明電極を有する光透過性基板と、

液晶層と、

スイッチ素子と保持容量と反射電極とを有する画素と、前記スイッチ素子を介して前記保持容量及び前記反射電極に接続され、且つ前記保持容量の少なくとも一部の上部に配置された第1の導電層からなる信号線と、を有し、前記液晶層を間に挟んで前記透明電極と前記反射電極とが対向するように配置された半導体基板と、

を含む反射型液晶表示装置であって、

前記保持容量は、前記半導体基板に形成された拡散層からなる第1電極と、前記信号線と前記第1電極の間に配置された第2の導電層からなる第2電極とを有し、

前記第1電極は前記スイッチ素子に接続され、前記第2電極には固定電位が供給されていることを特徴とする反射型液晶表示装置。 - 前記スイッチ素子と前記反射電極とは配線パターンを介して接続され、

該配線パターンは前記信号線と同一の前記第1の導電層からなり、

前記信号線と前記配線パターンとの間に、固定電位が供給された、前記第1の導電層からなるシールド線が配置されていることを特徴とする請求項1に記載の反射型液晶表示装置。 - 前記画素はマトリックス状に複数配置されており、隣接する画素の配線パターンと前記信号線との間に、固定電位が供給された前記第1の導電層からなる前記隣接する画素のシールド線が配置されていることを特徴とする請求項2に記載の反射型液晶表示装置。

- 前記反射電極と前記信号線との間に、固定電位が与えられた遮光層が配置されていることを特徴とする請求項1〜3のいずれか1項に記載の反射型液晶表示装置。

- 前記第2電極と前記シールド線とがスルーホールを介して接続されていることを特徴とする請求項2に記載の反射型液晶表示装置。

- 請求項1〜5のいずれか1項に記載の反射型液晶表示装置を有する液晶プロジェクターシステム。

- スイッチ素子と保持容量と反射電極とを有する画素と、前記スイッチ素子を介して前記保持容量及び前記反射電極に接続され、且つ前記保持容量の少なくとも一部の上部に配置された信号線と、を有する半導体基板からなる反射型液晶表示装置用の基板であって、

前記保持容量は、前記半導体基板に形成された拡散層からなる第1電極と、前記信号線と前記第1電極の間に配置された第2の導電層からなる第2電極とを有し、前記第1電極は前記スイッチ素子に接続され、前記第2電極には固定電位が供給されていることを特徴とする反射型液晶表示装置用の基板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012028888A JP5084958B2 (ja) | 2006-04-27 | 2012-02-13 | 反射型液晶表示装置及び反射型液晶表示装置用の基板 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006123411 | 2006-04-27 | ||

| JP2006123411 | 2006-04-27 | ||

| JP2012028888A JP5084958B2 (ja) | 2006-04-27 | 2012-02-13 | 反射型液晶表示装置及び反射型液晶表示装置用の基板 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007106059A Division JP5078416B2 (ja) | 2006-04-27 | 2007-04-13 | 反射型液晶表示装置及び反射型液晶表示装置用の基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012103733A true JP2012103733A (ja) | 2012-05-31 |

| JP5084958B2 JP5084958B2 (ja) | 2012-11-28 |

Family

ID=46394097

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012028888A Expired - Fee Related JP5084958B2 (ja) | 2006-04-27 | 2012-02-13 | 反射型液晶表示装置及び反射型液晶表示装置用の基板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5084958B2 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10325948A (ja) * | 1997-05-26 | 1998-12-08 | Matsushita Electron Corp | 反射型画像表示装置 |

| JPH1115021A (ja) * | 1997-06-26 | 1999-01-22 | Seiko Epson Corp | 液晶パネルおよび液晶パネル用基板および電子機器並びに投写型表示装置 |

| JP2004133147A (ja) * | 2002-10-10 | 2004-04-30 | Victor Co Of Japan Ltd | 液晶表示装置 |

| JP2004309681A (ja) * | 2003-04-04 | 2004-11-04 | Victor Co Of Japan Ltd | 反射型液晶表示装置 |

-

2012

- 2012-02-13 JP JP2012028888A patent/JP5084958B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10325948A (ja) * | 1997-05-26 | 1998-12-08 | Matsushita Electron Corp | 反射型画像表示装置 |

| JPH1115021A (ja) * | 1997-06-26 | 1999-01-22 | Seiko Epson Corp | 液晶パネルおよび液晶パネル用基板および電子機器並びに投写型表示装置 |

| JP2004133147A (ja) * | 2002-10-10 | 2004-04-30 | Victor Co Of Japan Ltd | 液晶表示装置 |

| JP2004309681A (ja) * | 2003-04-04 | 2004-11-04 | Victor Co Of Japan Ltd | 反射型液晶表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5084958B2 (ja) | 2012-11-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5078416B2 (ja) | 反射型液晶表示装置及び反射型液晶表示装置用の基板 | |

| KR100250852B1 (ko) | 액정표시장치 | |

| JP4003714B2 (ja) | 電気光学装置及び電子機器 | |

| US7701520B2 (en) | Liquid crystal panel and display device with data bus lines and auxiliary capacitance bus lines both extending in the same direction | |

| KR101562394B1 (ko) | 전기 광학 장치 및 전자 기기 | |

| JP5834733B2 (ja) | 電気光学装置、電子機器 | |

| JP5532797B2 (ja) | 電気光学装置及び電子機器 | |

| CN101206363B (zh) | 电光装置及电子设备 | |

| US7973868B2 (en) | Active matrix substrate, reflection type liquid crystal display apparatus and liquid crystal projector system | |

| KR100516250B1 (ko) | 전기 광학 장치 및 전자 기기 | |

| US20140003571A1 (en) | Shift register circuit, electro-optical device and electronic apparatus | |

| JP2004004540A (ja) | 電気光学装置、電気光学装置の駆動回路及び電子機器 | |

| US20020135549A1 (en) | Electro-optical apparatus and electronic unit | |

| JP5370221B2 (ja) | 電気光学装置及び電子機器 | |

| JPWO2009041112A1 (ja) | 表示装置 | |

| US20060113540A1 (en) | Reflective active matrix liquid crystal display and apparatus | |

| JP2004264534A (ja) | 反射型液晶表示装置 | |

| JP2008026348A (ja) | 電気光学装置及び電子機器 | |

| JP5084958B2 (ja) | 反射型液晶表示装置及び反射型液晶表示装置用の基板 | |

| JP4135547B2 (ja) | 反射型液晶表示装置 | |

| JPH07128687A (ja) | アクティブマトリックス型パネル装置 | |

| JP2000305105A (ja) | 液晶表示素子 | |

| JP2004184902A (ja) | 液晶表示装置 | |

| JP2004004541A (ja) | 電気光学装置、電気光学装置の駆動回路及び電子機器 | |

| JP2004361488A (ja) | 電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120807 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120904 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |