JP2012070319A - 画像処理方法、画像処理装置及び画像処理プログラム - Google Patents

画像処理方法、画像処理装置及び画像処理プログラム Download PDFInfo

- Publication number

- JP2012070319A JP2012070319A JP2010215144A JP2010215144A JP2012070319A JP 2012070319 A JP2012070319 A JP 2012070319A JP 2010215144 A JP2010215144 A JP 2010215144A JP 2010215144 A JP2010215144 A JP 2010215144A JP 2012070319 A JP2012070319 A JP 2012070319A

- Authority

- JP

- Japan

- Prior art keywords

- defective pixel

- pixel

- defective

- threshold

- threshold value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【解決手段】欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、欠陥画素検出対象画素の信号値との差分絶対値に対して、第一のしきい値と第一のしきい値より大きい第二のしきい値とによって欠陥画素検出対象画素が欠陥画素であるか否かを判定する(ステップST1〜ST6)。次に、差分絶対値が、第一のしきい値より大きく第二のしきい値より小さい場合は静的補正の対象として欠陥画素アドレスメモリに欠陥画素アドレスを登録し、差分絶対値が第二のしきい値より大きい場合は動的補正を行う画素として判定する(ステップST8〜ST12)。

【選択図】図2

Description

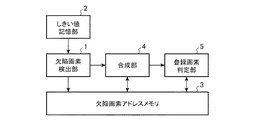

図1は、この発明の実施の形態1による画像処理方法を実施するための画像処理装置を示す構成図である。

図1に示す画像処理装置は、欠陥画素検出部1、しきい値記憶部2、欠陥画素アドレスメモリ3、合成部4、登録画素判定部5を備えている。

欠陥画素検出部1は、入力される欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、欠陥画素検出対象画素の信号値との差分絶対値に対して、しきい値記憶部2に記憶されている第一のしきい値(しきい値1)と、第一のしきい値より大きい第二のしきい値(しきい値2)とによって欠陥画素検出対象画素が欠陥画素であるか否かを判定するものである。しきい値記憶部2は、第一のしきい値と第二のしきい値とを記憶する記憶部である。欠陥画素アドレスメモリ3は、欠陥画素のアドレスを記憶するための記憶部であり、N枚分の欠陥画素のアドレスや合成された欠陥画素アドレス、さらに静的補正に用いるための最終的な欠陥画素のアドレスが記憶されるようになっている。合成部4は、欠陥画素アドレスメモリ3に記憶されているN枚の欠陥画素のアドレスの合成を行う処理部である。登録画素判定部5は、合成された欠陥画素のアドレスとしきい値との比較結果に基づいて、静的補正の対象として欠陥画素アドレスメモリ3に登録するか否かを決定する判定部である。

図2は、実施の形態1の画像処理方法を示すフローチャートである。

欠陥画素の検出にあたっては、従来技術と同様に「白キズ」検出用に遮光して撮影した黒画像と、「黒キズ」検出用に一定照度の光をあてた均一面を撮影した白画像の2枚の画像を用いる例について説明する。また、欠陥画素検出処理をプログラムで実現した場合について説明する。さらに、欠陥画素検出対象となる画像は一般的に撮影機器に使用されるベイヤー配列のイメージセンサで撮影した画像の場合について説明する。

本発明では、欠陥画素として判定するために予め与えられる二つのしきい値を用いる。

図3は二つのしきい値と欠陥画素レベルの判定内容を示した図である。図において、ブロック平均値は欠陥画素検出を行おうとする画素を含む所定の領域に含まれる同色の画素平均値を示している。欠陥画素検出対象の画素の信号レベルとブロック平均値の差分絶対値がしきい値2を超える値である場合(即ち検出対象画素の信号レベルが周辺画素の信号レベルから著しく乖離している場合)、欠陥画素検出部1は、これをレベル1の欠陥画素としてN(Nは1または2)枚目の欠陥画素アドレスメモリ3に登録する。また、欠陥画素検出対象の画素の信号レベルとブロック平均値の差分絶対値がしきい値1を超えてしきい値2以下である場合(即ち検出対象画素の信号レベルが周辺画素の信号レベルとそれほど乖離していない場合)、欠陥画素検出部1は、これをレベル0の欠陥画素としてN枚目の欠陥画素アドレスメモリ3に登録する。

1ライン目水平アドレス昇順

2ライン目水平アドレス昇順

: :

Mライン目水平アドレス昇順

また、明瞭な欠陥画素とは図3でしきい値2を超える(図4でF=1として登録された)欠陥画素であり、不明瞭な欠陥画素とは図3でしきい値1を超えかつしきい値2以下の(図4でF=0として登録された)欠陥画素である。

なお、本願発明の範囲内において、実施の形態を適宜、変更、省略等することが可能である。

Claims (7)

- 欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、前記欠陥画素検出対象画素の信号値との差分絶対値に対して、第一のしきい値と当該第一のしきい値より大きい第二のしきい値とによって前記欠陥画素検出対象画素が欠陥画素であるか否かを判定する欠陥画素判定ステップと、

前記差分絶対値が、前記第一のしきい値より大きく前記第二のしきい値より小さい場合は静的補正の対象として欠陥画素アドレスメモリに欠陥画素アドレスを登録し、前記差分絶対値が前記第二のしきい値より大きい場合は動的補正を行う画素として判定する登録画素判定ステップとを備えた画像処理方法。 - 欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、前記欠陥画素検出対象画素の信号値との差分絶対値が、所定のしきい値を超える場合は、前記欠陥画素検出対象画素が欠陥画素であると判定する欠陥画素判定ステップと、

前記欠陥画素が、独立した画素として存在する単キズであるか、連続した画素として存在する連キズであるかを判定する連キズ判定ステップと、

前記連キズ判定ステップでの判定結果が連キズであった場合は、静的補正の対象として欠陥画素アドレスメモリに登録を行う登録画素判定ステップとを備えた画像処理方法。 - 欠陥画素判定ステップでは、第一のしきい値と、当該第一のしきい値より大きい第二のしきい値とを設け、これら第一及び第二のしきい値との比較により判定を行い、

登録画素判定ステップでは、単キズの差分絶対値が前記第一のしきい値より大きく前記第二のしきい値より小さい場合は静的補正の対象として欠陥画素アドレスメモリへの登録を行うことを特徴とする請求項2記載の画像処理方法。 - 欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、前記欠陥画素検出対象画素の信号値との差分絶対値に対して、第一のしきい値と当該第一のしきい値より大きい第二のしきい値とによって前記欠陥画素検出対象画素が欠陥画素であるか否かを判定する欠陥画素検出部と、

前記差分絶対値が、前記第一のしきい値より大きく前記第二のしきい値より小さい場合は静的補正の対象として欠陥画素アドレスメモリに欠陥画素アドレスを登録し、前記差分絶対値が前記第二のしきい値より大きい場合は動的補正を行う画素として判定する登録画素判定部とを備えた画像処理装置。 - 欠陥画素検出対象画素を含む所定サイズのブロックの平均信号値と、前記欠陥画素検出対象画素の信号値との差分絶対値が、所定のしきい値を超える場合は、前記欠陥画素検出対象画素が欠陥画素であると判定する欠陥画素検出部と、

前記欠陥画素が、独立した画素として存在する単キズであるか、連続した画素として存在する連キズであるかを判定し、当該判定結果が連キズであった場合は、静的補正の対象として欠陥画素アドレスメモリに登録を行う登録画素判定部とを備えた画像処理装置。 - 欠陥画素検出部では、第一のしきい値と、当該第一のしきい値より大きい第二のしきい値とを設け、これら第一及び第二のしきい値との比較により判定を行い、

登録画素判定部では、単キズの差分絶対値が前記第一のしきい値より大きく前記第二のしきい値より小さい場合は静的補正の対象として欠陥画素アドレスメモリへの登録を行うことを特徴とする請求項5記載の画像処理装置。 - 請求項1から請求項3のうちのいずれか1項記載の画像処理方法をコンピュータに実行させるための画像処理プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010215144A JP2012070319A (ja) | 2010-09-27 | 2010-09-27 | 画像処理方法、画像処理装置及び画像処理プログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010215144A JP2012070319A (ja) | 2010-09-27 | 2010-09-27 | 画像処理方法、画像処理装置及び画像処理プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012070319A true JP2012070319A (ja) | 2012-04-05 |

| JP2012070319A5 JP2012070319A5 (ja) | 2013-06-27 |

Family

ID=46167018

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010215144A Pending JP2012070319A (ja) | 2010-09-27 | 2010-09-27 | 画像処理方法、画像処理装置及び画像処理プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012070319A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2018101940A (ja) * | 2016-12-21 | 2018-06-28 | 株式会社リコー | 光電変換装置、光電変換方法及び画像形成装置 |

| WO2018198916A1 (ja) * | 2017-04-24 | 2018-11-01 | 日本電気株式会社 | 画像処理装置、画像処理方法及び記憶媒体 |

| US10404930B2 (en) | 2014-11-13 | 2019-09-03 | Samsung Electronics Co., Ltd. | Pixel processing apparatus of processing bad pixel and removing noise, and image signal processing apparatus and image processing system each including the same |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000287135A (ja) * | 1999-03-31 | 2000-10-13 | Sony Corp | 撮像装置並びに固体撮像素子の画素欠陥検出装置及び方法 |

| JP2004015191A (ja) * | 2002-06-04 | 2004-01-15 | Fuji Photo Film Co Ltd | 固体撮像素子の欠陥補正装置及び方法 |

| JP2005109878A (ja) * | 2003-09-30 | 2005-04-21 | Hitachi Kokusai Electric Inc | 固体撮像素子の映像信号補正方法 |

| JP2005223398A (ja) * | 2004-02-03 | 2005-08-18 | Matsushita Electric Ind Co Ltd | 撮像装置 |

| JP2006345279A (ja) * | 2005-06-09 | 2006-12-21 | Fujifilm Holdings Corp | 固体撮像素子の画素欠陥検出方法 |

| JP2007124056A (ja) * | 2005-10-25 | 2007-05-17 | Canon Inc | 画像処理装置、制御方法、及びプログラム |

| JP2008236491A (ja) * | 2007-03-22 | 2008-10-02 | Fujifilm Corp | 撮像素子画像処理方法 |

| JP2009130553A (ja) * | 2007-11-22 | 2009-06-11 | Acutelogic Corp | 欠陥画素補正方法、欠陥画素補正プログラム及び欠陥画素補正装置 |

| JP2011166422A (ja) * | 2010-02-09 | 2011-08-25 | Ricoh Co Ltd | 撮像装置 |

-

2010

- 2010-09-27 JP JP2010215144A patent/JP2012070319A/ja active Pending

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000287135A (ja) * | 1999-03-31 | 2000-10-13 | Sony Corp | 撮像装置並びに固体撮像素子の画素欠陥検出装置及び方法 |

| JP2004015191A (ja) * | 2002-06-04 | 2004-01-15 | Fuji Photo Film Co Ltd | 固体撮像素子の欠陥補正装置及び方法 |

| JP2005109878A (ja) * | 2003-09-30 | 2005-04-21 | Hitachi Kokusai Electric Inc | 固体撮像素子の映像信号補正方法 |

| JP2005223398A (ja) * | 2004-02-03 | 2005-08-18 | Matsushita Electric Ind Co Ltd | 撮像装置 |

| JP2006345279A (ja) * | 2005-06-09 | 2006-12-21 | Fujifilm Holdings Corp | 固体撮像素子の画素欠陥検出方法 |

| JP2007124056A (ja) * | 2005-10-25 | 2007-05-17 | Canon Inc | 画像処理装置、制御方法、及びプログラム |

| JP2008236491A (ja) * | 2007-03-22 | 2008-10-02 | Fujifilm Corp | 撮像素子画像処理方法 |

| JP2009130553A (ja) * | 2007-11-22 | 2009-06-11 | Acutelogic Corp | 欠陥画素補正方法、欠陥画素補正プログラム及び欠陥画素補正装置 |

| JP2011166422A (ja) * | 2010-02-09 | 2011-08-25 | Ricoh Co Ltd | 撮像装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10404930B2 (en) | 2014-11-13 | 2019-09-03 | Samsung Electronics Co., Ltd. | Pixel processing apparatus of processing bad pixel and removing noise, and image signal processing apparatus and image processing system each including the same |

| JP2018101940A (ja) * | 2016-12-21 | 2018-06-28 | 株式会社リコー | 光電変換装置、光電変換方法及び画像形成装置 |

| WO2018198916A1 (ja) * | 2017-04-24 | 2018-11-01 | 日本電気株式会社 | 画像処理装置、画像処理方法及び記憶媒体 |

| JPWO2018198916A1 (ja) * | 2017-04-24 | 2020-02-27 | 日本電気株式会社 | 画像処理装置、画像処理方法及び記憶媒体 |

| US11039096B2 (en) | 2017-04-24 | 2021-06-15 | Nec Corporation | Image processing device, image processing method and storage medium |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5269841B2 (ja) | 画像処理装置 | |

| US20030179418A1 (en) | Producing a defective pixel map from defective cluster pixels in an area array image sensor | |

| US20070058056A1 (en) | Method and apparatus for real time identification and correction of pixel defects for image sensor arrays | |

| CN103139492B (zh) | 摄像装置、摄像方法以及监视系统 | |

| JP2011071616A (ja) | 画像処理装置 | |

| JP2005123946A (ja) | 欠陥画素検出方法、検出装置および撮像装置 | |

| JP2012054790A (ja) | 画像処理装置 | |

| JP2009302722A (ja) | 欠陥画素処理装置および欠陥画素処理方法 | |

| US7702179B2 (en) | Method and related compensation circuit for compensating black cores of an image sensor | |

| JP4985124B2 (ja) | 画像処理装置、画像処理方法、及び画像処理プログラム | |

| JP4591046B2 (ja) | 欠陥検出補正回路及び欠陥検出補正方法 | |

| JP2013168793A (ja) | 画像処理装置 | |

| JP2010021858A (ja) | 画素欠陥補正装置 | |

| JP2012070319A (ja) | 画像処理方法、画像処理装置及び画像処理プログラム | |

| JP5262953B2 (ja) | 画像処理装置、画像処理方法及びプログラム | |

| JP4331120B2 (ja) | 欠陥画素検出方法 | |

| JP2010068329A (ja) | 撮像装置 | |

| JP2006166194A (ja) | 画素欠陥検出回路及び画素欠陥検出方法 | |

| JP2010010760A (ja) | 撮像装置および方法 | |

| JP2007306506A (ja) | 撮像装置 | |

| JP2008148115A (ja) | 方向検出を用いた撮像デバイスの画像欠陥補正システム | |

| JP2011114473A (ja) | 画素欠陥補正装置 | |

| JP2009290653A (ja) | 欠陥画素補正装置、撮像装置、欠陥画素補正方法、およびプログラム | |

| JP4397869B2 (ja) | スミア補正方法及びスミア補正回路 | |

| JP2010050730A (ja) | 撮像装置及び欠陥補正装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130515 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130515 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140207 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140909 |