JP2010510656A - 誘電性アンチヒューズと直列にシリサイドに隣接して結晶化されたp−i−nダイオードおよびその形成方法 - Google Patents

誘電性アンチヒューズと直列にシリサイドに隣接して結晶化されたp−i−nダイオードおよびその形成方法 Download PDFInfo

- Publication number

- JP2010510656A JP2010510656A JP2009537188A JP2009537188A JP2010510656A JP 2010510656 A JP2010510656 A JP 2010510656A JP 2009537188 A JP2009537188 A JP 2009537188A JP 2009537188 A JP2009537188 A JP 2009537188A JP 2010510656 A JP2010510656 A JP 2010510656A

- Authority

- JP

- Japan

- Prior art keywords

- dielectric

- layer

- silicide

- conductor

- germanide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 73

- 229910021332 silicide Inorganic materials 0.000 title claims abstract description 47

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 title claims abstract description 47

- 230000015654 memory Effects 0.000 claims abstract description 128

- 239000004065 semiconductor Substances 0.000 claims abstract description 101

- 239000000463 material Substances 0.000 claims abstract description 79

- 230000000903 blocking effect Effects 0.000 claims abstract description 36

- 239000000758 substrate Substances 0.000 claims abstract description 34

- 238000000231 atomic layer deposition Methods 0.000 claims abstract description 9

- 239000004020 conductor Substances 0.000 claims description 128

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 34

- 239000010703 silicon Substances 0.000 claims description 33

- 229910052710 silicon Inorganic materials 0.000 claims description 32

- SCCCLDWUZODEKG-UHFFFAOYSA-N germanide Chemical compound [GeH3-] SCCCLDWUZODEKG-UHFFFAOYSA-N 0.000 claims description 25

- 230000015556 catabolic process Effects 0.000 claims description 15

- 229910018072 Al 2 O 3 Inorganic materials 0.000 claims description 14

- 229910017052 cobalt Inorganic materials 0.000 claims description 11

- 239000010941 cobalt Substances 0.000 claims description 11

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 11

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 11

- 229910052732 germanium Inorganic materials 0.000 claims description 10

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 9

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims description 9

- 229910045601 alloy Inorganic materials 0.000 claims description 9

- 239000000956 alloy Substances 0.000 claims description 9

- 239000010936 titanium Substances 0.000 claims description 9

- 229910052719 titanium Inorganic materials 0.000 claims description 9

- 229910017121 AlSiO Inorganic materials 0.000 claims description 8

- 229910003855 HfAlO Inorganic materials 0.000 claims description 8

- 229910004129 HfSiO Inorganic materials 0.000 claims description 8

- 229910021193 La 2 O 3 Inorganic materials 0.000 claims description 8

- -1 Ta 2 O 5 Inorganic materials 0.000 claims description 8

- 229910010413 TiO 2 Inorganic materials 0.000 claims description 8

- 229910006501 ZrSiO Inorganic materials 0.000 claims description 8

- 238000000151 deposition Methods 0.000 claims description 6

- 239000003989 dielectric material Substances 0.000 claims description 6

- 238000005530 etching Methods 0.000 claims description 6

- 238000000059 patterning Methods 0.000 claims description 5

- 229910021341 titanium silicide Inorganic materials 0.000 claims description 5

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 2

- DDHRUTNUHBNAHW-UHFFFAOYSA-N cobalt germanium Chemical compound [Co].[Ge] DDHRUTNUHBNAHW-UHFFFAOYSA-N 0.000 claims 2

- 230000007547 defect Effects 0.000 abstract description 13

- 239000010410 layer Substances 0.000 description 126

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 31

- 230000004888 barrier function Effects 0.000 description 17

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 13

- 239000000377 silicon dioxide Substances 0.000 description 13

- 235000012239 silicon dioxide Nutrition 0.000 description 13

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 6

- 229920005591 polysilicon Polymers 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 239000012790 adhesive layer Substances 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000002019 doping agent Substances 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229920002120 photoresistant polymer Polymers 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 230000006399 behavior Effects 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 239000012777 electrically insulating material Substances 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910000927 Ge alloy Inorganic materials 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229910000676 Si alloy Inorganic materials 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- AXQKVSDUCKWEKE-UHFFFAOYSA-N [C].[Ge].[Si] Chemical compound [C].[Ge].[Si] AXQKVSDUCKWEKE-UHFFFAOYSA-N 0.000 description 1

- 238000004026 adhesive bonding Methods 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 230000003190 augmentative effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Landscapes

- Semiconductor Memories (AREA)

Abstract

Description

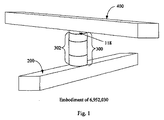

本願は、2006年11月15日に出願された「P-I-N Diode Crystallized Adjacent to a Silicide in Series with a Dielectric Antifuse」という米国特許出願第11/560,289号(特許文献1)、および2006年11月15日に出願された「Method for Making a P-I-N Diode Crystallized Adjacent to a Silicide in Series with a Dielectric Antifuse」という米国特許出願第11/560,283号(特許文献2)に基づいて優先権主張し、それぞれがあらゆる目的のためにその全体が本願明細書において参照により援用されている。

以下に、好ましい態様および実施形態を、添付図面を参照して説明する。

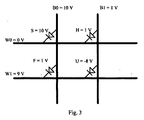

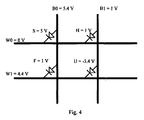

’030特許および’549出願のダイオードは、シリコンなどの半導体材料をアモルファス状態で堆積することによって形成され、次いで、熱アニールを行ってシリコンを結晶化し、多結晶シリコンまたはポリシリコンダイオードを形成する。’530出願で説明するように、堆積されたアモルファスシリコンが、二酸化ケイ素および窒化チタンなどの、アモルファスシリコンが高い格子不整合を有する材料との単なる接触で結晶化される場合、ポリシリコンは、結晶欠陥の増加とともに生じ、その結果、ポリシリコンに高抵抗を引き起こす。この高欠陥ポリシリコンによるプログラミングパルスの適用は、外見上、ポリシリコンを変えられ、その結果、ポリシリコンに低抵抗を引き起こす。

HfO2 またはAl2 O3 などのhigher−k材料の層は、誘電性遮断アンチヒューズとして機能を果たし、同じ電気的挙動を有するとともに、比較可能な質の二酸化ケイ素などのlower−k材料の層より厚くすることができる。

多くのhigh−k誘電体は、ALDを含む様々な堆積プロセスによって比較的低温で形成することができる。概して、加工温度を低くすることは、複雑な半導体装置の組立てにおいて常に有利であり、ドーパントの拡散、ピーリングなどを最小限にする。

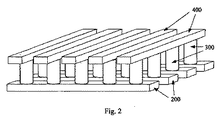

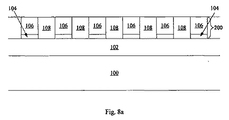

図8aを参照すると、メモリの形成は、基板100から開始する。この基板100は、そのような基板上の、単結晶シリコン、シリコン−ゲルマニウムまたはシリコン−ゲルマニウム−炭素などのIV−IV化合物、III−V化合物、II−VII化合物、エピタキシャル層、または他の任意の半導体材料などの本技術分野で公知の任意の半導体基板とすることができる。基板は、そこで製造された集積回路を含んでいてもよい。

絶縁層102は、基板100上に形成されている。絶縁層102は、酸化ケイ素、窒化ケイ素、Si−C−O−Hフィルムまたは他の適切な絶縁材料とすることができる。

支柱にパターン化される次の半導体材料を堆積する。半導体材料は、シリコン、ゲルマニウム、シリコン−ゲルマニウム合金、または他の適切な半導体、または半導体合金とすることができる。簡単にするために、ここでの説明は、半導体材料をシリコンと称するが、当然のことながら、当業者は、代わりに、これらの他の適切な材料のうちのいずれかを選択してもよい。

誘電体108は、半導体支柱300上に、および半導体支柱300間に堆積されて、それらの間のギャップを満たす。誘電体108は、酸化ケイ素、窒化ケイ素、または酸窒化ケイ素などの任意の公知の電気的絶縁材料とすることができる。好ましい実施形態では、二酸化ケイ素は、絶縁材料として使用される。

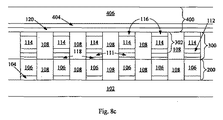

図8cを参照すると、支柱300上に形成された任意の自然酸化物を洗浄後、シリサイド形成金属、例えば、チタン、コバルト、クロム、タンタル、プラチナ、ニッケル、ニオブまたはパラジウムの層120が堆積される。層120は、チタンまたはコバルトであることが好ましい。層120がチタンであるなら、

その厚みは、約10〜約100Åであることが好ましく、約20Åであることが最も好ましい。窒化チタン層404は層120に続く。両方の層120、404は、約20〜約100Åであることが好ましく、約50Åであることが最も好ましい。次に、導電材料、例えば、タングステンの層406が堆積される。層406、404、120は、パターン化され、レール形状の上部導電体400にエッチングされ、下部導電体200に垂直な方向に延在することが好ましい。

第1のメモリレベルの形成が記載されてきた。増設メモリレベルは、この第1のメモリレベル上に形成されて、モノリシックな3次元メモリアレイを形成することができる。これまでに記載されたアレイは、単に1例であり、例えば、図6、図7に示すメモリセルのどちらかを含めて、他のように異なっていてもよい。

実施形態によっては、導電体は、メモリレベル間で共有されることができ、つまり、上部導電体400は、前述した次のメモリレベルの下部導電体として役立つ。他の実施形態では、中間誘電体(図示せず)は、図8cの第1のメモリレベル上に形成され、その表面は平坦化され、第2のメモリレベルの構成は、共有された導電体を有することなく、この平坦化中間誘電体上で開始する。

前の詳細な説明は、本発明がとることができる多くの形態のうちの2,3のみについて記載した。このため、この詳細な説明は、限定の目的でではなく実例の目的で意図される。すべての均等物を含む以下の特許請求の範囲のみが、本発明の範囲を定義するように意図される。

Claims (47)

- 半導体装置であって、

シリサイド層、ジャーマナイド層またはシリサイド−ジャーマナイド層に隣接して結晶化され、堆積された半導体材料からなる隣接するp−i−nダイオードと、

ダイオードを有する電気的に直列に配置され、8より大きい誘電率を有する誘電体を含む誘電性遮断アンチヒューズと、

を含む半導体装置。 - 請求項1記載の半導体装置において、

半導体材料は、多結晶である半導体装置。 - 請求項1記載の半導体装置において、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択される半導体装置。 - 請求項3記載の半導体装置において、

誘電体は、HfO2 またはAl2 O3 である半導体装置。 - 請求項1記載の半導体装置において、

シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層は、(a)チタンシリサイド、チタンシリサイド−ジャーマナイド、またはチタンジャーマナイド、または(b)コバルトシリサイド、コバルトシリサイド−ジャーマナイド、またはコバルトジャーマナイドである半導体装置。 - 請求項1記載の半導体装置において、

半導体材料は、シリコン、ゲルマニウムおよび/またはシリコン−ゲルマニウム合金を含む半導体装置。 - 請求項6記載の半導体装置において、

隣接するp−i−nダイオードは、隣接するp−i−nダイオードの下の下部導電体と隣接するp−i−nダイオードの上の上部導電体との間で垂直に配向され配置され、

誘電性遮断アンチヒューズは、隣接するp−i−nダイオードと上部導電体との間、または隣接するp−i−nダイオードと下部導電体との間に配置される半導体装置。 - 請求項7記載の半導体装置において、

上部導電体または下部導電体は、シリコン層を含まない半導体装置。 - 請求項7記載の半導体装置において、

シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層は、隣接するp−i−nダイオードの上にあり、

誘電性遮断アンチヒューズは、隣接するp−i−nダイオードの下にある半導体装置。 - 請求項7記載の半導体装置において、

誘電性遮断アンチヒューズは、約50Å以下の厚みである半導体装置。 - 請求項10記載の半導体装置において、

誘電性遮断アンチヒューズは、約20Å以下の厚みである半導体装置。 - 請求項10記載の半導体装置において、

誘電性遮断アンチヒューズは、原子層成長法によって形成される半導体装置。 - 請求項10記載の半導体装置において、

誘電性遮断アンチヒューズの一部は、絶縁破壊を受けて、隣接するp−i−nダイオードと上部導電体との間、または隣接するp−i−nダイオードと下部導電体との間で、誘電性遮断アンチヒューズを通る導電性パスを形成する半導体装置。 - 請求項6記載の半導体装置において、

下部導電体、隣接するp−i−nダイオードおよび上部導電体は、すべて、半導体基板の上に形成される半導体装置。 - 請求項6記載の半導体装置において、

隣接するp−i−nダイオードは、支柱の形態である半導体装置。 - 請求項1記載の半導体装置において、

シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層は、完成装置内に存在しない半導体装置。 - 第1のメモリレベルであって、

基板上に形成された複数の第1の実質的に平行で実質的に共平面の導電体と、

第1の導電体上に形成された複数の第2の実質的に平行で実質的に共平面の導電体と、

シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層に隣接して結晶化された半導体材料を含む、複数の垂直に配向された隣接するp−i−nダイオードと、

約8より大きな誘電率を有する誘電体からなる複数の誘電性遮断アンチヒューズと、

それぞれが、隣接するp−i−nダイオードのうちの1つと、および誘電性遮断アンチヒューズのうちの1つとを含む複数のメモリセルと、を含み、

各隣接するp−i−nダイオードは、第1の導電体のうちの1つと第2の導電体のうちの1つとの間に配置され、

各誘電性遮断アンチヒューズは、第1の導電体のうちの1つと隣接するp−i−nダイオードのうちの1つとの間、または第2の導電体のうちの1つと隣接するp−i−nダイオードのうちの1つとの間に配置される第1のメモリレベル。 - 請求項17記載の第1のメモリレベルにおいて、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択される第1のメモリレベル。 - 請求項17記載の第1のメモリレベルにおいて、

半導体材料は、シリコン、ゲルマニウムおよび/またはシリコン−ゲルマニウム合金を含む第1のメモリレベル。 - 請求項17記載の第1のメモリレベルにおいて、

誘電性遮断アンチヒューズは、隣接するp−i−nダイオードの下に配置される第1のメモリレベル。 - 請求項17記載の第1のメモリレベルにおいて、

誘電性遮断アンチヒューズは、隣接するp−i−nダイオードの下に配置され、シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層は、隣接するp−i−nダイオード上に配置される第1のメモリレベル。 - 請求項17記載の第1のメモリレベルにおいて、

少なくとも第2のメモリレベルが、第1のメモリレベル上にモノリシックに形成される第1のメモリレベル。 - 基板上に形成されたモノリシックな3次元メモリアレイであって、

(a)基板上にモノリシックに形成され、(i)第1の方向に延在する複数の第1の実質的に平行で実質的に共平面の導電体と、(ii)第1の方向と異なる第2の方向に延在し、第1の導電体上にある、複数の第2の実質的に平行で実質的に共平面の導電体と、(iii)それぞれが第1の導電体のうちの1つと第2の導電体のうちの1つとの間に垂直に配置され、シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層に隣接して結晶化され、堆積された半導体材料からなる複数の垂直に配向された隣接するp−i−nダイオードと、(iv)8より大きい誘電率を有する誘電体からなる複数の誘電性遮断アンチヒューズと、(v)それぞれが、ダイオードのうちの1つと、直列に配置された誘電性遮断アンチヒューズのうちの1つと、を含む複数のメモリセルと、を含む第1のメモリレベルと、

(b)第1のメモリレベル上にモノリシックに形成された第2のメモリレベルと、

を含むモノリシックな3次元メモリアレイ。 - 請求項23記載のモノリシックな3次元メモリアレイにおいて、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択されるモノリシックな3次元メモリアレイ。 - 不揮発性メモリセルを形成し、プログラムする方法であって、

堆積された半導体材料を含む隣接するp−i−nダイオードを形成するステップと、

堆積された半導体材料に接してシリサイド、シリサイド−ジャーマナイドまたはジャーマナイドの層を形成するステップと、

シリサイド、シリサイド−ジャーマナイドまたはジャーマナイドの層に接して、堆積された半導体材料を結晶化させるステップと、

8より大きい誘電率を有する誘電体の層を形成するステップと、

誘電体の層の一部を絶縁破壊にさらすステップと、を含み、

メモリセルは、隣接するp−i−nダイオードおよび誘電体の層を含む方法。 - 請求項25記載の方法において、

誘電体の層は、原子層成長法によって堆積される方法。 - 請求項25記載の方法において、

誘電体の層は、厚みが50Å以下である方法。 - 請求項27記載の方法において、

誘電体の層は、厚みが20Å以下である方法。 - 請求項25記載の方法において、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択される方法。 - 請求項29記載の方法において、

誘電体は、HfO2 またはAl2 O3 である方法。 - 請求項25記載の方法において、

堆積された半導体材料は、シリコン、ゲルマニウムまたはシリコン−ゲルマニウム合金を含む方法。 - 請求項25記載の方法において、

シリサイド、シリサイド−ジャーマナイドまたはジャーマナイドは、(a)チタンシリサイド、チタンシリサイド−ジャーマナイドまたはチタンジャーマナイド、または(b)コバルトシリサイド、コバルトシリサイド−ジャーマナイドまたはコバルトジャーマナイドである方法。 - 請求項25記載の方法において、

隣接するp−i−nダイオードは、第1の導電体と第2の導電体との間に配置され、誘電体の層は、(a)隣接するp−i−nダイオードと第1の導電体との間、または(b)隣接するp−i−nダイオードと第2の導電体との間に配置される方法。 - 請求項33記載の方法において、

第1の導電体と第2の導電体との間にプログラミング電圧を印加することによって、誘電層の一部を絶縁破壊にさらすステップが達成される方法。 - 請求項34記載の方法において、

プログラミング電圧は、約8Vを超えない方法。 - 請求項33記載の方法において、

隣接するp−i−nダイオードは、垂直に配向され、第1の導電体と第2の導電体との間に垂直に配置され、第2の導電体は、第1の導電体上にある方法。 - 請求項36記載の方法において、

隣接するp−i−nダイオードを形成するステップは、

第1の導電体を形成するステップと、

第1の導電体を形成するステップ後に、第1の導電体上に半導体積層を堆積するステップと、

単独のパターン化ステップで支柱の形態で、半導体積層をパターン化しエッチングするステップと、

半導体積層をパターン化およびエッチングするステップ後に、支柱上に第2の導電体を形成するステップと、を含み、

装置の完成後、隣接するp−i−nダイオードは、支柱内に配置される方法。 - 請求項25記載の方法において、

誘電体の層の一部を絶縁破壊にさらすステップの間にメモリセルがプログラムされる方法。 - 請求項25記載の方法において、

半導体材料は、多結晶である方法。 - 基板上に第1のメモリレベルをモノリシックに形成する方法であって、

第1の方向に延在する、複数の第1の実質的に平行で実質的に共平面の導電体を基板上に形成するステップと、

第1の導電体上に複数の垂直に配向され、シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層に接して結晶化された半導体材料を含む隣接するp−i−nダイオードを形成するステップと、

それぞれが第1の導電体のうちの1つと第2の導電体のうちの1つとの間に垂直に配置される隣接するp−i−nダイオード上にあり、第1の方向と異なる第2の方向に延在する、複数の第2の実質的に平行で実質的に共平面の導電体を形成するステップと、

それぞれが、隣接するp−i−nダイオードのうちの1つと第1の導電体のうちの1つとの間、または隣接するp−i−nダイオードのうちの1つと第2の導電体のうちの1つとの間に配置された、複数の誘電性遮断アンチヒューズを形成するステップと、を含み、

誘電性遮断アンチヒューズは、約8より大きな誘電率を有する誘電体を含む方法。 - 請求項40記載の方法において、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択される方法。 - 請求項40記載の方法において、

半導体材料は、シリコン、ゲルマニウムおよび/またはシリコン−ゲルマニウム合金を含む方法。 - 請求項40記載の方法において、

(a)誘電性遮断アンチヒューズは、ダイオードの下に配置され、シリサイド、シリサイド−ジャーマナイドまたはジャーマナイド層は、ダイオード上に配置される方法。 - 請求項40記載の方法において、

基板は、単結晶シリコンを含む方法。 - 請求項40記載の方法において、

少なくとも第2のメモリレベルは、第1のメモリレベル上にモノリシックに形成される方法。 - モノリシックな3次元メモリアレイを基板上に形成する方法であって、

(a)基板上に、(i)第1の方向に延在する複数の第1の実質的に平行で実質的に共平面の導電体を形成するステップと、(ii)第1の方向と異なる第2の方向に延在し、第1の導電体上にある複数の第2の実質的に平行で実質的に共平面の導電体を形成するステップと、(iii)シリサイド層、シリサイド−ジャーマナイド層またはジャーマナイド層に接して結晶化され、堆積された半導体材料からなり、それぞれが第1の導電体のうちの1つと第2の導電体のうちの1つとの間に垂直に配置された、複数の垂直に配向された隣接するp−i−nダイオードを形成するステップと、(iv)8より大きい誘電率を有する誘電体からなる複数の誘電性遮断アンチヒューズを形成するステップと、(v)それぞれがダイオードのうちの1つと直列に配置された誘電性遮断アンチヒューズのうちの1つを含む、複数のメモリセルを形成するステップと、を含む方法により形成される第1のメモリレベルをモノリシックに形成するステップと、

(b)第1のメモリレベル上に第2のメモリレベルをモノリシックに形成するステップと、

を含む方法。 - 請求項46記載の方法において、

誘電体は、HfO2 、Al2 O3 、ZrO2 、TiO2 、La2 O3 、Ta2 O5 、RuO2 、ZrSiOx 、AlSiOx 、HfSiOx 、HfAlOx 、HfSiON、ZrSiAlOx 、HfSiAlOx 、HfSiAlONおよびZrSiAlONからなる群から選択される方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/560,289 US8018024B2 (en) | 2003-12-03 | 2006-11-15 | P-i-n diode crystallized adjacent to a silicide in series with a dielectric antifuse |

| US11/560,283 US7682920B2 (en) | 2003-12-03 | 2006-11-15 | Method for making a p-i-n diode crystallized adjacent to a silicide in series with a dielectric antifuse |

| PCT/US2007/023855 WO2008060543A2 (en) | 2006-11-15 | 2007-11-13 | P-i-n diode crystallized adjacent to a silicide in series with a dielectric antifuse and methods of forming the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010510656A true JP2010510656A (ja) | 2010-04-02 |

| JP2010510656A5 JP2010510656A5 (ja) | 2010-10-21 |

Family

ID=42211734

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009537188A Pending JP2010510656A (ja) | 2006-11-15 | 2007-11-13 | 誘電性アンチヒューズと直列にシリサイドに隣接して結晶化されたp−i−nダイオードおよびその形成方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2010510656A (ja) |

| TW (1) | TWI424535B (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009289963A (ja) * | 2008-05-29 | 2009-12-10 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| JP2012023374A (ja) * | 2010-07-13 | 2012-02-02 | Crossbar Inc | 二端子抵抗性スイッチングデバイス構造及びその製造方法 |

| JP2012028765A (ja) * | 2010-07-09 | 2012-02-09 | Crossbar Inc | SiGe材料を使用する抵抗性メモリー |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4719910B2 (ja) * | 2008-11-26 | 2011-07-06 | 国立大学法人東北大学 | 半導体装置の製造方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06302700A (ja) * | 1993-04-19 | 1994-10-28 | Kawasaki Steel Corp | 半導体装置およびその製造方法 |

| JPH08139197A (ja) * | 1994-11-11 | 1996-05-31 | Tadahiro Omi | シリサイド反応を利用した半導体装置 |

| JP2003197867A (ja) * | 2001-12-14 | 2003-07-11 | Hewlett Packard Co <Hp> | メモリ構造における連続アンチヒューズ材料 |

| JP2003203864A (ja) * | 2002-01-09 | 2003-07-18 | Sangaku Renkei Kiko Kyushu:Kk | 半導体薄膜の製造方法 |

| JP2004327677A (ja) * | 2003-04-24 | 2004-11-18 | Sharp Corp | 半導体膜およびその製造方法 |

| JP2005347468A (ja) * | 2004-06-02 | 2005-12-15 | Matsushita Electric Ind Co Ltd | 不揮発性メモリ |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050158950A1 (en) * | 2002-12-19 | 2005-07-21 | Matrix Semiconductor, Inc. | Non-volatile memory cell comprising a dielectric layer and a phase change material in series |

-

2007

- 2007-11-13 JP JP2009537188A patent/JP2010510656A/ja active Pending

- 2007-11-15 TW TW96143253A patent/TWI424535B/zh not_active IP Right Cessation

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06302700A (ja) * | 1993-04-19 | 1994-10-28 | Kawasaki Steel Corp | 半導体装置およびその製造方法 |

| JPH08139197A (ja) * | 1994-11-11 | 1996-05-31 | Tadahiro Omi | シリサイド反応を利用した半導体装置 |

| JP2003197867A (ja) * | 2001-12-14 | 2003-07-11 | Hewlett Packard Co <Hp> | メモリ構造における連続アンチヒューズ材料 |

| JP2003203864A (ja) * | 2002-01-09 | 2003-07-18 | Sangaku Renkei Kiko Kyushu:Kk | 半導体薄膜の製造方法 |

| JP2004327677A (ja) * | 2003-04-24 | 2004-11-18 | Sharp Corp | 半導体膜およびその製造方法 |

| JP2005347468A (ja) * | 2004-06-02 | 2005-12-15 | Matsushita Electric Ind Co Ltd | 不揮発性メモリ |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009289963A (ja) * | 2008-05-29 | 2009-12-10 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| JP2012028765A (ja) * | 2010-07-09 | 2012-02-09 | Crossbar Inc | SiGe材料を使用する抵抗性メモリー |

| JP2012023374A (ja) * | 2010-07-13 | 2012-02-02 | Crossbar Inc | 二端子抵抗性スイッチングデバイス構造及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI424535B (zh) | 2014-01-21 |

| TW200837897A (en) | 2008-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7682920B2 (en) | Method for making a p-i-n diode crystallized adjacent to a silicide in series with a dielectric antifuse | |

| US8633567B2 (en) | Devices including a P-I-N diode disposed adjacent a silicide in series with a dielectric material | |

| TWI441263B (zh) | 具有大且均勻之電流的上指p-i-n二極體的大型陣列及其形成方法 | |

| US8349663B2 (en) | Vertical diode based memory cells having a lowered programming voltage and methods of forming the same | |

| KR101128246B1 (ko) | 비-휘발성 프로그램 가능한 메모리 | |

| US7855119B2 (en) | Method for forming polycrystalline thin film bipolar transistors | |

| JP5139269B2 (ja) | 半導体ダイオードを含む低温で製作された高密度不揮発性メモリアレイ | |

| CN101313423B (zh) | 包含氧化镍钴切换元件的存储单元 | |

| US20100288996A1 (en) | Memory arrays including memory levels that share conductors, and methods of forming such memory arrays | |

| CN101878508A (zh) | 多个反熔丝存储器单元以及形成、编程和测试该器件的方法 | |

| CN101553925B (zh) | 邻近于硅化物而结晶的与介电反熔丝串联的p-i-n二极管及其形成方法 | |

| JP2010510656A (ja) | 誘電性アンチヒューズと直列にシリサイドに隣接して結晶化されたp−i−nダイオードおよびその形成方法 | |

| US8004013B2 (en) | Polycrystalline thin film bipolar transistors |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100831 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100831 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130226 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130521 |