JP2010258301A - インターポーザ及び半導体装置 - Google Patents

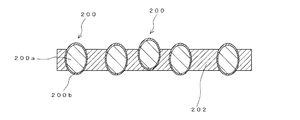

インターポーザ及び半導体装置 Download PDFInfo

- Publication number

- JP2010258301A JP2010258301A JP2009108269A JP2009108269A JP2010258301A JP 2010258301 A JP2010258301 A JP 2010258301A JP 2009108269 A JP2009108269 A JP 2009108269A JP 2009108269 A JP2009108269 A JP 2009108269A JP 2010258301 A JP2010258301 A JP 2010258301A

- Authority

- JP

- Japan

- Prior art keywords

- interposer

- connection terminal

- chip

- wiring board

- chip component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W70/655—

-

- H10W74/15—

-

- H10W90/724—

-

- H10W90/734—

Landscapes

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009108269A JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009108269A JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010258301A true JP2010258301A (ja) | 2010-11-11 |

| JP2010258301A5 JP2010258301A5 (enExample) | 2012-04-12 |

Family

ID=43318855

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009108269A Pending JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010258301A (enExample) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014212183A (ja) * | 2013-04-18 | 2014-11-13 | 大日本印刷株式会社 | 貫通電極基板の製造方法、貫通電極基板、および半導体装置 |

| US10806033B2 (en) | 2017-10-03 | 2020-10-13 | Murata Manufacturing Co., Ltd. | Interposer and electronic device |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501426A (ja) * | 1988-08-01 | 1991-03-28 | サーキット・コンポーネンツ・インコーポレイテッド | 高誘電率の軟質シート材料 |

| JPH1074668A (ja) * | 1996-08-30 | 1998-03-17 | Rohm Co Ltd | アレイ型固体電解コンデンサの構造及びその製造方法 |

| JP2001352004A (ja) * | 2000-06-09 | 2001-12-21 | Fujitsu Ltd | 回路基板及びその製造方法並びに半導体装置 |

| JP2005150490A (ja) * | 2003-11-18 | 2005-06-09 | Canon Inc | Icとプリント配線基板間のシート部品 |

| JP2005236008A (ja) * | 2004-02-19 | 2005-09-02 | Fujitsu Ltd | コンデンサシート |

| JP2009049087A (ja) * | 2007-08-16 | 2009-03-05 | Panasonic Corp | 電子部品と電子部品の製造方法 |

-

2009

- 2009-04-27 JP JP2009108269A patent/JP2010258301A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501426A (ja) * | 1988-08-01 | 1991-03-28 | サーキット・コンポーネンツ・インコーポレイテッド | 高誘電率の軟質シート材料 |

| JPH1074668A (ja) * | 1996-08-30 | 1998-03-17 | Rohm Co Ltd | アレイ型固体電解コンデンサの構造及びその製造方法 |

| JP2001352004A (ja) * | 2000-06-09 | 2001-12-21 | Fujitsu Ltd | 回路基板及びその製造方法並びに半導体装置 |

| JP2005150490A (ja) * | 2003-11-18 | 2005-06-09 | Canon Inc | Icとプリント配線基板間のシート部品 |

| JP2005236008A (ja) * | 2004-02-19 | 2005-09-02 | Fujitsu Ltd | コンデンサシート |

| JP2009049087A (ja) * | 2007-08-16 | 2009-03-05 | Panasonic Corp | 電子部品と電子部品の製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014212183A (ja) * | 2013-04-18 | 2014-11-13 | 大日本印刷株式会社 | 貫通電極基板の製造方法、貫通電極基板、および半導体装置 |

| US10806033B2 (en) | 2017-10-03 | 2020-10-13 | Murata Manufacturing Co., Ltd. | Interposer and electronic device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9578745B2 (en) | Printed wiring board, method for manufacturing printed wiring board and package-on-package | |

| US9693458B2 (en) | Printed wiring board, method for manufacturing printed wiring board and package-on-package | |

| US20080081161A1 (en) | Wiring board and semiconductor device | |

| CN101853826A (zh) | 连接部件和印刷电路板单元 | |

| KR101420514B1 (ko) | 전자부품들이 구비된 기판구조 및 전자부품들이 구비된 기판구조의 제조방법 | |

| JP2013219170A (ja) | 基板装置 | |

| TWI466611B (zh) | 晶片封裝結構、具有內埋元件的電路板及其製作方法 | |

| KR20090012664A (ko) | 금속 베이스 패키지 기판과 이를 이용한 3차원 다층 패키지모듈 및 그 제조방법 | |

| TWI498056B (zh) | 具有內埋元件的電路板、其製作方法及封裝結構 | |

| JP5093104B2 (ja) | 受動部品内蔵インターポーザ | |

| KR101565690B1 (ko) | 회로기판, 회로기판 제조방법, 전자부품 패키지 및 전자부품 패키지 제조방법 | |

| KR20160138754A (ko) | 인쇄회로기판, 반도체 패키지 및 그 제조방법 | |

| US9894790B2 (en) | Electronic component module and manufacturing method thereof | |

| JP2010258301A (ja) | インターポーザ及び半導体装置 | |

| JP2010272563A (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| KR101483874B1 (ko) | 인쇄회로기판 | |

| JP2010258301A5 (enExample) | ||

| US9107296B2 (en) | Thermo/electrical conductor arrangement for multilayer printed circuit boards | |

| KR102536256B1 (ko) | 임베디드 인쇄회로기판 | |

| KR102426111B1 (ko) | 임베디드 인쇄회로기판 | |

| JP2004303944A (ja) | モジュール基板及びその製造方法 | |

| JP2007027472A5 (enExample) | ||

| JP5601413B2 (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| KR100679816B1 (ko) | 반도체 패키지 | |

| KR100661653B1 (ko) | 기판조립체 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120229 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120229 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130702 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140408 |